# **Audio Processor for Portable Communication Devices**

## BelaSigna 300

#### Introduction

BelaSigna<sup>®</sup> 300 is a DSP-based mixed-signal audio processing system that delivers superior audio clarity without compromising size or battery life. The processor is specifically designed for monaural portable communication devices requiring high performance audio processing capabilities and programming flexibility when form-factor and power consumption are key design constraints.

The efficient dual—MAC 24-bit CFX DSP core, together with the HEAR configurable accelerator signal processing engine, high speed debugging interface, advanced algorithm security system, state-of-the-art analog front end, Class D output stage and much more, constitute an entire system on a single chip, which enables manufacturers to create a range of advanced and unique products. The system features a high level of instructional parallelism, providing highly efficient computing capability. It can simultaneously execute multiple advanced adaptive noise reduction and echo cancellation algorithms, and uses an asymmetric dual—core patented architecture to allow for more processing in fewer clock cycles, resulting in reduced power consumption.

BelaSigna 300 is supported by a comprehensive suite of development tools, hands—on training, full technical support and a network of solution partners offering software and engineering services to help speed product design and shorten time to market.

### **Key Features**

- Flexible DSP-based System: a complete DSP-based, mixed-signal audio system consisting of the CFX core, a fully programmable, highly cycle-efficient, dual-Harvard architecture 24-bit DSP utilizing explicit parallelism; the HEAR configurable accelerator for optimized signal processing; and an efficient input/output controller (IOC) along with a full complement of peripherals and interfaces, which optimize the architecture for audio processing at extremely low power consumption

- **Ultra-low-power:** typically 1–5 mA

- Excellent Audio Fidelity: up to 110 dB input dynamic range, exceptionally low system noise and low group delay

- **Miniature Form Factor:** available in a miniature 3.63 mm x 2.68 mm x 0.92 mm (including solder balls) WLCSP package.

- Multiple Audio Input Sources: four input channels from five input sources (depends on package selection) can be used simultaneously for multiple microphones or direct analog audio inputs

- Full Range of Configurable Interfaces: including a fast I<sup>2</sup>C-based interface for download, debug and general communication, a highly configurable PCM interface to stream data into and out of the device, a high-speed UART, an SPI port and 5 GPIOs

#### ON Semiconductor®

www.onsemi.com

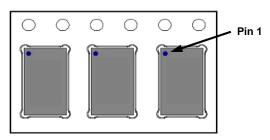

WLCSP-35 W SUFFIX CASE 567AG

#### MARKING DIAGRAM

BELASIGNA300 35-09-G AWLYYWWG

BELASIGNA300 = Device Code

35 = Number of Balls 09 = Revision of Die

G = Green

A Assembly Site

WL Wafer Lot Number

YY Year of Production, Last Two Numbers

WW Work Week Number

G = Pb-Free

#### ORDERING INFORMATION

| Device         | Package            | Shipping <sup>†</sup> |

|----------------|--------------------|-----------------------|

| B300W35A109XXG | WLCSP<br>(Pb-Free) | 2500 / Tape &<br>Reel |

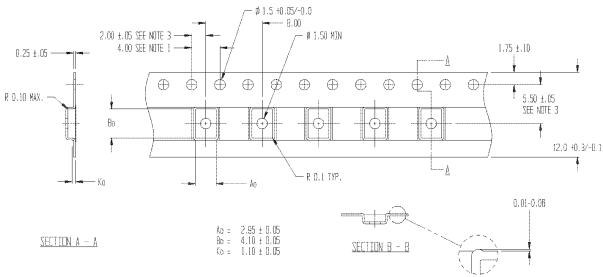

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

- Integrated A/D Converters and Powered Output: minimize need for external components

- Flexible Clocking Architecture: supports speeds up to 40 MHz

- "Smart" Power Management: including low current standby mode requiring only 0.06 mA

- Diverse Memory Architecture: 4864x48—bit words of shared memory between the CFX core and the HEAR accelerator plus 8–Kword DSP core data memory, 12–Kwords of 32–bit DSP core program memory as well as other memory banks

- Data Security: sensitive program data can be encrypted for storage in external NVRAM to prevent unauthorized parties from gaining access to proprietary software intellectual property, 128-bit AES encryption

- **Development Tools:** interface hardware with USB support as well as a full IDE that can be used for every step of program development including testing and debugging

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Contents**

| Introduction                                         | 1    |

|------------------------------------------------------|------|

| Figures and Data                                     | 3    |

| Mechanical Information and Circuit Design Guidelines | 6    |

| Architecture Overview                                |      |

| Application Diagrams                                 | . 24 |

| Assembly Information                                 | . 25 |

| Missallanaous                                        |      |

#### **Figures and Data**

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                | Min  | Max | Unit |  |  |

|----------------------------------------------------------|------|-----|------|--|--|

| Voltage at any input pin                                 | -0.3 | 2.0 | V    |  |  |

| Operating supply voltage (Note 1)                        | 0.9  | 2.0 | V    |  |  |

| Operating temperature range (Note 2)                     | -40  | 85  | °C   |  |  |

| Storage temperature range (Note 3) –55 85 °C             |      |     |      |  |  |

| Caution: Class 2 ESD Sensitivity, JESD22-A114-B (2000 V) |      |     |      |  |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Functional operation only guaranteed below 0°C for digital core (VDDC) and system voltages above 1.0 V.

- 2. Parameters may exceed listed tolerances when out of the temperature range 0 to 50°C.

- 3. Extended range –55 to 125°C for storage temperature is under qualification.

## **Electrical Performance Specifications**

The tests were performed at 20°C with a clean 1.8 V supply voltage. BelaSigna 300 was running in low voltage mode (VDDC = 1.2 V). The system clock (SYS\_CLK) was set to 5.12 MHz and the sampling frequency is 16 kHz unless otherwise noted. Parameters marked as screened are tested on each chip. Other parameters are qualified but not tested on every part.

**Table 2. ELECTRICAL SPECIFICATIONS**

| Description                      | Symbol               | Conditions                                                                                                         | Min  | Тур  | Max  | Units | Screened |

|----------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|------|------|------|-------|----------|

| OVERALL                          | •                    |                                                                                                                    |      |      |      | •     |          |

| Supply voltage                   | V <sub>BAT</sub>     | The WLCSP package option will not operate properly below 1.8 V if it relies on an external EEPROM powered by VBAT. | 0.9  | 1.8  | 2.0  | V     | <b>V</b> |

| Current consumption              | I <sub>BAT</sub>     | Filterbank, 100% CFX usage,<br>5.12 MHz, 16 kHz<br>Ambient room temperature                                        | -    | 750  | -    | μΑ    | <b>V</b> |

|                                  |                      | WDRC, VBAT = 1.8 V<br>Excludes output drive current<br>Ambient room temperature                                    | -    | 600  | -    | μΑ    | <b>V</b> |

|                                  |                      | AEC, VBAT = 1.8 V<br>Excludes output drive current<br>Ambient room temperature                                     | -    | 2.1  | -    | mA    | <b>V</b> |

|                                  |                      | Theoretical maximum Excludes output drive current Ambient room temperature                                         | -    | 10   | -    | mA    |          |

|                                  |                      | Deep Sleep current<br>Ambient room temperature,<br>VBAT = 1.25 V                                                   | -    | 26   | 40   | μΑ    |          |

|                                  |                      | Deep Sleep current<br>Ambient room temperature,<br>VBAT = 1.8 V                                                    | -    | 62   | 160  | μΑ    | V        |

| VREG (1 μF External Capac        | itor)                |                                                                                                                    |      |      |      |       |          |

| Regulated voltage output         | $V_{REG}$            |                                                                                                                    | 0.95 | 1.00 | 1.05 | V     | V        |

| Regulator PSRR                   | $V_{REG\_PSRR}$      | 1 kHz                                                                                                              | 50   | 55   | -    | dB    |          |

| Load current                     | I <sub>LOAD</sub>    |                                                                                                                    | -    | _    | 2    | mA    |          |

| Load regulation                  | LOAD <sub>REG</sub>  |                                                                                                                    | -    | 6.1  | 6.5  | mV/mA | V        |

| Line regulation                  | LINE <sub>REG</sub>  |                                                                                                                    | -    | 2    | 5    | mV/V  |          |

| VDBL (1 μF External Capaci       | itor)                |                                                                                                                    |      |      |      |       |          |

| Regulated doubled voltage output | VDBL                 |                                                                                                                    | 1.9  | 2.0  | 2.1  | V     | V        |

| Regulator PSRR                   | VDBL <sub>PSRR</sub> | 1 kHz                                                                                                              | 35   | 41   | -    | dB    |          |

| Load current                     | I <sub>LOAD</sub>    |                                                                                                                    | _    | _    | 2.5  | mA    |          |

Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description                               | Symbol                    | Conditions                                                                                                                                                                                                                 | Min                                                                             | Тур                                                                                  | Max                                        | Units       | Screened  |

|-------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------|-------------|-----------|

| VDBL (1 μF External Capaci                | tor)                      |                                                                                                                                                                                                                            |                                                                                 | 1                                                                                    |                                            | 1           |           |

| Load regulation                           | LOAD <sub>REG</sub>       |                                                                                                                                                                                                                            | -                                                                               | 7                                                                                    | 10                                         | mV/mA       | √         |

| Line regulation                           | LINE <sub>REG</sub>       |                                                                                                                                                                                                                            | _                                                                               | 10                                                                                   | 20                                         | mV/V        |           |

| VDDC (1 μF External Capaci                | itor)                     | 1                                                                                                                                                                                                                          |                                                                                 | 1                                                                                    |                                            |             | <u>I</u>  |

| Digital supply voltage output             | VDDC                      | Configured by a control register                                                                                                                                                                                           | 0.79                                                                            | 0.95                                                                                 | 1.25                                       | V           | $\sqrt{}$ |

| VDDC output level adjustment              | VDDC <sub>STEP</sub>      |                                                                                                                                                                                                                            | 27                                                                              | 29                                                                                   | 31                                         | mV          |           |

| Regulator PSRR                            | VDDC <sub>PSRR</sub>      | 1 kHz                                                                                                                                                                                                                      | 25                                                                              | 25.5                                                                                 | 26                                         | dB          |           |

| Load current                              | I <sub>LOAD</sub>         |                                                                                                                                                                                                                            | _                                                                               | _                                                                                    | 3.5                                        | mA          |           |

| Load regulation                           | LOAD <sub>REG</sub>       |                                                                                                                                                                                                                            | _                                                                               | 3                                                                                    | 12                                         | mV/mA       | √         |

| Line regulation                           | LINE <sub>REG</sub>       |                                                                                                                                                                                                                            | _                                                                               | 3                                                                                    | 8                                          | mV/V        |           |

| POWER-ON-RESET (POR)                      |                           |                                                                                                                                                                                                                            |                                                                                 | 1                                                                                    |                                            | 1           |           |

| POR startup voltage                       | VDDC <sub>STARTUP</sub>   |                                                                                                                                                                                                                            | 0.775                                                                           | 0.803                                                                                | 0.837                                      | V           |           |

| POR shutdown voltage                      | VDDC <sub>SHUTDOWN</sub>  |                                                                                                                                                                                                                            | 0.755                                                                           | 0.784                                                                                | 0.821                                      | V           |           |

| POR hysteresis                            | POR <sub>HYSTERESIS</sub> |                                                                                                                                                                                                                            | 13.8                                                                            | 19.1                                                                                 | 22.0                                       | mV          |           |

| POR duration                              | T <sub>POR</sub>          |                                                                                                                                                                                                                            | 11.0                                                                            | 11.6                                                                                 | 12.3                                       | ms          |           |

| INPUT STAGE                               |                           | <u> </u>                                                                                                                                                                                                                   |                                                                                 | 1                                                                                    |                                            | 1           | l         |

| Analog input voltage                      | V <sub>IN</sub>           |                                                                                                                                                                                                                            | 0                                                                               | _                                                                                    | 2                                          | V           |           |

| Preamplifier gain tolerance               | PAG                       | 1 kHz                                                                                                                                                                                                                      | -1                                                                              | 0                                                                                    | 1                                          | dB          | √         |

| Input impedance                           | R <sub>IN</sub>           | 0 dB preamplifer gain                                                                                                                                                                                                      | _                                                                               | 239                                                                                  | _                                          | kΩ          |           |

| 1                                         | "'                        | Non-zero preamplifier gains                                                                                                                                                                                                | 550                                                                             | 578                                                                                  | 615                                        | kΩ          | √         |

| Input referred noise  Input dynamic range | IN <sub>IRN</sub>         | Unweighted, 100 Hz to 10 kHz BW Preamplifier setting: 0 dB 12 dB 15 dB 18 dB 21 dB 24 dB 27 dB 30 dB 1 kHz, 20 Hz to 8 kHz BW Preamplifier setting: 0 dB 12 dB 13 dB 14 dB 15 dB 15 dB 16 dB 17 dB 18 dB 18 dB 19 dB 19 dB | -<br>-<br>-<br>-<br>-<br>-<br>-<br>85<br>84<br>84<br>84<br>83<br>82<br>81<br>80 | 39<br>10<br>7<br>6<br>4.5<br>4<br>3.5<br>3<br>89<br>88<br>88<br>87<br>86<br>85<br>83 | 50<br>12<br>9<br>8<br>5.5<br>5<br>4.5<br>4 | μVrms<br>dB | <b>V</b>  |

|                                           |                           | 30 dB                                                                                                                                                                                                                      | 78                                                                              | 81                                                                                   | -                                          |             |           |

| Input peak THD+N                          | IN <sub>THDN</sub>        | Any valid preamplifier gain, 1 kHz                                                                                                                                                                                         | _                                                                               | -70                                                                                  | -63                                        | dB          | $\sqrt{}$ |

| DIRECT DIGITAL OUTPUT                     | 1                         | <u> </u>                                                                                                                                                                                                                   |                                                                                 |                                                                                      |                                            | 1           | ı         |

| Maximum load current                      | I <sub>DO</sub>           | Normal mode                                                                                                                                                                                                                | _                                                                               | -                                                                                    | 50                                         | mA          |           |

| Output impedance                          | R <sub>DO</sub>           | Normal mode                                                                                                                                                                                                                | _                                                                               | -                                                                                    | 5.5                                        | Ω           |           |

| Output dynamic range                      | DO <sub>DR</sub>          | Unweighted, 100 Hz to 8 kHz<br>BW, mono                                                                                                                                                                                    | 92                                                                              | 95                                                                                   | -                                          | dB          |           |

Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description                                      | Symbol               | Conditions                            | Min                   | Тур               | Max           | Units | Screened |

|--------------------------------------------------|----------------------|---------------------------------------|-----------------------|-------------------|---------------|-------|----------|

| DIRECT DIGITAL OUTPUT                            |                      |                                       |                       |                   |               |       |          |

| Output THD+N                                     | DO <sub>THDN</sub>   | Unweighted, 100 Hz to 22 kHz BW, mono | -                     | <b>–</b> 79       | -76           | dB    | √        |

| Output voltage                                   | DO <sub>VOUT</sub>   |                                       | -V <sub>BATRCVR</sub> |                   | $V_{BATRCVR}$ | V     |          |

| ANTI-ALIASING FILTERS (In                        | put and Output)      |                                       |                       |                   |               |       |          |

| Preamplifier filter cut-off frequency            |                      | Preamp not bypassed                   | -                     | 20                | -             | kHz   | <b>√</b> |

| Digital anti–aliasing filter cut–off frequency   |                      |                                       | _                     | f <sub>S</sub> /2 | _             |       | <b>√</b> |

| Passband flatness                                |                      |                                       | -1                    | -                 | 1             | dB    |          |

| Input stopband attenuation                       |                      | 60 kHz (12 kHz cut-off)               | -                     | 60                | _             | dB    | √        |

| LOW-SPEED A/D                                    |                      |                                       |                       |                   |               |       | •        |

| Input voltage                                    |                      | Peak input voltage                    | 0                     | -                 | 2.0           | V     | √        |

| INL                                              |                      | From GND to 2*VREG                    | -                     | 4                 | 10            | LSB   |          |

| DNL                                              |                      | From GND to 2*VREG                    | -                     | _                 | 2             | LSB   |          |

| Maximum variation over temperature (0°C to 50°C) |                      |                                       | _                     | -                 | 5             | LSB   |          |

| Sampling frequency                               |                      | All channels sequentially             | -                     | 12.8              | -             | kHz   |          |

| Channel sampling frequency                       |                      | 8 channels                            | -                     | 1.6               | -             | kHz   |          |

| DIGITAL PADS                                     |                      |                                       |                       |                   |               |       |          |

| Voltage level for high input                     | $V_{IH}$             |                                       | VBAT<br>* 0.8         | -                 | _             | V     | √        |

| Voltage level for low input                      | V <sub>IL</sub>      |                                       | -                     | -                 | VBAT<br>* 0.2 | V     | √        |

| Voltage level for high output                    | V <sub>OH</sub>      | 2 mA source current                   | VDDO<br>* 0.8         | -                 | -             | V     | √        |

| Voltage level for low output                     | V <sub>OL</sub>      | 2 mA sink current                     | -                     | -                 | VDDO<br>* 0.2 | V     | √        |

| Input capacitance for digital pads               | C <sub>IN</sub>      |                                       | _                     | 4                 | -             | pF    |          |

| Pull–up resistance for digital input pads        | R <sub>UP_IN</sub>   |                                       | 220                   | 270               | 320           | kΩ    | √        |

| Pull–down resistance for digital input pads      | R <sub>DOWN_IN</sub> |                                       | 220                   | 270               | 320           | kΩ    | √        |

| Sample rate tolerance                            | FS                   | Sample rate of 16 kHz or 32 kHz       | -1                    | ±0                | +1            | %     |          |

| Rise and fall time                               | Tr, Tf               | Digital output pad                    |                       |                   |               |       |          |

| ESD                                              |                      | Human Body Model (HBM)                |                       |                   | 2             | kV    |          |

|                                                  |                      | Machine Model (MM)                    |                       |                   | 200           | V     |          |

|                                                  |                      | Charged Device Model (CDM)            |                       |                   | 500           | V     |          |

| Latch-up                                         |                      | V < GNDC, V > VBAT                    |                       |                   | 200           | mA    |          |

| OSCILLATION CIRCUITRY                            |                      |                                       |                       |                   |               |       |          |

| Internal oscillator frequency                    | SYS_CLK              |                                       | 0.5                   | -                 | 10.24         | MHz   | √        |

| Calibrated internal clock frequency              | SYS_CLK              |                                       | -1                    | ±0                | +1            | %     | √        |

| Internal oscillator jitter                       |                      | System clock: 1.28 MHz                | -                     | 0.4               | 1             | ns    |          |

Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description                                  | Symbol  | Conditions                  | Min | Тур | Max | Units | Screened  |

|----------------------------------------------|---------|-----------------------------|-----|-----|-----|-------|-----------|

| OSCILLATION CIRCUITRY                        |         |                             |     |     | •   |       | •         |

| External oscillator tolerances               | EXT_CLK | Duty cycle                  | 45  | 50  | 55  | %     |           |

|                                              |         | System clock: 30 MHz        | _   | _   | 300 | ps    |           |

| Maximum working frequency CLK <sub>MAX</sub> |         | External clock; VBAT: 1.8 V |     | _   | 40  | MHz   | $\sqrt{}$ |

| DIGITAL INTERFACES                           |         |                             |     |     |     |       |           |

| I2C baud rate                                |         | System clock < 1.6 MHz      | _   | _   | 100 | kbps  |           |

|                                              |         | System clock > 1.6 MHz      | _   | _   | 400 | kbps  |           |

| General–purpose UART baud rate               |         | System clock ≥ 5.12 MHz     | -   | 1   | -   | Mbps  |           |

#### **Environmental Characteristics**

All BelaSigna 300 parts are Pb-free, RoHS-compliant and Green.

BelaSigna 300 parts are qualified against standards outlined in the following sections.

All BelaSigna 300 parts are Green (RoHS-compliant). Contact ON Semiconductor for supporting documentation.

## **WLCSP Package Option**

The solder ball composition for the WLCSP package is SAC266.

**Table 3. PACKAGE-LEVEL QUALIFICATION**

| Packaging Level                       |                               |

|---------------------------------------|-------------------------------|

| Moisture sensitivity level            | JEDEC Level 1                 |

| Thermal cycling test (TCT)            | –55°C to 150°C for 500 cycles |

| Highly accelerated stress test (HAST) | 85°C / 85% RH for 1000 hours  |

| High temperature stress test (HTST)   | 150°C for 1000 hours          |

#### **Table 4. BOARD-LEVEL QUALIFICATION**

| Board Level |                                                 |

|-------------|-------------------------------------------------|

| Temperature | –40°C to 125°C for 2500 cycles with no failures |

## **Mechanical Information and Circuit Design Guidelines**

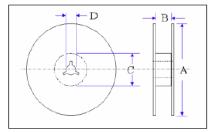

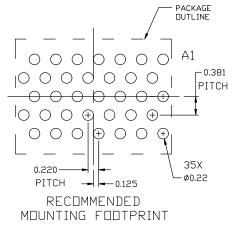

BelaSigna 300 is available in a 2.68 x 3.63 mm ultra-miniature wafer-level chip scale package (WLCSP).

## **WLCSP Pin Out**

A total of 35 active pins are present on BelaSigna 300. They are organized in a staggered array. A description of these pins is given in Table 5.

## **Table 5. PAD DESCRIPTIONS**

| Pad Index | BelaSigna 300 Pad Name  | Description                                            | I/O | A/D |

|-----------|-------------------------|--------------------------------------------------------|-----|-----|

| A1        | GNDRCVR                 | Ground for output driver                               | N/A | Α   |

| A5        | VBATRCVR                | Power supply for output stage                          | I   | Α   |

| B2        | RCVR_HP+                | Extra output driver pad for high power mode            | 0   | Α   |

| C3        | RCVR+                   | Output from output driver                              | 0   | Α   |

| А3        | RCVR-                   | Output from output driver                              | 0   | Α   |

| B4        | RCVR_HP-                | Extra output driver pad for high power mode            | 0   | Α   |

| B6        | CAP0                    | Charge pump capacitor pin 0                            | N/A | Α   |

| C5        | CAP1                    | Charge pump capacitor pin 1                            | N/A | Α   |

| A7        | VDBL                    | Doubled voltage                                        | 0   | Α   |

| B8        | VBAT                    | Power supply                                           | ı   | Α   |

| B10       | VREG                    | Regulated supply voltage                               | 0   | Α   |

| A9        | AGND                    | Analog ground                                          | N/A | Α   |

| A11       | Al4                     | Audio signal input 4                                   | ı   | Α   |

| B12       | AI2/LOUT2               | Audio signal input 2/output signal from preamp 2       | I/O | Α   |

| A13       | AI1/LOUT1               | Audio signal input 1/output signal from preamp 1       | I/O | Α   |

| B14       | AI0/LOUT0               | Audio signal input 0/output signal from preamp 0       | I/O | Α   |

| D14       | GPIO[4]/LSAD[4]         | General-purpose I/O 4/low speed AD input 4             | I/O | A/D |

| E13       | GPIO[3]/LSAD[3]         | General-purpose I/O 3/low speed AD input 3             | I/O | A/D |

| C13       | GPIO[2]/LSAD[2]         | General-purpose I/O 2/low speed AD input 2             | I/O | A/D |

| D12       | GPIO[1]/LSAD[1]/UART-RX | General-purpose I/O 1/low speed AD input 1/and UART RX | I/O | A/D |

| E11       | GPIO[0]/UART-TX         | General-purpose I/O 0/UART TX                          | I/O | A/D |

| C9        | GNDC                    | Digital ground                                         | N/A | Α   |

| C11       | SDA (I2C)               | I2C data                                               | I/O | D   |

| D10       | SCL (I2C)               | I2C clock                                              | I/O | D   |

| E9        | EXT_CLK                 | External clock input/internal clock output             | I/O | D   |

| D8        | VDDC                    | Core logic power                                       | 0   | Α   |

| E7        | SPI_CLK                 | Serial peripheral interface clock                      | 0   | D   |

| C7        | SPI_SERI                | Serial peripheral interface input                      | ı   | D   |

| D6        | SPI_CS                  | Serial peripheral interface chip select                | 0   | D   |

| E5        | SPI_SERO                | Serial peripheral interface output                     | 0   | D   |

| D4        | PCM_FR                  | PCM interface frame                                    | I/O | D   |

| E3        | PCM_SERI                | PCM interface input                                    | I   | D   |

| D2        | PCM_SERO                | PCM interface output                                   | 0   | D   |

| C1        | PCM_CLK                 | PCM interface clock                                    | I/O | D   |

| E1        | Reserved                | Reserved                                               |     |     |

## **Assembly / Design Notes**

For PCB manufacture with BelaSigna 300, ON Semiconductor recommends solder—on—pad (SoP) surface finish. With SoP, the solder mask opening should be non—solder mask—defined (NSMD) and copper pad geometry will be dictated by the PCB vendor's design requirements.

Alternative surface finishes are ENiG and OSP; volume of screened solder paste (#5) should be less than 0.0008 mm<sup>3</sup>. If no pre–screening of solder paste is used, then following conditions must be met:

#### **WLCSP Weight**

BelaSigna 300 has an average weight of 0.095 grams.

#### **Recommended Circuit Design Guidelines**

BelaSigna 300 is designed to allow both digital and analog processing in a single system. Due to the mixed–signal nature of this system, the careful design of the printed circuit board (PCB) layout is critical to maintain the high audio fidelity of BelaSigna 300. To avoid coupling noise into the audio signal path, keep the digital traces away from the analog traces. To avoid electrical feedback coupling, isolate the input traces from the output traces.

- 1. the solder mask opening should be >0.3 mm in diameter,

- 2. the copper pad will have 0.25 mm diameter, and

- 3. soldermask thickness should be less than 1 mil thick above the copper surface.

ON Semiconductor can provide BelaSigna 300 WLCSP land pattern CAD files to assist your PCB design upon request.

#### **Recommended Ground Design Strategy**

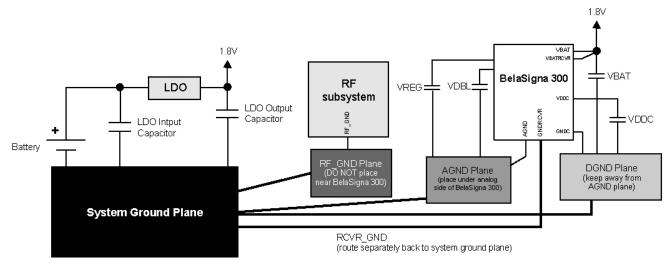

The ground plane should be partitioned into two: the analog ground plane (AGND) and the digital ground plane (DGND). These two planes should be connected together at a single point, known as the star point. The star point should be located at the ground terminal of a capacitor on the output of the power regulator as illustrated in Figure 1.

Figure 1. Schematic of Ground Scheme

The DGND plane is used as the ground return for digital circuits and should be placed under digital circuits. The AGND plane should be kept as noise—free as possible. It is used as the ground return for analog circuits and it should surround analog components and pins. It should not be connected to or placed under any noisy circuits such as RF chips, switching supplies or digital pads of BelaSigna 300 itself. Analog ground returns associated with the audio output stage should connect back to the star point on separate individual traces.

For details on which signals require special design consideration, see Table 6 and Table 7.

In some designs, space constraints may make separate ground planes impractical. In this case a star configuration strategy should be used. Each analog ground return should connect to the star point with separate traces.

#### **Internal Power Supplies**

Power management circuitry in BelaSigna 300 generates separate digital (VDDC) and analog (VREG, VDBL) regulated supplies. Each supply requires an external decoupling capacitor, even if the supply is not used externally. Decoupling capacitors should be placed as close as possible to the power pads. The VDDC internal regulator is a programmable power supply that allows the selection of the lowest digital supply depending on the clock frequency at which BelaSigna 300 will operate. See the Internal Digital Supply Voltage section for more details on VDDC.

Two other supply pins are also available on BelaSigna 300 (VDDO and VDDO\_SPI) which are internally connected to the VBAT pin.

Further details on these critical signals are provided in Table 6. Non-critical signals are outlined in Table 7.

**Table 6. CRITICAL SIGNALS**

| Pin Name                               | Description                                  | Routing Guideline                                                                                                                                                                                                                                             |

|----------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT                                   | Power supply                                 | Place 1 μF (min) decoupling capacitor close to pin. Connect negative terminal of capacitor to DGND plane.                                                                                                                                                     |

| VREG, VDBL                             | Internal regulator for analog sections       | Place separate 1 μF decoupling capacitors close to each pin. Connect negative capacitor terminal to AGND. Keep away from digital traces and output traces. VREG may be used to generate microphone bias. VDBL shall not be used to supply external circuitry. |

| AGND                                   | Analog ground return                         | Connect to AGND plane.                                                                                                                                                                                                                                        |

| VDDC                                   | Internal regulator for digital core          | Place 10 μF decoupling capacitor close to pin. Connect negative terminal of capacitor to DGND.                                                                                                                                                                |

| GNDC                                   | Digital ground return                        | Connect to digital ground.                                                                                                                                                                                                                                    |

| AI0/LOUT0,<br>AI1/LOUT1,<br>AI2/LOUT2  | Audio inputs                                 | Keep as short as possible.  Keep away from all digital traces and audio outputs.  Avoid routing in parallel with other traces.  Connect unused inputs to AGND.                                                                                                |

| RCVR+, RCVR-,<br>RCVR_HP+,<br>RCVR_HP- | Direct digital audio output                  | Keep away from analog traces, particularly audio inputs. Corresponding traces should be of approximately the same length. Ideally, route lines parallel to each other.                                                                                        |

| GNDRCVR                                | Output stage ground return                   | Connect to star point. Keep away from all analog audio inputs.                                                                                                                                                                                                |

| EXT_CLK                                | External clock input / internal clock output | Minimize trace length. Keep away from analog signals. If possible, surround with digital ground.                                                                                                                                                              |

Table 7. NON-CRITICAL SIGNALS

| Pin Name                            | Description                                           | Routing Guideline                    |

|-------------------------------------|-------------------------------------------------------|--------------------------------------|

| CAP0, CAP1                          | Internal charge pump – capacitor connection           | Place 100 nF capacitor close to pins |

| SDA, SCL                            | I2C port                                              | Keep as short as possible            |

| GPIO[30]                            | General-purpose I/O                                   | Not critical                         |

| UART_RX, UART_TX                    | General-purpose UART                                  | Not critical                         |

| PCM_FRAME, PCM_CLK, PCM_OUT, PCM_IN | PCM port                                              | Keep away from analog input lines    |

| LSAD[41]                            | Low-speed A/D converters                              | Not critical                         |

| SPI_CLK, SPI_CS, SPI_SERI, SPI_SERO | Serial peripheral interface port<br>Connect to EEPROM | Keep away from analog input lines    |

#### **Audio Inputs**

The audio input traces should be as short as possible. The input impedance of each audio input pad (e.g., AI0, AI1, AI2, AI3, AI4) is high (approximately 500 k $\Omega$ ); therefore a 10 nF capacitor is sufficient to decouple the DC bias. This capacitor and the internal resistance form a first-order analog high pass filter whose cutoff frequency can be calculated by  $f_{3dB}$  (Hz) = 1/(R x C x 2 $\pi$ ), which results in ~30 Hz for a 10 nF capacitor. This 10 nF capacitor value applies when the preamplifier is being used, in other words, when a non-unity gain is applied to the signals. When the preamplifier is by-passed, the impedance is reduced; hence, the cut-off frequency of the resulting high-pass filter could be too high. In such a case, the use of a 30-40 nF serial capacitor is recommended. In cases where line-level analog inputs without DC bias are used, the capacitor may be omitted for transparent bass response.

BelaSigna 300 provides microphone power supply (VREG) and ground (AGND). Keep audio input traces strictly away from output traces. A 2.0 V microphone bias might also be provided by the VDBL power supply.

Digital outputs (RCVR) MUST be kept away from microphone inputs to avoid cross-coupling.

#### **Audio Outputs**

The audio output traces should be as short as possible. The trace length of RCVR+ and RCVR- should be approximately the same to provide matched impedances.

#### **Recommendation for Unused Pins**

The table below shows the recommendation for each pin when they are not used.

**Table 8. RECOMMENDATIONS FOR UNUSED PADS**

| WLCSP Ball Index | BelaSigna 300 Signal Name | Recommended Connection when Not Used |

|------------------|---------------------------|--------------------------------------|

| B2               | RCVR_HP+                  | Do not connect                       |

| C3               | RCVR+                     | Do not connect                       |

| А3               | RCVR-                     | Do not connect                       |

| B4               | RCVR_HP-                  | Do not connect                       |

| A11              | Al4                       | Connect to AGND                      |

| N/A              | AI3/LOUT3                 | Connect to AGND                      |

| B12              | Al2/LOUT2                 | Connect to AGND                      |

| A13              | Al1/LOUT1                 | Connect to AGND                      |

| B14              | AI0/LOUT0                 | Connect to AGND                      |

| D14              | GPIO[4]/LSAD[4]           | Do not connect                       |

| E13              | GPIO[3]/LSAD[3]           | Do not connect                       |

| C13              | GPIO[2]/LSAD[2]           | Do not connect                       |

| D12              | GPIO[1]/LSAD[1]/UART-RX   | Do not connect                       |

| E11              | GPIO[0]/UART-TX           | Do not connect                       |

| E9               | EXT_CLK                   | Do not connect                       |

| E7               | SPI_CLK                   | Do not connect                       |

| C7               | SPI_SERI                  | Do not connect                       |

Table 8. RECOMMENDATIONS FOR UNUSED PADS (continued)

| WLCSP Ball Index | BelaSigna 300 Signal Name | Recommended Connection when Not Used |

|------------------|---------------------------|--------------------------------------|

| D6               | SPI_CS                    | Do not connect                       |

| E5               | SPI_SERO                  | Do not connect                       |

| D4               | PCM_FR                    | Do not connect                       |

| E3               | PCM_SERI                  | Do not connect                       |

| D2               | PCM_SERO                  | Do not connect                       |

| C1               | PCM_CLK                   | Do not connect                       |

| E1               | Reserved                  | Connect to GND                       |

#### **Architecture Overview**

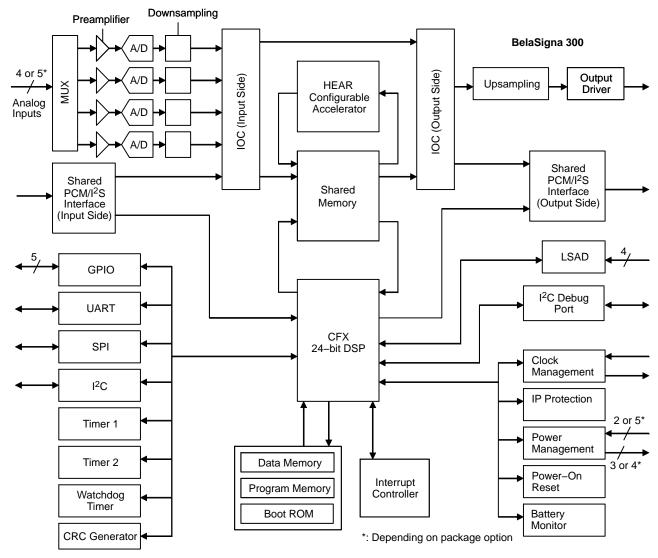

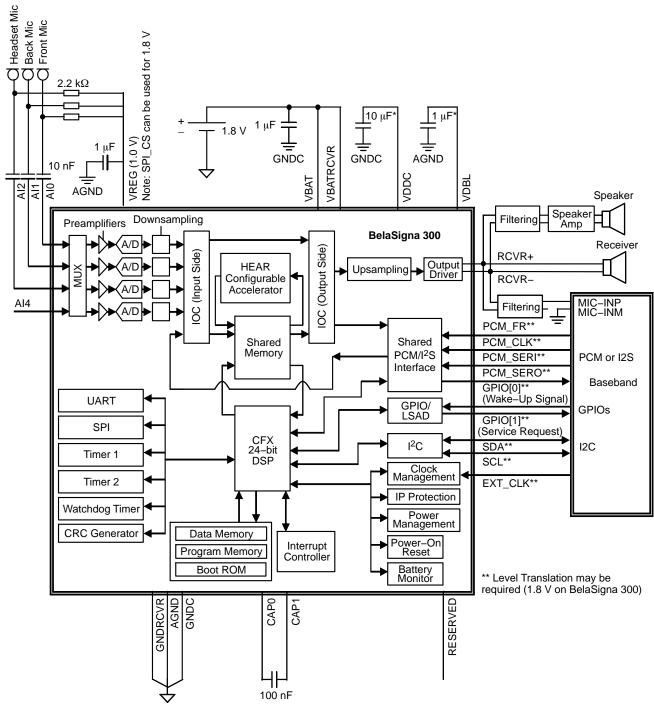

The architecture of BelaSigna 300 is shown in Figure 2.

Figure 2. BelaSigna 300 Architecture: A Complete Audio Processing System

#### **CFX DSP Core**

The CFX DSP is a user–programmable general–purpose DSP core that uses a 24-bit fixed–point, dual–MAC, dual–Harvard architecture. It is able to perform two MACs, two memory operations and two pointer updates per cycle, making it well–suited to computationally intensive algorithms.

#### The CFX features:

- Dual-MAC 24-bit load-store DSP core

- Four 56-bit accumulators

- Four 24-bit input registers

- Support for hardware loops nested up to 4 deep

- Combined XY memory space (48-bits wide)

- Dual address generator units

- Wide range of addressing modes:

- Direct

- Indirect with post-modification

- Modulo addressing

- Bit reverse

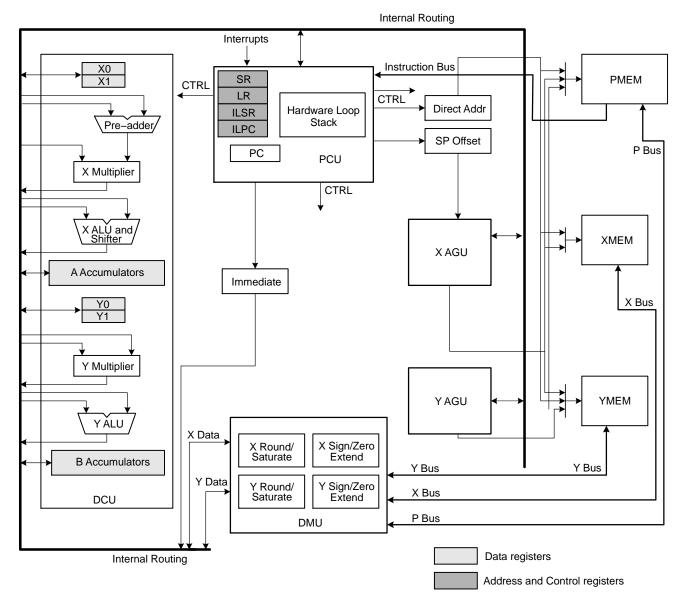

#### **CFX DSP Architecture**

The CFX architecture encompasses various memory types and sizes, peripherals, interrupt controllers, and interfaces. Figure 3 illustrates the basic architecture of the CFX. The control lines shown exiting the PCU indicate that control signals go from the PCU to essentially all other parts of the CFX.

The CFX employs a parallel instruction set for simultaneous control of multiple computation units. The DSP can execute up to four computation operations in parallel with two data transfers (including rounding and/or saturation as well as complex address updates), while simultaneously changing control flow.

Figure 3. CFX DSP Core Architecture

## **CFX DSP Instruction Set**

Table 9 shows the list of all general CFX instructions and their description. Many instructions have multiple variations not shown in the table. Please refer to the CFX DSP Architecture Manual for more details.

## Table 9. CFX SUMMARY INSTRUCTION SET

| Instruction | Description                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABS         | Calculate the absolute value of a data register or accumulator                                                                                                                       |

| ADD         | Add values (various combinations of accumulators, pointers and data registers)                                                                                                       |

| ADDMUL      | Add two XY data registers, multiply the result by a third XY data register, and store the result in an accumulator                                                                   |

| ADDMULADD   | Add two XY data registers, multiply the result by a third XY data register, and add the result to an accumulator                                                                     |

| ADDMULNEG   | Add two XY data registers, multiply the result by a third XY data register, negate the result and store it in an accumulator                                                         |

| ADDMULSUB   | Add two XY data registers, multiply the result by a third XY data register, and subtract the result from an accumulator                                                              |

| ADDSH       | Add two data registers or accumulators and shift right one bit, storing the result                                                                                                   |

| AND         | Perform a bitwise AND operation on the two operands                                                                                                                                  |

| BITCLR      | Clear a bit in the register                                                                                                                                                          |

| BITSET      | Set a bit in the register                                                                                                                                                            |

| BITTGL      | Toggle a bit in a data register                                                                                                                                                      |

| BITTST      | Test a bit in a data register                                                                                                                                                        |

| BREAKPOINT  | Halts the DSP for debugging if software breakpoints are enabled through the debug port                                                                                               |

| CALL        | Call a subroutine                                                                                                                                                                    |

| CLR         | Clear a word of X memory specified by an X pointer, with update                                                                                                                      |

| CMP         | Compare a data register or accumulator to another data register or accumulator or a value                                                                                            |

| CMPU        | Compare a data register to a value or another data register as unsigned values or compare two accumulators as unsigned values                                                        |

| DIVST       | Division step for dividing data register by data register and stores the result to a data register                                                                                   |

| ENDLOOP     | End a hardware loop before the count has reached zero                                                                                                                                |

| GOTO        | Branch to an address or label                                                                                                                                                        |

| INTERRUPT   | Software interrupt                                                                                                                                                                   |

| LOAD        | Load a register, accumulator or a memory location with another register, accumulator or data                                                                                         |

| LOG2ABS     | Calculate the logarithm base 2 of the absolute value of a data register, storing the result in a data register                                                                       |

| LOOP        | Loop with a specified count                                                                                                                                                          |

| MAX         | Determine the maximum value of two data registers or accumulators and store the result in a data register or accumulator                                                             |

| MIN         | Determine the minimum value of two data registers or accumulators and store the result in a data register or accumulator                                                             |

| MOVE        | Move a register or accumulator to a register or accumulator                                                                                                                          |

| MUL         | Multiply two XY data registers, storing the result in an accumulator                                                                                                                 |

| MULADD      | Multiply two XY data registers, and add the result to an accumulator                                                                                                                 |

| MULNEG      | Multiply two XY data registers, negate the result and store it in an accumulator                                                                                                     |

| MULSUB      | Multiply two XY data registers, and subtract the result from an accumulator                                                                                                          |

| NEG         | Negate a data register or accumulator, storing the result in a data register or accumulator                                                                                          |

| NLOG2ABS    | Calculate the logarithm base 2 of the absolute value of a data register, negate the result, and store the result in a data register                                                  |

| NOP         | No operation                                                                                                                                                                         |

| OR          | Perform a bitwise OR operation on two accumulators storing the result in an accumulator or on two data registers or a data register and value, storing the result in a data register |

| RETURN      | Return from a subroutine                                                                                                                                                             |

Table 9. CFX SUMMARY INSTRUCTION SET (continued)

| Instruction | Description                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

| RETURNI     | Return from an interrupt                                                                                                          |

| SHLL        | Shift a data register left logically                                                                                              |

| SHRA        | Shift a data register right arithmetically                                                                                        |

| SHRL        | Shift a data register right logically                                                                                             |

| SLEEP       | Enter sleep mode and wait for an interrupt and then wake up from sleep mode                                                       |

| STORE       | Store data, a register or accumulator in a register, accumulator or memory location                                               |

| SUB         | Subtract two data registers or accumulators, storing the result in a data register or accumulator                                 |

| SUBMUL      | Subtract two XY data registers, multiply the result by a third XY data register, and store the result in an accumulator           |

| SUBMULADD   | Subtract two XY data registers, multiply the result by a third XY data register, and add the result to an accumulator             |

| SUBMULNEG   | Subtract two XY data registers, multiply the result by a third XY data register, negate the result and store it in an accumulator |

| SUBMULSUB   | Subtract two XY data registers, multiply the result by a third XY data register, and subtract the result from an accumulator      |

| SUBSH       | Subtract two data registers or two accumulators and shift right one bit, storing the result in a data register or accumulator     |

| SUBSTEP     | Subtract a step register from the corresponding pointer                                                                           |

| SWAP        | Swap the contents of two data registers, conditionally                                                                            |

| XOR         | Perform a bitwise XOR operation on two data registers or a data register and a value, storing the result in a data register       |

#### **HEAR Configurable Accelerator**

The HEAR Configurable Accelerator is a highly optimized signal processing engine that is configured through the CFX. It offers high speed, high flexibility and high performance, while maintaining low power consumption. For added computing precision, the HEAR supports block floating point processing. Configuration of the HEAR is performed using the HEAR configuration tool (HCT). For further information on the usage of the HEAR and the HCT, please refer to the HEAR Configurable Accelerator Reference Manual.

The HEAR is optimized for advanced audio algorithms, including but not limited to the following:

- Dynamic range compression

- Directional processing

- Acoustic echo cancellation

- Noise reduction

To provide the ability for these algorithms to be executed efficiently, the HEAR excels at the following:

- Processing using a weighted overlap add (WOLA) filterbank or FFT

- Time domain filtering

- Subband filtering

- Attack/release filtering

- Vector addition/subtraction/multiplication

- Signal statistics (such as average, variance and correlation)

### Input/Output Controller (IOC)

The IOC is responsible for the automated data moves of all audio samples transferred in the system. The IOC can manage any system configuration and route the data accordingly. It is an advanced audio DMA unit.

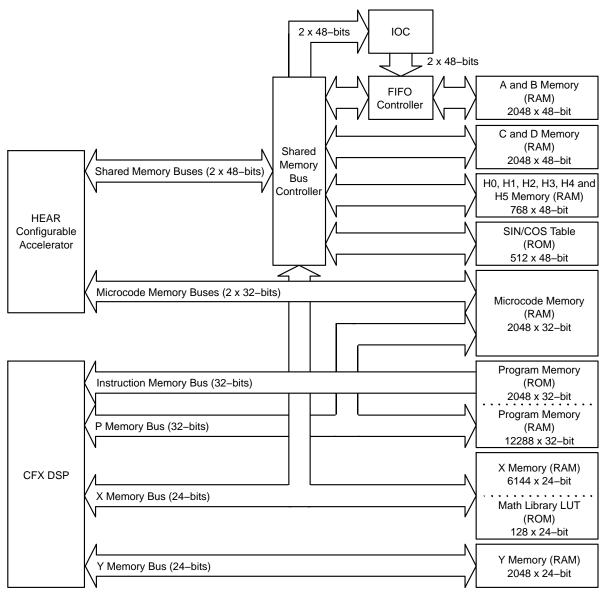

#### Memory

#### **RAM & ROM**

The size and width of each of the RAM and ROM structures are shown in Table 10:

**Table 10. RAM AND ROM STRUCTURE**

| Memory Structure       | Data Width | Memory Size |

|------------------------|------------|-------------|

| Program memory (ROM)   | 32         | 2048        |

| Program memory (RAM)   | 32         | 12288       |

| X memory (RAM)         | 24         | 6144        |

| Math library LUT (ROM) | 24         | 128         |

| Y memory (RAM)         | 24         | 2048        |

## **Shared Memories**

The shared CFX/HEAR memories include the following:

**Table 11. SHARED MEMORIES**

| Туре                     | Name                                        | Size                                                            |

|--------------------------|---------------------------------------------|-----------------------------------------------------------------|

| Data memory (RAM)        | H0MEM, H1MEM, H2MEM,<br>H3MEM, H4MEM, H5MEM | Each 128x48-bit words                                           |

| FIFO memory (RAM)        | AMEM, BMEM                                  | Each 1024x48-bit words                                          |

| Coefficient memory (RAM) | CMEM, DMEM                                  | Each 1024x48-bit words                                          |

| Data ROM                 | SIN/COS LUT                                 | 512x48-bit words containing the 512 point sin/cos look up table |

| Microcode memory (RAM)   | MICROCODE_MEM                               | 2048x32-bit words                                               |

#### **Memories Structure**

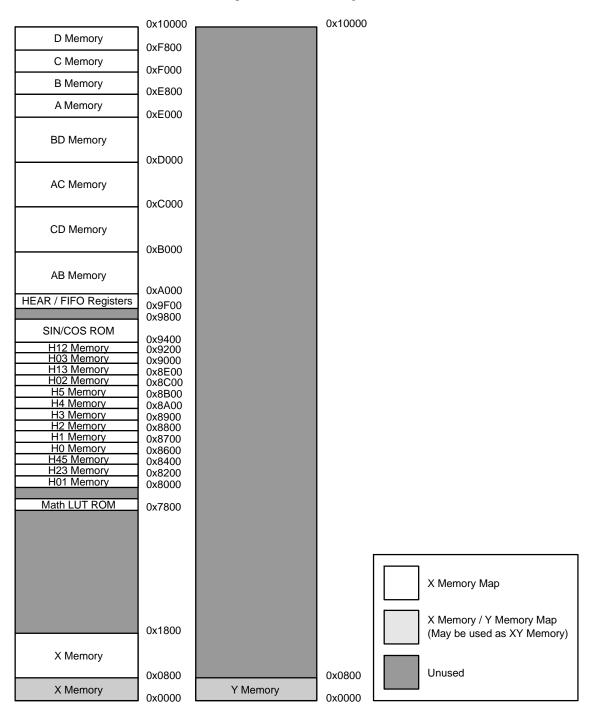

Figure 4 shows the system memory structure. The individual blocks are described in the sections that follow.

Figure 4. System Memory Architecture

#### **FIFO Controller**

The FIFO controller handles the moving of data to and from the FIFOs, after being initially configured. Up to eight FIFOs can be created by the FIFO controller, four in A memory (AMEM) and four in B memory (BMEM). Each

FIFO has a block counter that counts the number of samples read or written by the IOC. It creates a dedicated interrupt signal, updates the block counter and updates the FIFO pointers when a new block has been read or written.

#### **Memory Maps**

The structure of the XMEM and YMEM address spaces are shown in Figure 5.

Figure 5. XMEM and YMEM Memory Maps

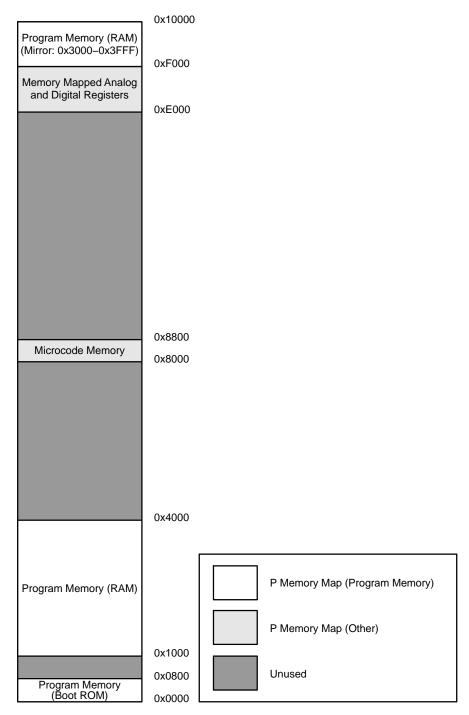

The structure of the PMEM address space is shown in Figure 6.

Figure 6. PMEM Memory Map

#### Other Digital Blocks and Functions

#### **General-Purpose Timer**

The CFX DSP system contains two general-purpose timers. These can be used for scheduling tasks that are not part of the sample-based signal-processing scheme, such as checking the battery voltage, and periodically asserting the available analog and digital inputs for purposes such as reading the value of a volume control potentiometer or detecting input from a push button.

#### **Watchdog Timer**

The watchdog timer is a programmable hardware timer that operates from the system clock and is used to ensure system sanity. It is always active and must be periodically acknowledged as a check that an application is still running. Once the watchdog times out, it generates an interrupt. If left to time out a second consecutive time without acknowledgement, a system reset will occur.

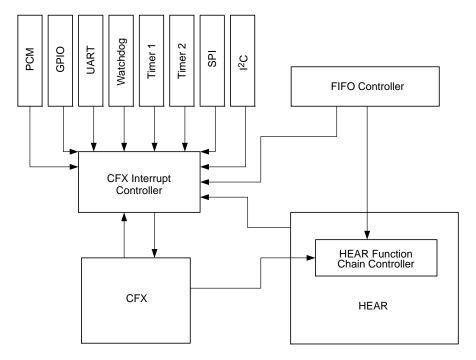

#### Interrupts

The interrupt flow of the system handles interrupts generated by the CFX DSP core and the HEAR accelerator. The CFX interrupt controller receives interrupts from the various blocks within the system. The FIFO controller can send interrupts to the CFX. The HEAR can generate events which are interrupts in the CFX.

#### **Hear Function Chain Controller**

The HEAR function chain controller responds to commands from the CFX, and events from the FIFO controller. It must be configured by the CFX to enable the triggering of particular function chains within a microcode configuration. This is accomplished through the appropriate setting of control registers as described in the Hardware Reference Manual for BelaSigna 300.

The interaction between the interrupt controller, the HEAR function chain controller and the rest of the system are shown in Figure 7.

Figure 7. Interrupt Flow

#### **Algorithm and Data Security**

Algorithm software code and user data that requires permanent retention is stored off the BelaSigna 300 chip in separate non-volatile memory. To support this, the BelaSigna 300 chip can gluelessly interface to an external SPI EEPROM.

To prevent unauthorized access to the sensitive intellectual property (IP) stored in the EEPROM, a comprehensive system is in place to protect manufacturer's application code and data. When locked the system implements an access restriction layer that prevents access to both volatile and non–volatile system memory. When unlocked, both memory and EEPROM are accessible.

To protect the IP in the non-volatile memory the system supports decoding algorithm and data sections belonging to an application that have been encrypted using the advanced encryption standard (AES) and stored in non-volatile memory. While system access restrictions are in place, the keys used in the decryption of these sections will be secured from external access by the regular access restrictions. When the system is externally "unlocked" these keys will be cleared, preventing their use in decoding an application by non-authorized parties. After un-restricting access in this way the system may then be restored by re-programming the decryption keys.

#### **Analog Blocks**

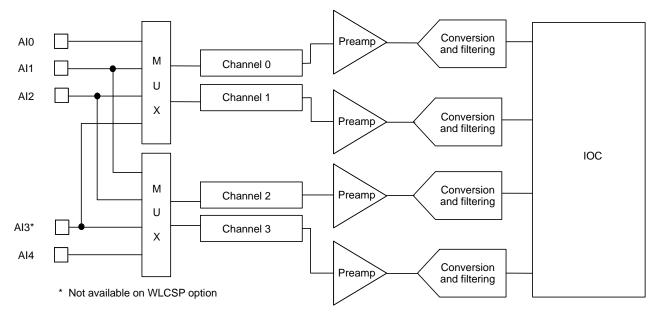

#### **Input Stage**

The analog audio input stage is comprised of four individual channels. For each channel, one input can be selected from any of the five possible input sources (depending on package option) and is then routed to the input of the programmable preamplifier that can be configured for bypass or gain values of 12 to 30 dB (3 dB steps). The input stage is shown in Figure 8.

A built-in feature allows a sampling delay to be configured for any one or more channels. This is useful in beam-forming applications.

Figure 8. Input Stage

#### Input Dynamic Range Extension (IDRX)

To increase the input dynamic range for a particular application, it is possible to pair—wise combine the four AD converters found on BelaSigna 300. This will increase the dynamic range up to 110 dB. When this technique is used, the device handles the preamplifier gain configuration based on the input level and sets it in such a way as to give the maximum possible dynamic range. This avoids having to make the design trade—off between sufficient amplification for low—level signals and avoiding saturation for high—level signals.

#### **Output Stage**

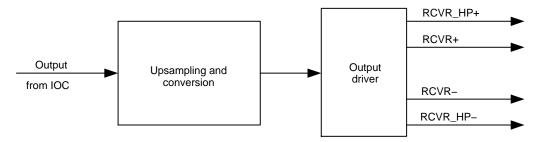

The output stage includes a 3<sup>rd</sup>-order sigma-delta modulator to produce a pulse density modulated (PDM) output signal. The sampling frequency of the sigma delta modulator is pre-scaled from the system clock.

The low-impedance output driver can also be used to directly drive an output transducer without the need for a

separate power amplifier or can be connected to another Digital Mic input on another system. The output stage is shown in Figure 9.

BelaSigna 300 has an option for high–power mode that decreases the impedance of the output stage, thus permitting higher possible acoustic output levels. To use this feature, RCVR\_HP+ should be connected to RCVR+, and RCVR\_HP- should be connected to RCVR-, you must combine the synchronized output signals externally to BelaSigna 300. Connect both RCVR+ and RCVR\_HP+ to a single terminal on an output transducer, and connect both RCVR- and RCVR\_HP- to the other terminal. An RC filter might be required based on receiver characteristics. Figure 9 shows the connections for the output driver in high–power mode

Electrical specifications on the output stage are available in Table 2.

Figure 9. Output Stage

Figure 10. External Signal Routing of Connections for High-Power Output Mode

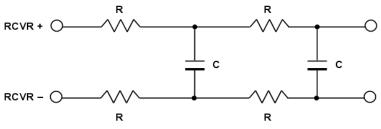

The high-frequencies in the Class-D PDM output are filtered by an RC filter or by the frequency response of the speaker itself. ON Semiconductor recommends a 2-pole RC

filter on the output stage if the output signal is not directly driving a receiver. Given below is the simple schematic for a 2–pole RC filter.

Figure 11. 2-Pole RC filter

Our recommendations for components for the RC Filter are given below:

For 8 KHz sampling, we recommend R = 8.2 k and C = 1 nF (3 dB cutoff frequency at 3.3 kHz)

For 16 KHz sampling, we recommend R = 8.2 k and C = 330 pF (3 dB cutoff frequency at 9 kHz)

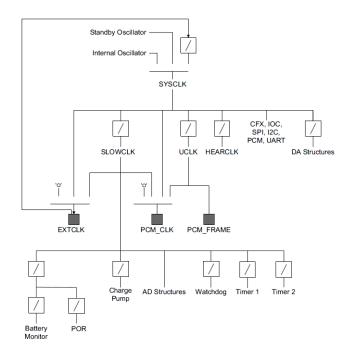

#### **Clock Generation Circuitry**

BelaSigna 300 is equipped with an un-calibrated internal RC oscillator that will provide clock support for booting and

stand—by mode operations. This internal clocking circuitry cannot be used during normal operation; as such, an external clock signal must be present on the EXT\_CLK pin to allow BelaSigna 300 to operate. All other needed clocks in the system are derived from this external clock frequency. Figure 12 shows the internal clock structure of BelaSigna 300.

Figure 12. Internal Clocking Structure

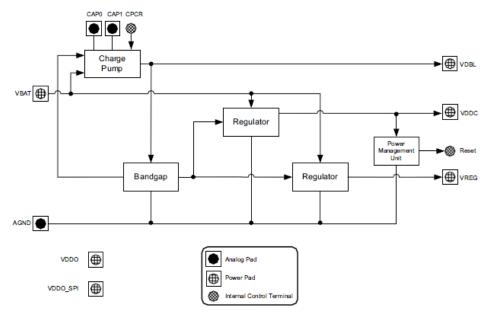

#### **Power Supply Unit**

BelaSigna 300 has multiple power sources as can be seen on Figure 13. Digital and analog sections of the chip have their own power supplies to allow exceptional audio quality.

Figure 13. Power Supply Structure

#### **Battery Supply Voltage (VBAT)**

The primary voltage supplied to a BelaSigna 300 device is VBAT. It is typically 1.8 V. BelaSigna 300 also uses VBAT to define the I/O voltage levels, as well as powering an external EEPROM on the SPI port. Consequently, any voltage below 1.8 V will result in incorrect operation of the EEPROM.

#### **Internal Band Gap Reference Voltage**

The band gap reference voltage has been stabilized over temperature and process variations. This reference voltage is used in the generation of all of the regulated voltages in the BelaSigna 300 system and provides a nominal 1 V reference signal to all components using the reference voltage.

#### Internal Digital Supply Voltage (VDDC)

The internal digital supply voltage is used as the supply voltage for all internal digital components, including being used as the interface voltage at the low side of the level translation circuitry attached to all of the external digital pads. VDDC is also provided as an output pad, where a capacitor to ground typically filters power supply noise. The VDDC internal regulator is a programmable power supply that allows the selection of the lowest digital supply depending on the clock frequency at which BelaSigna 300 will operate. In BelaSigna 300, the VDDC configuration is set by the boot ROM to its maximum value to allow for 40 MHz operation in all parts. Contact ON Semiconductor for more information regarding VDDC calibration.

#### **External Digital Supply Voltage (VDDO)**

This pin is not available on BelaSigna 300, as it is internally connected to VBAT.

#### SPI Port Digital Supply Voltage (VDDO\_SPI)

VDDO\_SPI is an externally provided power source dedicated to the SPI port. Communication with external EEPROMs will happen at the level defined on this pin. This pin is not available on the WLCSP option of BelaSigna 300, as it is internally connected to VBAT.