# 1.5 A Synchronous Buck Regulator

#### **Description**

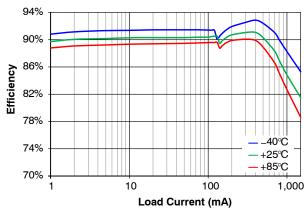

The FAN53713 is a Super Low Iq, step-down switching voltage regulator, that delivers a fixed output from an input voltage supply of 2.3 V to 5.5 V. Using a proprietary architecture with synchronous rectification, the FAN53713 is capable of delivering a peak efficiency of 93%, while maintaining efficiency over 90% at load currents as low as 1 mA.

The regulator operates with 0402 and 0603 input and output capacitors, respectively, which reduces the total solution size to 5.5 mm<sup>2</sup>. At moderate and light load, Pulse Frequency Modulation (PFM) is used to operate the device with a low quiescent current. Even with such a low quiescent current, the part exhibits excellent transient response during load swings. In Shutdown Mode, the supply current drops to 100 nA, reducing power consumption. The Mode pin allows the part to be in a Super Low IQ (SLIQ) mode with a typical quiescent current of 2 uA.

The FAN53713 is available in 6-bump, 0.4 mm pitch, Wafer-Level Chip-Scale Package (WLCSP).

#### **Features**

- 2 µA Typical Quiescent Current

- 5.5 mm<sup>2</sup> Total Solution Size

- 1.5 A Output Current Capability

- 0.6 V to 1.8 V Fixed Output Voltage

- 2.3 V to 5.5 V Input Voltage Range

- Best-in-Class Load Transient Response

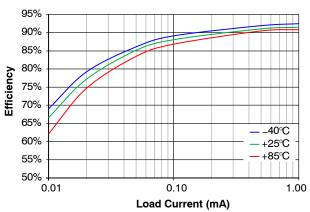

- Best-in-Class Efficiency with Sub 1 mA Output Currents

- Internal Soft-Start Limits Battery Current Below 150 mA to avoid Brown-out Scenarios

- Protection Faults (UVLO, OCP and OTP)

- Thermal Shutdown and Overload Protection

- 6-Bump WLCSP, 0.4 mm Pitch

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Applications**

- Wearables

- Smart Watch

- Health Monitoring

- Sensor Drive

- Energy Harvesting

- Utility and Safety Modules

- RF Modules

#### ON Semiconductor®

www.onsemi.com

WLCSP6 1.38 × 0.94 × 0.625 CASE 567UH

#### **MARKING DIAGRAM**

12KK XYZ

12 = Alphanumeric Device Marking

KK = Lot Run Code

X = Alphabetical Year CodeY = 2 Weeks Date CodeZ = Assembly Plant Code

# ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

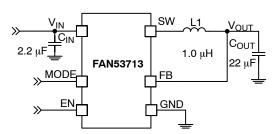

Figure 1. Typical Application

**Table 1. ORDERING INFORMATION**

| Part Number                       | Output Voltage<br>(Note 1) | Max. Output<br>Current (Note 1) | Temperature<br>Range | Package | Packing<br>Method | Device<br>Marking |

|-----------------------------------|----------------------------|---------------------------------|----------------------|---------|-------------------|-------------------|

| FAN53713UC02X                     | 0.7 V                      | 1.5 A                           | -40 to 85°C          | WLCSP   | Tape & Reel       | GJ                |

| FAN53713UC10X<br>(In Development) | 1.1 V                      | 1.5 A                           | −40 to 85°C          | WLCSP   | Tape & Reel       | LE                |

<sup>1.</sup> Other voltage and output current options are available. Contact an On Semiconductor representative.

#### **Table 2. RECOMMENDED EXTERNAL COMPONENTS**

| Component                 | Description                                     | Vendor                    | Parameter | Тур. | Unit |

|---------------------------|-------------------------------------------------|---------------------------|-----------|------|------|

| L                         | 1.0 $\mu H$ , 20%, 2.3 A, 107 m $\Omega$ , 1608 | DFE160810S-1R0M (Murata)  | L         | 1.0  | μΗ   |

| C <sub>IN</sub>           | $2.2~\mu F,  20\%,  6.3~V,  X5R,  0402$         | C1005X5R0J225M050BC (TDK) | С         | 2.2  | ⊏    |

| C <sub>OUT</sub> (Note 1) | 22 μF, 20%, 6.3 V, X5R, 0603                    | C1608X5R0J226M080AC (TDK) | С         | 22   | μ⊢   |

<sup>1.</sup> A 10  $\mu$ F, 0402 capacitor can be used to reduce total solution size at the expense of load transient performance.

# **Pin Configuration**

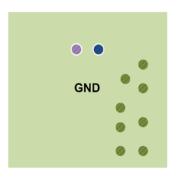

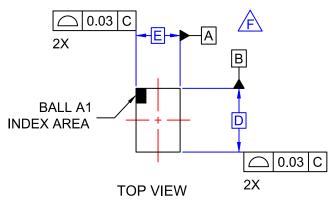

Figure 2. Top View

Figure 3. Bottom View

#### **Table 3. PIN DEFINITIONS**

| Pin # Name                                              |      | Description                                                                                                                                                                     |

|---------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 EN Enable. The device is in when >1.2 V. Do not leav |      | Enable. The device is in Shutdown Mode when voltage to this pin is <0.4 V and enabled when >1.2 V. Do not leave this pin floating. Recommended for GPIO 1.8 V to drive this pin |

| A2                                                      | VIN  | Input Voltage. Connect to input power source across C <sub>IN</sub>                                                                                                             |

| B1                                                      | MODE | MODE. Logic "LOW" allows the IC to be in a Super Low IQ (SLIQ) state. A Logic HIGH allows the part to be in normal Iq state Auto Mode                                           |

| B2                                                      | SW   | Switching Node. Connect to SW pad of inductor                                                                                                                                   |

| C1                                                      | FB   | Feedback. Connect to positive side of output capacitor                                                                                                                          |

| C2                                                      | GND  | Ground. Power and IC ground. All signals are referenced to this pin                                                                                                             |

#### **Table 4. ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                              | Min. | Max.                           | Unit |

|-------------------|----------------------------------------|------|--------------------------------|------|

| V <sub>IN</sub>   | Input Voltage                          | -0.3 | 6.5                            | V    |

| V <sub>SW</sub>   | Voltage on SW Pin                      | -0.3 | V <sub>IN</sub> + 0.3 (Note 1) | V    |

| V <sub>CTRL</sub> | EN, FB and Mode Pin Voltage            | -0.3 | V <sub>IN</sub> + 0.3 (Note 1) | V    |

| ESD               | Human Body Model per JESD22-A114       | 2    | 2.0                            |      |

|                   | Charged Device Model per JESD22-C101   |      | 1.0                            |      |

| TJ                | Junction Temperature                   | -40  | +150                           | °C   |

| T <sub>STG</sub>  | Storage Temperature                    | -40  | +150                           | °C   |

| TL                | Lead Soldering Temperature, 10 Seconds |      | +260                           | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> Lesser of 6 V or  $V_{IN}$  + 0.3 V.

**Table 5. RECOMMENDED OPERATING CONDITIONS**

| Symbol                    | Parameter                      | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------------|------|------|------|------|

| V <sub>IN</sub>           | Supply Voltage Range           | 2.3  |      | 5.5  | V    |

| lout                      | Continuous Output Current      | 0    |      | 1.5  | Α    |

|                           | Pulsed Output Current, 100 μs  | 0    |      | 1.6  | Α    |

| C <sub>IN</sub>           | Input Capacitor                |      | 2.2  |      | μF   |

| C <sub>OUT</sub> (Note 1) | Output Capacitor               | 3    |      | 100  | μF   |

| L                         | Inductor                       | 0.47 | 1.0  | 1.3  | μН   |

| T <sub>A</sub>            | Operating Ambient Temperature  | -40  |      | +85  | °C   |

| T <sub>J</sub>            | Operating Junction Temperature | -40  |      | +125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### **Table 6. THERMAL PROPERTIES**

| Symbol        | Parameter                                       | Min. | Тур. | Max. | Unit |

|---------------|-------------------------------------------------|------|------|------|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance (Note 1) |      | 125  |      | °C/W |

<sup>1.</sup> Junction-to-ambient thermal resistance is a function of application and board layout. This data is simulated with four-layer 2s2p boards with vias in accordance to JESD51- JEDEC standard. Special attention must be paid not to exceed the junction temperature.

**Table 7. ELECTRICAL CHARACTERISTICS** Minimum and Maximum Values are at  $V_{IN} = V_{EN} = 3.6$  V,  $V_{A} = -40$ °C to +85°C, unless otherwise noted. Typical values are at  $V_{A} = 25$ °C,  $V_{A} = V_{EN} = 3.6$  V,  $V_{OUT} = 1.8$  V

| Symbol                 | Parameter                       | Condition                                                                | Min. | Тур. | Max. | Unit |

|------------------------|---------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| I <sub>Q,SLIQ</sub>    | Quiescent Current               | SLIQ Mode, no load, non-switching                                        |      | 2    |      | μΑ   |

| I <sub>Q,PFM</sub>     | PFM Quiescent Current           | PFM Mode, no load, non-switching                                         |      | 5    |      | μΑ   |

| I <sub>SD</sub>        | Shutdown Supply Current         | EN=GND, V <sub>IN</sub> =3.6 V, no load                                  |      | 100  |      | nA   |

| V <sub>UVLO_RISE</sub> | Under-Voltage Lockout Threshold | V <sub>IN</sub> Rising                                                   | 2.10 | 2.15 | 2.21 | V    |

| V <sub>UVLO_FALL</sub> | ]                               | V <sub>IN</sub> Falling                                                  | 2.00 | 2.05 | 2.10 | V    |

| V <sub>IH</sub>        | HIGH-Level Input Voltage        |                                                                          | 1.2  |      |      | V    |

| V <sub>IL</sub>        | LOW-Level Input Voltage         |                                                                          |      |      | 0.4  | V    |

| I <sub>LIM</sub>       | Peak Current Limit              | V <sub>IN</sub> = 4.35 V                                                 |      | 2215 |      | mA   |

| V <sub>OACC</sub>      | Output Voltage Accuracy         | V <sub>OUT</sub> = 0.6 V to 1.8 V, I <sub>OUT(DC)</sub> = 0,<br>PWM Mode | -25  |      | +25  | mV   |

|                        |                                 | V <sub>OUT</sub> = 0.6 V to 1.8 V, I <sub>OUT(DC)</sub> = 0,<br>PFM Mode | -40  |      | +40  | mV   |

| R <sub>DS(on)</sub>    | PMOS On Resistance              | V <sub>IN</sub> = V <sub>GS</sub> = 3.6 V                                |      | 135  |      | mΩ   |

|                        | NMOS On Resistance              | V <sub>IN</sub> = V <sub>GS</sub> = 3.6 V                                |      | 95   |      | mΩ   |

| T <sub>TSD</sub>       | Thermal Shutdown                |                                                                          |      | 150  |      | °C   |

| T <sub>HYS</sub>       | Thermal Shutdown Hysteresis     |                                                                          |      | 15   |      | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

<sup>1.</sup> Effective capacitance after DC bias.

**Table 8. SYSTEM CHARACTERISTICS** The following system characteristics are guaranteed by design and are not performed in production testing. Recommended operating conditions, unless otherwise noted,  $V_{IN} = 2.3 \text{ V}$  to 5.5 V,  $T_A = -40^{\circ}\text{C}$  to +85°C,  $V_{OUT} = 1.8 \text{ V}$ . Typical values are given at  $T_A = 25^{\circ}\text{C}$ ,  $V_{IN} = 3.6 \text{ V}$ . System characteristics are based on circuit per Figure 1. L = 1.0 μH, 2.3 A, 107 mΩ DCR, DFE160810S-1R0M (Murata),  $C_{IN} = 1 \times 2.2 \,\mu\text{F}$ , 6.3 V, 0402 (1005 metric), C1005X5R0J225M050BC (TDK) and  $C_{OUT} = 1 \times 22 \,\mu\text{F}$ , 6.3 V, 0603 (1608 metric), C1608X5R0J226M080AC (TDK).

| Symbol                       | Parameter       | Condition                                                                                                                                                | Min. | Тур. | Max. | Unit               |

|------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|

| LOAD <sub>REG</sub>          | Load Regulation | I <sub>OUT</sub> = 10 μA to 1 mA, SLIQ Mode                                                                                                              |      | -9.0 |      | mV/mA              |

|                              |                 | I <sub>OUT</sub> = 200 mA to 300 mA, PWM                                                                                                                 |      | -2.0 |      | mV/A               |

| LINE <sub>REG</sub>          | Line Regulation | $3.0 \text{ V} \le V_{IN} \le 4.35 \text{ V},$<br>$I_{OUT} = 1 \text{ A, PWM}$                                                                           |      | -0.5 |      | mV/V               |

| V <sub>OUT_RIPPLE</sub>      | Ripple Voltage  | I <sub>OUT</sub> = 250 μA, SLIQ Mode                                                                                                                     |      | 40   |      | mV                 |

|                              |                 | I <sub>OUT</sub> = 20 mA, PFM Mode                                                                                                                       |      | 25   |      |                    |

|                              |                 | I <sub>OUT</sub> = 200 mA, PWM Mode                                                                                                                      |      | 5    |      |                    |

| Eff                          | Efficiency      | I <sub>OUT</sub> = 100 μA, SLIQ Mode                                                                                                                     |      | 88   |      | %                  |

|                              |                 | I <sub>OUT</sub> = 500 μA, SLIQ Mode                                                                                                                     |      | 91   |      |                    |

|                              |                 | I <sub>OUT</sub> = 1 mA, PFM Mode                                                                                                                        |      | 90   |      |                    |

|                              |                 | I <sub>OUT</sub> = 100 mA, PFM Mode                                                                                                                      |      | 91   |      |                    |

|                              |                 | I <sub>OUT</sub> = 300 mA, PWM Mode                                                                                                                      |      | 91   |      |                    |

| Eff                          | Efficiency      | I <sub>OUT</sub> = 500 mA, PWM Mode                                                                                                                      |      | 90   |      | mV/mA mV/A mV/V mV |

|                              |                 | I <sub>OUT</sub> = 700 mA, PWM Mode                                                                                                                      |      | 88   |      |                    |

| $\Delta V_{OUT\_LOAD}$       | Load Transient  | $I_{OUT}$ = 10 mA $\Leftrightarrow$ 150 mA,<br>$T_{R}$ = $T_{F}$ = 1 $\mu$ s, Auto Mode                                                                  |      | ±40  |      | mV                 |

|                              |                 | $I_{OUT}$ = 100 μA $\Leftrightarrow$ 500 μA,<br>$T_{R}$ = $T_{F}$ = 1 μs, SLIQ Mode                                                                      |      | ±15  |      | % mV mV            |

| $\Delta V_{	ext{OUT\_LINE}}$ | Line Transient  | $\begin{aligned} V_{IN} = 3.0 \text{ V} &\Leftrightarrow 3.6 \text{ V}, T_R = T_F = 10 \mu\text{s}, \\ I_{OUT} = 300 \text{ mA, PWM Mode} \end{aligned}$ |      | ±20  |      | mV                 |

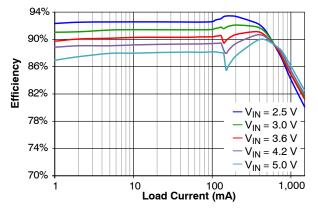

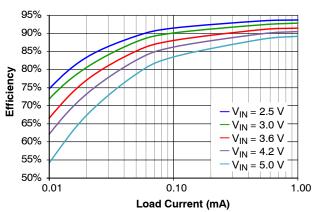

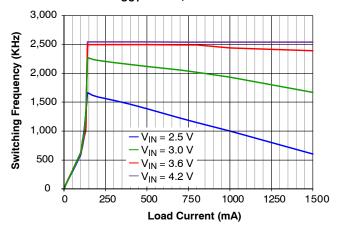

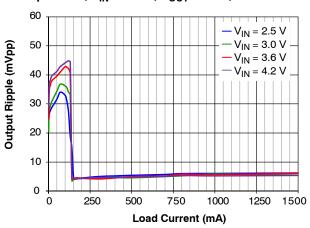

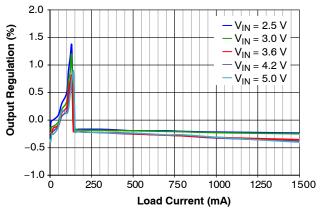

#### **Typical Characteristics**

Unless otherwise specified,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, Auto Mode,  $T_A$  = 25°C; circuit and components according to Figure 1 and Table 2.

Figure 4. Efficiency vs. Load Current and Input Voltage, V<sub>OUT</sub> = 1.8 V, Auto Mode

Figure 6. Efficiency vs. Load Current and Input Voltage,  $V_{OUT}$  = 1.8 V, SLIQ Mode

Figure 8. Frequency vs. Load Current and Input Voltage, Auto Mode, V<sub>OUT</sub> = 1.8 V, Auto Mode

Figure 5. Efficiency vs. Load Current and Temperature,  $V_{\text{IN}}$  = 3.6 V ,  $V_{\text{OUT}}$  = 1.8 V, Auto Mode

Figure 7. Efficiency vs. Load Current and Temperature,  $V_{\text{IN}}$  = 3.6 V ,  $V_{\text{OUT}}$  = 1.8 V, SLIQ Mode

Figure 9. Output Ripple vs. Load Current and Input Voltage, V<sub>OUT</sub> = 1.8 V, Auto Mode

#### Typical Characteristics (continued)

Unless otherwise specified,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, Auto Mode,  $T_A$  = 25°C; circuit and components according to Figure 1 and Table 2.

2.0 1.5 Output Regulation (%) 1.0 0.5 0.0 -0.5 -1.040°C +25°C -1.5 +85°C -2.0 1250 250 500 750 1000 1500 Load Current (mA)

Figure 10. Output Regulation vs. Load Current and Input Voltage, V<sub>OUT</sub> = 1.8 V, Auto Mode

Figure 11. Output Regulation vs. Load Current and Temperature,  $V_{IN} = 3.6 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$ , Auto Mode

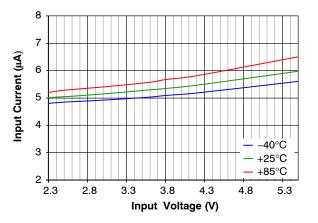

Figure 12. Quiescent Current vs. Input Voltage and Temperature, VOUT = 1.8 V, Auto Mode

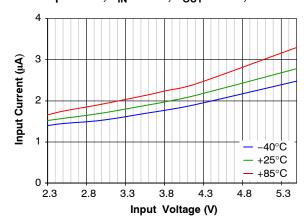

Figure 13. Quiescent Current vs. Input Voltage and Temperature, VOUT = 1.8 V, SLIQ Mode

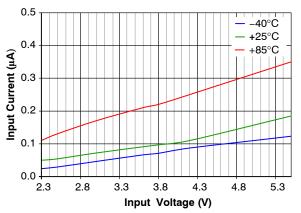

Figure 14. Shutdown Current vs. Input Voltage and Temperature

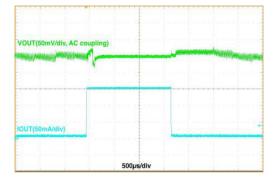

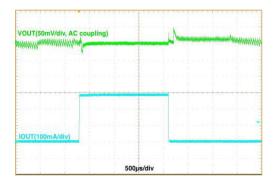

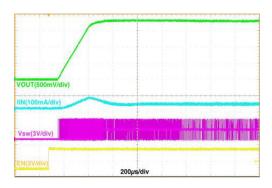

Figure 15. Load Transient,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, 10 mA  $\Leftrightarrow$ 150 mA, 1  $\mu s$  Edge, Auto Mode

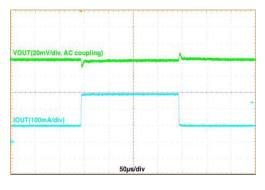

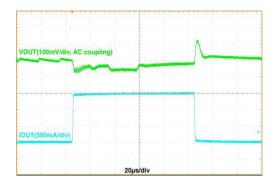

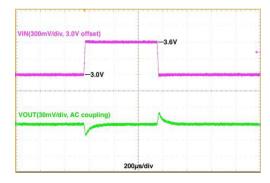

#### Typical Characteristics (continued)

Unless otherwise specified,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, Auto Mode,  $T_A$  = 25°C; circuit and components according to Figure 1 and Table 2.

Figure 16. Load Transient,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, 5 mA  $\leftrightarrow$ 300 mA, 1  $\mu s$  Edge, Auto Mode

Figure 17. Load Transient,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, 100 mA  $\leftrightarrow$ 300 mA, 1  $\mu$ s Edge, Auto Mode

Figure 18. Load Transient,  $V_{IN}$  = 3.6 V,  $V_{OUT}$  = 1.8 V, 10 mA  $\Leftrightarrow$ 1500 mA, 1  $\mu s$  Edge, Auto Mode

Figure 19. Line Transient,  $V_{IN}$  = 3.0 V  $\leftrightarrow$  3.6 V,  $V_{OUT}$  = 1.8 V, 10  $\mu s$  Edge, 300 mA Load, Auto Mode

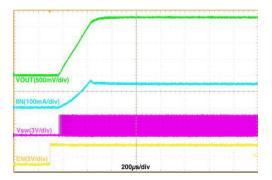

Figure 20. Start-up, V<sub>IN</sub>= 3.6 V, V<sub>OUT</sub>= 1.8 V, 50 mA Resistive Load, Auto Mode

Figure 21. Start-up, V<sub>IN</sub>= 3.6 V, V<sub>OUT</sub>= 1.8 V, 300 mA Resistive Load, Auto Mode

#### **Operation Description**

The FAN53713 is a Super Low Iq (SLIQ), step-down switching voltage regulator, typically operating at 2.5 MHz in Continuous Conduction Mode(CCM). Using a proprietary architecture with synchronous rectification, the FAN53713 is capable of delivering a peak efficiency of 93%, while maintaining efficiency over 90% at load currents sub 1mA.

In SLIQ mode the device is very efficient with load currents in the uA range. In SLIQ mode the device draws less than 2  $\mu$ A typical from the battery with no load. The load transients in SLIQ mode are best in class.

The FAN53713 provides a fixed output voltage of 0.6 V to 1.8 V and load capability of 1.5 A, which can support wearable or mobile phone applications which use Li–Ion batteries. Specialized soft–start limits the battery current to 150 mA to limit any brown out occurrences.

#### **Control Scheme**

#### **Enable and Disable**

When EN pin is Low, all circuits are off and the IC draws 100 nA current. When EN is High and  $V_{\rm IN}$  is above its UVLO threshold, the regulator begins a soft–start cycle. The FAN53713 has internal soft–start which limits the battery current draw to 150 mA. Once the part reaches 95% of  $V_{\rm OUT}$  target, the part will transition to the correct mode of operation depending on load current. The part starts up within 400  $\mu$ s typical with the recommended external components listed in Table 2.

#### **MODE Pin**

Setting Mode Pin Low sets the device in SLIQ mode; setting Mode Pin High sets the device in normal Iq Auto Mode.

#### **Protection Features**

#### **V<sub>OUT</sub>** Fault

If the  $V_{OUT}$  fails to reach 95% of  $V_{OUT}$  target within 1.8 ms during startup, a  $V_{OUT}$  fault is declared. During the fault condition the part restarts every 20 ms to achieve the 95% target voltage. Once the output voltage reaches the 95%  $V_{OUT}$  target voltage within 1.8 ms during startup, the  $V_{OUT}$  fault clears.

#### **Over-Current Protection (OCP)**

A heavy load or short circuit on the output causes the current in the inductor to increase until a maximum current threshold is reached in the high-side switch. Upon reaching

this point, the high-side switch turns off, preventing high currents from causing damage. The regulator continues to limit the current cycle-by-cycle. After 500 µs of current limit, the regulator triggers an over-current fault, causing the regulator to shut down for about 20 ms before attempting a restart.

#### Under-Voltage Lockout (UVLO)

When EN is HIGH, the under-voltage lockout keeps the part from operating until the input supply voltage rises high enough to properly operate. This ensures no misbehavior of the regulator during startup or shutdown.

#### Over-Temperature Protection (OTP)

When the die temperature increases, due to a high load condition and/or a high ambient temperature, the output switching is disabled until the die temperature falls sufficiently. The junction temperature at which the thermal shutdown activates is nominally 150°C with a 15°C hysteresis. Once the junction temperature falls below the hysteresis threshold, the regulator performs a soft–start.

#### **Modes of Operations**

## SLIQ (Super Low IQ)

In SLIQ Mode the device acts in a modified PFM mode with a super low Iq state. The part draws 2 µA with no load.

The part enters SLIQ Mode when the Mode pin is set to logic "LOW". Before pulling the Mode Pin Low, the load current should drop below 1 mA to maintain output voltage regulation in SLIQ mode. The maximum load current in SLIQ Mode that the device can support is 1 mA. If load current exceeds 1 mA, it is recommended to place part in Auto Mode by pulling Mode pin High so that the device can support more current.

The part can support more than 1 mA in SLIQ Mode if the output capacitor is increased.

#### PFM

At light load operation in Auto Mode, the device enters PFM mode when load current is below 100 mA typically. PFM mode reduces switching frequency as well as battery current draw, which yields high efficiency.

When Mode pin goes High, the part will transition from SLIQ Mode into normal PFM mode within 10 µs, typically.

#### **PWM**

When load is high, the part transitions smoothly from PFM mode to PWM mode. The part enters PWM mode when load current exceeds 132 mA, typically.

#### **Applications Information**

#### Selecting the Inductor

The output inductor must meet both the required inductance and the energy-handling capability of the application. The inductor value affects average current limit, output voltage ripple, and efficiency.

The ripple current ( $\Delta I$ ) of the regulator is:

$$\Delta I \approx \frac{V_{OUT}}{V_{IN}} \times \left(\frac{V_{IN} - V_{OUT}}{L \times f_{SW}}\right)$$

(eq. 1)

The maximum average load current,  $I_{MAX(LOAD)}$ , is related to the peak current limit,  $I_{LIM(PK)}$ , by the ripple current, given by:

$$I_{MAX(LOAD)} = I_{LIM(PK)} - \frac{\Delta I}{2}$$

(eq. 2)

The transition between PFM and PWM operation is determined by the point at which the inductor valley current crosses zero. The regulator DC current when the inductor current crosses zero,  $I_{DCM}$ , is:

$$I_{DCM} = \frac{\Delta I}{2}$$

(eq. 3)

The FAN53713 is optimized for operation with  $L = 1.0 \,\mu\text{H}$ , but is stable with inductances up to 1.3 H (nominal). The inductor should be rated to maintain at least 80% of its value at  $I_{LIM(PK)}$ .

Efficiency is affected by the inductor DCR and inductance value. Decreasing the inductor value for a given physical size typically decreases the DCR; but because  $\Delta I$  increases, the RMS current increases, as do the core and skin effect losses.

$$I_{RMS} = \sqrt{I_{OUT(DC)}^2} + \frac{\Delta I^2}{12}$$

(eq. 4)

The increased RMS current produces higher losses through the  $R_{\rm DS(ON)}$  of the IC MOSFETs, as well as the inductor DCR.

Increasing the inductor value produces lower RMS currents, but degrades transient response. For a given

physical inductor size, increased inductance usually results in an inductor with lower saturation current and higher DCR.

Table 3 shows the effects of inductance higher or lower than the recommended 1.0  $\mu H$  on regulator performance.

#### **Output Capacitor**

Increasing  $C_{OUT}$  has no effect on loop stability and can therefore be increased to reduce output voltage ripple or to improve transient response. Vice versa, lower  $C_{OUT}$  can be used but with a compromise of load transient response. Output voltage ripple,  $\Delta V_{OUT}$ , is:

$$\Delta V_{OUT} = \Delta I_L \Bigg[ \frac{f_{SW} \times C_{OUT} \times ESR^2}{2 \times D \times (1 - D)} + \frac{1}{8 \times F_{SW} \times C_{OUT}} \Bigg] (\text{eq. 5})$$

#### **Input Capacitor**

The 2.2  $\mu$ F ceramic input capacitor should be placed as close as possible between the VIN pin and GND to minimize the parasitic inductance. If a long wire is used to bring power to the IC, additional "bulk" capacitance (electrolytic or tantalum) should be placed between  $C_{IN}$  and the power source lead to reduce the ringing that can occur between the inductance of the power source leads and  $C_{IN}$ .

The effective capacitance value decreases as  $V_{IN}$  increases due to DC bias effects.

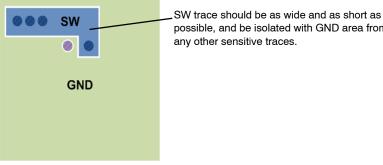

## **PCB Layout Guidelines**

- The input capacitor (C<sub>IN</sub>) should be connected as close as possible to the VIN and GND pins Connect to VIN and GND using only top metal.

Do not route through vias (see Figure 22)

- 2. Place the inductor (L) as close as possible to the IC. Use short wide traces for the main current paths

- An output capacitor (C<sub>OUT</sub>) should be placed as close as possible to the IC. Connection to GND should only be on top metal. Feedback signal connection to VOUT should be routed away from noisy components and traces (e.g. SW line)

Table 9. EFFECTS OF CHANGES in Inductor Value (from 1.0 mH Recommended Value) on Regulator Performance

|                |                        | I                 |                    |

|----------------|------------------------|-------------------|--------------------|

| Inductor Value | I <sub>MAX(LOAD)</sub> | ΔV <sub>OUT</sub> | Transient Response |

| Increase       | Increase               | Decrease          | Degraded           |

| Decrease       | Decrease               | Increase          | Improved           |

Connect V<sub>IN</sub> pin and C<sub>IN</sub> using only top metal. NODE L (FB) Connect  $C_{\mbox{\scriptsize OUT}}$  and GND pin only on top layer GND **VOUT** Put as many as possible vias connected to COUT ground plane (Layer 2), to help dissipate heat. Connect GND vias to system ground

VOUT trace should be as wide and as short as possible, for low impedance, also should be routed away from noisy components and traces (e.g. SW line)

> The ground area should be made as large as possible to help dissipate heat

Figure 22. Top Layer

Layer 2 should be a solid ground layer, to shield VOUT from capacitive coupling of the fast edges of SW node.

Logic signals can be routed on this layer.

Figure 23. Layer 1

possible, and be isolated with GND area from any other sensitive traces.

Figure 24. Layer 3

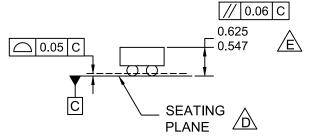

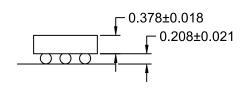

#### WLCSP6 1.38x0.94x0.625 CASE 567UH ISSUE O

**DATE 31 APR 2017**

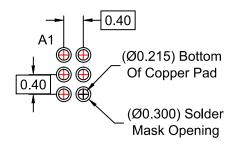

RECOMMENDED LAND PATTERN (NSMD PAD TYPE)

SIDE VIEWS

#

# **NOTES**

- A. NO JEDEC REGISTRATION APPLIES.

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCE PER  $_{\wedge}$  ASME Y14.5M, 2009.

- D. DATUM C IS DEFINED BY THE SPHERICAL CROWNS OF THE BALLS.

- E. PACKAGE NOMINAL HEIGHT IS

586 ± 39 MICRONS (547-625 MICRONS).

FOR DIMENSIONS D,E,X, AND Y SEE PRODUCT DATASHEET.

| DOCUMENT NUMBER: | 98AON13465G            | Electronic versions are uncontrolled except when accessed directly from the Document Rep<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | WLCSP6 1.38x0.94x0.625 |                                                                                                                                                                             | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales