# Secondary Side Synchronous Rectifier Controller for Flyback Converters

#### Description

The FAN6241M6X is a secondary-side synchronous rectifier (SR) controller for an isolated flyback converter operating in Discontinuous Conduction Mode (DCM). The adaptive dead-time control algorithm minimizes the body diode conduction of SR MOSFET while guaranteeing stable and robust SR operation against noise and disturbance caused by the circuit parasitic components. The 26 V rated input voltage LDO and Low VDD Under-Voltage Lockout (UVLO) voltage allow FAN6241M6X to be used for wide ranges of switched mode power supply output voltage without additional circuit.

#### **Features**

- Support Discontinuous Conduction Modes (DCM) and Boundary Conduction Mode (BCM)

- Adaptive Turn-off Dead Time Tuning for General SR MOSFET Application

- 120 V of Voltage Rating on the Drain Pin

- Charge Pump (CP) Function which Enhance SR MOSFET Voltage

Driving Level through Connected a Ceramic Capacitor between Gate

and CP Pin

- Short Turn-on Delay (20 ns)

- Supporting PD General Output Voltage (VIN) Range: 3.25 V~25 V with LDO Input

- Fewest External Component Allowed

- At Green mode SR Driving Signal is Still Working under Extremely Low Power Consumption

- Small Footprint: SOT-23 6 pin

- These Device is Pb-Free and is RoHS Compliant

#### **Typical Applications**

- Travel Adapter for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices that Require CV/CC Control

1

• IoT Power Applications5tt

# ON Semiconductor®

www.onsemi.com

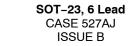

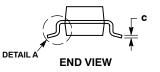

SOT-23, 6 Lead CASE 527AJ

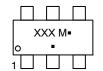

#### MARKING DIAGRAM

FAN6241 = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

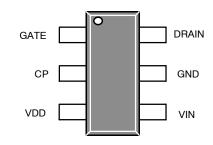

# PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

# **ORDERING INFORMATION**

| Part Number | Operating Temperature | Package                 | Packing Method    |

|-------------|-----------------------|-------------------------|-------------------|

| FAN6241M6X  | −40°C ~125°C          | 6-Lead, SOT23 (Pb-Free) | 3000 / Tap & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

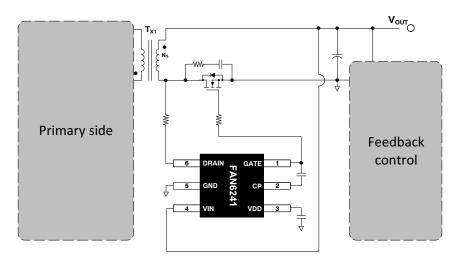

Figure 1. FAN6241M6X Typical Application Schematic

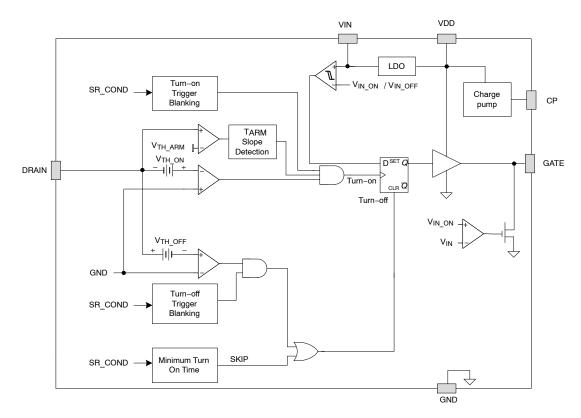

Figure 2. FAN6241M6X Function Block Diagram

# **PIN FUNCTION DESCRIPTION**

| Pin #                                           | Name | Description                                                                                                                                        |

|-------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                               | GATE | Gate drive output pin                                                                                                                              |

| 2                                               | CP   | SR gate charge pump. connect one 3.3 nF capacitor to GATE pin                                                                                      |

| 3                                               | VDD  | Internal regulator 5 V output and gate drive power supply rail. Bypass with 1 μF capacitor to GND                                                  |

| 4                                               | VIN  | LDO input, supports up to 26 V operation. An integrated 5 V LDO generates the internal VDD power supply rail for the low–voltage control circuitry |

| 5 GND Ground pin                                |      | Ground pin                                                                                                                                         |

| 6 DRAIN Synchronous rectifier drain sense input |      | Synchronous rectifier drain sense input                                                                                                            |

# ABSOLUTE MAXIMUM RATINGS (Notes 1, 2, 3)

| Parameter                          | Symbol                                            | Min. | Max.  | Unit |

|------------------------------------|---------------------------------------------------|------|-------|------|

| V <sub>IN</sub>                    | Power Supply Input Pin Voltage -0.3               |      | 26    | V    |

| V <sub>DD</sub>                    | Internal Regulator Output Pin Voltage             | -0.3 | 6.5 V | V    |

| V <sub>DRAIN</sub>                 | Drain Sense Input Pin Voltage                     | -1   | 120   | V    |

| $V_{GATE}$                         | Gate Drive Output Pin Voltage                     | -0.3 | 6.5 V | ٧    |

| СР                                 | Charge pump Pin Voltage -0.3                      |      | 6.5 V | V    |

| P <sub>D</sub>                     | Power Dissipation (T <sub>A</sub> = 25°C)         |      | 540   | mW   |

| $\theta_{\sf JA}$                  | Thermal Resistance (Junction-to-Ambient Thermal)  |      | 230   | °C/W |

| TJ                                 | Operating Junction Temperature                    | -40  | 125   | °C   |

| T <sub>STG</sub>                   | Storage Temperature Range                         | -60  | 150   | °C   |

| TL                                 | Lead Temperature (Soldering) 10 Seconds           |      | 260   | °C   |

| Electrostatic Discharge Capability | Human Body Model, ANSI / ESDA / JEDEC JS-001-2012 |      | 2.0   | kV   |

|                                    | Charged Device Model, JESD22-C101                 |      | 0.5   |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. All voltage values, except differential voltages, are given with respect to the GND pin.

2. Stresses beyond these listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 3. Meets JEDEC standards JS-001-2012 and JESD 22-C101.

# THERMAL CHARACTERISTICS (Note 4)

| Parameter                             | Symbol            | Min | Unit |

|---------------------------------------|-------------------|-----|------|

| Junction-to-Ambient Thermal Impedance | $\theta_{\sf JA}$ | 230 | °C/W |

| Junction-to-Top Thermal Impedance     | $\theta_{JT}$     | 36  | °C/W |

<sup>4.</sup>  $T_A = 25^{\circ}C$  unless otherwise specified.

# **RECOMMENDED OPERATING RANGES** (Note 5)

| Parameter                             | Symbol          | Min. | Max. | Unit |

|---------------------------------------|-----------------|------|------|------|

| Power Supply Input Pin Voltage        | $V_{VIN}$       | 2.8  | 20   | V    |

| Internal Regulator Output Pin Voltage | $V_{VDD}$       | 2.8  | 6    | V    |

| Drain Sense Input Pin Voltage         | $V_{DRAIN}$     | -0.3 | 100  | V    |

| Gate Drive Output Pin Voltage         | $V_{GATE}$      | -0.3 | 6    | V    |

| Charge pump Pin voltage               | V <sub>CP</sub> | 0    | 5.5  | V    |

#### ELECTRICAL CHARACTERISTICS V<sub>IN</sub> = 5.5 V and T<sub>A</sub> = -40~125°C unless noted

| Parameter                               | Conditions                                                                      | Symbol                           | Min. | Тур.  | Max.  | Unit |

|-----------------------------------------|---------------------------------------------------------------------------------|----------------------------------|------|-------|-------|------|

| VDD SECTION                             |                                                                                 |                                  |      |       |       |      |

| Turn-On Threshold                       | V <sub>IN</sub> rising                                                          | V <sub>IN-ON</sub>               | 3.06 | 3.38  | 3.70  | V    |

| Turn-Off Threshold                      | V <sub>IN</sub> falling                                                         | V <sub>IN-OFF</sub>              | 2.78 | 2.915 | 3.050 | V    |

| Operating Current                       | $f_{SW}$ = 100 kHz, $C_{iss}$ = 3.3 nF, $V_{IN}$ = 5 V                          | I <sub>IN-OP</sub>               | -    | 2.0   | 3.5   | mA   |

| Operating Current at green mode         | $f_{SW} = 100 \text{ Hz}, C_{iss} = 3.3 \text{ nF}, V_{IN} = 5 \text{ V}$       | I <sub>IN-GREEN</sub>            | -    | 250   | 350   | μΑ   |

| POWER SUPPLY SECTION                    |                                                                                 |                                  |      |       |       |      |

| Internal LDO Output Voltage             | V <sub>IN</sub> = 20 V                                                          | $V_{DD}$                         | 5.10 | 5.35  | 5.60  | V    |

| Dropout Voltage of LDO                  | I <sub>OUT</sub> = 10 mA, V <sub>IN</sub> = 3.3 V                               | V <sub>DO</sub>                  | -    | -     | 0.3   | V    |

| DRAIN VOLTAGE SENSING SI                | ECTION                                                                          |                                  |      |       |       |      |

| Comparator Input Offset<br>Voltage      | Internal design suggestion                                                      | V <sub>OSI</sub> (Note 6)        | -1   | 0     | 1     | mV   |

| Turn-On Threshold Voltage               | $R_{DRAIN} = 0 \Omega$ (includes comparator input offset voltage)               | V <sub>TH-ON</sub>               | -250 | -200  | -150  | mV   |

| Turn-Off Threshold Tuning<br>Range      | 15 Steps                                                                        | V <sub>TH-OFF</sub>              | -5   | -     | 5     | mV   |

| Turn-On Delay                           | With 50 mV overdrive<br>From V <sub>TH-ON</sub> to V <sub>GATE</sub> = 1 V      | t <sub>ON.DLY</sub><br>(Note 6)  | -    | 20    | -     | ns   |

| Turn-Off Delay                          | With 0 mV overdrive From V <sub>TH-OFF</sub> to V <sub>GATE</sub> voltage = 1 V | t <sub>OFF-DLY</sub><br>(Note 6) | -    | 20    | -     | ns   |

| Slope detection disable criteria        |                                                                                 | t <sub>SLO-DIS</sub>             | -    | 100   | -     | μs   |

| Gate Re-arming threshold                | V <sub>IN</sub> = 5 V (Typically 0.65V <sub>DD</sub> )                          | V <sub>TH-ARM</sub>              | 3.00 | 3.25  | 3.50  | V    |

| Gate Re-arming time for slope detection |                                                                                 | t <sub>ARM</sub> (Note 6)        | 75   | 90    | 105   | ns   |

| Slope detection high threshold          |                                                                                 | V <sub>TH-HGH</sub><br>(Note 6)  | 0.4  | 0.5   | 0.6   | V    |

| MINIMUM ON-TIME AND MINI                | MUM OFF-TIME SECTION                                                            |                                  |      |       |       |      |

| Adaptive Minimum On-Time<br>Ratio       | Ratio between minimum on time and SR conduction of previous switching cycle     | K <sub>TON</sub> (Note 6)        | -    | 50    | -     | %    |

| Minimum On-Time low value               |                                                                                 | t <sub>ON-MIN-LL</sub>           | 300  | 450   | 600   | ns   |

| Minimum On-Time High value              |                                                                                 | t <sub>ON-MIN-UL</sub>           | 1    | 2     | 3     | μs   |

| Minimum Off-Time                        |                                                                                 | t <sub>OFF-MIN</sub>             | 1.0  | 1.2   | 1.4   | μs   |

| DEAD TIME CONTROL SECTION               | ON                                                                              |                                  |      |       |       |      |

| Dead time self-tuning target            | From GATE OFF to V <sub>DRAIN</sub> rising above 0.5 V                          | t <sub>DEAD</sub> (Note 6)       | 150  | 200   | 230   | ns   |

|                                         |                                                                                 |                                  |      |       |       |      |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

5. The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. On Semiconductor does not recommend exceeding them or designing to Absolute Maximum Ratings.

# **ELECTRICAL CHARACTERISTICS** $V_{IN} = 5.5 \ V$ and $T_A = -40 \sim 125 ^{\circ} C$ unless noted

| Parameter                             | Conditions                                                                          | Symbol                     | Min.  | Тур.  | Max.  | Unit   |  |

|---------------------------------------|-------------------------------------------------------------------------------------|----------------------------|-------|-------|-------|--------|--|

| GREEN MODE CONTROL                    |                                                                                     |                            |       |       |       |        |  |

| Gate Period of enter green mode       |                                                                                     | t <sub>GREEN-ON</sub>      | 240   | 300   | 360   | μs     |  |

| Gate period of leave green mode –min  |                                                                                     | t <sub>GREEN-OFF-min</sub> | 80    | 100   | 120   | μs     |  |

| Gate period of leave green mode –max  |                                                                                     | t <sub>GREEN-OFF-max</sub> | 120   | 150   | 180   | μs     |  |

| Gate cycle of leave green mode        | ts< tGREEN-OFF-min                                                                  | N <sub>GREEN-OFF</sub>     | -     | 32    | -     | Cycles |  |

| OUTPUT DRIVER SECTION                 |                                                                                     |                            |       |       |       |        |  |

| Output Voltage Low                    | V <sub>IN</sub> = 6 V                                                               | V <sub>OL</sub>            | _     | _     | 0.25  | V      |  |

| Output Voltage High                   | V <sub>IN</sub> = 6 V                                                               | V <sub>OH</sub>            | 5.0   | 5.5   | 6.0   | ٧      |  |

| Rise Time                             | $V_{IN} = 5 \text{ V}, C_L = 3300 \text{ pF, GATE} = 1 \text{ V} \sim 4 \text{ V}$  | t <sub>R</sub>             | -     | -     | 24    | ns     |  |

| Fall Time                             | $V_{IN} = 5 \text{ V}, C_L = 3300 \text{ pF, GATE} = 4 \text{ V} \sim 1 \text{ V}$  | t <sub>F</sub>             | -     | -     | 21    | ns     |  |

| Gate voltage during charge pump       | V <sub>IN</sub> = 3.3 V, C <sub>LOAD</sub> = 3300 pF,<br>Ciss = 4.7 ns, fs = 100 Hz | V <sub>GATE-CP</sub>       | 4.0   | 5.0   | 6.0   | V      |  |

| Gate clamping level before IC turn on | V <sub>IN</sub> < V <sub>IN</sub> ON, C <sub>LOAD</sub> = 3300 pF                   | V <sub>0V-CLAMP</sub>      | -     | -     | 0.5   | V      |  |

| CP function enable level              | High to low enable level                                                            | V <sub>CP-EN</sub>         | 4.30  | 4.45  | 4.60  | V      |  |

| CP function disable level             | Low to high disable level                                                           | V <sub>CP-DIS</sub>        | 4.610 | 4.755 | 4.900 | V      |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

6. Guaranteed by Design.

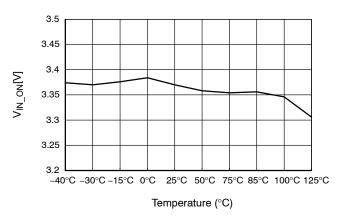

# TYPICAL PERFORMANCE CHARACTERISTICS

9

8 7 6 5 4 3 -40°C -30°C-15°C 0°C 25°C 50°C 75°C 85°C 100°C125°C Temperature (°C)

Figure 3.  $V_{\text{IN\_ON}}$  vs. Temperature

Figure 4. t<sub>F</sub> vs. Temperature

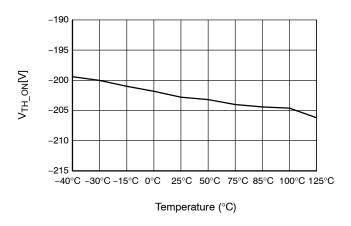

Figure 5.  $V_{TH\ ON}$  vs. Temperature

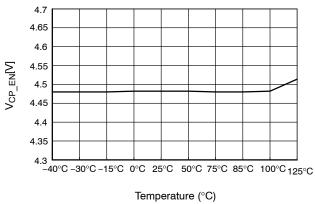

Figure 6. V<sub>CP\_EN</sub> vs. Temperature

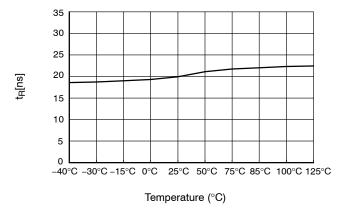

Figure 7.  $t_R$  vs. Temperature

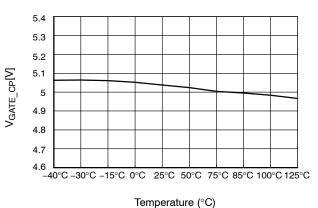

Figure 8.  $V_{GATE\ CP}$  vs. Temperature

#### **FUNCTIONAL DESCRIPTION**

#### **Theory of SR Control Operation**

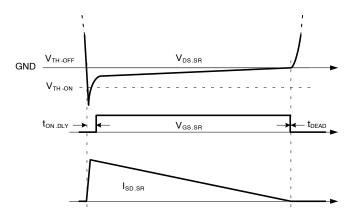

For an ideal circuit operation, the SR control algorithm of FAN6241M6X is very straightforward. FAN6241M6X controls the SR MOSFET based on the instantaneous Drain–to–Source voltage as illustrated in Figure 9. When the body diode starts conducting, the drain–to–source voltage drops below the turn–on threshold ( $V_{TH-ON}$ ) which triggers the turn–on of the gate. Then the product of  $R_{DS-ON}$

and instantaneous SR current determines the Drain-to-Source voltage. When the drain-to-source voltage reaches the turn-off threshold ( $V_{TH-OFF}$ ) as SR MOSFET current decreases to near zero, FAN6241M6X turns off the gate. If the turn off threshold ( $V_{TH-OFF}$ ) is 0 V and no stray inductance from MOSFET package and PCB layout, there is no dead time which is an ideal case.

Figure 9. SR MOSFET Operation Waveforms (Ideal Case)

# SR Turn-On Algorithm

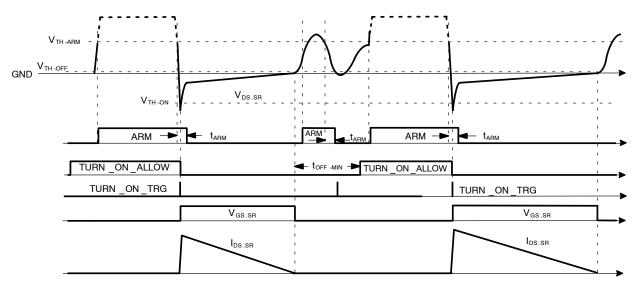

As the diagram shown in Figure 10, the turn-on of SR GATE is triggered by the three input signals of AND gate. The first input signal is TURN\_ON\_ALLOW signal, which is given after  $t_{\rm OFF-MIN}$  from the falling edge of  $V_{\rm GS.SR}$  signal. The second input is the TURN\_ON\_TRG signal,

which is enable after DRAIN pin voltage drops below  $V_{TH-ON}$ . The third signal is  $t_{ARM}$  which allows turn-on trigger only when SR drain voltage drops fast with a large slope, preventing SR from triggering by the drain resonance voltage in DCM operation.

Figure 10. Turn-On Algorithm

#### SR Turn-Off Algorithm

As diagram shown in Figure 11, the turn-off of SR GATE is triggered by the two input signals of AND gate. The first input signal is turn off signal, which is enabled when V<sub>DS.SR</sub>>V<sub>TH\_OFF</sub>. The second input is TURN OFF ALLOW signal given from the adaptive

turn-off blanking. The blanking time is adaptively determined as half of SR conduction time (SR\_COND) of the previous switching cycle for better noise immunity.  $V_{TH\_OFF}$  is automatically adjusted based on the dead time to minimize the conduction time of the body diode of SR FFT

Figure 11. SR Turn-Off Algorithm

#### **Dead Time Tuning**

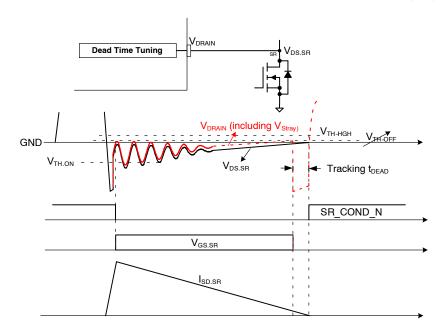

When the drain-to-source voltage reaches the turn-off threshold ( $V_{TH-OFF}$ ) as SR MOSFET current decreases to near zero, FAN6241M6X turns off the gate. However, usually there also exists voltage offset induced by the stray inductance of MOSFET package and PCB layout. Therefore, it is very difficult to optimize dead time against all the circuit tolerances and operating conditions.

FAN6241M6X implements dead time self–tuning control block in Figure 12. FAN6241M6X tries to optimize dead time to 190 ns(typ.) by modulating the  $V_{TH-OFF}$  level. The  $V_{TH-OFF}$  adjustment range is from – 5 mV to +5 mV with 4 bits resolution. Each step of  $V_{TH-OFF}$  adjustment is 0.156 mV per bit. FAN6241M6X optimizes the dead time by increasing  $V_{TH-OFF}$  step by step until  $T_{DEAD}$  is shorter than targeting dead time 200 ns(typ.).

Figure 12. SR Dead Time Tracking

#### **Charge Pump**

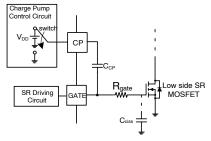

Generally, SR driving voltage is powered by  $V_{DD}$  through VIN to drive SR MOSFET through GATE pin so the GATE driving voltage be higher than VIN. When VIN is low, FET is not fully turned on, high conduction loss is inevitable and suffers total system efficiency. In order to achieve system high efficiency and low MOSFET thermal performance at low system output voltage (low VIN) with high output current application case, GATE voltage boosting function is introduced as Figure 13.

Figure 13. Charge Pump Control Circuit

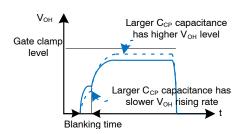

Non-logic MOSFET, that have conventional gate on threshold, is around 4 V(max) of gate threshold voltage. FAN6241M6X's internal charge pump works as Figure 14 to raise gate voltage, VOH. During blanking time the switch inside Charge Pump Control Circuit will switch to GND in order to have CCP charge via SR Driving Circuit. After blanking time, the switch will connect to V<sub>DD</sub> to boost V<sub>OH</sub>. The  $V_{OH}$  will be clamped to 5.5 V(typ.) to ensure the voltage no higher than pin maximum rating to ensure driving circuit safe operation. An adequate C<sub>CP</sub> capacitance is required to achieve reasonable GATE drive voltage for different SR MOSFET selection. While C<sub>CP</sub> capacitance is larger, the higher is VOH voltage that will have smaller MOSFET R<sub>ds-on</sub>. However, charging current from SR Driving Circuit takes longer time to charge Cciss and CCP. In the end of blanking time larger C<sub>CP</sub> has higher V<sub>OH</sub> level but slower V<sub>OH</sub> rising rate to late turn on MOSFET. R<sub>gate</sub> used for EMI solution also will reduce SR Driving Circuit charging current to slow down V<sub>OH</sub> rising rate as well.

Figure 14. Timing Flow of Charge Pump

Below summarize all kinds of  $C_{CP}$  and  $R_{gate}$  combination results which needs to trade off for EMI and efficiency

- C<sub>CP</sub> capacitance increase→ Slower V<sub>OH</sub> rising rate but greater V<sub>OH</sub>

- C<sub>CP</sub> capacitance decrease→ Faster V<sub>OH</sub> rising rate but less V<sub>OH</sub>

- R<sub>gate</sub> increase → Slower V<sub>OH</sub> rising rate and lower V<sub>OH</sub> with better EMI

- R<sub>gate</sub> decrease → Faster V<sub>OH</sub> rising rate and higher V<sub>OH</sub> but poor EMI

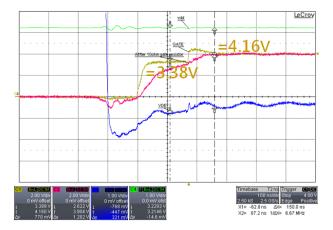

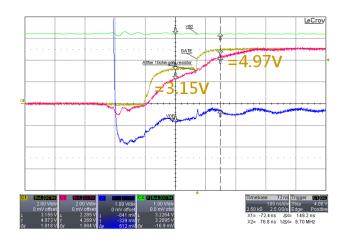

As real test Figure 15 and Figure 16 using  $C_{CP}=2.2~nF$  and 10 nF are half and double size of  $C_{ciss}=5.32~nF$  (typ.) of MOSFET NVMFS6B03NL respectively with 10  $\Omega$  R<sub>gate</sub>. At 3.3 V V<sub>BUS</sub> which is the minimum output voltage for example, the V<sub>OH</sub> is 4.16 V and 4.97 V with  $C_{CP}=2.2~nF$  and 10 nF respectively that allow user to use non–logic MOSFET for to achieve cost effective.

Figure 15. V<sub>OH</sub> Level with C<sub>CP</sub> = 2.2 nF (ch1: GATE pin; ch2: MOSFET Vgs; ch3: V<sub>RAIN</sub>: ch4: VDD)

Figure 16.  $V_{OH}$  Level with  $C_{CP}$  = 10 nF (ch1: GATE pin; ch2: MOSFET Vgs; ch3: VRAIN: ch4: VDD)

#### **PCB LAYOUT GUIDANCE**

# Printed Circuit Board (PCB) Layout

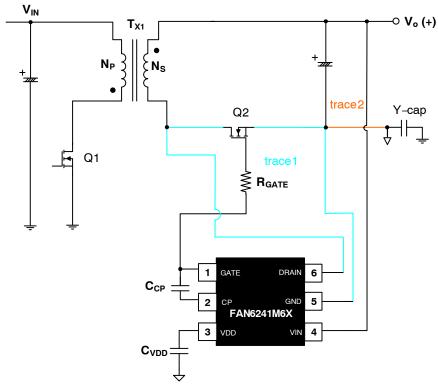

Better PCB layout improves and minimizes excessive EMI and prevents power supply from being disrupted during ESD/Surge test. Figure 17 shows the layout guidance for low-side system

#### IC Side:

• Due to VDS direct sensing method, trace1 (light blue) should be as short as possible to have better noise immunity

• GND pin is also to be routed close to the source of SR FET Q2, with short routings

#### System Side:

Y-cap is connected to output cap directly as trace2 (orange)

Figure 17. SR Layout Considerations of Low-Side System

**DATE 29 FEB 2012**

- ASIES.

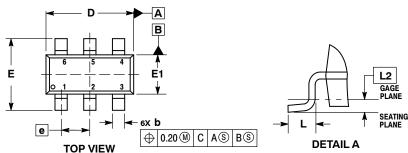

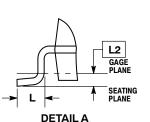

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DATUM C IS THE SEATING PLANE.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   |             | 1.45 |  |

| A1  | 0.00        | 0.15 |  |

| A2  | 0.90        | 1.30 |  |

| b   | 0.20        | 0.50 |  |

| C   | 0.08        | 0.26 |  |

| D   | 2.70        | 3.00 |  |

| Е   | 2.50        | 3.10 |  |

| E1  | 1.30        | 1.80 |  |

| е   | 0.95 BSC    |      |  |

| L   | 0.20 0.60   |      |  |

| L2  | 0.25 BSC    |      |  |

# **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code

Μ = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " •", may or may not be present.

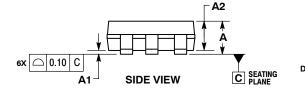

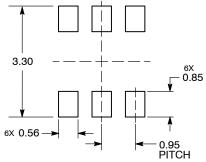

#### **RECOMMENDED** SOLDERING FOOTPRINT\*

DIMENSIONS: MILLIMETERS

| DOCUMENT NUMBER: | OCUMENT NUMBER: 98AON34321E Electronic versions are uncontrolled except when accessed directly Printed versions are uncontrolled except when stamped "CONTROL |  |             |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:     | SOT-23, 6 LEAD                                                                                                                                                |  | PAGE 1 OF 1 |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales