# JN Semiconductor®

To kara more about Old Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

May 2024

# FAN73611\_OP Single-Channel High-Side Gate Drive IC

#### **Features**

- Floating Channel for Bootstrap Operation to +600V

- 250 mA/500 mA Sourcing/Sinking Current Driving Capability

- Common-Mode dv/dt Noise-Canceling Circuit

- 3.3 V and 5 V Input Logic Compatible

- Output In Phase with Input Signal

- Under-Voltage Lockout for V<sub>DD</sub> and V<sub>BS</sub>

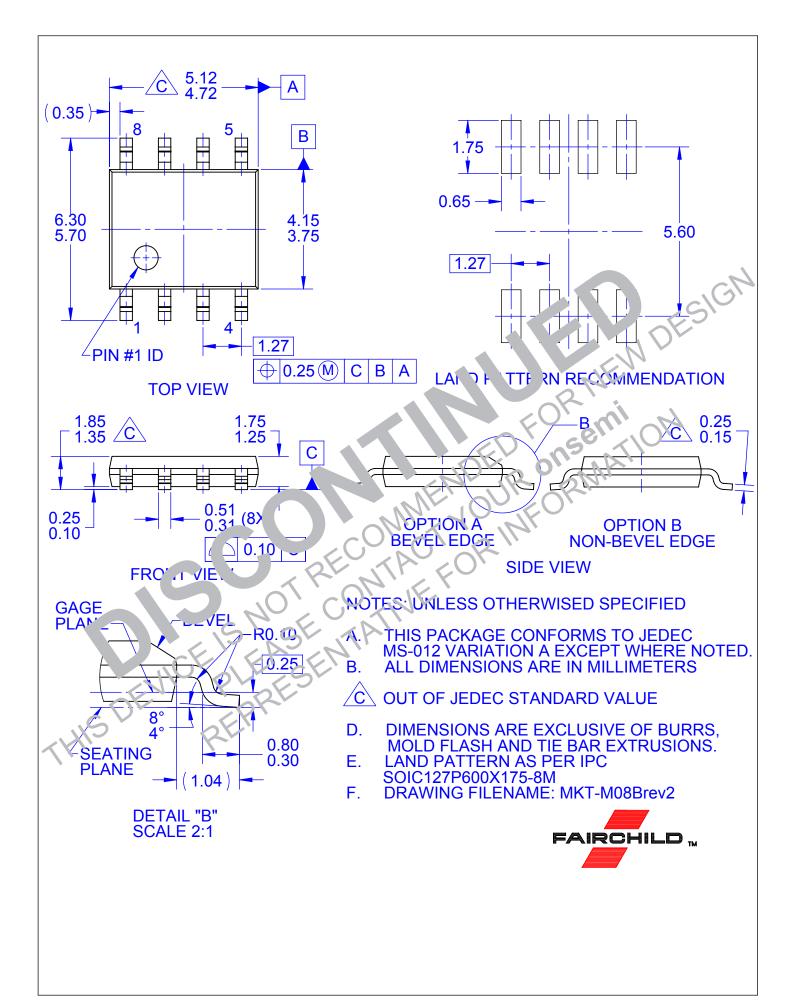

- 8-Lead Small Outline Package (SOP)

The FAN73611\_OP is a monolithic bigh-side gate drive IC that can drive MOSFETs and serating up to +600 V. Fairchild's high-voltage rocess and common mode noise canceling to iniques rovid stable operation of the high-side driver in high additional recurrent stances. An advantable in-shift incuit offers high-side gate driver peraticular  $V_S=-9.2$  (typical) for  $V_{BS}=15$ . The VLO coults prevents malfunction when  $V_{DC}$  or  $V_{BS}=10$ . The the specified threshold voltage. The rest typically source/sink 250 mA/500 mA; the vely, such is suitable for Plasma Display Panel (Fig. 2) a plication, motor drive invertex, and switching mode power supply applications.

### **Applications**

- PDP Scan Driver

- Motor Driver

- Switching-Mode Power July ( MPS)

# Related A plic ton Jtes

- AN 6076 Design .d Application Guide of Boostrar,

\_ircu. `or i oh-voitage Cate Drive IC

- N-905 Design Guide for Selection of Bootstrap

- AN 3102 Recommendations to Avoid Snort Pulse Width Issues in HVIC Cate Driver Applications

### Description

# Ordering Information

| Part Number                  | Package | Operating Temperature | Packing Method | Description         |

|------------------------------|---------|-----------------------|----------------|---------------------|

| FAN73611MX_OP <sup>(1)</sup> | 8 SOP   | -40°C ~ 125°C         | Tape & Reel    | General Application |

#### Note:

1. This device passed wave soldering test by JESD22A-111.

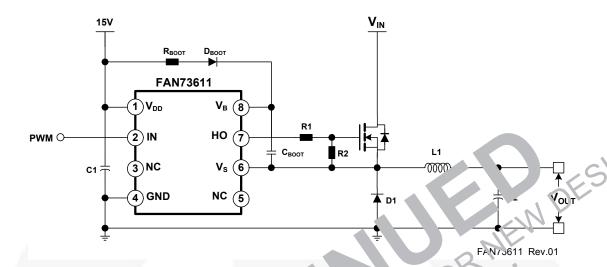

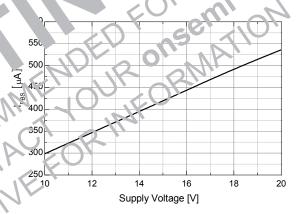

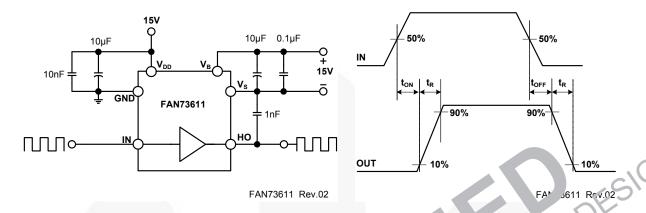

### **Typical Application Diagrams**

Figure 1. Step-Down (Buc) Control Verter Application

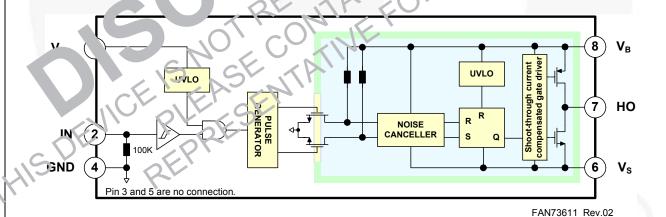

### Internal Block Diagn

Figure 2. Functional Block Diagram

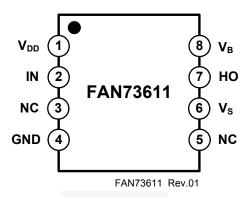

# **Pin Configuration**

Figure 3. Pin Configuration (Top View)

### **Pin Definitions**

| Pin # | Name            | Description                             |

|-------|-----------------|-----------------------------------------|

| 1     | V <sub>DD</sub> | Supply Vulage                           |

| 2     | IN              | Log mut i High-to Je Gate Driver Output |

| 3     | NC              | Co 'ecuc                                |

| 4     | GND             | Grc d                                   |

| 5     |                 | No unnection                            |

| 6     | V <sub>S</sub>  | піgh-Voltage Floatir g Supply Retu 1    |

| 7     |                 | High-Side Driver Cutput                 |

| 8     | V <sub>B</sub>  | Fligh-Side Fluating Supriy              |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.  $T_A=25^{\circ}C$  unless otherwise specified.

| Symbol              | Characteristics                        | Min.                | Max.                | Unit   |

|---------------------|----------------------------------------|---------------------|---------------------|--------|

| V <sub>S</sub>      | High-Side Floating Offset Voltage      | V <sub>B</sub> -25  | V <sub>B</sub> +0.3 | V      |

| V <sub>B</sub>      | High-Side Floating Supply Voltage      | -0.3                | 625.0               | V      |

| V <sub>HO</sub>     | High-Side Floating Output Voltage      | V <sub>S</sub> -0.3 | V <sub>B</sub> +0.3 | V      |

| V <sub>DD</sub>     | Low-Side and Logic Supply Voltage      | -0.3                | 25.0                | V      |

| V <sub>IN</sub>     | Logic Input Voltage                    | -0.3                | V <sub>D</sub>      | V      |

| dV <sub>S</sub> /dt | Allowable Offset Voltage Slew Rate     |                     | 50                  | V/ns   |

| P <sub>D</sub>      | Power Dissipation <sup>(2, 3, 4)</sup> |                     | J.0.                | W      |

| $\theta_{JA}$       | Thermal Resistance                     |                     | 200                 | °C /\V |

| T <sub>J</sub>      | Junction Temperature                   | -5                  | +150                | , ℃    |

| T <sub>STG</sub>    | Storage Temperature                    | -55                 | -150                | °C     |

#### Notes:

- 2. Mounted on 76.2 x 114.3 x 1.6 mm PCB (FR-4 glass 30. ma rial).

- 3. Refer to the following standards:

JESD51-2: Integrated circuits thermal test mathod expressions and conditions, natural convection, and JESD51-3: Low effective thermal conductivity and standards surface mount package.

- 4. Do not exceed power dissipation (PD) to include irreduces

### Recommended Or Julian Cor litions

The Recommended Or rating Conditions table defines the conditions for actual device operation. Recommended operating condition, are recific to ensure optimal performance to the datasheet specifications. Fairchild does not recommend e. eed them... designing to absolute maximum ratings.

| emb.            | Parameter                                 | Min.               | Max.               | Unit |

|-----------------|-------------------------------------------|--------------------|--------------------|------|

| V <sub>L</sub>  | High-Side Floating Supply Voltage         | V <sub>S</sub> +10 | V <sub>S</sub> +20 | V    |

| Vc              | Figh-Side Floating Supply Officet Voltage | 6-V <sub>DD</sub>  | 600                | V    |

| НО              | Ligh-Side Output Voltage                  | V <sub>S</sub>     | $V_{B}$            | V    |

| Vini            | Logic เลput Vokage                        | GND                | $V_{DD}$           | V    |

| V <sub>DD</sub> | Supply Votage                             | 10                 | 20                 | V    |

| T <sub>A</sub>  | Operating Ambient Temperature             | -40                | +125               | °C   |

### **Electrical Characteristics**

$V_{BIAS}(V_{DD},\,V_{BS})$  = 15.0 V and  $T_A$  = 25°C unless otherwise specified. The  $V_{IN}$  and  $I_{IN}$  parameters are referenced to GND. The  $V_O$  and  $I_O$  parameters are relative to  $V_S$  and are applicable to the respective output HO.

| Symbol                                   | Characteristics                                                                           | Test Condition                                                    | Min. | Тур. | Max. | Unit |

|------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| Power Su                                 | pply Section                                                                              |                                                                   |      |      | 1    |      |

| $I_{QDD}$                                | Quiescent V <sub>DD</sub> Supply Current                                                  | V <sub>IN</sub> =0 V or 5 V, C <sub>LOAD</sub> =1000 pF           |      | 80   | 140  | μА   |

| I <sub>PDD</sub>                         | Operating V <sub>DD</sub> Supply Current                                                  | C <sub>LOAD</sub> =1000 pF, f <sub>IN</sub> =20 KHz,<br>RMS value |      | 80   | 160  | μА   |

| $V_{DDUV+} \ V_{BSUV+}$                  | $V_{DD}$ and $V_{BS}$ Supply Under-Voltage Positive Going Threshold Voltage               | V <sub>DD</sub> =Sweep, V <sub>BS</sub> =Sweep                    | 7.8  | 8.8  | 9.8  | ٧    |

| V <sub>DDUV-</sub><br>V <sub>BSUV-</sub> | V <sub>DD</sub> and V <sub>BS</sub> Supply Under-Voltage Negative Going Threshold Voltage | V <sub>DD</sub> =Sweep, V <sub>BS</sub> =Sweep                    | 7.   | 8.3  | 9.3  | 8    |

| V <sub>DDHYS</sub><br>V <sub>BSHYS</sub> | $V_{DD}$ and $V_{BS}$ Supply Under-Voltage Lockout Hysteresis Voltage                     | V <sub>DD</sub> =Sweep, V <sub>BS</sub> =Swε τ                    |      | 0.5  | (O)  | ٧    |

| I <sub>LK</sub>                          | Offset Supply Leakage Current                                                             | V <sub>B</sub> =V <sub>S</sub> =600 V                             |      | 6    | 10   | μА   |

| I <sub>QBS</sub>                         | Quiescent V <sub>BS</sub> Supply Current                                                  | V <sub>IN</sub> =0 ' 5 V, OAL JU pF                               | 2    | 60   | 100  | μА   |

| I <sub>PBS</sub>                         | Operating V <sub>BS</sub> Supply Current                                                  | C <sub>O</sub> , =1c 7 pr, :20 KHz<br>RMS 'ue                     | -ex  | 420  | 600  | μΑ   |

| Input Log                                | ic Section                                                                                | OED OF                                                            | 3    | 7    |      |      |

| $V_{IH}$                                 | Logic "1" Input Voltage                                                                   | ND R                                                              | 2.5  |      |      | V    |

| $V_{IL}$                                 | Logic "0" Input Voltage                                                                   | WE, Op, O                                                         |      |      | 0.8  | V    |

| I <sub>IN+</sub>                         | Logic Input High Bias rrrent                                                              | V <sub>N</sub> =5 V                                               |      | 50   | 75   | μА   |

| I <sub>IN-</sub>                         | Logic Input L w Bias Cu.                                                                  | V <sub>IN</sub> =0 V                                              |      |      | 2    | μА   |

| $R_{IN}$                                 | Input Do Resi ance                                                                        | (K-CO)                                                            | 60   | 100  |      | ΚΩ   |

| Gate Driv                                | r C tion                                                                                  |                                                                   |      |      |      |      |

| V                                        | in the Liver utput Voltage (V <sub>BIAS</sub> · V <sub>D</sub> )                          | I 'o Load                                                         |      |      | 0.1  | V    |

| V <sub>OL</sub>                          | Lov. evel Octput Voltage                                                                  | No Load                                                           |      |      | 0.1  | V    |

|                                          | Output High, Short Circuit Pulsed Current                                                 | V <sub>HO</sub> =0 V, V <sub>IN</sub> =5 V, PW ≤10 μs             | 200  | 250  | 7    | mA   |

| I <sub>O-</sub>                          | Output Low, Short Circuit Puisea Current                                                  | $V_{HO}$ =15 V, $V_{IN}$ =0 V, PW $\leq$ 10 $\mu$ s               | 400  | 500  |      | mA   |

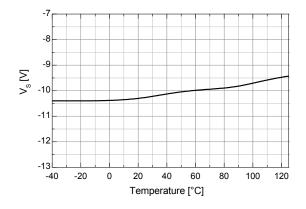

| C VS                                     | Allowable Negative V., Pin Voltage for IN<br>Signal Propagation to HO                     | V <sub>BS</sub> =15 V                                             |      | -9.8 | -7.0 | V    |

## **Dynamic Electrical Characteristics**

$\rm V_{DD}\text{=}V_{BS}\text{=}15$  V,  $\rm C_{LOAD}\text{=}1000$  pF, and  $\rm T_{A}\text{=}25^{\circ}C,$  unless otherwise specified.

| Symbol           | Parameter                       | Conditions          | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------|---------------------|------|------|------|------|

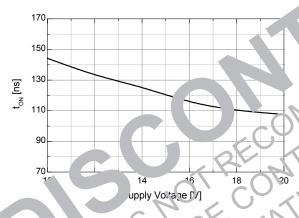

| t <sub>on</sub>  | Turn-On Propagation Delay Time  | V <sub>S</sub> =0 V | 70   | 120  | 170  | ns   |

| t <sub>off</sub> | Turn-Off Propagation Delay Time | V <sub>S</sub> =0 V | 70   | 120  | 170  | ns   |

| t <sub>r</sub>   | Turn-On Rise Time               |                     |      | 70   | 140  | ns   |

| t <sub>f</sub>   | Turn-Off Fall Time              |                     |      | 30   | 60   | ns   |

.

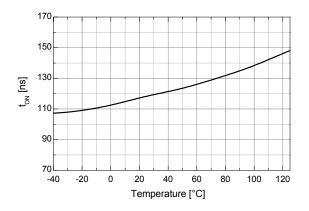

## **Typical Characteristics**

170 150 130 110 90 -40 -20 0 20 60 80 0 120 Ten ratur C]

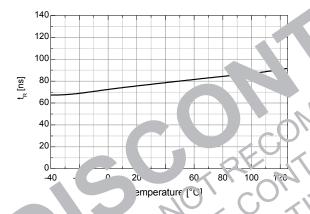

Figure 5. Turn-On Propagation Delay vs. Temperature

Figu. 6. Tu. -On pagation Delay vs. emperature

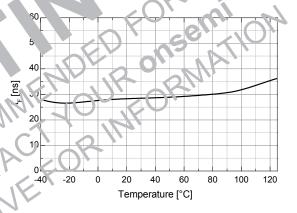

Figu. 7. rn-On Ries Time vs. Temperature

Figure 8. Turn-Off Fall Time vs. Temperature

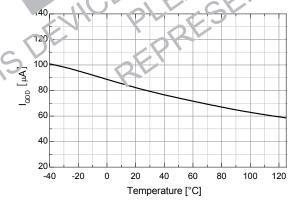

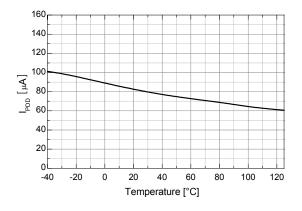

Figure 9. Quiescent V<sub>DD</sub> Supply Current vs. Temperature

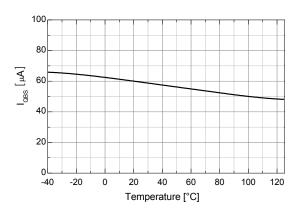

Figure 10. Quiescent V<sub>BS</sub> Supply Current vs. Temperature

600 550 500 500 440 350 300 250 -40 -20 0 20 60 80 0 120 Ten\_\_ratur C]

Figure 11. Operating  $V_{DD}$  Supply Current vs. Temperature

Figure 2. Op htm Supply Current vs. amperature

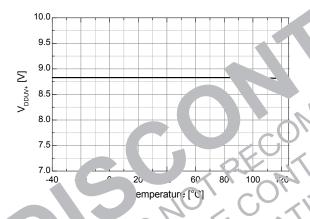

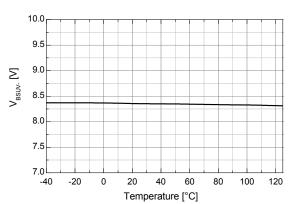

Figure 3. V<sub>DD</sub> U /LQ+ vs. Temperature

Figure 14.  $V_{DD}$  UVLO- vs. Temperature

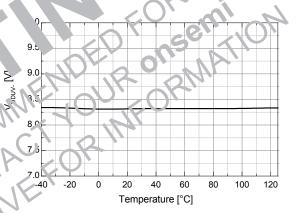

Figure 15.  $V_{BS}$  UVLO+ vs. Temperature

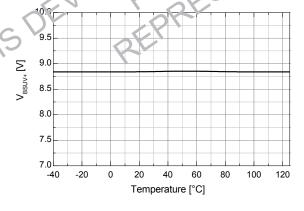

Figure 16.  $V_{BS}$  UVLO- vs. Temperature

3.0 2.5 2.0 1.5 1.0 0.5 -40 -20 0 20 5 60 '0 0 120 Tem, 'att', C]

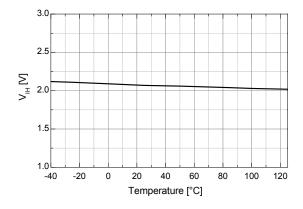

Figure 17. Logic HIGH Input Voltage vs. Temperature

Fig. > 18. L. nic Input Voltage vs. emperature

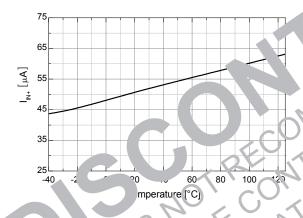

Fig e 1 Logic High Input Stas Current

vs. Temperature

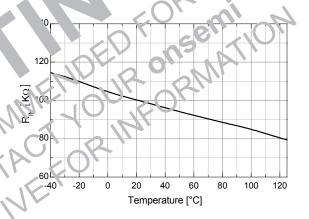

Figure 20. Input Pull-Down Resistance vs. Temperature

Figure 21. High-Level Output Voltage vs. Temperature

Figure 22. Low-Level Output Voltage vs. Temperature

-4

-6

-8

-8

-7

-10

-12

-14

-16

10

12

14

16

18

20

Supi Volta [V]

Figure 23. Allowable Negative V<sub>S</sub> Voltage vs. Temperature

Figure 4. Allc able gative V<sub>3</sub> Voltage vs. 5 pply Voltage

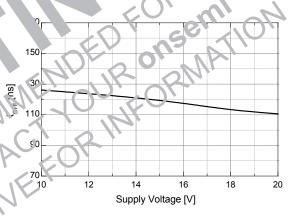

Filine 5. Turn On Propagation Delay vs. Supply Voltage

Figure 26. Turn-Off Propagation Delay vs. Supply Voltage

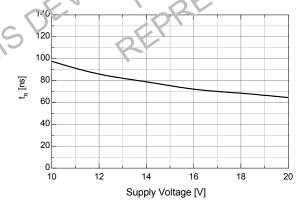

Figure 27. Turn-On Rise Time vs. Supply Voltage

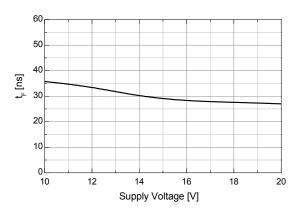

Figure 28. Turn-Off Fall Time vs. Supply Voltage

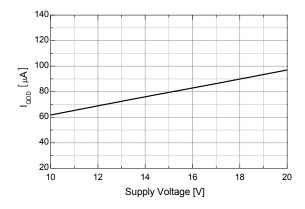

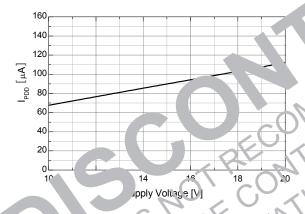

Figure 29. Quiescent V<sub>DD</sub> Supply Current vs. Supply Voltage

Figure 1. Qu. cei as Supply Current vs. 5 pply Voltage

Fig. 'e 5. Operating V<sub>DD</sub> Supply Current vs. Supply Yoltage

Figure 32. Operating V<sub>BS</sub> Supply Current vs. Supply Voltage

# **Switching Time Definitions**

Figure 33. Switching Time Test Circuit and Way form of fin or

Figure 34. Floating Supply Voltage Transient Test

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative