# Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

# FL7733 Primary-Side-Regulated LED Driver with Power Factor Correction

#### **Features**

#### **High Performance**

- Cost-Effective Solution without Requiring Input Bulk Capacitor and Secondary Feedback Circuitry

- Power Factor Correction

- THD <10% Over Universal Line Range</p>

- Constant Current Tolerance:

- < ±1% Over Universal Line Voltage Variation

- < ±1% by 50% 100% Load Voltage Variation

- < ±1% by ±20% Magnetizing Inductance Variation

- High-Voltage Startup with V<sub>DD</sub> Regulation

- Adaptive Feedback Loop Control for Startup without Overshoot

### **High Reliability**

- LED Short / Open Protection

- Output Diode Short Protection

- Sensing Resistor Short / Open Protection

- V<sub>DD</sub> Over-Voltage Protection (OVP)

- V<sub>DD</sub> Under-Voltage Lockout (UVLO)

- Over-Temperature Protection (OTP)

- All Protections are Auto Restart (AR)

- Cycle-by-Cycle Current Limit

- Application Input Voltage Range: 80 V<sub>AC</sub> 308 V<sub>AC</sub>

# **Applications**

LED Lighting System

## Description

This highly integrated PWM controller with advanced Primary-Side Regulation (PSR) technique provides features to enhance the performance of low-to-mid-power LED lighting converter. The FL7733 LED driver is designed with minimum system components while LED current is accurately controlled by Fairchild's TRUECURRENT® technique and improved feedback loop control. Constant Current (CC) tolerance less than  $\pm 1\%$  over the universal line voltage range meets the requirement of highly reliable LED brightness management.

By minimizing turn-on time fluctuation, high power factor, and low THD; <10% THD over the universal line range can be obtained. An integrated high-voltage startup circuit implements fast startup and high system efficiency. During startup, adaptive feedback loop control anticipates the steady-state condition and sets initial feedback condition close to the steady state to ensure no overshoot or undershoot of LED current.

The FL7733 provides powerful protections, such as LED short / open, output diode short, sensing resistor short / open, and over-temperature for high system reliability.

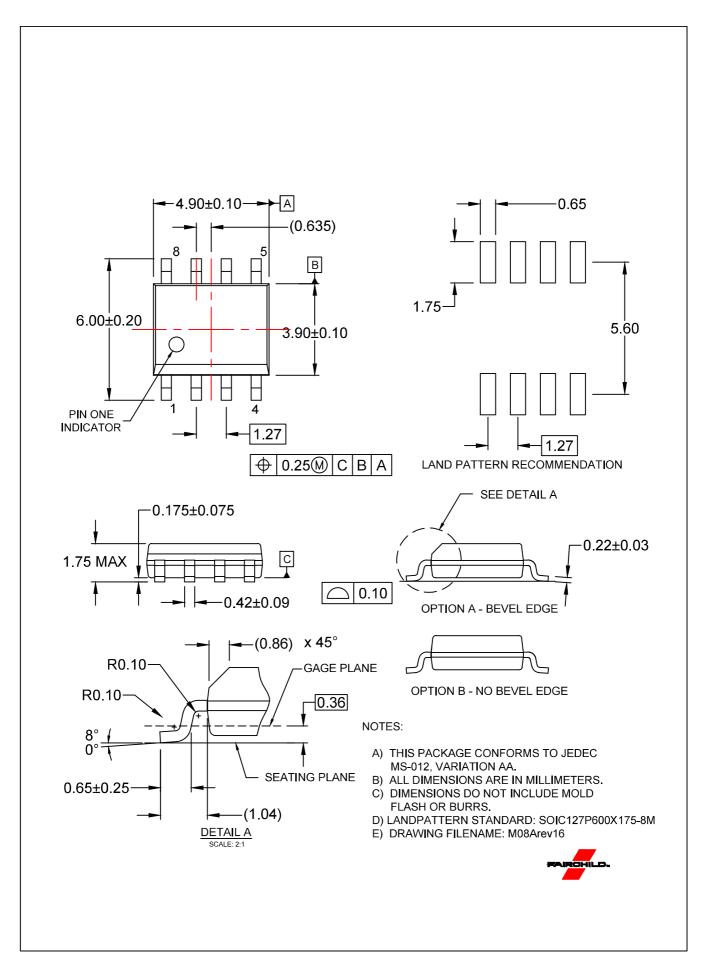

The FL7733 controller is available in an 8-pin Small-Outline Package (SOP).

#### Related Resources

AN-5076 — Design High Power Factor Flyback Converter using FL7733 for LED Driver with Ultra-Wide Output Voltage

AN-FEBFL7733\_L50U008A — User Guide for FEBFL7733\_L50U008A Evaluation Board of 8.4 W LED Driver (PFC PSR Flyback)

AN-FEBFL7733 L52U050A — User Guide for FEBFL7733 L52U050A Evaluation Board of 50 W LED Driver (PFC PSR Flyback)

Ordering Information

| Part Number Operating Temperature Range |                 | Package                               | Packing Method |  |

|-----------------------------------------|-----------------|---------------------------------------|----------------|--|

| FL7733MX                                | -40°C to +125°C | 8-Lead, Small Outline Package (SOP-8) | Tape & Reel    |  |

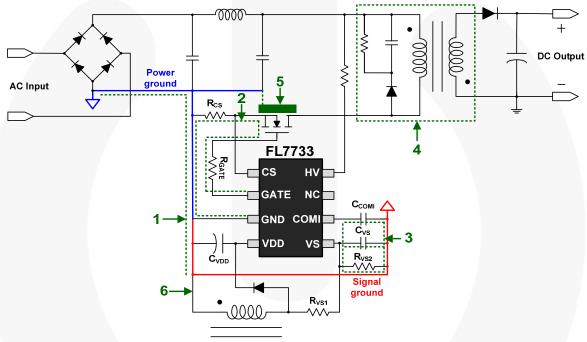

# **Application Diagram**

Figure 1. Typical Application

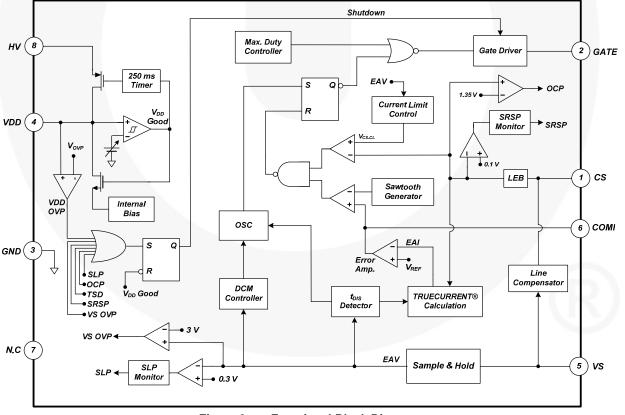

# **Block Diagram**

Figure 2. Functional Block Diagram

# **Marking Information**

F: Fairchild Logo

Z: Plant Code

X: 1-Digit Year CodeY: 1-Digit Week Code

TT: 2-Digit Veek Code

T: Package Type (M=SOP)

M: Manufacture Flow Code

Figure 3. Top Mark

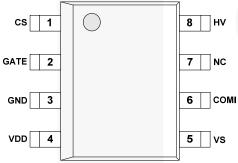

# **Pin Configuration**

Figure 4. Pin Configuration (Top View)

# **Pin Descriptions**

| Pin# | Name | Description                                                                                                                                                                                            |  |  |  |

|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | CS   | Current Sense. This pin connects a current-sense resistor to detect the MOSFET current for constant output current regulation.                                                                         |  |  |  |

| 2    | GATE | <b>PWM Signal Output</b> . This pin uses the internal totem-pole output driver to drive the power MOSFET.                                                                                              |  |  |  |

| 3    | GND  | Ground                                                                                                                                                                                                 |  |  |  |

| 4    | VDD  | Power Supply. IC operating current and MOSFET driving current are supplied using this pin.                                                                                                             |  |  |  |

| 5    | VS   | <b>Voltage Sense</b> . This pin detects the output voltage and discharge time information for CC regulation. This pin is connected to the auxiliary winding of the transformer via a resistor divider. |  |  |  |

| 6    | COMI | Constant Current Loop Compensation. This pin is connected to a capacitor between COMI and GND for compensating the current loop gain.                                                                  |  |  |  |

| 7    | NC   | No Connect                                                                                                                                                                                             |  |  |  |

| 8    | HV   | High Voltage. This pin is connected to the rectified input voltage via a resistor.                                                                                                                     |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol            | Parameter                                |      | Max. | Unit |

|-------------------|------------------------------------------|------|------|------|

| HV                | HV Pin Voltage                           |      | 700  | V    |

| $V_{VDD}$         | DC Supply Voltage <sup>(1,2)</sup>       |      | 30   | ٧    |

| V <sub>VS</sub>   | VS Pin Input Voltage                     | -0.3 | 6.0  | ٧    |

| V <sub>CS</sub>   | CS Pin Input Voltage                     | -0.3 | 6.0  | ٧    |

| V <sub>COMI</sub> | COMI Pin Input Voltage                   | -0.3 | 6.0  | ٧    |

| $V_{GATE}$        | GATE Pin Input Voltage                   | -0.3 | 30.0 | ٧    |

| P <sub>D</sub>    | Power Dissipation (T <sub>A</sub> <50°C) |      | 633  | mW   |

| TJ                | Maximum Junction Temperature             |      | 150  | °C   |

| T <sub>STG</sub>  | Storage Temperature Range                | -55  | 150  | °C   |

| TL                | Lead Temperature (Soldering) 10 Seconds  |      | 260  | °C   |

#### Notes:

- 1. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

- 2. All voltage values, except differential voltages, are given with respect to GND pin.

# Thermal Impedance

T<sub>A</sub>=25°C, unless otherwise specified

| Symbol        | Parameter                             | Value | Unit |

|---------------|---------------------------------------|-------|------|

| θЈА           | Junction-to-Ambient Thermal Impedance | 158   | °C/W |

| $\theta_{JC}$ | Junction-to-Case Thermal Impedance    | 39    | °C/W |

#### Note:

3. Referenced the JEDEC recommended environment, JESD51-2, and test board, JESD51-3, 1S1P with minimum land pattern.

# **ESD Capability**

| Symbol | Parameter                                     | Value | Unit |

|--------|-----------------------------------------------|-------|------|

| ESD    | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 | 4     | kV   |

|        | Charged Device Model, JESD22-C101             | 2     | ٨V   |

#### Note:

4. Meets JEDEC standards JESD22-A114 and JESD 22-C101.

# **Electrical Characteristics**

$V_{DD}$ =15 V,  $T_{J}$ =-40 to +125°C, unless otherwise specified. Currents are defined as positive into the device and negative out of device.

| Symbol                    | Parameter                                         | Conditions                                                                                  | Min.                                  | Тур. | Max. | Unit |

|---------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------|------|------|------|

| $V_{\text{DD-ON}}$        | Turn-On Threshold Voltage                         |                                                                                             | 14.5                                  | 16.0 | 17.5 | V    |

| $V_{DD\text{-}OFF}$       | Turn-Off Threshold Voltage                        |                                                                                             | 6.75                                  | 7.75 | 8.75 | V    |

| I <sub>DD-OP</sub>        | Operating Current                                 | C <sub>L</sub> =1 nF, f=f <sub>MAX-CC</sub>                                                 | 3                                     | 4    | 5    | mA   |

| I <sub>DD-ST</sub>        | Startup Current                                   | V <sub>DD</sub> =V <sub>DD-ON</sub> -1.6 V                                                  |                                       | 30   | 50   | μA   |

| $V_{VDD\text{-}OVP}$      | V <sub>DD</sub> Over-Voltage Protection Level     |                                                                                             | 23                                    | 24   | 25   | V    |

| SATE SECTION              | ON                                                |                                                                                             | 4                                     | l.   | ı    |      |

| V <sub>OL</sub>           | Output Voltage Low                                | $T_A$ =25°C, $V_{DD}$ =20 V, $I_{DD\_GATE}$ =1 mA                                           |                                       |      | 1.5  | V    |

| V <sub>OH</sub>           | Output Voltage High                               | T <sub>A</sub> =25°C, V <sub>DD</sub> =10 V,<br>I <sub>DD</sub> =1 mA                       | 5                                     |      |      | ٧    |

| I <sub>SOURCE</sub>       | Peak Sourcing Current <sup>(5)</sup>              | V <sub>DD</sub> =10 ~ 20 V                                                                  |                                       | -60  |      | mA   |

| I <sub>SINK</sub>         | Peak Sinking Current <sup>(5)</sup>               | V <sub>DD</sub> =10 ~ 20 V                                                                  |                                       | 180  |      | mA   |

| $t_R$                     | Rising Time                                       | T <sub>A</sub> =25°C, V <sub>DD</sub> =15 V,<br>C <sub>LOAD</sub> =1 nF                     | 100                                   | 150  | 200  | ns   |

| t <sub>F</sub>            | Falling Time                                      | T <sub>A</sub> =25°C, V <sub>DD</sub> =15 V,<br>C <sub>LOAD</sub> =1 nF                     | 20                                    | 60   | 100  | ns   |

| $V_{CLAMP}$               | Output Clamp Voltage                              | V <sub>DD</sub> =20 V, V <sub>CS</sub> =0 V,<br>V <sub>VS</sub> =0 V, V <sub>COM</sub> =0 V | 12                                    | 15   | 18   | ٧    |

| IV STARTUP                | SECTION                                           |                                                                                             | · · · · · · · · · · · · · · · · · · · |      |      |      |

| I <sub>HV</sub>           | Supply Current From HV Pin                        | T <sub>A</sub> =25°C, V <sub>IN</sub> =90 V <sub>AC</sub> ,<br>V <sub>DD</sub> =0 V         |                                       |      | 9    | mA   |

| I <sub>HV-LC</sub>        | Leakage Current after Startup                     |                                                                                             |                                       | 1    | 10   | μA   |

| t <sub>R-JFET</sub>       | JFET Regulation Time after Startup <sup>(5)</sup> | T <sub>A</sub> =25°C                                                                        | 190                                   | 250  | 310  | ms   |

| V <sub>JFET-HL</sub>      | JFET Regulation High Limit Voltage                |                                                                                             | 17.5                                  | 19.0 | 20.5 | V    |

| $V_{JFET-LL}$             | JFET Regulation Low Limit Voltage                 |                                                                                             | 11.5                                  | 13.0 | 14.5 | V    |

| URRENT-ER                 | RROR-AMPLIFIER SECTION                            |                                                                                             |                                       | l .  |      |      |

| 9м                        | Transconductance <sup>(5)</sup>                   | T <sub>A</sub> =25°C                                                                        | 11                                    | 17   | 23   | µmho |

| I <sub>COMI-SINK</sub>    | COMI Sink Current                                 | T <sub>A</sub> =25°C, V <sub>EAI</sub> =2.55 V,<br>V <sub>COMI</sub> =5 V                   | 12                                    | 18   | 24   | μA   |

| I <sub>COMI-SOURCE</sub>  | COMI Source Current                               | T <sub>A</sub> =25°C, V <sub>EAI</sub> =0.45 V,<br>V <sub>COMI</sub> =0 V                   | 12                                    | 18   | 24   | μA   |

| V <sub>COMI-HGH</sub>     | COMI High Voltage                                 | V <sub>EAI</sub> =0 V                                                                       | 4.7                                   |      |      | V    |

| $V_{\text{COMI-LOW}}$     | COMI Low Voltage                                  | V <sub>EAI</sub> =5 V                                                                       |                                       |      | 0.1  | V    |

| V <sub>COMI_INT.CLP</sub> | Initial COMI Clamping Voltage <sup>(5)</sup>      |                                                                                             |                                       | 1.2  |      | V    |

| t <sub>COMI_INT.CLP</sub> | Time for Initial COMI Clamping <sup>(5)</sup>     |                                                                                             |                                       | 15   |      | ms   |

Continued on the following page...

# **Electrical Characteristics** (Continued)

$V_{DD}$ =15 V,  $T_J$ =-40 to +125°C, unless otherwise specified. Currents are defined as positive into the device and negative out of device.

| Symbol                            | Parameter                                                                       | Conditions                                        | Min.  | Тур.  | Max.  | Unit |

|-----------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------|-------|-------|-------|------|

| VOLTAGE-SEI                       | NSE SECTION                                                                     |                                                   | I     | l .   |       |      |

| V <sub>VS-MAX-CC</sub>            | V <sub>S</sub> for Maximum Frequency in CC                                      | f=f <sub>MAX-CC</sub> -2 kHz                      | 2.25  | 2.35  | 2.45  | V    |

| V <sub>VS-MIN-CC</sub>            | V <sub>S</sub> for Minimum Frequency in CC                                      | f=f <sub>MIN-CC</sub> +2 kHz                      | 0.55  | 0.85  | 1.15  | V    |

| t <sub>DIS-BNK</sub>              | t <sub>DIS</sub> Blanking Time of V <sub>S</sub> <sup>(5)</sup>                 |                                                   | 0.85  | 1.15  | 1.45  | μs   |

| I <sub>VS-BNK</sub>               | V <sub>S</sub> Current for VS Blanking                                          |                                                   | -75   | -90   | -105  | μΑ   |

| V <sub>VS-OVP</sub>               | V <sub>S</sub> Level for Output Over-Voltage Protection                         |                                                   | 2.95  | 3.00  | 3.15  | V    |

| V <sub>VS-LOW-CL-EN</sub>         | V <sub>S</sub> Threshold Voltage to Enable Low Current Limit <sup>(5)</sup>     |                                                   | 0.25  | 0.30  | 0.35  | V    |

| V <sub>VS-HIGH-CL-DIS</sub>       | V <sub>S</sub> Threshold Voltage to Disable<br>Low Current Limit <sup>(5)</sup> |                                                   | 0.54  | 0.60  | 0.66  | V    |

| V <sub>VS-SLP-TH</sub>            | V <sub>S</sub> Threshold Voltage for Output<br>Short-LED Protection             |                                                   | 0.25  | 0.30  | 0.35  | V    |

| t <sub>SLP-BNK</sub>              | V <sub>S</sub> Detection Disable Time after Startup <sup>(5)</sup>              | T <sub>A</sub> =25°C                              |       | 15    |       | ms   |

| CURRENT-SE                        | NSE SECTION                                                                     |                                                   |       |       |       |      |

| $V_{RV}$                          | Reference Voltage                                                               | T <sub>A</sub> =25°C                              | 1.485 | 1.500 | 1.515 | V    |

| t <sub>LEB</sub>                  | Leading-Edge Blanking Time <sup>(5)</sup>                                       |                                                   |       | 300   |       | ns   |

| t <sub>MIN</sub>                  | Minimum On Time in CC <sup>(5)</sup>                                            | V <sub>COMI</sub> =0 V                            |       | 500   |       | ns   |

| t <sub>PD</sub>                   | Propagation Delay to GATE Output                                                |                                                   | 50    | 100   | 150   | ns   |

| V <sub>CS-HIGH-CL</sub>           | High Current Limit Threshold                                                    |                                                   | 0.9   | 1.0   | 1.1   | ٧    |

| V <sub>CS-LOW-CL</sub>            | Low Current Limit Threshold                                                     |                                                   | 0.16  | 0.20  | 0.24  | V    |

| t <sub>LOW-CM</sub>               | Low Current Mode Operation Time at Startup <sup>(5)</sup>                       |                                                   |       | 20    |       | ms   |

| V <sub>CS-SRSP</sub>              | V <sub>CS</sub> Threshold Voltage for Sensing Resistor Short Protection         |                                                   |       |       | 0.1   | V    |

| V <sub>CS-OCP</sub>               | V <sub>CS</sub> Threshold Voltage for Over-<br>Current Protection               | T <sub>A</sub> =25°C                              | 1.20  | 1.35  | 1.50  | V    |

| V <sub>CS</sub> / I <sub>VS</sub> | Relation of Line Compensation Voltage and V <sub>S</sub> Current <sup>(5)</sup> |                                                   |       | 21.5  |       | V/A  |

| OSCILLATOR                        | SECTION                                                                         |                                                   |       |       |       |      |

| f <sub>MAX-CC</sub>               | Maximum Frequency in CC                                                         | T <sub>A</sub> =25°C, V <sub>DD</sub> =10 V, 20 V | 60    | 65    | 70    | kHz  |

| f <sub>MIN-CC</sub>               | Minimum Frequency in CC                                                         | T <sub>A</sub> =25°C, V <sub>DD</sub> =10 V, 20 V | 21.0  | 23.5  | 26.0  | kHz  |

| t <sub>ON-MAX</sub>               | Maximum Turn-On Time                                                            | T <sub>A</sub> =25°C, f=f <sub>MAX-CC</sub>       | 10.4  | 13.0  | 15.6  | μs   |

| OVER-TEMPE                        | RATURE-PROTECTION SECTION                                                       |                                                   |       | •     |       |      |

| T <sub>OTP</sub>                  | Threshold Temperature for OTP <sup>(5)</sup>                                    |                                                   |       | 150   |       | °C   |

| T <sub>OTP-HYS</sub>              | Restart Junction Temperature<br>Hysteresis <sup>(5)</sup>                       |                                                   |       | 10    |       | °C   |

|                                   | 1                                                                               | ı                                                 |       |       |       |      |

#### Note:

5. These parameters, although guaranteed by design, are not production tested.

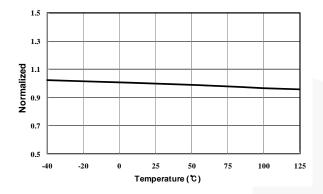

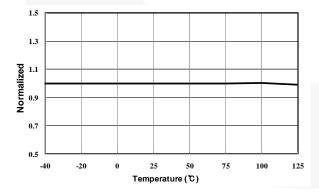

# **Typical Performance Characteristics**

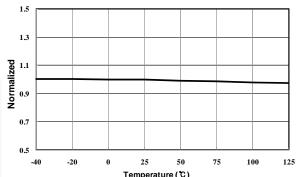

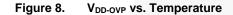

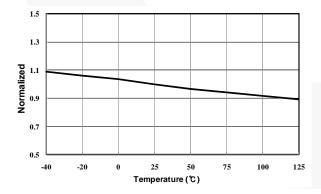

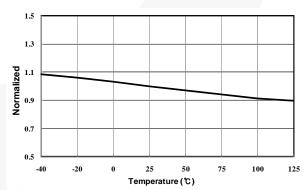

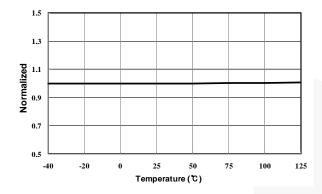

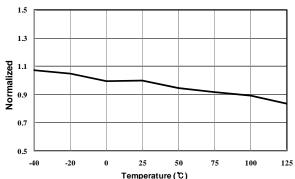

Figure 5. V<sub>DD-ON</sub> vs. Temperature

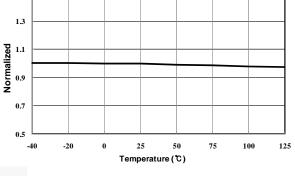

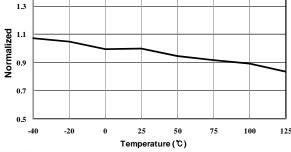

Figure 6. V<sub>DD-OFF</sub> vs. Temperature

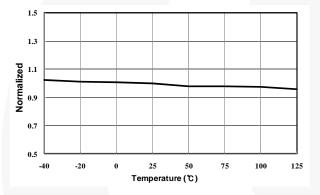

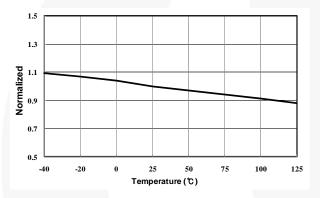

Figure 7. I<sub>DD-OP</sub> vs. Temperature

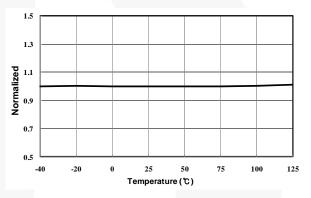

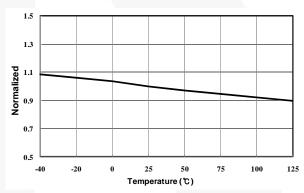

Figure 9. f<sub>MAX-CC</sub> vs. Temperature

Figure 10. f<sub>MIN-CC</sub> vs. Temperature

# **Typical Performance Characteristics** (Continued)

Figure 11. V<sub>VR</sub> vs. Temperature

Figure 12. Gm vs. Temperature

Figure 13. I<sub>COMI-SOURCE</sub> vs. Temperature

Figure 14. I<sub>COMI-SINK</sub> vs. Temperature

Figure 15. V<sub>VS-OVP</sub> vs. Temperature

Figure 16. V<sub>CS-OCP</sub> vs. Temperature

# **Functional Description**

FL7733 is AC-DC PWM controller for LED lighting applications. TRUECURRENT® techniques regulate accurate constant LED current; independent of input voltage, output voltage, and magnetizing inductance variations. The DCM control in the oscillator reduces conduction loss and maintains DCM operation over a wide range of output voltage, which implements high power factor correction in a single-stage flyback or buck-boost topology. A variety of protections, such as LED short / open protection, sensing resistor short / open protection, over-temperature protection, and cycle-by-cycle current limitation stabilize system operation and protect external components.

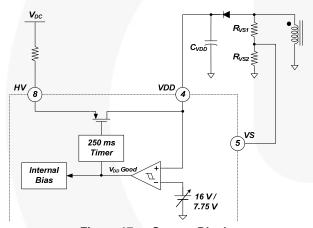

#### Startup

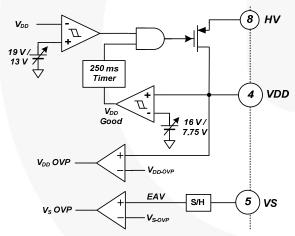

At startup, an internal high-voltage JFET supplies startup current and  $V_{\text{DD}}$  capacitor charging current, as shown in Figure 17. When  $V_{\text{DD}}$  reaches 16 V, switching begins and the internal high-voltage JFET continues to supply  $V_{\text{DD}}$  operating current for an initial 250 ms to maintain  $V_{\text{DD}}$  voltage higher than  $V_{\text{DD-OFF}}.$  As the output voltage increases, the auxiliary winding becomes the dominant  $V_{\text{DD}}$  supply current source.

Figure 17. Startup Block

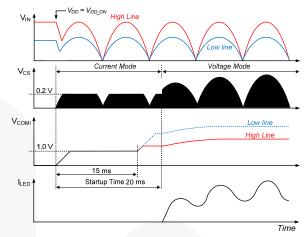

Switching is controlled by current-mode for 20 ms after  $V_{\text{DD-ON}}$ . During current-mode switching with the flyback or buck-boost topology, output current is only determined by output voltage. Therefore, the output voltage increases with constant slope, regardless of line voltage variation. Short-LED Protection (SLP) is enabled after the 15 ms SLP blanking time so that the output voltage is higher than SLP threshold voltage and successful startup is guaranteed without SLP in normal condition.

During current-mode switching, COMI voltage, which determines turn-on time in voltage mode, is adjusted close to the steady state level by sensing peak line voltage. The COMI capacitor is charged to 1.2 V for 15 ms and adjusted to a modulated level inversely proportional to  $V_{\rm IN}$  peak value for 5 ms. Turn-on time right after 20 ms startup time can be controlled close to steady state on time so that voltage mode is smoothly entered without LED current overshoot or undershoot.

Figure 18. Startup Sequence

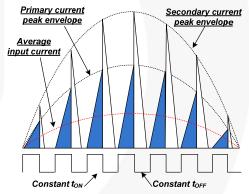

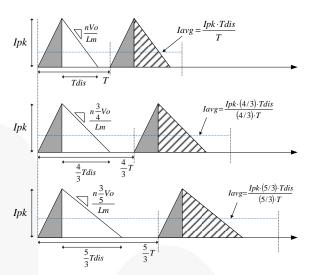

#### PFC and THD

In the flyback or the buck-boost topology, constant turnon time and constant frequency in Discontinuous Conduction Mode (DCM) operation can achieve high PF and low THD, as shown in Figure 19. Constant turn-on time is maintained by the internal error amplifier and a large external COMI capacitor (typically over 1  $\mu F)$  at COMI pin. Constant frequency and DCM operation are managed by DCM control.

Figure 19. Power Factor Correction

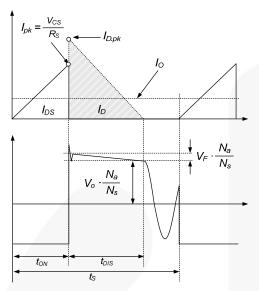

# Constant-Current Regulation The output current can be estimated using the peak drain current and inductor current discharge time

drain current and inductor current discharge time because output current is the same as the average of the diode current in steady state. The peak value of the drain current is determined by the CS peak voltage detector. The inductor current discharge time (t<sub>DIS</sub>) is sensed by a t<sub>DIS</sub> detector. With peak drain current, inductor current discharging time and operating switching period information, the TRUECURRENT® calculation block estimates output current as follows:

$$I_o = \frac{1}{2} \cdot \frac{t_{D/S}}{t_S} \cdot V_{CS} \cdot n_{PS} \cdot \frac{1}{R_S}$$

$$\frac{t_{D/S}}{t_S} \cdot V_{CS} = 0.25$$

$$I_o = 0.125 \cdot \frac{n_{PS}}{R_S}$$

(1)

where,  $n_{PS}$  is the primary-to-secondary turn ratio and  $R_S$  is a sensing resistor connected between the source terminal of the MOSFET and ground.

Figure 20. Key Waveforms for Primary-Side Regulation

The output of the current calculation is compared with an internal precise voltage reference to generate an error voltage ( $V_{\text{COMI}}$ ), which determines the MOSFET's turn-on time in voltage-mode control. With Fairchild's innovative TRUECURRENT® technique, constant-current output can be precisely controlled.

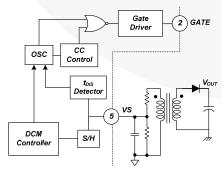

#### **DCM Control**

As mentioned above, DCM should be guaranteed for high power factor in flyback topology. To maintain DCM across a wide range of output voltage, the switching frequency is linearly adjusted by the output voltage in linear frequency control. Output voltage is detected by the auxiliary winding and the resistive divider connected to the VS pin, as shown in Figure 21. When the output voltage decreases, secondary diode conduction time is increased and the DCM control lengthens the switching period, which retains DCM operation over the wide output voltage range, as shown in Figure 22. The frequency control lowers the primary rms current with better power efficiency in full-load condition.

Figure 21. DCM and BCM Control

Figure 22. Primary and Secondary Current

#### **BCM Control**

The end of secondary diode conduction time could possibly be behind the end of a switching period set by DCM control. In this case, the next switching cycle starts at the end of secondary diode conduction time since FL7733 doesn't allow CCM. Consequently, the operation mode changes from DCM to BCM.

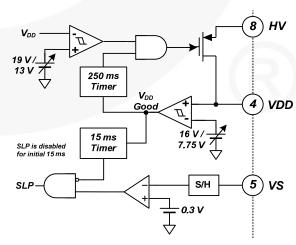

# **Short-LED Protection (SLP)**

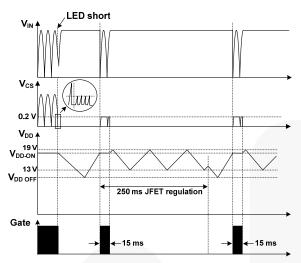

In case of a short-LED condition, the secondary diode is stressed by high current. When  $V_{\rm S}$  voltage is lower than 0.3 V due to a short-LED condition, the cycle-by-cycle current limit level changes to 0.2 V from 1.0 V and SLP is triggered if the  $V_{\rm S}$  voltage is less than 0.3 V for four (4) consecutive switching cycles. Figure 23 and Figure 24 show the SLP block and operational waveforms during LED-short condition. To set enough auto-restart time for system safety under protection conditions,  $V_{\rm DD}$  is maintained between 13 V and 19 V, which is higher than UVLO, for 250 ms after  $V_{\rm DD-ON}$ . SLP is disabled for an initial 15 ms to ensure successful startup in normal LED condition.

Figure 23. Internal SLP Block

Figure 24. Waveforms in Short-LED Condition

# **Open-LED Protection**

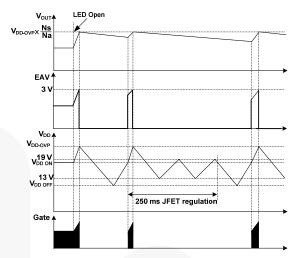

FL7733 protects external components, such as output diodes and output capacitors, during open-LED condition. During switch turn-off, the auxiliary winding voltage is applied as the reflected output voltage. Because the  $V_{\rm DD}$  and  $V_{\rm S}$  voltages have output voltage information through the auxiliary winding, the internal voltage comparators in the VDD and VS pins can trigger output Over-Voltage Protection (OVP), as shown in Figure 25 and Figure 26.

Figure 25. Internal OVP Block

Figure 26. Waveforms in LED Open Condition

# **Sensing Resistor Short Protection (SRSP)**

In a sensing resistor short condition, the  $V_{CS}$  level is almost zero and pulse-by-pulse current limit or OCP is not effective. The FL7733 is designed to provide sensing resistor short protection for both current and voltage mode operation. If the  $V_{CS}$  level is less than 0.1 V in the first switching cycle, the GATE output is stopped by current-mode SRSP. After 20 ms startup time, the GATE is shut down by the voltage-mode SRSP if  $V_{CS}$  level is less than 0.1 V at over 60% level of peak  $V_{IN}$ .

# **Under-Voltage Lockout (UVLO)**

The  $V_{DD}$  turn-on and turn-off thresholds are fixed internally at 16 V and 7.75 V, respectively. During startup, the  $V_{DD}$  capacitor must be charged to 16 V through the high-voltage JFET to enable the FL7733. The  $V_{DD}$  capacitor continues to supply  $V_{DD}$  until auxiliary power is delivered from the auxiliary winding of the main transformer.  $V_{DD}$  should remain higher than 7.75 V during this startup process. Therefore, the  $V_{DD}$  capacitor must be adequate to keep  $V_{DD}$  over the UVLO threshold until the auxiliary winding voltage is above 7.75 V.

#### **Over-Current Protection (OCP)**

When an output diode or secondary winding are shorted, switch current with extremely high di/dt can flow through the MOSFET even by minimum turn-on time. The FL7733 is designed to protect the system against this excessive current. When the CS voltage across the sensing resistor is higher than 1.35 V, the OCP comparator output shuts down GATE switching.

In a sensing resistor open condition, the sensing resistor voltage can't be detected and output current is not regulated properly. If the sensing resistor is damaged open-circuit, the parasitic capacitor in the CS pin is charged by internal CS current sources. Therefore, the  $V_{CS}$  level is built up to the OCP threshold voltage and then switching is shut down immediately.

#### Over-Temperature Protection (OTP)

The temperature-sensing circuit shuts down PWM output if the junction temperature exceeds 150°C. The hysteresis temperature after OTP triggering is 10°C.

# **PCB Layout Guidance**

PCB layout for a power converter is as important as circuit design because PCB layout with high parasitic inductance or resistance can lead to severe switching noise with system instability. PCB should be designed to minimize switching noise into control signals.

- The signal ground and power ground should be separated and connected only at one position (GND pin) to avoid ground loop noise. The power ground path from the bridge diode to the sensing resistors should be short and wide.

- Gate-driving current path (GATE R<sub>GATE</sub> MOSFET R<sub>CS</sub> GND) must be as short as possible.

- 3. Control pin components; such as  $C_{\text{COMI}}$ ,  $C_{\text{VS}}$ , and  $R_{\text{VS2}}$ ; should be placed close to the assigned pin and signal ground.

- High-voltage traces related to the drain of MOSFET and RCD snubber should be kept far way from control circuits to avoid unnecessary interference.

- 5. If a heat sink is used for the MOSFET, connect this heat sink to power ground.

- The auxiliary winding ground should be connected closer to the GND pin than the control pin components' ground.

Figure 27. Layout Example

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see any inability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and ex

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative