# Type-C CC and SBU Protection IC

### **PRODUCT SUMMARY**

#### **General Description**

The FUSB251 is an I2C controlled switch with over voltage protection on CC and SBU pins in Type–C interface port. The device has SPST switches on CC1/2 and SBU1/2 which enable automatically with valid VDD so that Type–C/PD controller can use the over voltage protected CC path. The FUSB251 has dead battery mode, CC pulled down with Rd, where Source device can provide Vbus for battery charging. Another feature in FUSB251 is moisture detection on both CC and SBU paths with ADC detection. Once moisture is detected, and Interrupt is generated and the corresponding register is updated to notify host. The device has on–chip IEC protection with surge protection on both CC and SBU. Both CC and SBU ports are 24 V DC tolerant. Package type is WLCSP with 15 ball 3x5 array.

#### Features

- Low Ron SPST Switches on both CC1/2 and SBU1/2 Path for Type-C

- Dead Battery Mode Provides Default Rd Presenting on CC1/2

- 24 V DC Tolerant on CC and SBU

- ±35 V Surge Protection on CC and SBU

- Over Voltage Protection on CC and SBU

- I2C Interface with Processor with Interrupt for event Notification

- Moisture Detection on CC and SBU Pins

- On-chip IEC ESD Protection with External Capacitor on CAP Pin

- CC Ron 0.3 Ω Typical

- SBU Ron 3  $\Omega$  Typical

- 50 MHz Bandwidth on SBU Switch

- 15 ball WLCSP

#### Applications

- Smart Phones

- Tablets, Netbooks, Ultra-Mobile PCs

- Gaming Devices and E-books

- Portable Devices with Li–ion Battery

- Car Cigarette Jack

- External USB Storage

### **ON Semiconductor®**

www.onsemi.com

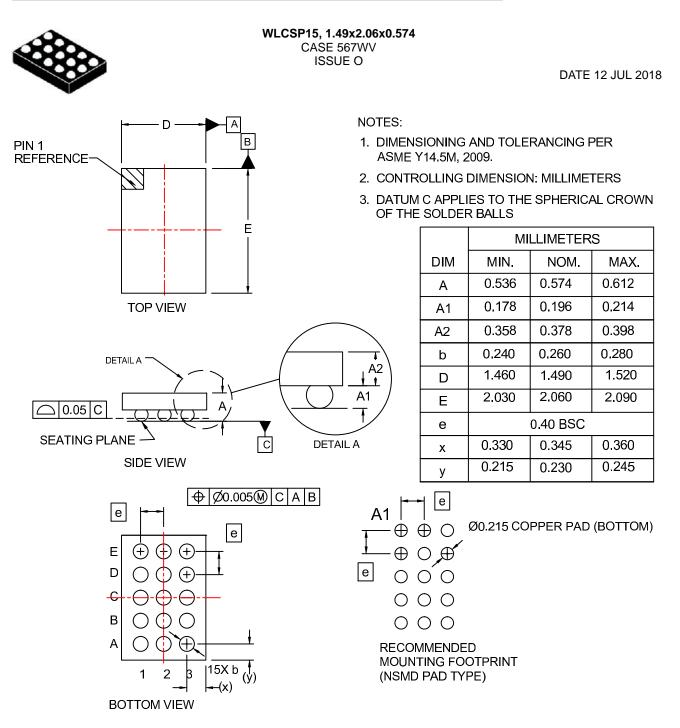

WLCSP15, 1.49x2.06x0.574 CASE 567WV

#### MARKING DIAGRAM

= Pin A1 Mark

UE

KK

XY

Ζ

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

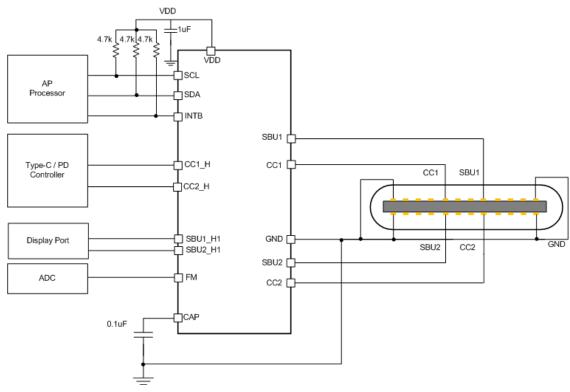

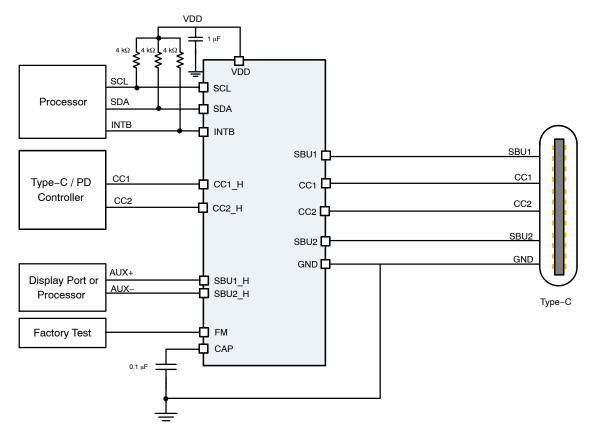

### **APPLICATION DIAGRAM**

### PART NUMBERING

### **ORDERING INFORMATION**

| Pa | art Number | Temperature Range | Package                                           | Packing Method † |

|----|------------|-------------------|---------------------------------------------------|------------------|

| FU | SB251UCX   | −40 to 85°C       | WLCSP, 3 x 5 array, 15 ball,<br>1.49 mm x 2.06 mm | Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### **PRODUCT PIN ASSIGNMENTS**

### **Pin Configuration**

Figure 2. Pin Configuration

### **Pin Descriptions**

#### **PIN DESCRIPTIONS**

| Pin# | Name   | Туре              | Description                                                                                                                        |

|------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|

| C1   | GND    | Ground            | GND                                                                                                                                |

| A2   | VDD    | Power             | Power                                                                                                                              |

| A3   | CC1    | I/O               | Type-C CC interface. Connect to USB Type-C connector CC1 pin                                                                       |

| B3   | CC2    | I/O               | Type-C CC interface. Connect to USB Type-C connector CC2 pin                                                                       |

| A1   | CC1_H  | I/O               | Type-C CC Host interface, Connect to USB Type-C controller CC1 pin                                                                 |

| B1   | CC2_H  | I/O               | Type-C CC Host interface, Connect to USB Type-C controller CC2 pin                                                                 |

| D3   | SBU1   | I/O               | Type-C SBU interface, Connect to USB Type-C connector SBU1 pin                                                                     |

| E3   | SBU2   | I/O               | Type-C SBU interface, Connect to USB Type-C connector SBU2 pin                                                                     |

| D1   | SBU1_H | I/O               | Type-C SBU Host Interface, Connect to Host side SBU1 application pin                                                               |

| E1   | SBU2_H | I/O               | Type-C SBU Host Interface, Connect to Host side SBU2 application pin.                                                              |

| E2   | FM     | I/O               | Factory test mode pin, Connect to ADC input of host processor. If not used, connect to GND. FM can be switched over to one of SBU. |

| C3   | CAP    | 0                 | Capacitor pin, Connect to 0.1 $\mu$ F capacitor to GND                                                                             |

| B2   | SCL    | Open Drain Input  | I <sup>2</sup> C interface, Pull up to Vdd is required, Connect to SCL pin of Processor                                            |

| C2   | SDA    | Open Drain I/O    | I <sup>2</sup> C interface, Pull up to Vdd is required, Connect to SDA pin of Processor                                            |

| D2   | INTB   | Open Drain Output | Interrupt for Host alert, Pull-up to VDD required, Connect to processor<br>Interrupt input                                         |

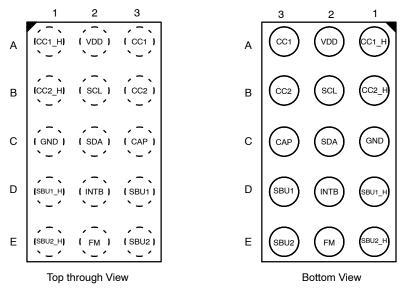

### PRODUCT BLOCK DIAGRAM

Figure 3. Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Parameter              | Conditions                                  | Min  | Тур | Max  | Units |

|-----------------------|------------------------|---------------------------------------------|------|-----|------|-------|

| TJ                    | Junction Temperature   |                                             | -40  |     | +150 | °C    |

| T <sub>STG</sub>      | Storage Temp           |                                             | -65  |     | +150 | °C    |

| VDD                   | Supply voltage         | Slew Rate 2 V/µs (rising), 1 V/µs (falling) | -0.5 |     | 12.0 | V     |

| VCC                   | Vccx to GND            |                                             | -0.5 |     | 24   | V     |

| VSBU                  | VSBUx to GND           |                                             | -0.5 |     | 24   | V     |

| VCCx_H and<br>VSBUx_H | VCCX_H, VSBUx_H to GND |                                             | -0.5 |     | 6.0  | V     |

| ICCSW                 | DC CC switch current   |                                             |      |     | 1.25 | А     |

| ISBUSW                | DC SBU switch current  |                                             |      |     | 100  | mA    |

| IIK                   | DC input diode current |                                             | -50  |     |      | mA    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### ESD RATINGS - JEDEC / IEC SPECIFICATION

| Electro Static Discharge (ESD) Specifications | Condit                   | Value             | Unit   |   |

|-----------------------------------------------|--------------------------|-------------------|--------|---|

| Human Body Model, JEDEC JESD22-A114           | CCx and SBUx             | pins to GND       | ±5000  | V |

|                                               | Other pins               |                   | ±2000  |   |

| Charged Device Model, JEDEC JESD22-C101       | All pir                  | All pins          |        |   |

| IEC 61000-4-2 System ESD                      | CCx and SBUx pins to GND | Air-gap Discharge | ±15000 |   |

|                                               |                          | Contact Discharge | ±8000  |   |

| IEC 61000-4-5 Lightning and Surge             | CCx and SBUx             | pins to GND       | ±35    |   |

#### **OPERATING CONDITIONS**

| Symbol                | Parameter                                           | Conditions                                  | MIn | Тур | Max                                                                                    | Unit |

|-----------------------|-----------------------------------------------------|---------------------------------------------|-----|-----|----------------------------------------------------------------------------------------|------|

| VDD                   | Supply Voltage Range                                |                                             | 2.7 | 3.8 | 5.5                                                                                    | V    |

| T <sub>A</sub>        | Operating Ambient Temperature                       |                                             | -40 |     | +85                                                                                    | °C   |

| T <sub>IN</sub> + 0.3 | Junction Temperature                                |                                             | -40 |     | +125                                                                                   | °C   |

| VCCx,<br>VCCx_H       | CC1 CC2, CC1_H, CC2_H voltage                       |                                             | 0   |     | 5.5                                                                                    | V    |

| VSBUx,<br>VSBUx_H     | SBU1, SBU2, SBU1_H,<br>SBU2_H voltage               |                                             | 0   |     | 4.2                                                                                    | V    |

| C_CAP                 | External capacitor capacitance                      |                                             |     | 0.1 | 1.0                                                                                    | μF   |

| VPU                   | Pull up resistor power rail of SDA, SCL<br>and INTB |                                             | 1.7 |     | VDD                                                                                    | V    |

| ICCSW                 | CC switch current                                   | $T_A = 25^{\circ}C$ and $T_A = 85^{\circ}C$ |     |     | $\begin{array}{l} 1000 \ (T_{A}=25^{\circ}C),\\ 800 \ (T_{A}=85^{\circ}C) \end{array}$ | mA   |

| ISBU                  | SBU switch current                                  |                                             |     |     | 50                                                                                     | mA   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

| Symbol                    | Parameter                                                    | Conditions                                                                                                                                                                                                                | Min  | Тур                                                          | Max                   | Unit |

|---------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------|-----------------------|------|

| Ι <sub>Q</sub>            | Quiescent supply current                                     | VDD = 2.7 to 5.5 V, Switch is closed,<br>no load, moisture detection is not<br>enabled                                                                                                                                    |      | 15                                                           |                       | μΑ   |

| I <sub>MOS</sub>          | Current with moisture detection enabled                      | VDD = 2.7 to 5.5 V, Switch is closed,<br>CC toggle and CC moisture<br>detection is enabled, Avg for 1 sec                                                                                                                 |      | 30                                                           |                       | μΑ   |

| I <sub>DRY</sub>          | Current consumption when Dry check is working on             | VDD = 2.7 to 5.5 V,<br>Moisture detected, and Dry check<br>enabled, T(PD, period) = 4 sec                                                                                                                                 |      | 15                                                           |                       | μΑ   |

| I <sub>OFF</sub>          | Power off leakage current                                    | VDD = 0 V, Except CC1/CC2                                                                                                                                                                                                 |      | 1                                                            |                       | μA   |

| V <sub>UVLO</sub>         | Under voltage Lockout                                        | VDD Rising, VDD Falling                                                                                                                                                                                                   |      | 2.45 (Rising),<br>2.40 (Falling)                             | 2.55 (Rising)         | V    |

| T <sub>SD</sub>           | Thermal Shut down                                            | Shutdown Threshold/ Return from<br>Shutdown/ Hysteresis                                                                                                                                                                   |      | 150°C<br>(shutdown),<br>130°C (Return),<br>20°C (Hysteresis) |                       |      |

| I <sub>CC_LEAK</sub>      | CC ON leakage current                                        | VDD = 2.7 to 5.5 V, CC Switch<br>closed, CCx_H float, measure<br>leakage from CCx with 3.3 V                                                                                                                              |      |                                                              | 0.5                   | μΑ   |

| R <sub>ON_CC</sub>        | CC1, CC2 RON resistance                                      | VDD = 2.7 to 5.5 V, IOUT = 200 mA                                                                                                                                                                                         |      | 300                                                          | 1                     | mΩ   |

| R <sub>Flatness_CC</sub>  | VDD = 2.7 to 5.5 V,<br>Vcc swing = 0 V - 1.2 V               |                                                                                                                                                                                                                           |      | 10                                                           |                       | mΩ   |

| V <sub>OVP_CC</sub>       | CC over voltage protection threshold                         | VDD = 2.7 to 5.5 V, VCC rising                                                                                                                                                                                            | 5.70 | 5.85                                                         | 6.00                  | V    |

| V <sub>OVP_CC_FALL</sub>  | CC recover threshold when voltage on CC is falling           | VDD = 2.7 V to 5.5 V                                                                                                                                                                                                      |      | 5.70                                                         |                       | V    |

| V <sub>OV_HYS_CC</sub>    | CC OVP threshold Hysteresis                                  | VDD = 2.7 to 5.5 V                                                                                                                                                                                                        |      |                                                              | 0.15                  | V    |

| t <sub>CC_OVP</sub>       | CC OVP Trip time (Note 1)                                    | $\label{eq:VDD} \begin{array}{l} \text{VDD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ CCx rise from 4} \\ \text{V to 6 V with 1 V/ns slew rate,} \\ \text{RL} = 30 \ \Omega \text{ on CCx_H} \end{array}$                   |      | 250                                                          |                       | ns   |

| Rd_CC                     | Dead battery pull down resistance                            | VDD = 0 to UVLO, Dead battery<br>resistance / Voltage on pin                                                                                                                                                              | 4.1  | 5.1                                                          | 6.1                   | kΩ   |

| V <sub>OVP_SBU</sub>      | SBU over voltage threshold                                   | VDD = 2.7 to 5.5 V, SBU Rising                                                                                                                                                                                            | 4.4  | 4.5                                                          | 4.7                   | V    |

| V <sub>OVP_SBU_FALL</sub> | SBU OVP recovery threshold when<br>voltage on SBU is falling | VDD = 2.7 V to 5.5 V                                                                                                                                                                                                      |      | 4.35                                                         |                       | V    |

| V <sub>OV_SBU_HYS</sub>   | SBU OVP Hysteresis                                           | VDD = 2.7 to 5.5 V, Measure<br>difference between SBUX rising and<br>falling OVP threshold                                                                                                                                |      |                                                              | 0.15                  | V    |

| I <sub>SBU_ON_LEAK</sub>  | SBU ON leakage current                                       | VDD = 2.7 to 5.5 V, Switch closed,<br>SBUX_H floating, measure leakage<br>@1 V SBU Note (SBU ON leakage spec<br>is different depending on temperature)<br>(Note 1)                                                        |      | 1                                                            | 5 @85°C,<br>15 @100°C | nA   |

| ISBU_OFF_LEAK             | SUB OFF leakage from SBUx                                    | VDD = 2.7 to 5.5 V, Switch open,<br>Measure leakage current from SBUx<br>with 0 – VDD                                                                                                                                     | -0.5 |                                                              | 0.5                   | μΑ   |

| R <sub>ON_SBU</sub>       | SBU1, SBU2 Switch ON resistance                              | VDD = 2.7 to 5.5 V, VSW_SBU<br>= VDD, ISBU_ON = -8mĀ                                                                                                                                                                      |      | 3                                                            | 5                     | Ω    |

| R <sub>Flatness_SBU</sub> | SBU RON Flatness                                             | VDD = 2.7 to 5.5 V,<br>VSBU Swing = 0 - VDD                                                                                                                                                                               |      | 0.1                                                          |                       | Ω    |

| T <sub>OVP_SBU</sub>      | SBU OVP response time (Note 1)                               | $\label{eq:VDD} \begin{array}{l} \text{VDD} = 2.7 \text{ to } 5.5 \text{ V}, \text{SBUx rise from} \\ 4 \text{ V to } 6 \text{ V with } 1 \text{ V/ns.} \\ \text{RL} = 30 \ \Omega \text{ on } \text{SBUx_H} \end{array}$ |      | 0.5                                                          |                       | μs   |

| R <sub>ON_FM</sub>        | FM to SBU1 or SBU2 ON resistance                             | VDD = 2.7 to 5.5 V, Close FM to<br>SBU1 or SBU2 switch, VSW_SBU<br>= VDD, ISBU_ON = -8 mA                                                                                                                                 |      | 15                                                           |                       | Ω    |

| R <sub>Flatness_FM</sub>  | FM to SBU1/SBU2 switch Rflatness                             | VDD = 2.7 to 5.5 V,<br>VSBU_Swing = 0 - VDD                                                                                                                                                                               |      | 0.1                                                          |                       | Ω    |

| C <sub>ON_CC</sub>        | CC Switch ON capacitance (Note 1)                            | VDD = 2.7 to 5.5 V,<br>VCC_SW = 0 - 1.2 V, f = 400 kHz                                                                                                                                                                    |      | 50                                                           |                       | pF   |

**ELECTRICAL SPECIFICATION TABLE** Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25^{\circ}$ C and VDD = 3.8 V unless otherwise specified.

| Symbol                   | Parameter                                                            | Conditions                                                                                                       | Min                 | Тур | Мах | Unit     |

|--------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|----------|

| C <sub>ON_SBU</sub>      | SBU Switch ON capacitance (Note 1)                                   | VDD = 2.7 to 5.5 V, Capacitance<br>from SBUx or SBUx_H to GND.<br>Switch closed, VSW = 0 – VDD,                  |                     | 25  |     | pF       |

| BW <sub>CC</sub>         | CC channel bandwidth (Note 1)                                        | tannel bandwidth (Note 1)<br>VDD = 3.6 V, -3 dB bandwidth,<br>RL = 50 $\Omega$ , CL = 200 pF                     |                     | 25  |     | MHz      |

| BW <sub>SBU</sub>        | SBU switch Bandwidth (Note 1)                                        | VDD = 3.6 V, $-3$ dB bandwidth<br>between SBUx and SBUx_H.<br>Singled ended, RL = 50 $\Omega$                    |                     | 30  |     | MHz      |

| T <sub>CC_MOS</sub>      | Timer of CC moisture detection (Note 1)                              | VDD = 2.7 to 5.5 V,<br>Timer for searching both CC rise.<br>Timer reset at both CC rising.                       | 108                 | 120 | 132 | ms       |

| T <sub>DRY</sub>         | Dry check period (Note 1)                                            | VDD = 2.7 to 5.5 V, Timer period of<br>SBU moisture detection for Dry<br>check, Programmable                     | 0.1                 |     | 10  | S        |

| T <sub>SBU_PRD</sub>     | Time between SBU1 and SBU2 mois-<br>ture detection (Note 1)          | VDD = 2.7 to 5.5 V, SBU moisture<br>detection enabled and measure<br>time voltage source on from SBU1<br>to SBU2 | 0.9                 | 1.0 | 1.1 | ms       |

| V <sub>CC_RISE_MOS</sub> | Moisture detection start voltage when both CC1 and CC2 rise          | VDD = 2.7 to 5.5 V                                                                                               | 130                 | 200 | 270 | mV       |

| V <sub>OUTL_INTB</sub>   | INTB output Low voltage                                              | VDD = 2.7 to 5.5 V                                                                                               |                     |     | 0.4 | V        |

| V <sub>IH_I2C</sub>      | SDA, SCL High level input voltage                                    | VDD = 2.7 to 5.5 V                                                                                               | 1.2                 |     |     | V        |

| V <sub>HYS_I2C</sub>     | SDA, SCL Hysteresis of Schmitt Trigger                               | VDD = 2.7 to 5.5 V                                                                                               | 200                 |     |     | mV       |

|                          |                                                                      |                                                                                                                  | 0.5                 |     |     | <u> </u> |

| I <sub>I2C</sub>         | Input Current of SDA and SCL Pins                                    | VDD = 2.7 to 5.5 V,<br>Input Voltage 0 to VDD                                                                    | -0.5                |     | 0.5 | μΑ       |

| ICCT_I2C                 | VDD current when SDA or SCL is HIGH                                  | Input voltage is 1.8 V                                                                                           | -0.5                |     | 2.5 | μA       |

| V <sub>OL_SDA</sub>      | Low-Level Output Voltage                                             | VDD = 2.7 to 5.5 V, 2 mA sink cur-<br>rent, Pull up to VDD                                                       | 0                   |     | 0.3 | V        |

| C <sub>I2C</sub>         | Capacitance on SDA and SCL (Note 1)                                  | VDD = 2.7 to 5.5 V                                                                                               |                     |     | 10  | pF       |

| f_SCL                    | I2C SCL clock frequency                                              |                                                                                                                  |                     |     | 400 | kHz      |

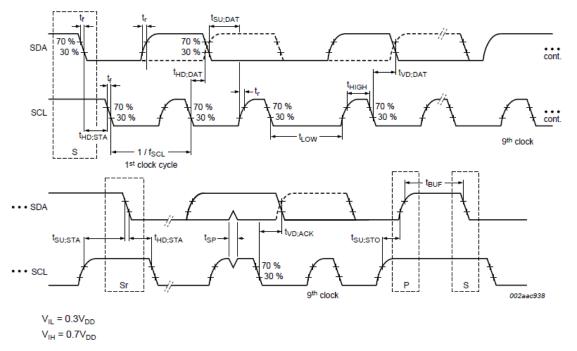

| tHD ; STA                | Hold Time (Repeated) START Condition                                 |                                                                                                                  | 0.6                 |     |     | μs       |

| tLOW                     | LOW Period of I2C_SCL Clock                                          |                                                                                                                  | 1.3                 |     |     | μs       |

| tHIGH                    | High Period of I2C_SCL Clock                                         |                                                                                                                  | 0.6                 |     |     | μs       |

| tSU ; STA                | Set-up Time for Repeated START<br>Condition                          |                                                                                                                  | 0.6                 |     |     | μs       |

| tHD ; DAT                | Data Hold Time                                                       |                                                                                                                  | 0                   |     | 0.9 | μs       |

| tSU ; DAT                | Data Set-up Time                                                     |                                                                                                                  | 100                 |     |     | ns       |

| tR                       | Rise Time of I2C_SDA and I2C_SCL Signals                             |                                                                                                                  | 20 ×<br>(VDD/5.5 V) |     | 250 | ns       |

| tF                       | Fall Time of I2C_SDA and I2C_SCL Signals                             |                                                                                                                  | 20×<br>(VDD/5.5 V)  |     | 250 | ns       |

| tSU ; STO                | Set-up Time for STOP Condition                                       |                                                                                                                  | 0.6                 |     |     | μs       |

| tBUF                     | BUS-Free Time between STOP and START Conditions                      |                                                                                                                  | 1.3                 |     |     | μs       |

| tSP                      | Pulse Width of Spikes that Must Be<br>Suppressed by the Input Filter |                                                                                                                  | 0                   |     | 50  | ns       |

**ELECTRICAL SPECIFICATION TABLE** Unless otherwise specified: Recommended  $T_A$  and  $T_J$  temperature ranges. All typical values are at  $T_A = 25^{\circ}$ C and VDD = 3.8 V unless otherwise specified.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 1. Guaranteed by Design, Characterization, not Production tester.

Figure 4. Definition of Timing for Full-Speed Mode Devices on the I2C Bus

#### FUNCTIONAL SPECIFICATIONS

#### **POR and Reset**

The FUSB251 closes both CC and SBU switches with a valid VDD supply after Power On reset. Until valid VDD is supplied, FUSB251 presents Rd on both CC1 and CC2 so that a source device can provide Vbus and Type–C controller can present Rd continuously after POR so VBUS will be consistent. At UVLO condition which is 2.4 volt (falling), CC and SBU switches get open again and Rd will be presented on both CC.

There is device reset register, bit0 in 0x0B register. If the register bit is set, all registers in the device are set to default, so momentarily both switches will be open and closed back.

#### CC and SBU Switch Characteristics

The FUSB251 has 2x SPST switches on both CCx and SBUx with OVP feature. Both CC and SBU switch paths are closed automatically with valid Vdd supply. CC switch is used for Type–C / PD communication channel. Also Vconn can be provided through the switch from CCx\_H to CCx. Up to 1A Vconn current can be provided over the low Ron(0.3  $\Omega$ ) path. Both CCx and SBUx pins are 24 volt DC-tolerant. SBU switch can be used for DisplayPort Aux channels following USB PD Alternative mode or UART.

#### **Dead Battery Mode**

Upon dead battery condition, the both CC1/2 ports present Rd(5.1 k $\Omega$ ) pull down to allow a Type–C source device to attach and provide Vbus to the sink which is under dead battery mode. Once system power comes back and valid VDD supplied to FUSB251, the dead battery Rd is removed and both CC switches are closed. Then, Type–C / PD controller can detect the attached Type–C source device.

#### **Over Voltage Protection**

When an over-voltage event is detected on either CCx or SBUx, the FUSB251 will activate OVP circuit to open the switch within tOVP. The OVP event is independent between CC and SBU. Any CC channel OVP opens the CC1 and CC2 switch path only, and SBU switch is keep closed. OVP on SBU opens the SBU switch only. Upon the detection of an over-voltage event, the INTB pin is asserted low to notify processor with register update.

When OVP condition is removed from the port, the switch path is closed automatically and OVP recovery interrupt is generated to notify processor. Getting interrupt service is not required to close the switch back. OVP function is only working on the connector face ports, CCx and SBUx.

#### FM Pin

FM pin is for Factory test Mode (FM) purpose. When Factory test mode is used over Type–C connector and if host device needs to detect Factory Test fixtures by using ID with ADC function, the FM can be used by connecting FM to ADC input port in the processor. Without any external pull down on FM PIN, FM can be switched to one of SBU pins, default is SBU1 and it can be manually switched over to SBU2 if needed. The other SBU2 or SBU1 pin will be open.

If Factory test mode is not needed, pull down(less than  $10 \text{ k}\Omega$ ) or direct connecting to GND makes switch close between SBUx H and SBUx after POR or reset.

#### Manual Mode Control

For switch, there is manual mode switch control for CC and SBU switches. Processor can manually open or close the switch paths in the FUSB251 even though both switches are closed in default with valid VDD. Manual mode switch configuration overrides the auto switch control. However, there are exceptions, such as during moisture detection process and OVP event because switch has to be open in these cases. The switch configuration has to be set in the switch control register and then, bit 0 of control register has to be set.

#### Surge and ESD Protection

The FUSB251 connector facing ports, CCx and SBUx, are designed to endure up to  $\pm 35$ volt surge protection. The voltage can occur when 20 volt DC voltage from VBUS touches the CC and SBU pins with the inductance inside cable. Also, system ESD protection, IEC61000–4–2, is supported with the external capacitor on CAP pin.

#### **Capacitor Recommendation**

The CAP pin needs an external capacitor ranges  $0.1 \,\mu\text{F}$  to  $1.0 \,\mu\text{F}$ . Recommended capacitor type is X7R which has low capacitance variation with temperature change and 0603 or larger size. Also the capacitor rated voltage is important because the voltage on the CAP could be greater than 35 volt with Surge or hot plug in the Type–C cable so 50 volt or larger rated capacitor is recommended.

#### Interrupt Service

FUSB251 has INTB pin to notify processor the status change in the device. Any change in the Interrupt register will trigger the INTB pin which is open drain output. INTB is ready after POR or reset without any register set. Once INTB pin is triggered to low, the pin stays low until the interrupt register is read by processor. The interrupt mask registers are default disabled. If any interrupt mask bit is set, the corresponding interrupt register bit won't set, so INTB pin won't be triggered.

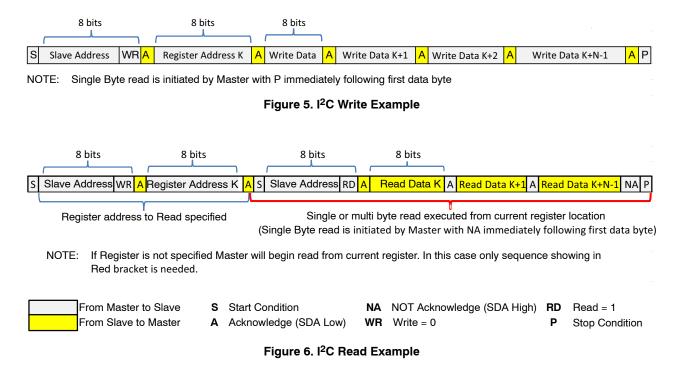

#### I2C Interface

The FUSB251 includes a full I2C slave controller. The I2C slave fully complies with the I2C specification version

6 requirements. This block is designed for fast mode signals. Examples of an  $I^2C$  write and read sequence are shown in below figures respectively.

#### SLAVE ADDRESS

| Part Number | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0     |

|-------------|-------|-------|-------|-------|-------|-------|-------|-----------|

| FUSB251UCX  | 0     | 1     | 0     | 1     | 0     | 0     | 0     | R(1)/W(0) |

#### **Moisture Detection**

#### **CC Moisture Detection**

Moisture detection is default disabled. Once CC moisture detection is enabled, voltage of both CC1\_H and CC2\_H are monitored to see if both CCs rise above 170 mV. If they rise above the voltage, moisture detection started on one of the CC first, and moisture detection on the other CC is occurred at the next both CC rising. If only one of CCs rises up above the threshold, in case of source device attach, CC moisture detection does not start.

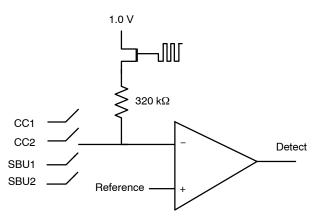

If both CCs cross the threshold, both CC switches are open momentarily, and FUSB251 supplies 1volt source onto one of CCs with 320 k $\Omega$  pull up. And ADC detection is enabled to measure the voltage of the CC channel. Since moisture in connector can make leakage path between the CC pin and other pins including GND, there will be resistance between CC and GND and it can be detected by ADC. Once moisture detection is finished on one CC, the other CC channel is also tried at the next both CC rise. If there is no both CC rise on either CC within 120 ms from the last detection, it will go to timer expire. If source or sink device is attached, the timer will expire. Timer expire is interrupted to host and CC moisture detection stops and moisture detection is continued on SBU float voltage detection instead. To be determined as moisture presence, both CC channels have to be tried and moisture has to be detected on either of channel with no timer expire. If moisture is detected, the result is updated in the register and interrupt is triggered to processor. Regardless of moisture presence on CC, once detection is finished, both CC switches are closed again for Type–C controller to use the CC channel. Moisture detection range can be changed by I2C register, Threshold1 in 0x08. Once the measured resistance is less than the threshold, it will be detected as moisture.

If sink device is attached while host with FUSB251 is on DRP toggle, both CC will rise together, So, CC moisture detection will happen. And, FUSB251 can find the Rd in sink device because the Rd,  $5.1 \text{ k}\Omega$ , is in moisture detection range. But the other CC channel detection will end up as timer expire because there will be no both CC rise after attach. So, the final result will be timer expire and moisture detection will continue on SBU pins.

To support audio and debug accessories which have two terminations on both CC, there is a register bit in the control register, bit7 in 0x02. The register bit makes moisture detection occur on every other both CC rising so moisture detection skips for Type–C detection can happen during the time. Detection time on CC moisture is dependent on the settling time and number of ADC read, default is 1 time ADC and 400  $\mu$ s settle time. They can be programmed in Timer2 register, 0x0C.

#### **SBU Moisture Detection**

If CC port is on DRP or Source mode, moisture inside connector can make leakage path from CC to SBU, which makes SBU can have float voltage similar to the shape of CC. So the SBU float voltage can be detected if moisture is present while CC is on toggle or SRC mode. SBU float voltage detection can be started with the EN\_SBUFT register set. If the bit is set, FUSB251 starts monitoring voltage on both SBU1 and SUB2, and if the voltage on either port is the same or above the threshold, the moisture\_status register (0x06, bit 4 and/or 5) is set with an interrupt. With the interrupt, processor can turn off the CC and SBU switch path to protect from corrosion, or processor could further moisture check using force SBU detection.

SBU float voltage detection also can be enabled when CC moisture detection result is timer expire, which can happen where there is no DRP toggle on CC. For example, if CC moisture detection is enabled where Type–C accessory is already plugged–in, the moisture detection will end up timer expire and so SBU float voltage detection will be started instead.

Once SBU float voltage detection is enabled, it keeps monitoring until moisture found. If device is reset or both EN\_CC and EN\_SBUFT are disabled, the floating detection stops and goes back to disable mode which is idle mode.

Force SBU detection is initiated by EN\_SBU or Auto\_EN\_SBU bit. Auto\_EN\_SBU bit is for pre-set before

moisture is detected, EN\_SBU can be set at anytime when SBU moisture detection is needed. After either CC or SBU float voltage detection detected moisture, if Auto\_EN\_SBU bit is set, FUSB251 goes to moisture detection on SBU with the same way of CC moisture detection, using 1volt source with 320 k $\Omega$  pull up, which is secondary moisture detection using SBU. So, Host processor can use force SBU detection in case CC moisture or SBU float voltage detection result is not enough and additional moisture detection is needed.

Force SBU detection makes open the both CC and SBU switches and detects moisture on SBU. Opening CC switch will disconnect the Type–C device and will remove Vbus from Type–C source. The detection time of SBU force detection is 1msec. Device reset or moisture reset bit can be used to close the CC and SBU switch again.

If moisture is present in connector and if source device provides VBUS, there could be OVP interrupt on SBU by leakage path between Vbus and SBU.

#### **Dry Check**

Dry check routine can be started after moisture is detected by force SBU detection. After moisture detected on SBU, if EN\_DRY bit is enabled, dry check routine is started which is keep checking moisture on SBU every second or up to 10second. The Dry check timer can be set in the register, 0x0A, timer register. Also, the moisture threshold can be set in the Threshold2 register, 0x09. If Dry condition is reached, Interrupt is generated to let host know the change, then processor has to disable all the moisture detection or moisture reset to go to idle mode. If moisture reset bit is set after Dry condition reached, the moisture detection state machine will restart based on control register bits.

Figure 7. Moisture Detection with ADC

### ADC TABLE FOR MOISTURE DETECTION

|    | Bit  | Pull up (k $\Omega$ ) to 1 V | Moisture resistance (k $\Omega$ ) | Voltage (V) |

|----|------|------------------------------|-----------------------------------|-------------|

| 0  | 0    | 320                          | 17                                | 0.05        |

| 1  | 1    | 320                          | 36                                | 0.1         |

| 2  | 10   | 320                          | 56                                | 0.15        |

| 3  | 11   | 320                          | 80                                | 0.2         |

| 4  | 100  | 320                          | 107                               | 0.25        |

| 5  | 101  | 320                          | 137                               | 0.3         |

| 6  | 110  | 320                          | 172                               | 0.35        |

| 7  | 111  | 320                          | 213                               | 0.4         |

| 8  | 1000 | 320                          | 262                               | 0.45        |

| 9  | 1001 | 320                          | 320                               | 0.5         |

| 10 | 1010 | 320                          | 391                               | 0.55        |

| 11 | 1011 | 320                          | 480                               | 0.6         |

| 12 | 1100 | 320                          | 594                               | 0.65        |

| 13 | 1101 | 320                          | 747                               | 0.7         |

| 14 | 1110 | 320                          | 960                               | 0.75        |

| 15 | 1111 | 320                          | 1,280                             | 0.8         |

### **REGISTER MAPPING TABLE**

|         |                 |                |                  |           | Read Only      | Write Only   | Read / Write | Read / Clear    | Write / Clear |  |

|---------|-----------------|----------------|------------------|-----------|----------------|--------------|--------------|-----------------|---------------|--|

| Address | Name            | Bit[7]         | Bit[6]           | Bit[5]    | Bit[4]         | Bit[3]       | Bit[2]       | Bit[1]          | Bit[0]        |  |

| 0x01    | Product ID      |                | [                | Device ID |                | Produ        | uct ID       | Revisio         | in ID         |  |

| 0x02    | Control         | Debug_Acc      | NU               | EN_DRY    | Auto_EN_SBU    | EN_SBUFT     | EN_SBU       | EN_CC           | MAN_SW        |  |

| 0x03    | Interrupt       | 1              | NU               | CC2_Timer | CC1_Timer      | DRY_CHG      | MOS_CHG      | OVP_REC         | OVP           |  |

| 0x04    | Interrupt_Mask  | NU Mask_CC2_Ti |                  |           | Mask_CC1_Timer | Mask_DRY_CHG | Mask_MOS_CHG | Mask_OVP_Rec    | Mask_OVP      |  |

| 0x05    | Status          | LOOK4CC        | LOOK4CC LOOK4SBU |           | NU             |              |              | OVP_SBU         | OVP_CC        |  |

| 0x06    | Moisture Status | F              | ault             | SBU2_FT   | SBU1_FT        | SBU2_MOS     | SBU1_MOS     | CC2_MOS         | CC1_MOS       |  |

| 0x07    | Switch control  |                |                  | NU        |                | 5            |              |                 | CC            |  |

| 0x08    | Threshold1      |                | SBU              | _MOS_DET  |                |              | CC_MOS       | S_DET           |               |  |

| 0x09    | Threshold2      | NU             | SBU_F            | loat_DET  |                | -            | VDRY         |                 |               |  |

| 0x0A    | Timer           | NU             |                  |           |                |              | -            | TDRY(DRY timer) |               |  |

| 0x0B    | RESET           |                |                  |           | NU             |              |              | MOS Reset       | Device reset  |  |

| 0x0C    | Timer2          |                |                  | NU        |                | Number of    | ADC Read     | CC settle       | e time        |  |

#### DEVICE ID Address: 01h Reset Value: 0x100X\_XXXX Type: Read

| Bit # | Name        | R/W/C | Size (Bits) | Description                                      |

|-------|-------------|-------|-------------|--------------------------------------------------|

| 7:4   | Device ID   | R     | 4           | 1000 : OPT_A                                     |

| 3:2   | Product ID  | R     | 2           | 00 : FUSB251UCX(Default)                         |

| 1:0   | Revision ID | R     | 2           | 00 : RevA<br>01 : RevB<br>10 : RevC<br>11 : RevD |

### CONTROL

Address: 02h Reset Value: 0x0000\_0000 Type: Read / Write

| Bit # | Name        | R/W/C | Size (Bits) | Description                                              |

|-------|-------------|-------|-------------|----------------------------------------------------------|

| 7     | Debug_Acc   | R/W   | 1           | 1 : Support Debug_Accessory detection                    |

| 6     | NU          | R     | 1           | 1 : Do not use                                           |

| 5     | EN_DRY      | R/W   | 1           | 1 : Enable Dry check                                     |

| 4     | AUTO_EN_SBU | R/W   | 1           | 1 : Enable Auto_EN_SBU                                   |

| 3     | EN_SBUFT    | R/W   | 1           | 1 : Enable float voltage detection on SBU                |

| 2     | EN_SBU_MOS  | R/W   | 1           | 1 : Enable moisture detection on SBU with voltage source |

| 1     | EN_CC_MOS   | R/W   | 1           | 1 : Enable moisture detection on CC with voltage source  |

| 0     | MAN_SW      | R/W   | 1           | 1 : Enable manual mode switch control                    |

### INTERRUPT

Address: 03h Reset Value: 0x0000\_0000 Type: Read

| Bit # | Name      | R/W/C | Size (Bits) | Description                          |

|-------|-----------|-------|-------------|--------------------------------------|

| 7:6   | NU        | R     | 2           | Do not use                           |

| 5     | CC2_TIMER | R     | 1           | 1 : CC2 Timer interrupt              |

| 4     | CC1_TIMER | R     | 1           | 1 : CC1 Timer interrupt              |

| 3     | DRY_CHG   | R     | 1           | 1 : Dry status change interrupt      |

| 2     | MOS_CHG   | R     | 1           | 1 : Moisture status change interrupt |

| 1     | OVP_REC   | R     | 1           | 1 : OVP Recovery interrupt           |

| 0     | OVP       | R     | 1           | 1 : OVP interrupt                    |

### INTERRUPT\_MASK

Address: 04h Reset Value: 0x0000\_0000 Type: Read / Write

| Bit # | Name           | R/W/C | Size (Bits) | Description                  |

|-------|----------------|-------|-------------|------------------------------|

| 7:6   | NU             | R/W   | 2           | Do not use                   |

| 5     | Mask_CC2_Timer | R/W   | 1           | 1 : Mask CC2 Timer interrupt |

| 4     | Mask_CC1_Timer | R/W   | 1           | 1 : Mask CC1 Timer interrupt |

#### INTERRUPT\_MASK Address: 04h Reset Value: 0x0000\_0000 Type: Read / Write

| 3 | Mask_Dry_Detect | R/W | 1 | 1 : Mask DRY status change interrupt      |

|---|-----------------|-----|---|-------------------------------------------|

| 2 | Mask_MOS_Detect | R/W | 1 | 1 : Mask Moisture status change interrupt |

| 1 | Mask_OVP_REC    | R/W | 1 | 1 : Mask OVP recovery interrupt           |

| 0 | Mask_OVP        | R/W | 1 | 1 : Mask OVP Interrupt                    |

#### STATUS Address: 05h Reset Value: 0x0000\_0000 Type: Read

| Bit # | Name     | R/W/C | Size (Bits) | Description                                                                     |

|-------|----------|-------|-------------|---------------------------------------------------------------------------------|

| 7     | LOOK4CC  | R     | 1           | 1 : Device is monitoring moisture on CC1 or CC2                                 |

| 6     | LOOK4SBU | R     | 1           | 1 : Device is monitoring moisture on SBU1 or SBU2 using float voltage detection |

| 5     | LOOK4DRY | R     | 1           | 1 : Monitoring Dry check on SBU1 and SBU2                                       |

| 3:2   | NU       | R     | 1           | Do not use                                                                      |

| 1     | OVP_SBU  | R     | 1           | 1 : OVP conditions on SBU1 or SBU2                                              |

| 0     | OVP_CC   | R     | 1           | 1 : OVP conditions on CC1 or CC2                                                |

#### MOISTURE\_STATUS Address: 06h

Reset Value: 0x0000\_0000 Type: Read

| Bit # | Name     | R/W/C | Size (Bits) | Description                                                                                                                                                                       |

|-------|----------|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6   | FAULT    | R     | 2           | These bits are set when moisture detection on SBU using volt-<br>age source didn't detect moisture. "01" and "10" will be set with<br>other register bit such as bit0/1 or bit4/5 |

|       |          |       |             | 00 : No moisture detection tried on SBU                                                                                                                                           |

|       |          |       |             | 01 : Moisture was detected on CC but not found on SBU                                                                                                                             |

|       |          |       |             | 10 : Moisture was detected by SBU Float voltage detec-<br>tion(SBUFT) but not found on SBU                                                                                        |

|       |          |       |             | 11 : No moisture detected on both CC and SBU                                                                                                                                      |

| 5     | SBUF2_FT | R     | 1           | 1 : Float voltage detected on SBU2                                                                                                                                                |

| 4     | SBU1_FT  | R     | 1           | 1 : Float voltage detected on SBU1                                                                                                                                                |

| 3     | SBU2_MOS | R     | 1           | 1 : Moisture detected on SBU2                                                                                                                                                     |

| 2     | SBU1_MOS | R     | 1           | 1 : Moisture detected on SBU1                                                                                                                                                     |

| 1     | CC2_MOS  | R     | 1           | 1 : Moisture detected on CC2                                                                                                                                                      |

| 0     | CC1_MOS  | R     | 1           | 1 : Moisture detected on CC1                                                                                                                                                      |

### SWITCH CONTROL

Address: 07h Reset Value: 0x0000\_0000 Type: Read / Write

| Bit # | Name | R/W/C | Size (Bits) | Description |

|-------|------|-------|-------------|-------------|

| 7:3   | NU   | R/W   | 5           | Do not use  |

#### SWITCH CONTROL Address: 07h Reset Value: 0x0000\_0000 Type: Read / Write

| 2:1 | SBU | R/W | 2 | 00 : Open both SBU1 and SBU2 switches<br>01 : SBU1 and SBU2 close to SBU1_H and SBU2_H<br>10 : SBU2 closes to FM, SBU1, SBU1_H and SBU2_H are open<br>11 : SBU1 closes to FM, SBU2, SBU1_H and SBU2_H are open |

|-----|-----|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | СС  | R/W | 1 | 0 : CC1 and CC2 switch are open<br>1 : CC1 and CC2 close to CC1_H and CC2_H                                                                                                                                    |

### THRESHOLD 1

Address: 08h Reset Value: 0x1011\_1011 Type: Read / Write

| Bit # | Name        | R/W/C | Size (Bits) | Description                                                             |

|-------|-------------|-------|-------------|-------------------------------------------------------------------------|

| 7:4   | SBU_MOS_DET | R/W   | 4           | 0000 : 17 kΩ<br>0001 : 36 kΩ<br><br>1011 : 480 kΩ<br><br>1111 : 1280 kΩ |

| 3:0   | CC_MOS_DET  | R/W   | 4           | 0000 : 17 kΩ<br>0001 : 36 kΩ<br><br>1011 : 480 kΩ<br><br>1111 : 1280 kΩ |

### **THRESHOLD 2**

Address: 09h Reset Value: 0x0001\_1101 Type: Read / Write

| Bit # | Name          | R/W/C | Size (Bits) | Description                                                                                                                  |

|-------|---------------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------|

| 7     | NU            | R     | 1           | Do not use                                                                                                                   |

| 6:4   | SBU_Float_DET | R/W   | 3           | 000 : 100 mV<br>001 : 200 mV<br>010 : 300 mV<br>011 : 400 mV<br>100 : 500 mV<br>101 : 600 mV<br>110 : 700 mV<br>111 : 800 mV |

| 3:0   | VDRY          | R/W   | 4           | 0000 : 17 kΩ<br>0001 : 36 kΩ<br><br>1101 : 747 kΩ<br><br>1111 : 1280                                                         |

#### TIMER Address: 0Ah Reset Value: 0x0000\_0100 Type: Read / Write

| Bit # | Name | R/W/C | Size (Bits) | Description                                                                                                             |

|-------|------|-------|-------------|-------------------------------------------------------------------------------------------------------------------------|

| 7:3   | NU   | R     | 5           | Do not use                                                                                                              |

| 2:0   | TDRY | R/W   | 3           | 000 : 50 ms<br>001 : 100 ms<br>010 : 250 ms<br>011 : 1 sec<br>100 : 2 sec<br>101 : 4 sec<br>110 : 8 sec<br>111 : 10 sec |

### RESET

Address: 0Bh Reset Value: 0x0000\_0100 Type: Read / Write

| Bit # | Name      | R/W/C | Size (Bits) | Description                                                                                                                                                                                                                                          |

|-------|-----------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2   | NU        | R     | 6           | Do not use                                                                                                                                                                                                                                           |

| 1     | MOS Reset | R/W/C | 1           | 1 : Reset moisture detection state machine and clear moisture status, Read returns '0'.                                                                                                                                                              |

|       |           |       |             | This register bit resets moisture detection state machine and<br>moisture status register is cleared. Control register is not affected<br>by this bit. If any moisture detection enable bit was set, moisture<br>detection will restart by MOS Reset |

| 0     | Reset     | R/W/C | 1           | 1 : Reset the device, Read returns '0'<br>The Device Reset includes FM pin configuration so FM pin status<br>is checked after this Reset                                                                                                             |

### TIMER2

Address: 0Ch Reset Value: 0x0000\_0100 Type: Read / Write

| Bit # | Name               | R/W/C | Size (Bits) | Description                                                                |

|-------|--------------------|-------|-------------|----------------------------------------------------------------------------|

| 7:4   | NU                 | R     | 4           | Do not use                                                                 |

| 3:2   | Number of ADC Read | R/W   | 2           | 00 : 1 time<br>01 : 2 times<br>10 : 3 timers<br>11 : Do not use(no change) |

| 1:0   | CC Settle time     | R/W   | 2           | <b>00 : 400 μs</b><br>01 : 300 μs<br>10 : 500 μs<br>11 : 600 μs            |

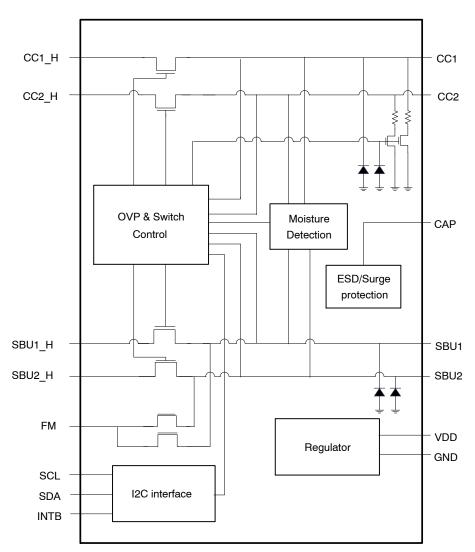

### **APPLICATION CIRCUIT**

Figure 8. Application Circuit

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 98AON94758G              | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | WLCSP15, 1.49x2.06x0.574 |                                                                                                                                                                                     | PAGE 1 OF 1 |

| ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                          |                                                                                                                                                                                     |             |

© Semiconductor Components Industries, LLC, 2018

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>