# ON Semiconductor®

# CMOS LSI RDS復調LSI

http://onsemi.jp

### 概要

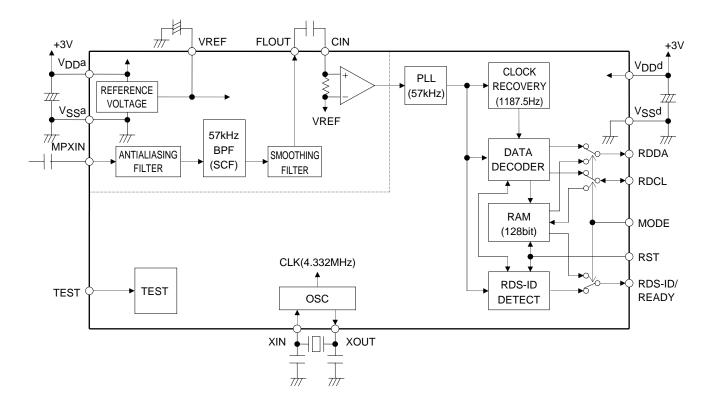

LC72725KVは、RDS(Radio Data System)信号復調処理用LSIである。

このLSIはBPF復調回路およびデータバッファを内蔵しており、RDSデータを外部からのクロック入力により読み出すこと(スレーブ動作)が可能である。RDSクロック出力に同期して読み出すマスタ動作も可能である。

### 機能

・BPF : スイッチド・キャパシタ・フィルタ(SCF)

・RDS復調 : 57KHzキャリア再生・クロック再生

バイフェーズデコード・差動デコード

・バッファ : 128ビット(約100ms)のデータ保存可能

・データ出力 :マスタ/スレーブ読みだし切換え

・RDS-ID検出 : IDリセット可能・スタンバイ制御 : 水晶発振回路停止

・低電圧対応 ・完全無調整

# 絶対最大定格/Ta=25 ,VSSd=VSSa=0V

| 項目     | 記号                    | 端子名                                  | 条件                                         | 定格値                             | unit |

|--------|-----------------------|--------------------------------------|--------------------------------------------|---------------------------------|------|

| 最大電源電圧 | V <sub>DD</sub> max   | V <sub>DD</sub> d, V <sub>DD</sub> a | V <sub>DD</sub> a V <sub>DD</sub> d + 0.3V | - 0.3~ +6.5                     | V    |

| 最大入力電圧 | V <sub>IN</sub> 1 max | TEST, MODE, XIN, RDCL, RST           |                                            | - 0.3 ~ V <sub>DD</sub> d + 0.3 | V    |

|        | V <sub>IN</sub> 2 max | MPXIN,CIN                            |                                            | - 0.3 ~ V <sub>DD</sub> a + 0.3 | V    |

| 最大出力電圧 | V <sub>0</sub> 1 max  | RDS-ID(READY)                        |                                            | - 0.3~ +6.5                     | V    |

|        | V <sub>O</sub> 2 max  | XOUT, RDDA, RDCL                     |                                            | - 0.3 ~ V <sub>DD</sub> d + 0.3 | V    |

|        | V <sub>0</sub> 3 max  | FLOUT                                |                                            | - 0.3 ~ V <sub>DD</sub> a + 0.3 | V    |

| 最大出力電流 | I <sub>0</sub> 1 max  | XOUT, FLOUT, RDDA, RDCL              |                                            | +2.0                            | mA   |

|        | I <sub>O</sub> 2 max  | RDS-ID(READY)                        |                                            | +8.0                            | mA   |

| 許容消費電力 | Pd max                |                                      | Ta 85                                      | 100                             | mW   |

| 動作周囲温度 | Topr1                 |                                      | V <sub>DD</sub> =2.7V ~ 5.5V               | - 20 ~ + 70                     |      |

|        | Topr2                 |                                      | V <sub>DD</sub> =3.0V ~ 5.5V               | - 40 ~ + 85                     |      |

| 保存周囲温度 | Tstg                  |                                      |                                            | - 40 ~ + 125                    |      |

ただし、VDDa VDDd+0.3V

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。最大定格は、ストレス印加に対してのみであり、推奨動作条件を超えての機能 的動作に関して意図するものではありません。推奨動作条件を超えてのストレス印加は、デバイスの信頼性に影響を与える危険性があります。

許容動作範囲/Ta= - 20 ~ +70 , VSSd=VSSa=0V, VDDd=VDDa=2.7V ~ 5.5V

$/Ta=-40 \sim +85 \quad , VSSd=VSSa=0 \\ V, VDDd=VDDa=3.0 \\ V \sim 5.5 \\ V$

| 項目                | 記号                | 端子名                                 | 条件              | min                  | typ   | max                           | un i t |

|-------------------|-------------------|-------------------------------------|-----------------|----------------------|-------|-------------------------------|--------|

| 電源電圧              | V <sub>DD</sub> 1 | V <sub>DD</sub> d,V <sub>DD</sub> a | Ta= - 20 ~ + 70 | 2.7                  |       | 5.5                           | V      |

|                   | V <sub>DD</sub> 2 | V <sub>DD</sub> d,V <sub>DD</sub> a | Ta= - 40 ~ +85  | 3.0                  |       | 5.5                           | V      |

| 入力「H」レベル電圧        | V <sub>IH</sub> 1 | TEST, MODE, RST                     |                 | 0.7V <sub>DD</sub> d |       | 6.5                           | V      |

|                   | V <sub>IH</sub> 2 | RDCL                                |                 | 0.7V <sub>DD</sub> d |       | $V_{\mbox{\scriptsize DD}} d$ | V      |

| 入力「L」レベル電圧        | VIL               | TEST, MODE, RST, RDCL               |                 | 0                    |       | 0.3V <sub>DD</sub> d          | ٧      |

| 出力電圧              | V <sub>0</sub> 1  | RDDA, RDCL                          |                 |                      |       | V <sub>DD</sub> d             | V      |

|                   | V <sub>0</sub> 2  | RDS-ID(READY)                       |                 |                      |       | 6.5                           | V      |

| 入力振幅              | VIN               | MPXIN                               | f=57 ± 2kHz     | 1.6                  |       | 50                            | mVrms  |

|                   | VXIN              | XIN                                 |                 | 400                  |       | 1500                          | mVrms  |

| 発振保証水晶振動子         | Xtal              | XIN,XOUT                            | CI 120Ω         |                      | 4.332 |                               | MHz    |

| 水晶発振周波数偏差         | TXtal             | XIN,XOUT                            | Fo=4.332MHz     |                      |       | ± 100                         | ppm    |

| RDCL セットアップ<br>時間 | tCS               | RDCL,RDDA                           |                 | 0                    |       |                               | μs     |

| RDCL「H」レベル時間      | tCH               | RDCL                                |                 | 0.75                 |       |                               | μs     |

| RDCL「L」レベル時間      | tCL               | RDCL                                |                 | 0.75                 |       |                               | μs     |

| データ出力時間           | tDC               | RDCL,RDDA                           |                 |                      |       | 0.75                          | μs     |

| READY 出力時間        | tRC               | RDCL, READY                         |                 |                      |       | 0.75                          | μs     |

| READY「L」レベル時間     | tRL               | READY                               |                 |                      |       | 107                           | ms     |

# 電気的特性/許容動作条件において

| 項目            | 記号                | 端子名                                   | 条件                                                                                | min                     | typ                  | max  | unit |

|---------------|-------------------|---------------------------------------|-----------------------------------------------------------------------------------|-------------------------|----------------------|------|------|

| 入力抵抗値         | Rmpxin            | MPXIN-V <sub>SS</sub> a               | f=57kHz                                                                           |                         | 100                  |      | kΩ   |

|               | Rcin              | CIN-V <sub>SS</sub> a                 | f=57kHz                                                                           |                         | 100                  |      | kΩ   |

| 内蔵帰還抵抗        | Rf                | XIN                                   |                                                                                   |                         | 1.0                  |      | MΩ   |

| 中心周波数         | fc                | FLOUT                                 |                                                                                   | 56.5                    | 57.0                 | 57.5 | kHz  |

| - 3dB 帯域幅     | BW - 3dB          | FLOUT                                 |                                                                                   | 2.5                     | 3.0                  | 3.5  | kHz  |

| 増幅度           | Gain              | MPXIN-FLOUT                           | f=57kHz                                                                           | 28                      | 31                   | 34   | dB   |

| 阻止域減衰量        | Att1              | FLOUT                                 | $\Delta f = \pm 7 \text{kHz}$                                                     | 30                      |                      |      | dB   |

|               | Att2              | FLOUT                                 | f < 45kHz, f > 70kHz                                                              | 40                      |                      |      | dB   |

|               | Att3              | FLOUT                                 | f < 20kHz                                                                         | 50                      |                      |      | dB   |

| 基準電圧出力        | Vref              | Vref                                  | V <sub>DD</sub> a=3V                                                              |                         | 1.5                  |      | ٧    |

| ヒステリシス幅       | VHIS              | TEST, MODE, RST, RDCL                 |                                                                                   |                         | 0.1V <sub>DD</sub> d |      | V    |

| 出力「L」レベル電圧    | V <sub>OL</sub> 1 | RDDA, RDCL                            | I=2mA                                                                             |                         |                      | 0.4  | V    |

|               | V <sub>0L</sub> 2 | RDS-ID(READY)                         | I=8mA                                                                             |                         |                      | 0.4  | V    |

| 出力「H」レベル電圧    | VOH               | RDDA, RDCL                            | I=2mA                                                                             | V <sub>DD</sub> d - 0.4 |                      |      | V    |

| 入力「H」レベル電流    | I <sub>IH</sub> 1 | TEST, MODE, RST, RDCL                 | V <sub>1</sub> =6.5V                                                              |                         |                      | 5.0  | μΑ   |

|               | I <sub>IH</sub> 2 | XIN                                   | VI=NDDq                                                                           | 2.0                     |                      | 11   | μΑ   |

| 入力「L」レベル電流    | I <sub>IL</sub> 1 | TEST, MODE, RST, RDCL                 | V <sub>I</sub> =0V                                                                |                         |                      | 5.0  | μΑ   |

|               | 1 <sub>1</sub> L2 | XIN                                   | V1=0V                                                                             | 2.0                     |                      | 11   | μΑ   |

| 出力オフリーク<br>電流 | IOFF              | RDS-ID(READY)                         | V <sub>0</sub> =6.5V                                                              |                         |                      | 5.0  | μΑ   |

| 消費電流          | I <sub>DD</sub>   | V <sub>DD</sub> d + V <sub>DD</sub> a | V <sub>DD</sub> d + V <sub>DD</sub> a<br>(V <sub>DD</sub> d=V <sub>DD</sub> a=3V) |                         | 5                    |      | mA   |

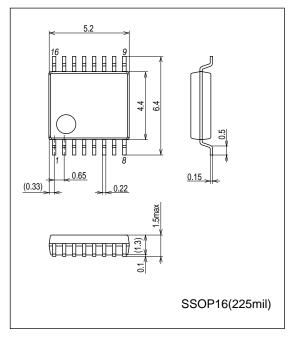

# 外形図

unit:mm (typ)

3178B

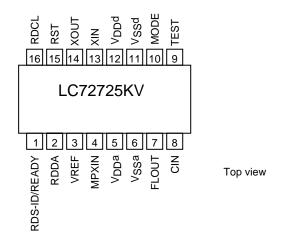

# ピン配置図

# ブロック図

| 端   | フ 높出 | $\Box$ |

|-----|------|--------|

| ルボー | 一試   | 明      |

|     |      |        |

| 端子説明     |                   |     |                                                                                |                                                        |

|----------|-------------------|-----|--------------------------------------------------------------------------------|--------------------------------------------------------|

| 端子<br>番号 | 端子名               | 1/0 | 端子機能                                                                           | 端子形式                                                   |

| 3        | VREF              | 出力  | 基準電圧出力(VDDa/2)                                                                 | V <sub>DD</sub> a A                                    |

| 4        | MPXIN             | 入力  | ベースバンド(マルチプレックス)信号入力                                                           | V <sub>DD</sub> d<br>V <sub>SS</sub> d                 |

| 7        | FLOUT             | 出力  | サブキャリア出力(フィルタ出力)                                                               |                                                        |

| 8        | CIN               | 入力  | サブキャリア入力(コンパレータ入力)                                                             | V <sub>DD</sub> a<br>V <sub>SS</sub> a /// VREF        |

| 5        | V <sub>DD</sub> a | -   | アナログ系電源(+3V)                                                                   |                                                        |

| 6        | Vssa              | -   | アナログ系グランド                                                                      |                                                        |

| 14       | XOUT              | 出力  | 水晶発振出力(4.332MHz)                                                               | V <sub>DD</sub> d                                      |

| 13       | XIN               | 入力  | 水晶発振入力(外部基準信号入力)                                                               | XIN VSSd XOUT                                          |

| 9        | TEST              |     | テスト入力                                                                          | □ <b>→</b> S                                           |

| 10       | MODE              |     | 読みだしモード設定(0:マスタ,1:スレーブ)                                                        | _ * ~                                                  |

| 15       | RST               |     | RDS-ID/RAM リセット(正極性)                                                           | /// V <sub>SS</sub> d                                  |

| 2        | RDDA              | 出力  | RDS データ出力                                                                      | ↑ V <sub>DD</sub> d<br>→ →<br>→<br>→ V <sub>SS</sub> d |

| 16       | RDCL              | 入出力 | RDS クロック出力(マスタモード)/<br>RDS クロック入力(スレーブモード)                                     | VDDd<br>VSSd                                           |

| 1        | RDS-ID/<br>READY  | 出力  | RDS 信頼度データ出力/READY 出力<br>(RDS-ID は High: RDS 信頼度が高いデータ、<br>Low: RDS 信頼度が低いデータ) | V <sub>SS</sub> d ////                                 |

| 12       | V <sub>DD</sub> d | 1   | デジタル系電源(+3V)                                                                   |                                                        |

| 11       | V <sub>SS</sub> d | -   | デジタル系グランド                                                                      |                                                        |

| _        |                   |     |                                                                                |                                                        |

# 入出力の説明

| TEST | MODE | 回路動作モード             | RDCL 端子 | RDS-ID/READY 端子 |

|------|------|---------------------|---------|-----------------|

| 0    | 0    | マスタ動作モード            | クロック出力  | RDS-ID 出力       |

| 0    | 1    | スレーブ動作モード           | クロック入力  | READY 出力        |

| 1    | 0    | スタンバイモード (水晶発振停止)   | -       | -               |

| 1    | 1    | LSI テストモード(ユーザ設定不可) | -       | -               |

|       | RST 端子                                  |  |  |  |

|-------|-----------------------------------------|--|--|--|

| RST=0 | 通常動作                                    |  |  |  |

| RST=1 | RDS-ID・復調回路クリア + READY・メモリクリア(スレーブモード時) |  |  |  |

| RDS-ID/READY 端子 |                               |  |  |

|-----------------|-------------------------------|--|--|

| マスタ動作時          | RDS-ID 出力(Active-high)        |  |  |

| スレーブ動作時         | 読み出しデータ READY 出力(Active-high) |  |  |

注意: RDS-ID(READY)端子はNchオープンドレイン端子となっており、プルアップ抵抗を接続することによりデータが出力される。

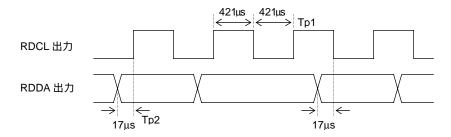

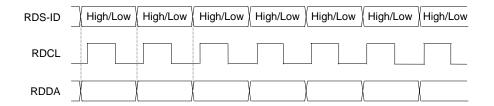

### RDCL/RDDA 出力タイミング

### ・マスタ動作モードの場合

### RDS-ID の出力タイミング

注意: RDS-IDはHigh: RDS信頼度が高いデータ Low: RDS信頼度が低いデータ

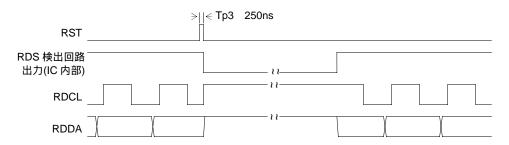

### RST の動作

# ・マスタ動作モードの場合

注意:RST入力後、IC内部のRDS検出回路出力がIow highまでRDCL,RDDA出力はhighレベルでストップする。

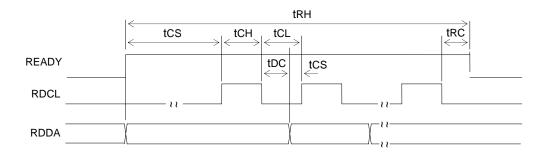

# スレーブ動作モード時の RDCL 制御

| 項目            | 記号  | 端子          | 条件 | min  | typ | max  | un i t |

|---------------|-----|-------------|----|------|-----|------|--------|

| RDCL セットアップ時間 | tCS | RDCL, RDDA  |    | 0    |     |      | μs     |

| RDCL「H」レベル時間  | tCH | RDCL        |    | 0.75 |     |      | μs     |

| RDCL「L」レベル時間  | tCL | RDCL        |    | 0.75 |     |      | μs     |

| データ出力時間       | tDC | RDCL, RDDA  |    |      |     | 0.75 | μs     |

| READY 出力時間    | tRC | RDCL, READY |    |      |     | 0.75 | μs     |

| READY「H」レベル時間 | tRH | READY       |    |      |     | 107  | ms     |

- 注意:1.READY信号がHighとなってから、RDCLクロック入力を開始する。READY状態がLowの時、RDCL はLowレベルで待機すること。

- 2.RDCL入力をLow High Lowと行うごとに、RDCLがLowとなってからtRC時間以降のタイミングで、READYレベルを確認し、もしHighの時は次のRDCLクロック入力を続行する。もしREADYがLowの時はRDCL入力をその時点で停止する。

- 3.上記タイミングを満足するとき、RDDAはRDCLの立ち上がりまたは立ち下がりどちらのタイミングでも取り込むことができる。

- 4.READY信号はメモリ上の最後のデータを読み込んだ後、RDCLの立ち下がりからtRC時間後に Lowになる。また、1ビットでもメモリにデータが書き込まれればHighになりデータ読み出 しが可能。

- 5.チャネル切換え時には、直後にRST入力によりメモリおよびREADYリセットを行うことが 望ましい。

そうでないと、メモリ上に前チャネルの受信データが残ることがある。RST入力を行うと、メモリにはRDS-IDが検出されるまでデータは書き込まれず、従ってREADY信号はRDS-ID検出後にHighとなる。(スレーブ動作時にはRDS-IDは出力されないが、IC内部では検出している。)RST入力後、一旦RDS-IDが検出されると、それ以降の受信データはRDS-IDの検出状況にかかわらずメモリに書き込まれる。

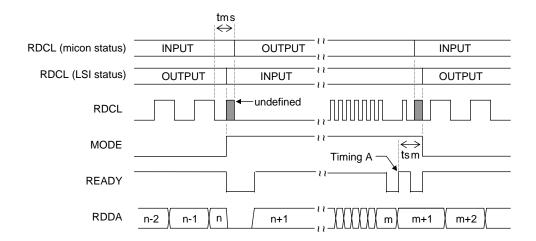

- 6.読み出し途中で、読み出しモードをマスタ/スレーブに切換えることができる。 この場合、データの連続性を保つためには以下の点に注意することが必要である。

- (1)マスタ時データ取り込みタイミング RDCLの立ち下がりタイミングでデータを取り込むこと。

- (2)マスタ スレーブ切換えタイミング

RDCL出力がLowになってRDDAデータを取り込んでから、直ちにMODEをHighにした後、マイコンからRDCL信号(Low)を出力開始する。RDCLがLowとなってから840μs(tms)以内にマイコンからのRDCL出力が開始されねばならない。この場合最後にマスタモードで読み出したデータがn番目のデータとすると、n+1番目のデータからメモリに書き込まれる。

(3)スレーブ マスタ切換えタイミング

メモリデータを一旦全て読み込みREADYがLowとなってから、次にもう一度READYがHigh になるまで待ち(Timing A)、直ちにデータを1bit読み出してRDCLクロックを入力する。その後READYがLowとなった時点でマイコンからのRDCL出力は終了し、その後MODEをLow とする。READYがHighとなって(Timing A)から840 $\mu$ s(tsm)以内にMODEをLowに切換えねばならない。

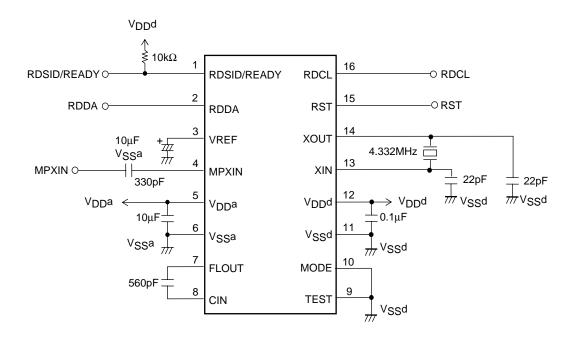

### 応用接続例(マスタ動作モードの場合)

注意事項: RST端子を未使用の場合、グランドに接続すること。

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equ

のN Semiconductor及びONのロゴはSemiconductor Components Industries, LLC (SCILLC)の登録商標です。SCILLCは持許、商標、著作権、トレードシークレット(営業秘密)と他の知的所有権に対する権利を保有します。SCILLCの製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLCは通告なしで、本書記載の製品の変更を行うことがあります。SCILLCは、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害に対して、いかなる責任も負うことはできません。SCILLCデータシートや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあり、実際の性能も時間の経過により変化する可能性があります。「標準的」パラメータを含むすべての動作パラメータは、ご使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致します。SCILLCは、その特許権やその他の権利の下、いかなるライセンスも許諾しません。SCILLC製品は、人体への外科的移植を目的とするシステムへの使用、生命維持を目的としたアプリケーション、また、SCILLC製品の不具合による死傷等の事故が起こり得るようなアプリケーションなどへの使用を意図した設計はされておらず、また、これらを使用対象としておりません。お客様が、このような意図されたものではない、許可されていないアプリケーション用にSCILLC製品を購入または使用した場合、たとえ、SCILLCがその部品の設計または製造に関して過失があったと主張されたとしても、そのような意図せぬ使用、また未許可の使用に関連した死傷等から、直接、又は間接的に生じるすべてのクレーム、費用、損害、経費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、SCILLCとその役員、従業員、子会社、関連会社、代理店に対して、いかなる損害も与えないものとします。

SCILLCは雇用機会均等/差別撤廃雇用主です。この資料は適用されるあらゆる著作権法の対象となっており、いかなる方法によっても再販することはできません。