# Serial Flash Memory 2 Mb (256K x 8)

ON Semiconductor®

www.onsemi.jp

# 概要

LE25U20AMB は、2M bit (256K×8 ビット構成)の SPI バス対応のフラッシュメモリで、2.5 V 単一電源となっている。シリアルフラッシュメモリの特長を生かし、8 pin パッケージに収納されている。この特長から、携帯情報機器などの小型化が要求されるアプリケーションのプログラム格納に最適である。また、小セクターイレーズ機能により、比較的書き換え回数が少なく、EEPROM では容量不足となるパラメータやデータ格納にも適している。

SOIC-8 / SOP8K (200 mil)

# 特長

・2.5 V 単一電源によるリード/ライト動作が可能:

電源電圧範囲 2.30 V~3.60 V

・動作周波数 : 30 MHz・温度範囲 : -40~+85°C

・シリアルインタフェース : SPI Mode0, Mode3 対応

・セクタサイズ :4K バイト/小セクタ, 64K バイト/セクタ

・ 小セクタイレーズ, セクタイレーズ, チップイレーズ機能

ページプログラム機能: 256 バイト/ページ

ブロックプロテクト機能

・ステータス機能 : レディー/ビジー情報, プロテクト情報

・高信頼性リード/ライト

書換え回数 : 100,000 回

小セクタイレーズ時間 : 40 ms (typ), 150ms(max)セクタイレーズ時間 : 80 ms (typ), 250ms(max)チップイレーズ時間 : 250 ms (typ), 1.6s(max)

ページプログラム時間 : 4.0 ms / 256 バイト(typ), 5.0 ms / 256 バイト(max)

データ保持期間 : 20 年

・パッケージ : SOP8K (200 mil)

この製品は米国 SST 社(Silicon Storage Technology, Inc.)のライセンスを受けています。

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 21 of this data sheet.

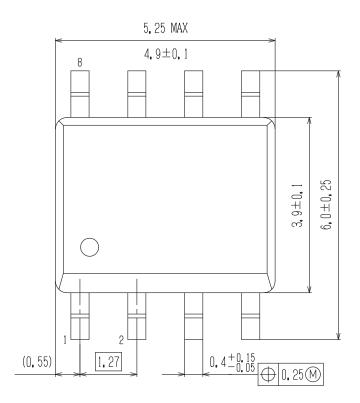

外形図 unit: mm

SOIC-8 / SOP8K (200 mil) CASE 751CV ISSUE O

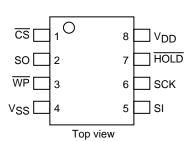

図1:ピン配置図

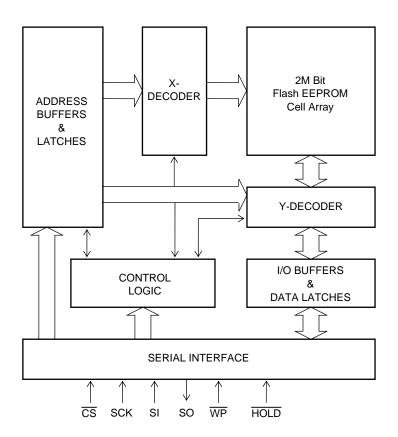

# 図2:ブロック図

表 1: 端子説明

| <u>X · · · ·</u>  | 加丁凯叻      |                                         |

|-------------------|-----------|-----------------------------------------|

| 記号                | 端子名       | 機能                                      |

| SCK               | シリアルクロック  | データの入出力タイミングを制御するピン。                    |

|                   |           | 立ち上がりに同期して入力データやアドレスをラッチし、立ち下がりに同期して    |

|                   |           | データを出力する。                               |

| SI                | シリアルデータ入力 | このピンからデータやアドレスが入力され、シリアルクロックの立ち上がりに同    |

|                   |           | 期して内部にラッチされる。                           |

| S0                | シリアルデータ出力 | シリアルクロックの立ち下がりに同期して、このピンからデバイス内部に格納さ    |

|                   |           | れたデータが出力される。                            |

| CS                | チップセレクト   | このピンが論理低レベルの時、デバイスはアクティブとなる。            |

|                   |           | このピンが論理高レベルの時、デバイスは非選択となりスタンバイ状態となる。    |

| WP                | ライトプロテクト  | このピンが論理低レベルの時、ステータスレジスタライトプロテクト SRWP が有 |

|                   |           | 効となる。                                   |

| HOLD              | ホールド      | このピンが論理低レベルの時、シリアルコミュニケーションが中断される。      |

| $v_{\mathrm{DD}}$ | 電源        | 電源電圧 2.30V~3.60V を供給する。                 |

| $v_{SS}$          | 接地        | 電源電圧 OV を供給する。                          |

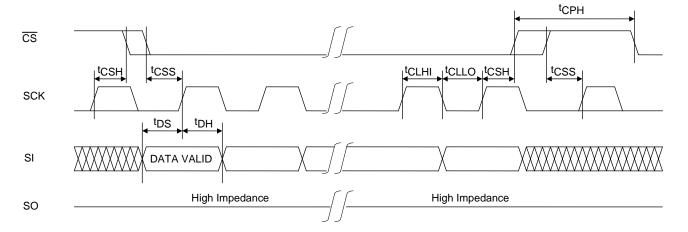

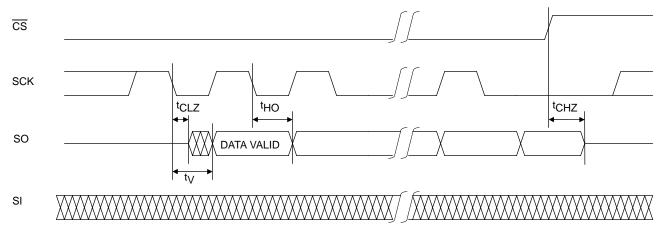

#### デバイス動作

LE25U20AMB はシリアルインタフェースに対応した工業標準の EPROM の機能に、2.5~V 単一電源による電気的なオンチップ消去を追加した製品である。チップ内にコマンドレジスタを内蔵することによりインタフェースおよび制御が容易になっている。デバイスのリード、イレーズ、プログラムおよびその他必要な機能は、コマンドレジスタを介して実行される。表 2: コマンド設定に従って入力されたコマンドのアドレスおよびデータは、必要な動作を行うためデバイス内部にラッチされる。図 3: シリアル入力タイミングにシリアルデータの入力のタイミング波形を示す。まず、 $\overline{CS}$ が立ち下がるとデバイスが選択され、コマンドやアドレス等がシリアルに入力可能となる。それらの入力は、 $\overline{SC}$ Kの立ち上がりに同期し $\overline{B}$ it7から順次内部にとり込まれる。この時、出力端子 $\overline{SO}$ 0 は高インピーダンス状態となっている。出力端子が低インピーダンス状態になるのは、リード、ステータスレジスタリードとシリコン  $\overline{D}$ 0 の時で、クロックの立ち下がりに同期してデータが $\overline{B}$ it7 から順次出力される。シリアル出力タイミングについては、図  $\overline{A}$ 1: シリアル出力タイミングを参照すること。LE25U20AMB はシリアルインタフェース  $\overline{SO}$ 1 mode0 と  $\overline{SO}$ 1 mode3 の双方に対応している。 $\overline{CS}$ 3 が 自動的に選択される。

表 2:コマンド設定

| <u>X-:</u> |         |         |        |       |      |      |        |

|------------|---------|---------|--------|-------|------|------|--------|

| コマンド       | 第1バス    | 第2バス    | 第3バス   | 第4バス  | 第5バス | 第6バス | 第 n バス |

|            | サイクル    | サイクル    | サイクル   | サイクル  | サイクル | サイクル | サイクル   |

| リード        | 03h     | A23-A16 | A15-A8 | A7-A0 |      |      |        |

| 9 · R      | 0Bh     | A23-A16 | A15-A8 | A7-A0 | X    |      |        |

| 小セクタイレーズ   | D7h/20h | A23-A16 | A15-A8 | A7-A0 |      |      |        |

| セクタイレーズ    | D8h     | A23-A16 | A15-A8 | A7-A0 |      |      |        |

| チップイレーズ    | C7h     |         |        |       |      |      |        |

| ページプログラム   | 02h     | A23-A16 | A15-A8 | A7-A0 | PD * | PD * | PD *   |

| ライトイネーブル   | 06h     |         |        |       |      |      |        |

| ライトディセーブル  | 04h     |         |        |       |      |      |        |

| パワーダウン     | B9h     |         |        |       |      |      |        |

| ステータス      | 05h     |         |        |       |      |      |        |

| レジスタリード    | USII    |         |        |       |      |      |        |

| ステータス      | 0.11    | DATA    |        |       |      |      |        |

| レジスタライト    | 01h     | DATA    |        |       |      |      |        |

| シリコン       | OE!     |         |        |       |      |      |        |

| ID リード 1   | 9Fh     |         |        |       |      |      |        |

| シリコン       | A DI-   | v       | v      | v     |      |      |        |

| ID リード2    | ABh     | X       | X      | X     |      |      |        |

| パワーダウン     | ABh     |         |        |       |      |      |        |

| からの抜け出し    | ADII    |         |        |       |      |      |        |

# 表2の説明:

X は don't care つまり、いずれの値を入力してもかまわないという意味である。

各コードの後ろの h は 16 進の数値を表記していることを意味する。

すべてのコマンドについて A23-A18 は don't care となる。

リードコマンド以外でコマンドを認識させるためには、全てのバスサイクル入力後CSを立ち上げる必要がある。

\*PD:ページプログラムデータ。

# 図3:シリアル入力タイミング

# 図4:シリアル出力タイミング

# コマンドと動作説明

表 2: コマンド設定にコマンドのリストと概要を示す。それぞれのコマンドに対応する機能と動作 の詳細な説明を次に示す。

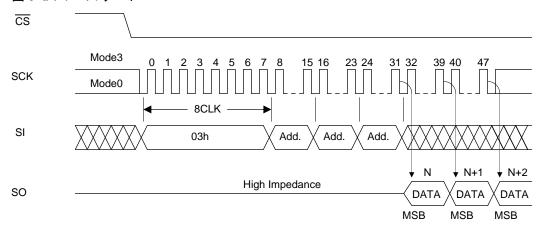

# 1. リード

リードコマンドには、4 バスリードコマンドと 5 バスリードコマンドの 2 種類がある。このうち 4 バスリードコマンドは、第 1 バスサイクルから第 4 バスサイクルで構成され、(03h) に続けて 24 ビットのアドレスを入力する仕様となっており、指定したアドレスのデータが SCK に同期して出力される。データの出力は、第 4 バスサイクル Bit0 の立ち下がりクロックを基準に SO から出力される。図 5-a: 4 バスリードにタイミング波形を示す。

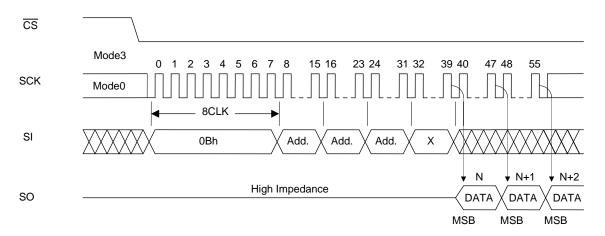

5 バスリードは、第 1 バスサイクルから第 5 バスサイクルで構成され、(0Bh) に続けて 24 ビットのアドレスと 8 ビットのダミービットを入力する。データ出力は、第 5 バスサイクル Bit0 の立ち下がりクロックを基準に 50 から出力される。図 5-b:5 バスリードにタイミング波形を示す。これら 2 つのコマンドの違いは、第 5 バスサイクルでのダミービット入力が有るか無いかの違いのみとなっている。

リードコマンドを入力し、指定したアドレスのデータを出力した後に SCK を入力し続けると、SCK を入力している期間中デバイス内部でアドレスを自動的にインクリメントして、それに対応したデータを順に出力する。クロックの入力を続け、内部のアドレスが最上位アドレス (3FFFFh) に達しデータが出力された後、なおも SCK の入力が続く場合、内部のアドレスは最下位アドレス (00000h) に戻ってデータの出力が続く。 CSを論理高レベルにすることで、デバイスは非選択になり、リードサイクルは終了する。デバイスの非選択時は、出力端子 SO は高インピーダンスの状態となる。

# 図 5-a:4バスリード

#### 図 5-b:5 バスリード

# 2. ステータスレジスタ

ステータスレジスタとは、デバイスの内部の動作状態や設定状態を保持しており、その情報の読み出し(ステータスレジスタリード)や、プロテクト情報の書き換え(ステータスレジスタライト)が可能である。レジスタは全部で8ビットあり、それぞれのビットの意味を表3:ステータスレジスタに示す。

表 3: ステータスレジスタ

| ビット    | 名称   | 論理 | 機能                                    | 電源投入時          |

|--------|------|----|---------------------------------------|----------------|

| D:+0   | DDV  | 0  | レディー状態                                | 0              |

| Bit0   | RDY  | 1  | イレーズ/プログラム状態                          | 0              |

| D:+1   | WIEN | 0  | ライト禁止状態                               | 0              |

| Bit1   | WEN  | 1  | ライト可能状態                               | 0              |

| Bit2   | BP0  | 0  | ブロッカプラニカ 1 桂却                         | 不揮発情報          |

|        |      | 1  | ブロックプロテクト情報<br>ステータスレジスタ BPO, BP1 の項、 | /1/1平分门月前      |

| D: 49  |      | 0  | メノーダスレンスダ bru, br1 の頃、<br>参照          | <b>了</b> ₩% 桂却 |

| Bit3   |      | 1  | <b>参照</b>                             | 不揮発情報          |

| Bit4   |      |    |                                       | 0              |

| Bit5   |      |    | リザーブビット                               | 0              |

| Bit6   |      |    |                                       | 0              |

| D: . T | CDWD | 0  | ステータスレジスタライト可能状態                      | 工任水柱和          |

| Bit7   | SRWP | 1  | ステータスレジスタライト禁止状態                      | 不揮発情報          |

# 2-1. ステータスレジスタリード

ステータスレジスタリードにより、ステータスレジスタの内容を読み出すことができる。ステータスレジスタリードは、下記の動作中にも行うことが可能である。

- ・小セクタイレーズ、セクタイレーズ、チップイレーズ

- ・ページプログラム

- ステータスレジスタライト

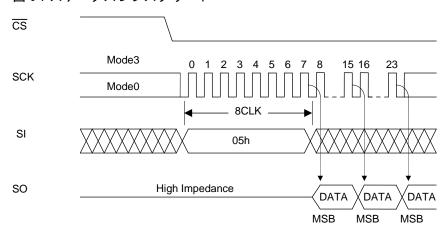

図 6:ステータスレジスタリードにステータスレジスタリードのタイミング波形を示す。ステータスレジスタコマンドは、第1バスサイクルのみで構成され、(05h)の8ビット目を入力したクロック (SCK)の立ち下りに同期して、ステータスレジスタの内容が出力される。出力される順序は SRWP (Bit7) が最初で、1クロックが入力されるたびにその立ち下がりに同期して $\overline{RDY}$  (Bit0) までのデータが順に出力される。 $\overline{RDY}$  (Bit0) が出力された後、なおもクロックの入力が続く場合、最初に出力されたビット (SRWP) に戻って、データ出力が出力され、以後クロック入力が続く限り出力が繰り返される。ステータスレジスタリードは、いつでも (プログラム、イレーズサイクル中も) 読出すことが可能である。

図 6: ステータスレジスタリード

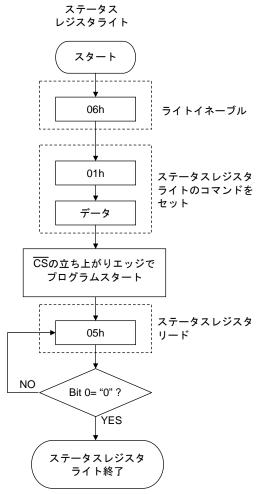

# 2-2. ステータスレジスタライト

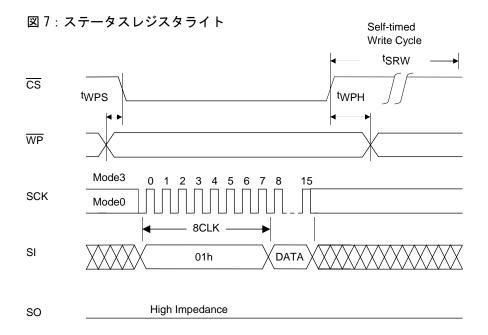

ステータスレジスタライトにより、ステータスレジスタの BPO、BP1、SRWP を書換えることができる。 $\overline{RDY}$ 、WEN、Bit4、Bit5 と Bit6 はリードオンリーであり書換えることはできない。BPO、BP1、SRWP は不揮発メモリに記憶しており、書き込みを行うと電源を切断してもその内容は保持される。図 7:ステータスレジスタライトにステータスレジスタライトのタイミング波形を、また、図 21にステータスレジスタライトのフローチャートを示す。ステータスレジスタライトコマンドは、第 1バスサイクルと第 2 バスサイクルで構成され、(01h) に続けて DATA を入力した後、 $\overline{CS}$ を立ち上げることで内部のライト動作が始まる。ステータスレジスタライトは、デバイス内部で自動的にイレーズ、プログラムが行われるので、あらかじめ消去などの処理を行う必要はない。この操作で BPO、BP1、SRWP の書換えを行うことができる。ステータスレジスタライト時に、書換えを行うことのできないビット、つまり、 $\overline{RDY}$ (Bit0)、WEN(Bit1)、Bit4、Bit5、Bit6にデータを設定しても書き込みは行われないので、いずれの値に設定しても不具合は発生しない。ステータスレジスタライトの終了は、ステータスレジスタリードの $\overline{RDY}$ により検知することができる。また、ステータスレジスタの書換え回数は、1000回(Min.)である。ステータスレジスタライトを行うには、 $\overline{WP}$ ピンを論理高レベル、ステータスレジスタのWEN を"1"状態にしておく必要がある。

# 2-3. 各ステータスレジスタの内容

#### RDY (Bit0)

RDYは、ライト(プログラム、イレーズ、およびステータスレジスタライト)の終了を検知するためのレジスタである。RDYが"1"状態の場合、デバイスはビジー状態であり、"0"状態であればライトが終了していることを示す。

#### WEN(Bit1)

WEN は、デバイスがライト可能であるかどうかを検知するためのレジスタである。WEN が "0" 状態であれば、ライトコマンドを入力しても、デバイスはライト動作を行われない。WEN が "1" 状態であれば、ブロックプロテクトされていない領域にライトを行うことが可能である。

WEN は、ライトイネーブルコマンドおよびライトディセーブルコマンドにより、コントロールできる。ライトイネーブルコマンド(06h)を入力することにより、WEN は"1"状態に、また、ライトディセーブルコマンド(04h)を入力することにより"0"状態にすることができる。また、下記の状態の時は、不用意な書き込みを防止するため自動的にWENが"0"状態となる。

- 電源投入時

- ・小セクタイレーズ、セクタイレーズ、チップイレーズの終了後

- ページプログラムの終了後

- ・ステータスレジスタライトの終了後

\*各ライト動作(小セクタイレーズ、セクタイレーズ、チップイレーズ、ページプログラム、ステータスレジスタライト)への入力コマンドが不成立、プロテクトされたアドレスへのライト動作等、LE25U20AMB 内部でライト動作が行われなかった場合、WEN は、そのコマンド発行前の状態を維持する。また、リード動作によって WEN の状態が変わることはない。

# BPO、BP1 (Bit2、3)

ブロックプロテクト BPO、BP1 は書き込みを行うことが可能なステータスレジスタビットで、その内容によりプロテクトするメモリ空間を設定することができる。設定条件は表 4: プロテクトレベル設定条件を参照すること。

表 4: プロテクトレベル設定条件

| プロテクトレベル      | ステータスレ | ジスタビット | プロニカト何は       |  |

|---------------|--------|--------|---------------|--|

| プロケクトレベル      | BP1    | BP0    | プロテクト領域       |  |

| 0(全領域アンプロテクト) | 0      | 0      | 無し            |  |

| 1(1/4プロテクト)   | 0      | 1      | 30000h∼3FFFFh |  |

| 2(1/2 プロテクト)  | 1      | 0      | 20000h∼3FFFFh |  |

| 3(全領域プロテクト)   | 1      | 1      | 00000h∼3FFFFh |  |

<sup>\*</sup>プロテクトレベルが0の時のみ、チップイレーズ可能

#### SRWP (Bit7)

ステータスレジスタライトプロテクト SRWP は、ステータスレジスタのプロテクトを行うためのビットで書換えを行うことが可能である。SRWP が "1" 状態、かつ、 $\overline{WP}$ ピンが論理低レベルである時、ステータスレジスタライトコマンドは無視され、ステータスレジスタの BPO、BP1、SRWP は保護される。 $\overline{WP}$ ピンが論理高レベルである時は、SRWP の状態にかかわらず、ステータスレジスタはプロテクトされない。SRWP 設定条件を表 5: SRWP 設定条件に示す。

表 5: SRWP 設定条件

| WPピン | SRWP | ステータスレジスタ<br>プロテクト状態 |

|------|------|----------------------|

| 0    | 0    | アンプロテクト              |

| 0    | 1    | プロテクト                |

| 1    | 0    | アンプロテクト              |

| 1    | 1    | アンプロテクト              |

Bit4、Bit5、Bit6 はリザーブビットとなっており意味を持っていない。

#### 3. ライトイネーブル

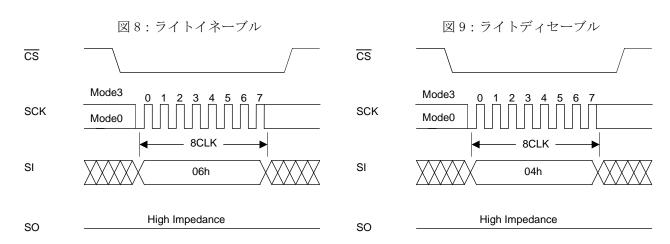

下記の動作を行う前には、あらかじめデバイスをライトイネーブル状態にしておく必要がある。これは、ステータスレジスタの WEN を "1" 状態にする操作と同じで、ライトイネーブルコマンドの入力を行うことで可能になる。図8: ライトイネーブルに、ライトイネーブル動作を行う場合のタイミング波形を示す。ライトイネーブルコマンドは、第1バスサイクルのみで構成され、(06h)を入力することにより行われる。

- ・小セクタイレーズ、セクタイレーズ、チップイレーズ

- ・ページプログラム

- ・ステータスレジスタライト

# 4. ライトディセーブル

ライトディセーブルは、ステータスレジスタの WEN を "0" 状態にセットし、不用意なライトを禁止するコマンドである。図9: ライトディセーブルにタイミング波形を示す。ライトディセーブルコマンドは、第1バスサイクルのみで構成され、(04h)を入力する。ライトディセーブル状態(WEN "0")からの抜け出しは、ライトイネーブルコマンド(06h)で WEN "1" にすることにより行われる。

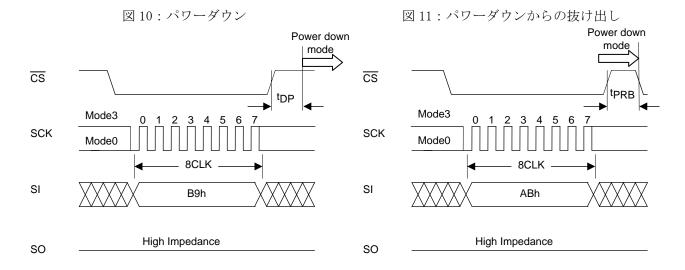

#### 5. パワーダウン

パワーダウンは、シリコン ID リード 2 とパワーダウンからの抜け出しコマンド以外の、全てのコマンドを受け付け禁止状態(パワーダウン)にするコマンドである。図 10:パワーダウンにタイミング波形を示す。パワーダウンコマンドは、第1バスサイクルのみで構成され、(B9h)を入力する。ただし、内部ライト動作実行中のパワーダウンコマンドは無視される。一方、パワーダウンからの抜け出しは、パワーダウンからの抜け出しコマンドで行う(シリコン ID リード 2 コマンド(ABh)の1バスサイクル以上が入力された場合も、パワーダウンから抜け出す)。図 11:パワーダウンからの抜け出しに、パワーダウンからの抜け出しコマンドのタイミング波形を示す。

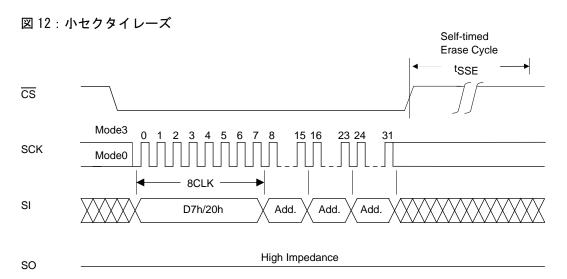

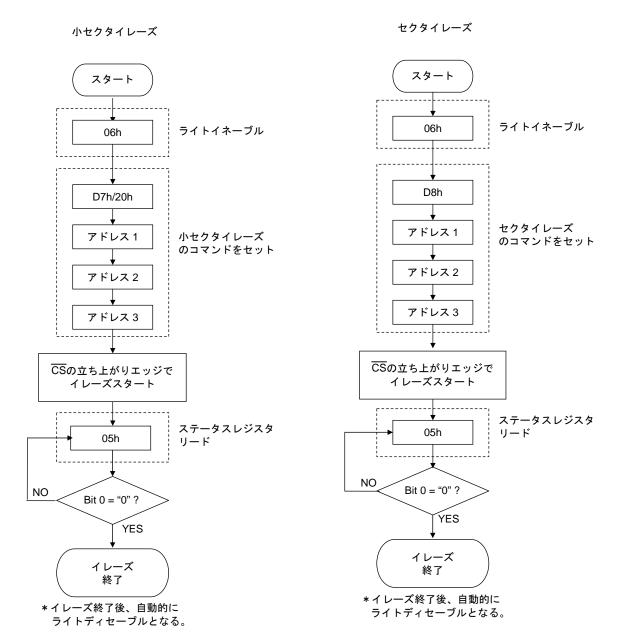

# 6. 小セクタイレーズ

小セクタイレーズは、任意の小セクタのメモリセルデータを"1"状態にする操作である。小セクタは 4Kbyte で構成される。図 12: 小セクタイレーズにタイミング波形を、図 21 にフローチャートを示す。小セクタイレーズコマンドは、第 1 バスサイクルから第 4 バスサイクルで構成され、(D7h/20h) に続けて 24 ビットのアドレスを入力する。アドレスは、A17~A12 が有効で、A23~A18 は、don't care となっている。コマンドの入力終了後、 $\overline{\text{CS}}$ の立ち上がりエッジから内部イレーズ動作が始まり、内部タイマの制御で自動的に終了する。また、イレーズの終了は、ステータスレジスタ  $\overline{\text{(RDY)}}$  を用いて検知することができる。

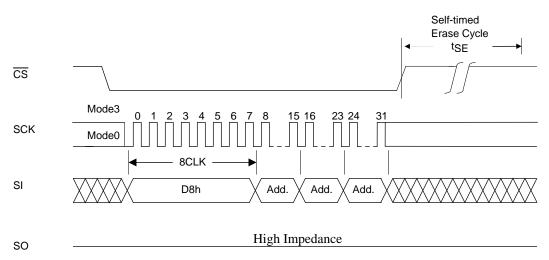

# 7. セクタイレーズ

セクタイレーズは、任意のセクタのメモリセルデータを"1"状態にする操作である。セクタは 64Kbyte で構成される。図 13:セクタイレーズにタイミング波形を、図 21 にフローチャートを示す。 セクタイレーズコマンドは、第 1 バスサイクルから第 4 バスサイクルで構成され、(D8h) に続けて 24 ビットのアドレスを入力する。アドレスは、A17~A16 が有効で、A23~A18 は、don't care となっている。コマンドの入力終了後、 $\overline{\text{CS}}$ の立ち上がりエッジから内部イレーズ動作が始まり、内部タイマの制御で自動的に終了する。また、イレーズの終了は、ステータスレジスタ  $\overline{\text{(RDY)}}$  を用いて検知することができる。

# 図 13:セクタイレーズ

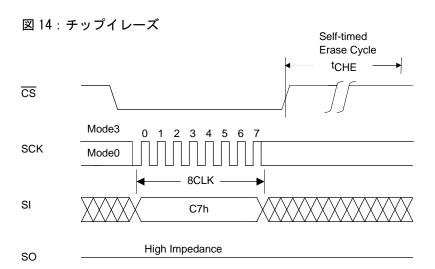

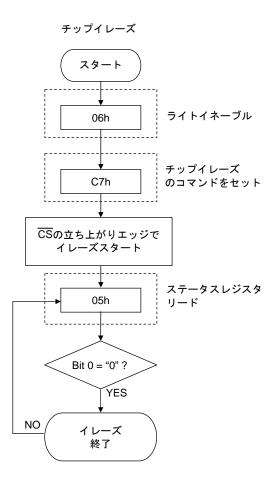

#### 8. チップイレーズ

チップイレーズは、全セクタのメモリセルデータを"1"状態にする操作である。図 14:チップイレーズにタイミング波形を、図 21 にフローチャートを示す。チップイレーズコマンドは、第 1 バスサイクルのみで構成され、(C7h)を入力することにより行われる。コマンド入力終了後、CSの立ち上がりエッジから内部イレーズ動作が始まり、内部タイマの制御で自動的に終了する。また、イレーズの終了は、ステータスレジスタ(RDY)を用いて検知することができる。

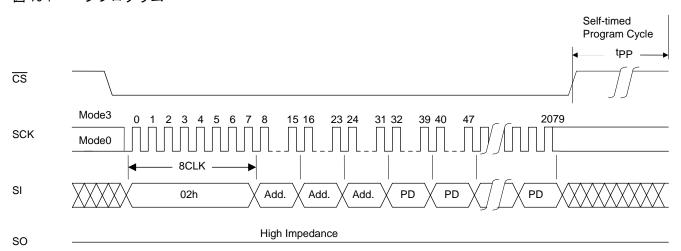

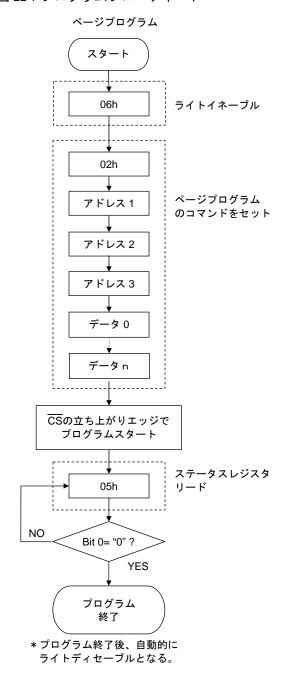

# 9. ページプログラム

ページプログラムは、セクタの同一ページ内(ページアドレス:  $A17\sim A8$ )に、1 バイトから 256 バイトの任意のバイト数をプログラムする操作である。プログラムを行うページはあらかじめ小セクタイレーズ、セクタイレーズあるいはチップイレーズで消去しておく必要がある。図 15:ページプログラムにページプログラムのタイミング波形を、図 22 にフローチャートを示す。 $\overline{CS}$ を立ち下げた後、コマンド(02H)を入力し、引き続き 24 ビットのアドレスを入力する。アドレスは  $A17\sim A0$  が有効である。その後、 $\overline{CS}$ を立ち上げるまではクロックの立ち上がりの度にプログラムデータがロードされ、 $\overline{CS}$ が立ち上がるまでデータのロードが続く。ロードされるデータが 256 バイトを超えた場合は、最後にロードされた 256 バイトがプログラムされる。プログラムデータはバイト単位でロードする必要があり、それ以外のタイミングで $\overline{CS}$ を立ち上げた場合は、プログラム動作は行われない。ページプログラム時間は、256 バイト(1ページ)を一度にプログラムする場合、4.0ms (Typ.)となる。

# 図 15:ページプログラム

# 10. シリコン ID リード

シリコン ID リードは、製造者コードとデバイス ID をリードするための操作である。なお、シリコン ID リードコマンドは、ライト中は受け付けられない。

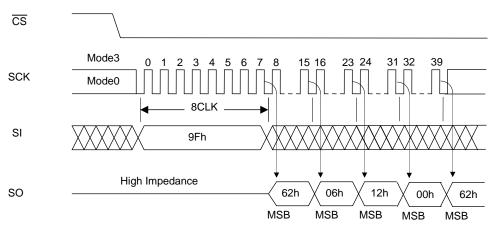

シリコン ID リードを行う方法は2種類あり、それそれにデバイス ID が割り与えられている。一つ目は、9Fh のコマンド入力を行う方法で、第1バスサイクルの入力だけで設定が完了し、その後のバスサイクルでは、JEDEC で割り当てられた製造者コード  $62h \cdot 2$  バイトのデバイス ID コード (メモリータイプ、メモリー容量)・リザーブコードが順に出力される。また、クロックの入力が続く限り、4 バイトの出力コードは繰り返し出力される。表  $6_-1:$  シリコン ID リード 1 に出力コード、図  $16_-a:$  シリコン ID リード 1 を示す。

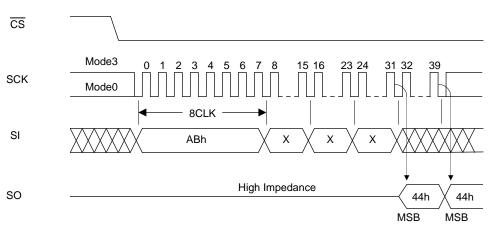

二つ目の方法は、ABh のコマンドを入力する方法である。第 1 バスサイクルから第 4 バスサイクルで構成され、(ABh) に続けて 24 ビットのダミービットを入力すると、1 バイトのシリコン ID コードがリードできる。表  $6_2:$  シリコン ID リード 2 に出力コード、図 16-b: シリコン ID リード 2 に タイミング波形を示す。デバイスコードを読み出した後、なおも SCK 入力が続く場合は、デバイスコードが出力され続ける。データ出力は、第 4 バスサイクル Bit0 の立ち下がりクロックから出力され、 $\overline{CS}$ を立ち上げることで、シリコン ID リードは終了する。

表 6\_1: シリコン ID リード1

|         |               | 出力コード      |

|---------|---------------|------------|

| 製造者コード  |               | 62h        |

| 2 バイト   | メモリータイプ       | 06h        |

| デバイス ID | メモリー容量<br>コード | 12h(2MBit) |

| リザーブコード |               | 00h        |

表 6\_2: シリコン ID リード 2

|         | 出力コード |

|---------|-------|

| 1バイト    | 44h   |

| デバイス ID |       |

図 16-a:シリコン ID リード1

図 16-b:シリコン ID リード 2

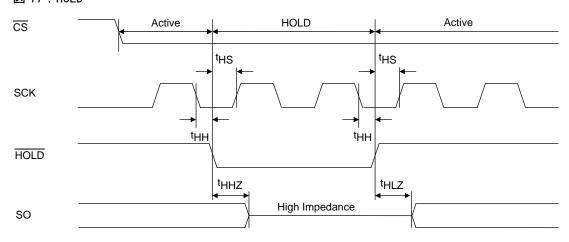

# 11. ホールド機能

$\overline{\text{HOLD}}$ ピンによるホールド機能は、シリアルコミュニケーションを中断(ホールド状態) するために使用する。図  $17:\overline{\text{HOLD}}$ にタイミング波形を示す。SCK が論理低レベルで $\overline{\text{HOLD}}$ を立ち下げると、デバイスはホールド状態となり、 $\overline{\text{HOLD}}$ を立ち上げると、ホールド状態から抜けだす。SCK が論理高レベルの時に、 $\overline{\text{HOLD}}$ の立ち下げ、立ち上げを行わないこと。ホールド機能は、 $\overline{\text{CS}}$ が論理低レベルの時有効で、 $\overline{\text{CS}}$ を立ち上げると、ホールド状態から抜け、シリアルコミュニケーションはリセットされる。ホールド状態時、SO は  $\overline{\text{Hi-Z}}$  出力で  $\overline{\text{SI}}$ 、SCK は don't care となる。

図 17: HOLD

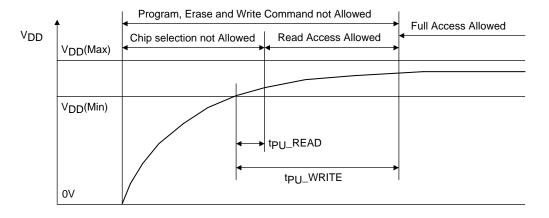

# 12. 電源投入

不用意な書き込みを防止するため、電源投入時は、 $\overline{CS}$ を  $V_{CC}$  にしておくこと。リード動作の開始は、電源を投入し電源電圧が 2.30V 以上で、電圧が安定した状態から  $100\mu s$  ( $t_{PU}$ \_READ)後に、コマンドを入力すること。また、ライト動作の開始は、同じく電圧が安定した状態から 10ms ( $t_{PU}$ \_WRITE) 後に、コマンドを入力すること。

図 18: パワーオンタイミング

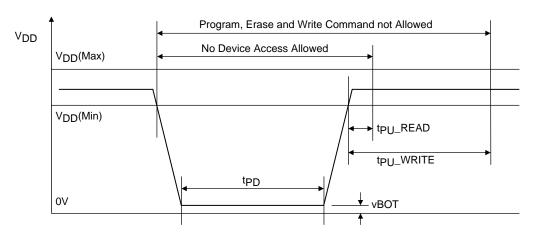

# 13. ハードウエアデータ保護

電源投入時の不用意な書き込みを防ぐために、LE25U20AMB は内部にパワーオンリセット機能がある。パワーリセット回路を安定に動作させるために、以下の条件を守ること。

また、書き込み期間中の電源の瞬断についてはそのデータは保証されない。

# 図 19:パワーダウンタイミング

# 14. ソフトウエアデータ保護

LE25U20AMBは、以下の条件ではコマンドを認識しないことにより、不用意な動作を無くしている。

- ・ライトコマンド入力時、CSの立ち上げタイミングが、バスサイクル間(SCKの 8CLK 単位)で無い場合。

- ・ページプログラムのデータがバイト単位で無い場合。

- ・ステータスレジスタライトのコマンド入力が、2バスサイクル以上の場合。

# 15. デカップリングコンデンサ

デバイスを安定に動作させるために、 $V_{DD}$ – $V_{SS}$  間に 0.  $1\mu F$  のセラミックコンデンサをデバイスごとに付加すること。

# 絶対最大定格

| 項目        | 記号                  | 条件                 | 定格値                      | unit |

|-----------|---------------------|--------------------|--------------------------|------|

| 最大電源電圧    | V <sub>DD</sub> max | V <sub>SS</sub> 基準 | −0.5~+4.6                | V    |

| 全ピン DC 電圧 | VIN/VOUT            | V <sub>SS</sub> 基準 | $-0.5 \sim V_{DD} + 0.5$ | V    |

| 保存温度      | Tstg                |                    | -55∼+150                 | °C   |

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。これらの定格値を超えた場合は、デバイスの機能性を損ない、ダメージが 生じ、信頼性に影響を及ぼす危険性があります。

# 動作範囲

| 項目     | 記号       | 条件 | 定格値       | unit |

|--------|----------|----|-----------|------|

| 動作電源電圧 | $v_{DD}$ |    | 2.30~3.60 | V    |

| 動作周囲温度 | Topr     |    | -40∼+85   | °C   |

# DC許容動作条件

| 項目                              | 記号               | 条件                                                                                                                                                                                                                                        | min                  | typ | max                | unit |

|---------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|--------------------|------|

| リード時動作電流                        | ICCR             | CS = 0.1V <sub>DD</sub> , HOLD = WP = 0.9V <sub>DD</sub>     SI = 0.1V <sub>DD</sub> / 0.9V <sub>DD</sub> , SO = 開放     動作周波数 = 30 MHz,     V <sub>DD</sub> = V <sub>DD</sub> max                                                         |                      |     | 6                  | mA   |

| ライト時動作電流<br>(イレーズ+<br>ページプログラム) | ICCW             | $V_{DD} = V_{DD}$ max, $t_{SSE} = 40$ ms,<br>$t_{SE} = 80$ ms, $t_{CHE} = 160$ ms,<br>$t_{PP} = 5.0$ ms                                                                                                                                   |                      |     | 15                 | mA   |

| CMOS スタンバイ<br>電流                | $I_{SB}$         | $\overline{\text{CS}} = \overline{\text{HOLD}} = \overline{\text{WP}} = \text{V}_{\text{DD}},$ $\text{SI} = \text{V}_{\text{SS}} / \text{V}_{\text{DD}}, \text{SO} = 開放,$ $\text{V}_{\text{DD}} = \text{V}_{\text{DD}} \text{ max}$       |                      |     | 50                 | μΑ   |

| パワーダウン<br>スタンバイ電流               | I <sub>DSB</sub> | $\overline{\text{CS}} = \overline{\text{HOLD}} = \overline{\text{WP}} = \text{V}_{\text{DD}},$<br>$\text{SI} = \text{V}_{\text{SS}} / \text{V}_{\text{DD}}, \text{SO} = 開放,$<br>$\text{V}_{\text{DD}} = \text{V}_{\text{DD}} \text{ max}$ |                      |     | 10                 | μΑ   |

| 入力リーク電流                         | ILI              | $V_{IN} = V_{SS} \sim V_{DD}$ , $V_{DD} = V_{DD}$ max                                                                                                                                                                                     |                      |     | 2                  | μΑ   |

| 出力リーク電流                         | IFO              | $V_{IN} = V_{SS} \sim V_{DD}$ , $V_{DD} = V_{DD}$ max                                                                                                                                                                                     |                      |     | 2                  | μΑ   |

| 入力低電位                           | V <sub>IL</sub>  | $V_{DD} = V_{DD} \max$                                                                                                                                                                                                                    | -0.3                 |     | $0.3V_{DD}$        | V    |

| 入力高電位                           | $v_{IH}$         | $V_{DD} = V_{DD} \min$                                                                                                                                                                                                                    | 0.7V <sub>DD</sub>   |     | $V_{\rm DD} + 0.3$ | V    |

| 出力低電位                           | V <sub>OL</sub>  | $I_{OL} = 100 \mu A, V_{DD} = V_{DD} min$ $I_{OL} = 1.6 mA, V_{DD} = V_{DD} min$                                                                                                                                                          |                      |     | 0.2<br>0.4         | V    |

| 出力高電位                           | VOH              | $I_{OH} = -100 \mu A$ , $V_{DD} = V_{DD} min$                                                                                                                                                                                             | V <sub>CC</sub> -0.2 |     |                    | V    |

推奨動作範囲を超えるストレスでは推奨動作機能を得られません。推奨動作範囲を超えるストレスの印加は、デバイスの信頼性に影響を与える危険性があります。

# 電源投入タイミング

| 項目               | 記号                     | 規棒  | unit |       |  |

|------------------|------------------------|-----|------|-------|--|

| · 块口             | pL ク                   | min | max  | uiiit |  |

| 電源投入からリード動作までの時間 | tpU_READ               | 100 |      | μs    |  |

| 電源投入からライト動作までの時間 | t <sub>PU_</sub> WRITE | 10  |      | ms    |  |

| 電源立ち下げ時間         | tPD                    | 10  |      | ms    |  |

| 電源立ち下げ電圧         | vBOT                   |     | 0.2  | V     |  |

# 端子容量 / Ta = 25°C, f = 1 MHz

|        | ,               |                |      |       |

|--------|-----------------|----------------|------|-------|

| 項目記号条件 |                 | 規格値            | unit |       |

| 73.17  | 11. 万           | 木厂             | max  | uiiit |

| 出力端子容量 | $C_{DQ}$        | $V_{DQ} = 0 V$ | 12   | pF    |

| 入力端子容量 | C <sub>IN</sub> | $V_{IN} = 0 V$ | 6    | pF    |

注: このパラメータは全数測定されたものではなく、サンプル値である。

# AC 特性

| 75.0                        | 記号              | 規格値 |      |      |      |

|-----------------------------|-----------------|-----|------|------|------|

| 項目                          |                 | min | typ  | max  | unit |

| クロック周波数                     | fCLK            |     |      | 30   | MHz  |

| SCK 論理高レベルパルス幅              | tCLHI           | 16  |      |      | ns   |

| SCK 論理低レベルパルス幅              | tCLLO           | 16  |      |      | ns   |

| 入力信号立ち上がり/立ち下がり時間           | $t_{RF}$        |     |      | 20   | ns   |

| CSセットアップ時間                  | tCSS            | 10  |      |      | ns   |

| CSホールド時間                    | tCSH            | 10  |      |      | ns   |

| データセットアップ時間                 | $t_{DS}$        | 5   |      |      | ns   |

| データホールド時間                   | tDH             | 5   |      |      | ns   |

| CS待機パルス幅                    | tCPH            | 25  |      |      | ns   |

| CSからの出力高インピーダンス時間           | tCHZ            |     |      | 15   | ns   |

| SCK からの出力データ時間              | tv              |     | 10   | 15   | ns   |

| 出力データホールド時間                 | tHO             | 1   |      |      | ns   |

| HOLDセットアップ時間                | t <sub>HS</sub> | 7   |      |      | ns   |

| HOLDホールド時間                  | t <sub>HH</sub> | 3   |      |      | ns   |

| <b>HOLD</b> からの出力低インピーダンス時間 | tHLZ            |     |      | 9    | ns   |

| <b>HOLD</b> からの出力高インピーダンス時間 | tHHZ            |     |      | 9    | ns   |

| WPセットアップ時間                  | twps            | 20  |      |      | ns   |

| WPホールド時間                    | tWPH            | 20  |      |      | ns   |

| ライトステータスレジスタ時間              | tSRW            |     | 5    | 15   | ms   |

| ページプログラムサイクル時間              | tpp             |     | 4.0  | 5.0  | ms   |

| 小セクタイレーズサイクル時間              | tSSE            |     | 0.04 | 0.15 | S    |

| セクタイレーズサイクル時間               | t <sub>SE</sub> |     | 0.08 | 0.25 | S    |

| チップイレーズサイクル時間               | tCHE            |     | 0.25 | 1.6  | S    |

| パワーダウン時間                    | t <sub>DP</sub> |     |      | 3    | μs   |

| パワーダウンリカバリ時間                | tPRB            |     |      | 3    | μs   |

| SCK からの出力低インピーダンス時間         | tCLZ            | 0   |      |      | ns   |

製品パラメータは、特別な記述が無い限り、記載されたテスト条件に対する電気的特性で示しています。異なる条件下で製品動作を行った時には、電気的特性で示している特性を得られない場合があります。

# AC 試験条件

入力パルスレベル0 V, 2.5 V入力立ち上がり/立ち下がり時間5 ns入力タイミングレベル0.3VDD, 0.7VDD出力タイミングレベル1/2 × VDD出力負荷30 pF

\*注:typ についての試験条件は、 $V_{DD} = 2.5 V$ 、室温測定である。

# 図 20:ステータスレジスタライトフローチャート

\*ステータスレジスターライト終了後、 自動的にライトディセーブルとなる。

# 図 21: イレーズフローチャート

# 図 22: プログラムフローチャート

\*イレーズ終了後、自動的にライトディセーブルとなる。

# ORDERING INFORMATION

| Device        | Package                                              | Shipping (Qty / Packing) |

|---------------|------------------------------------------------------|--------------------------|

| LE25U20AMB-AH | SOIC-8 / SOP8K (200 mil)<br>(Pb-Free / Halogen Free) | 2000 / Tape & Reel       |

<sup>†</sup> テープ&リール仕様(製品配置方向, テープサイズ含む)に関する情報については、Tape and Reel Packaging Specifications パンフレット(BRD8011/D)をご参照ください。http://www.onsemi.com/pub\_link/Collateral/BRD8011-D.PDF

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

ON Semiconductor 及び ON SemiconductorのコゴはON Semiconductorという商号を使うSemiconductor Components Industries, LLC 若しくはその子会社の米国及び/または他の国における商標です。ON Semiconductorは特許、商標、著作権、トレードシークレット(営業秘密)と他の知的所有権に対する権利を保有します。ON Semiconductorの製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductorは通告なして、本書記載の製品の変更を行うことがあります。ON Semiconductorは、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害など一切の損害に対して、いかなる責任も負うことはできません。お客様は、ON Semiconductorによって提供されたサポートやアプリケーション情報の如何にかかわらず、すべての法令、規制、安全性の要求あるいは標準の遵守を含む、ON Semiconductor 製品を使用したお客様の製品とアプリケーションについて一切の責任を負うものとします。ON Semiconductorデータシートや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあり、実際の性能も時間の経過により変化する可能性があります。「標準的」パラメータを含むすべての動作パラメータは、で使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致します。ON Semiconductorは、その特許権やその他の権利の下、いかなるテクセンスも許諾しません。ON Semiconductor製品は、生命維持装置や、いかなるFDA(米国食品医薬品局)クラス3の医療機器、FDAが管轄しない地域において同一もしくは類似のものと分類される医療機器、あるいは、人体への移植を対象とした機器における重要部品などへの使用を意図した設計はされておらず、また、これらを使用対象としておりません。お客様が、このような意図されたものではない、許可されていないアプリケーション用にON Semiconductor製品を購入または使用した場合、たとえ、ON Semiconductorがその部品の設計または製造に関して過失があったと主張されたをしても、そのような意図せぬ使用、また未許可の使用に関連した現場、たとえ、CN Semiconductor がその部品の設計または製造に関して過失があったと主張されたとしても、そのような意図せぬ使用、また未許可の使用に関連した死傷等から、直接、又は間接的に生じるすべてのクレーム、費用、損害、経費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、ON Semiconductor とその役員、従業員、子会社、関連会社、代理店に対して、いかなる方法によっても再販するとしてきません。