# DUSEU

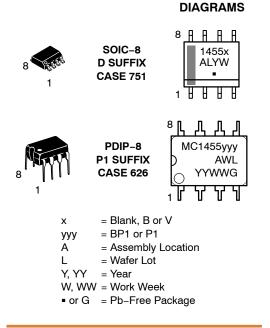

MARKING

# Timers

# MC1455, MC1455B, **NCV1455B**

The MC1455 monolithic timing circuit is a highly stable controller capable of producing accurate time delays or oscillation. Additional terminals are provided for triggering or resetting if desired. In the time delay mode, time is precisely controlled by one external resistor and capacitor. For astable operation as an oscillator, the free-running frequency and the duty cycle are both accurately controlled with two external resistors and one capacitor. The circuit may be triggered and reset on falling waveforms, and the output structure can source or sink up to 200 mA or drive TTL circuits.

### Features

- Direct Replacement for NE555 Timers

- Timing from Microseconds through Hours

- Operates in Both Astable and Monostable Modes

- Adjustable Duty Cycle

- High Current Output Can Source or Sink 200 mA

- Output Can Drive TTL

- Temperature Stability of 0.005% per °C

- Normally ON or Normally OFF Output

- Pb-Free Packages are Available

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.

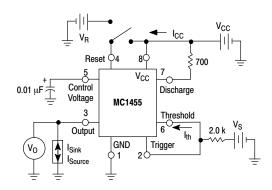

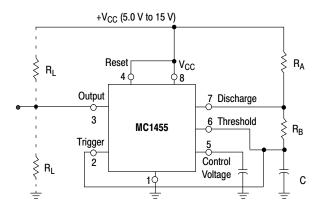

Test circuit for measuring DC parameters (to set output and measure parameters):

- a) When  $V_S \ge 2/3 V_{CC}$ ,  $V_O$  is low.

- b) When  $V_S \le 1/3 V_{CC}$ ,  $V_O$  is high. c) When  $V_O$  is low, Pin 7 sinks current. To test for Reset, set  $V_O$ high, apply Reset voltage, and test for current flowing into Pin 7. When Reset is not in use, it should be tied to V<sub>CC</sub>.

#### Figure 3. General Test Circuit

### MAXIMUM RATINGS (T<sub>A</sub> = +25°C, unless otherwise noted.)

| Rating                                                                                                                                                                      | Symbol                           | Value                                 | Unit                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------|---------------------------|

| Power Supply Voltage                                                                                                                                                        | V <sub>CC</sub>                  | +18                                   | Vdc                       |

| Discharge Current (Pin 7)                                                                                                                                                   | I <sub>7</sub>                   | 200                                   | mA                        |

| Power Dissipation (Package Limitation)<br>P1 Suffix, Plastic Package<br>Derate above $T_A = +25^{\circ}C$<br>D Suffix, Plastic Package<br>Derate above $T_A = +25^{\circ}C$ | P <sub>D</sub><br>P <sub>D</sub> | 625<br>5.0<br>625<br>160              | mW<br>mW/°C<br>mW<br>°C/W |

| Operating Temperature Range (Ambient)<br>MC1455B<br>MC1455<br>NCV1455B                                                                                                      | T <sub>A</sub>                   | -40 to +85<br>0 to +70<br>-40 to +125 | °C                        |

| Maximum Operating Die Junction Temperature                                                                                                                                  | TJ                               | +150                                  | °C                        |

| Storage Temperature Range                                                                                                                                                   | T <sub>stg</sub>                 | -65 to +150                           | °C                        |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

| Characteristics                                                                                                                                                                                                                                                                                                                                                                              | Symbol                           | Min                   | Тур                                   | Max                              | Unit               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|---------------------------------------|----------------------------------|--------------------|

| Operating Supply Voltage Range                                                                                                                                                                                                                                                                                                                                                               | V <sub>CC</sub>                  | 4.5                   | -                                     | 16                               | V                  |

| Supply Current $V_{CC} = 5.0 \text{ V}, \text{ R}_{L} = \infty$ $V_{CC} = 15 \text{ V}, \text{ R}_{L} = \infty$ , Low State (Note 1)                                                                                                                                                                                                                                                         | Icc                              |                       | 3.0<br>10                             | 6.0<br>15                        | mA                 |

| Timing Error (R = 1.0 k $\Omega$ to 100 k $\Omega$ ) (Note 2)<br>Initial Accuracy C = 0.1 $\mu$ F<br>Drift with Temperature<br>Drift with Supply Voltage                                                                                                                                                                                                                                     |                                  |                       | 1.0<br>50<br>0.1                      |                                  | %<br>PPM/°C<br>%/V |

| Threshold Voltage/Supply Voltage                                                                                                                                                                                                                                                                                                                                                             | V <sub>th</sub> /V <sub>CC</sub> | -                     | 2/3                                   | -                                |                    |

| Trigger Voltage<br>$V_{CC} = 15 V$<br>$V_{CC} = 5.0 V$                                                                                                                                                                                                                                                                                                                                       | V <sub>T</sub>                   |                       | 5.0<br>1.67                           |                                  | V                  |

| Trigger Current                                                                                                                                                                                                                                                                                                                                                                              | Ι <sub>Τ</sub>                   | -                     | 0.5                                   | -                                | μA                 |

| Reset Voltage                                                                                                                                                                                                                                                                                                                                                                                | V <sub>R</sub>                   | 0.4                   | 0.7                                   | 1.0                              | V                  |

| Reset Current                                                                                                                                                                                                                                                                                                                                                                                | I <sub>R</sub>                   | -                     | 0.1                                   | -                                | mA                 |

| Threshold Current (Note 3)                                                                                                                                                                                                                                                                                                                                                                   | l <sub>th</sub>                  | -                     | 0.1                                   | 0.25                             | μΑ                 |

| Discharge Leakage Current (Pin 7)                                                                                                                                                                                                                                                                                                                                                            | I <sub>dischg</sub>              | -                     | -                                     | 100                              | nA                 |

| Control Voltage Level<br>$V_{CC} = 15 V$<br>$V_{CC} = 5.0 V$                                                                                                                                                                                                                                                                                                                                 | V <sub>CL</sub>                  | 9.0<br>2.6            | 10<br>3.33                            | 11<br>4.0                        | V                  |

| $\begin{array}{c} \text{Output Voltage Low} \\ I_{Sink} = 10 \text{ mA } (V_{CC} = 15 \text{ V}) \\ I_{Sink} = 50 \text{ mA } (V_{CC} = 15 \text{ V}) \\ I_{Sink} = 100 \text{ mA } (V_{CC} = 15 \text{ V}) \\ I_{Sink} = 200 \text{ mA } (V_{CC} = 15 \text{ V}) \\ I_{Sink} = 8.0 \text{ mA } (V_{CC} = 5.0 \text{ V}) \\ I_{Sink} = 5.0 \text{ mA } (V_{CC} = 5.0 \text{ V}) \end{array}$ | V <sub>OL</sub>                  | -<br>-<br>-<br>-<br>- | 0.1<br>0.4<br>2.0<br>2.5<br>-<br>0.25 | 0.25<br>0.75<br>2.5<br>-<br>0.35 | V                  |

| Output Voltage High<br>$V_{CC} = 15 V (I_{Source} = 200 \text{ mA})$<br>$V_{CC} = 15 V (I_{Source} = 100 \text{ mA})$<br>$V_{CC} = 5.0 V (I_{Source} = 100 \text{ mA})$                                                                                                                                                                                                                      | V <sub>OH</sub>                  | _<br>12.75<br>2.75    | 12.5<br>13.3<br>3.3                   |                                  | V                  |

| Rise Time Differential Output                                                                                                                                                                                                                                                                                                                                                                | tr                               | -                     | 100                                   | -                                | ns                 |

| Fall Time Differential Output                                                                                                                                                                                                                                                                                                                                                                | t <sub>f</sub>                   | -                     | 100                                   | -                                | ns                 |

**ELECTRICAL CHARACTERISTICS** ( $T_A = +25^{\circ}C$ ,  $V_{CC} = +5.0$  V to +15 V, unless otherwise noted.)

1. 'Supply current when output is high is typically 1.0 mA less.

Supply current when output is high is typically 1.0 mA less.

Tested at V<sub>CC</sub> = 5.0 V and V<sub>CC</sub> = 15 V Monostable mode.

This will determine the maximum value of R<sub>A</sub> + R<sub>B</sub> for 15 V operation. The maximum total R = 20 MΩ.

T<sub>low</sub> = 0°C for MC1455, T<sub>low</sub> = -40°C for MC1455B, NCV1455B T<sub>high</sub> = +70°C for MC1455, T<sub>high</sub> = +85°C for MC1455B, T<sub>high</sub> = +125°C for NCV1455B

NCV prefix is for Automotive and other applications requiring site and change control.

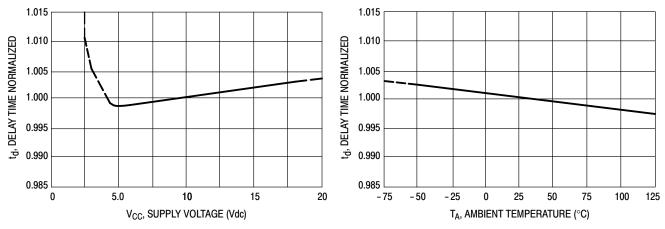

Figure 10. Delay Time versus Supply Voltage

Figure 11. Delay Time versus Temperature

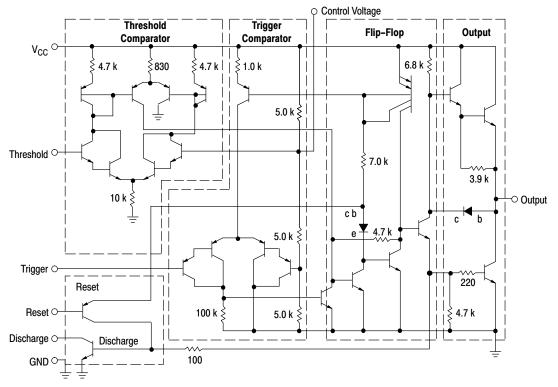

Figure 13. Representative Circuit Schematic

#### **GENERAL OPERATION**

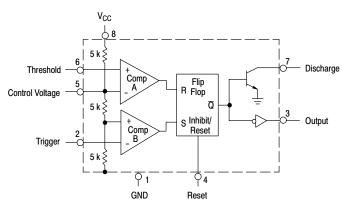

The MC1455 is a monolithic timing circuit which uses an external resistor – capacitor network as its timing element. It can be used in both the monostable (one–shot) and astable modes with frequency and duty cycle controlled by the capacitor and resistor values. While the timing is dependent upon the external passive components, the monolithic circuit provides the starting circuit, voltage comparison and other functions needed for a complete timing circuit. Internal to the integrated circuit are two comparators, one for the input signal and the other for capacitor voltage; also a flip–flop and digital output are included. The comparator reference voltages are always a fixed ratio of the supply voltage thus providing output timing independent of supply voltage.

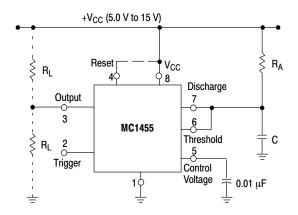

#### **Monostable Mode**

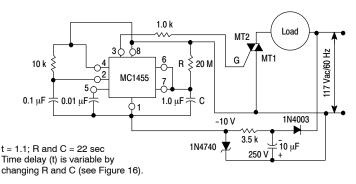

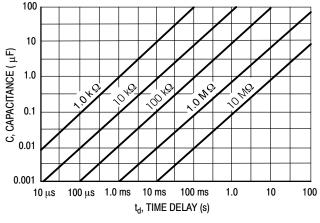

In the monostable mode, a capacitor and a single resistor are used for the timing network. Both the threshold terminal and the discharge transistor terminal are connected together in this mode (refer to circuit in Figure 14). When the input voltage to the trigger comparator falls below  $1/3 V_{CC}$ , the comparator output triggers the flip–flop so that its output sets low. This turns the capacitor discharge transistor "off" and drives the digital output to the high state. This condition allows the capacitor to charge at an exponential rate which is set by the RC time constant. When the capacitor voltage reaches  $2/3 V_{CC}$ , the threshold comparator resets the flip–flop. This action discharges the timing capacitor and returns the digital output to the low state. Once the flip–flop has been triggered by an input signal, it cannot be retriggered until the present timing period has been completed. The time that the output is high is given by the equation  $t = 1.1 R_A C$ . Various combinations of R and C and their associated times are shown in Figure 16. The trigger pulse width must be less than the timing period.

A reset pin is provided to discharge the capacitor, thus interrupting the timing cycle. As long as the reset pin is low, the capacitor discharge transistor is turned "on" and prevents the capacitor from charging. While the reset voltage is applied the digital output will remain the same. The reset pin should be tied to the supply voltage when not in use.

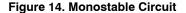

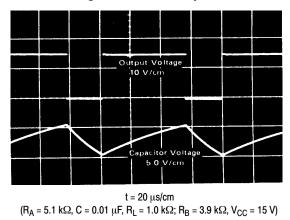

t = 50  $\mu \text{s/cm}$  (R\_A = 10 kΩ, C = 0.01  $\mu \text{F},$  R\_L = 1.0 kΩ, V\_{CC} = 15 V)

Figure 15. Monostable Waveforms

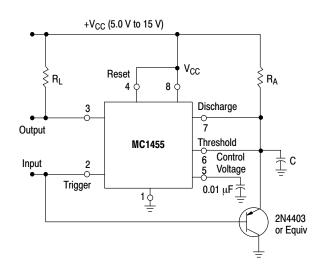

Figure 17. Astable Circuit

### Astable Mode

In the astable mode the timer is connected so that it will retrigger itself and cause the capacitor voltage to oscillate between  $1/3 V_{CC}$  and  $2/3 V_{CC}$ . See Figure 17.

The external capacitor changes to  $2/3 V_{CC}$  through  $R_A$  and  $R_B$  and discharges to  $1/3 V_{CC}$  through  $R_B$ . By varying the ratio of these resistors the duty cycle can be varied. The charge and discharge times are independent of the supply voltage.

The charge time (output high) is given by:

$t_1 = 0.695 (R_A + R_B) C$

The discharge time (output low) is given by:

$$t_2 = 0.695 (R_B) C$$

Thus the total period is given by:

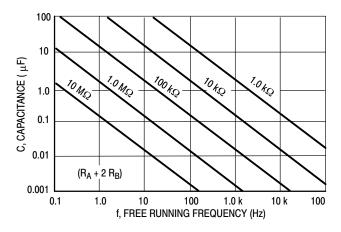

$T = t_1 + t_2 = 0.695 (R_A + 2R_B)C$

The frequency of oscillation is then:

$$f = \frac{1}{1} = \frac{1.44}{(\mathsf{R}\mathsf{A} + 2\mathsf{R}\mathsf{B})\mathsf{C}}$$

and may be easily found as shown in Figure 19.

The duty cycle is given by:  $DC = \frac{R_A + R_B}{R_A + 2R_B}$

Figure 16. Time Delay

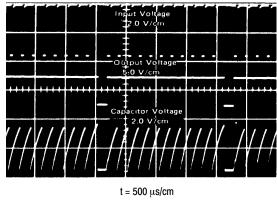

Figure 18. Astable Waveforms

To obtain the maximum duty cycle  $R_A$  must be as small as possible; but it must also be large enough to limit the discharge current (Pin 7 current) within the maximum rating of the discharge transistor (200 mA).

The minimum value of  $R_A$  is given by:

$$\mathsf{R}_{\mathsf{A}} \geq \frac{\mathsf{V}_{\mathsf{CC}}(\mathsf{Vdc})}{\mathsf{I7}\;(\mathsf{A})} \geq \frac{\mathsf{V}_{\mathsf{CC}}(\mathsf{Vdc})}{0.2}$$

Figure 19. Free Running Frequency

# **APPLICATIONS INFORMATION**

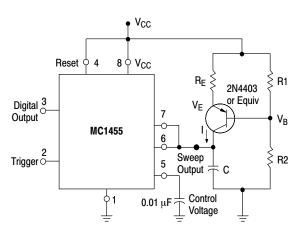

# Linear Voltage Ramp

In the monostable mode, the resistor can be replaced by a constant current source to provide a linear ramp voltage. The capacitor still charges from 0 V<sub>CC</sub> to 2/3 V<sub>CC</sub>. The linear ramp time is given by:

$$t = \frac{2}{3} \frac{V_{CC}}{1}, \text{ where } I = \frac{V_{CC} - V_B - V_{BE}}{R_F}$$

If  $V_{B}$  is much larger than  $V_{BE}\!,$  then t can be made independent of  $V_{CC}\!.$

Figure 20. Linear Voltage Sweep Circuit

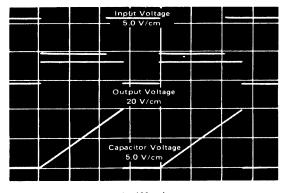

t = 100 µs/cm (R<sub>E</sub> = 10 kΩ, R2 = 100 kΩ, R1 = 39 kΩ, C = 0.01 µF, V<sub>CC</sub> = 15 V)

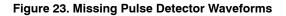

### **Missing Pulse Detector**

The timer can be used to produce an output when an input pulse fails to occur within the delay of the timer. To accomplish this, set the time delay to be slightly longer than the time between successive input pulses. The timing cycle is then continuously reset by the input pulse train until a change in frequency or a missing pulse allows completion of the timing cycle, causing a change in the output level.

Figure 21. Missing Pulse Detector

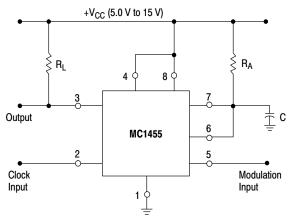

# **Pulse Width Modulation**

If the timer is triggered with a continuous pulse train in the monostable mode of operation, the charge time of the capacitor can be varied by changing the control voltage at Pin 5. In this manner, the output pulse width can be modulated by applying a modulating signal that controls the threshold voltage.

Figure 24. Pulse Width Modulator

# **Test Sequences**

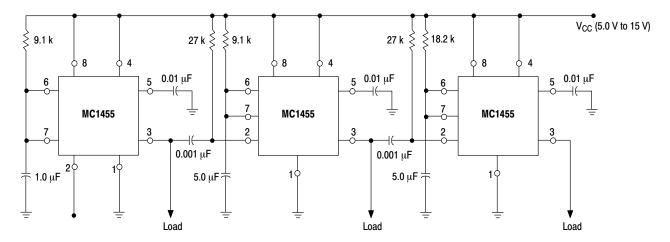

Several timers can be connected to drive each other for sequential timing. An example is shown in Figure 26 where the sequence is started by triggering the first timer which runs for 10 ms. The output then switches low momentarily and starts the second timer which runs for 50 ms and so forth.

Figure 26. Sequential Timer

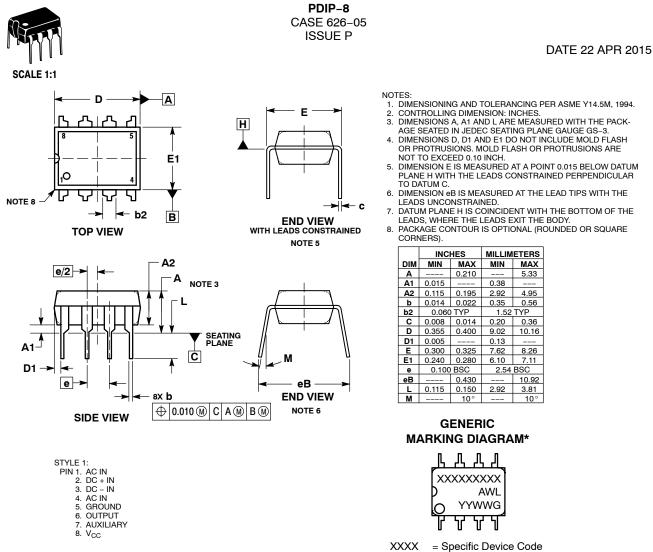

# **ORDERING INFORMATION**

| Device        | Operating Temperature Range                      | Package             | Shipping <sup>†</sup>    |

|---------------|--------------------------------------------------|---------------------|--------------------------|

| MC1455P1      |                                                  | PDIP-8              | 50 Units / Rail          |

| MC1455P1G     |                                                  | PDIP–8<br>(Pb–Free) | 50 Units / Rail          |

| MC1455DG      | T <sub>A</sub> = 0°C to +70°C                    | SOIC-8<br>(Pb-Free) | 98 Units / Rail          |

| MC1455DR2     |                                                  | SOIC-8              | 2500 Units / Tape & Reel |

| MC1455DR2G    |                                                  | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC1455BD      |                                                  | SOIC-8              | 98 Units / Rail          |

| MC1455BDR2    |                                                  | SOIC-8              | 2500 Units / Tape & Reel |

| MC1455BDR2G   |                                                  | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

| MC1455BP1     |                                                  | PDIP-8              | 50 Units / Rail          |

| MC1455BP1G    |                                                  | PDIP–8<br>(Pb–Free) | 50 Units / Rail          |

| NCV1455BDR2*  |                                                  | SOIC-8              | 2500 Units / Tape & Reel |

| NCV1455BDR2G* | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$ | SOIC-8<br>(Pb-Free) | 2500 Units / Tape & Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*NCV prefix is for automotive and other applications requiring site and control changes.

A = Assembly Location

- WL = Wafer Lot

- YY = Year

- WW = Work Week

- G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb–Free indicator, "G" or microdot " ■", may or may not be present.

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |  |

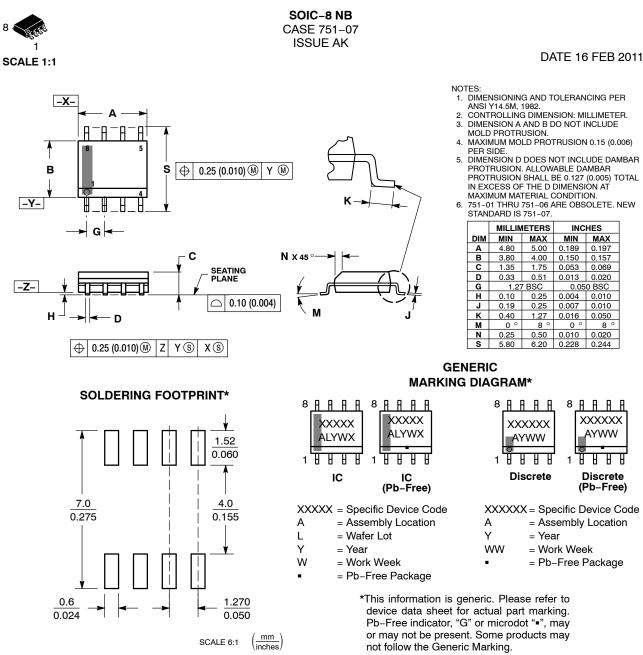

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN

| DOCUMENT NUMBER: | 98ASB42564B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOIC-8 NB                                                                                                                                                                                       |  | PAGE 2 OF 2 |

|                  |                                                                                                                                                                                                 |  |             |

onsem and of isor in are trademarks or semiconductor compension instructions, the do onsem or its subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced states and/or outrofts, or non-emitting the subsidiaries in the oniced stat purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>