# Integrated Synchronous Buck Converter

# 6 A

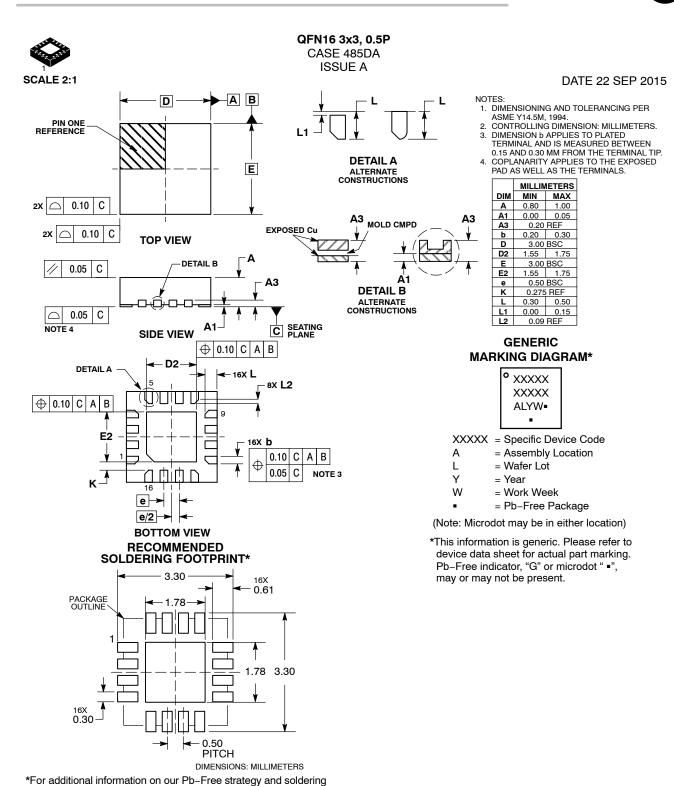

NCP3136 is a fully integrated synchronous buck converter for 3.3 V and 5 V step-down applications. It can provide up to 6.5 A instantaneous current. NCP3136 supports high efficiency, fast transient response and provides power good indicator. The control scheme includes two operation modes: FCCM and automatic CCM/DCM. In automatic CCM/DCM mode, the controller can smoothly switch between CCM and DCM, where converter runs at reduced switching frequency with much higher efficiency. NCP3136 is available in 3 mm x 3 mm QFN16 pin package.

#### **Features**

- High Efficiency in Both CCM and DCM

- Operation Frequency: 1.1 MHz

- Support MLCC Output Capacitor

- Small Footprint, 3 mm x 3 mm, 16-pin QFN Package

- 2.9 V to 5.5 V Wide Conversion Voltage Range

- $\bullet~$  Output Voltage Range from 0.6 V to 0.84 X  $V_{IN}$

- Automatic Power-Saving Mode

- Voltage Mode Control

- Support Pre-bias Start-up Functionality

- Output Discharge Operation

- Over-Temperature Protection

- Built-in Over-Voltage, Under-Voltage and Over-Current Protection

- Power Good Indicator

- This Device is Pb-Free and is RoHS Compliant

## **Applications**

- 5 V Step Down Rail

- 3.3 V Step Down Rail

# ON Semiconductor®

www.onsemi.com

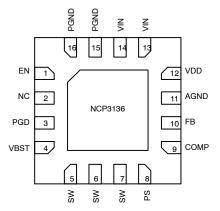

## QFN16 CASE 485DA

**MARKING**

3136 ALYW•

3136 = Specific Device Code A = Assembly Location

L = Wafer Lot Y = Year W = Work Week = Pb-Free Package

(Note: Microdot may be in either location)

#### **PINOUT DIAGRAM**

#### **ORDERING INFORMATION**

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCP3136MNTXG | QFN16<br>(Pb-Free) | 3000 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

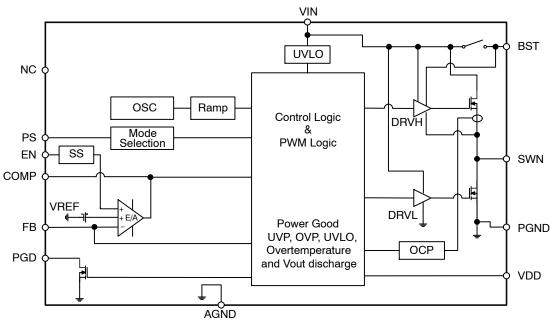

Figure 1. Block Diagram

# **PIN DESCRIPTION**

| Pin No. | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN     | Logic control to enabling the switcher. Internally pulled up to VDD with a 1.35 M $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                     |

| 2       | NC     | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | PGD    | Open drain power good output.                                                                                                                                                                                                                                                                                                                                                                                            |

| 4       | BST    | Gate drive voltage for high side FET. Connect capacitor from this pin to SWN.                                                                                                                                                                                                                                                                                                                                            |

| 5,6,7   | SWN    | Switch node between high-side MOSFET and low-side MOSFET.                                                                                                                                                                                                                                                                                                                                                                |

| 8       | PS     | Mode configuration pin:    Connecting to ground: Forced CCM    Pulled high or floating (internal pulled high): Forced CCM    Connect with 24.3 k $\Omega$ to GND: Automatic CCM/DCM    Connect with 57.6 k $\Omega$ to GND: Automatic CCM/DCM    Connect with 105 k $\Omega$ to GND: Automatic CCM/DCM    Connect with 105 k $\Omega$ to GND: Automatic CCM/DCM    Connect with 174 k $\Omega$ to GND: Automatic CCM/DCM |

| 9       | COMP   | Output of the error amplifier.                                                                                                                                                                                                                                                                                                                                                                                           |

| 10      | FB     | Feedback pin. Connect to resistor divider to set up the desired output voltage.                                                                                                                                                                                                                                                                                                                                          |

| 11      | AGND   | Analog ground                                                                                                                                                                                                                                                                                                                                                                                                            |

| 12      | VDD    | Power supply input for control circuitry.                                                                                                                                                                                                                                                                                                                                                                                |

| 13,14   | VIN    | Power input for power conversion and gate driver supply.                                                                                                                                                                                                                                                                                                                                                                 |

| 15,16   | PGND   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                             |

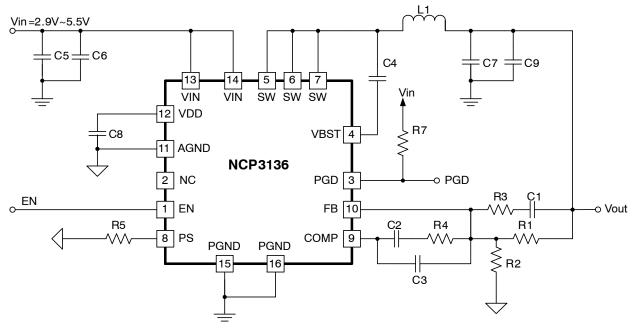

Figure 2. Application Circuit

# **ABSOLUTE MAXIMUM RATINGS**

|                                                              |         | ٧                       |      |           |      |  |

|--------------------------------------------------------------|---------|-------------------------|------|-----------|------|--|

| Parameter                                                    |         | Condition               |      | Max       | Unit |  |

| Input Voltage Range                                          |         | VIN, PS                 | -0.3 | 6.5       | ٧    |  |

|                                                              |         | VBST                    | -0.3 | 17        |      |  |

|                                                              | VBST    | (with respect to SW)    | -0.3 | 6.5       | 1    |  |

|                                                              |         | EN, FB                  | -0.3 | VDD + 0.3 |      |  |

| Output Voltage Range                                         | SW      | DC                      | -1   | 6.5       | V    |  |

|                                                              | T       | Pulse < 20 ns, E = 5 μJ | -3   | 10        |      |  |

|                                                              |         | PGD                     |      | 6.5       |      |  |

|                                                              |         | COMP                    | -0.3 | VDD + 0.3 |      |  |

|                                                              |         | PGND                    |      | 0.3       | 1    |  |

| Operation ambient temperature                                |         | T <sub>A</sub>          |      | 125       | °C   |  |

| Storage temperature                                          |         | T <sub>S</sub>          |      | 150       |      |  |

| Junction temperature                                         |         | TJ                      | -40  | 150       |      |  |

| Thermal Characteristics                                      |         | $R_{	hetaJA}$           |      | 45.4      |      |  |

| Electrostatic Discharge                                      | Humar   | Human Body Model (HBM)  |      | 2000      |      |  |

|                                                              | Charged | Device Model (CDM)      | 2    | 2000      |      |  |

| Lead temperature 1.6 mm (1/16 inch) from case for 10 seconds |         |                         | 300  |           | °C   |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

# **RECOMMENDED OPERATION RATINGS**

|                                            |                           | Value |     |      |      |

|--------------------------------------------|---------------------------|-------|-----|------|------|

| Parameter                                  | Condition                 | Min   | Тур | Max  | Unit |

| Input Voltage Range                        | VIN                       | 2.9   |     | 5.5  | V    |

|                                            | VBST                      | -0.1  |     | 13.5 |      |

|                                            | VBST (with respect to SW) | -0.1  |     | 6.0  |      |

|                                            | EN, PS, FB                | -0.1  |     | VDD  |      |

| Output Voltage Range                       | VDD                       | 2.9   |     | 5.5  | V    |

|                                            | SW                        | -1    |     | 6.5  |      |

|                                            | PGD                       | -0.1  |     | 6.0  |      |

|                                            | COMP                      | -0.1  |     | VDD  |      |

|                                            | PGND                      | -0.1  |     | 0.1  |      |

| Junction temperature range, T <sub>J</sub> |                           |       |     | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{IN} = 3.3 \text{ V}, T_A = T_J = -40 ^{\circ}\text{C to } + 125 ^{\circ}\text{C}. \text{ Typical values are at } T_A = 25 ^{\circ}\text{C}, PGND = GND \text{ unless otherwise noted})$

| Parameter                                             | SYMBOL               | Test Conditions                                                                                                                                               | Min  | Тур  | Max  | Unit  |

|-------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| POWER SUPPLY                                          |                      |                                                                                                                                                               |      |      |      |       |

| VIN operation voltage VIN Nominal input voltage range |                      | 2.9                                                                                                                                                           |      | 5.5  | V    |       |

| VIN UVLO threshold                                    |                      | Ramp up; EN = 'HI'                                                                                                                                            |      | 2.8  |      | V     |

| VIN UVLO hysteresis                                   |                      |                                                                                                                                                               |      | 110  |      | mV    |

| VOLTAGE MONITOR                                       |                      |                                                                                                                                                               |      |      | •    | •     |

| Power good low voltage                                |                      | Pull-down voltage with 4 mA sink current                                                                                                                      |      | 60   | 200  | mV    |

| Power good high leakage current                       |                      |                                                                                                                                                               | -2.0 | 0    | 2.0  | μΑ    |

| Power good threshold                                  |                      | Feedback lower voltage limit                                                                                                                                  | 80   | 83   | 86   | %Vref |

| Power good threshold                                  |                      | Feedback higher voltage limit                                                                                                                                 | 114  | 117  | 120  | %Vref |

| Power good high delay                                 | t <sub>PGDELAY</sub> |                                                                                                                                                               |      | 400  |      | μs    |

| Output over-voltage protection threshold at FB        |                      |                                                                                                                                                               | 114  | 117  | 120  | %Vref |

| Over-voltage blanking time                            | T <sub>OVPDLY</sub>  | Time from FB higher than 20% of Vref<br>to OVP fault                                                                                                          | 1.0  | 1.5  | 2.5  | μs    |

| Output under-voltage protection threshold at FB       |                      |                                                                                                                                                               | 80   | 83   | 86   | %Vref |

| Under-voltage blanking time                           | T <sub>UVPDLY</sub>  | Time from FB lower than<br>20% of Vref to UVP fault                                                                                                           |      | 11   |      | μs    |

| SUPPLY CURRENT (T <sub>J</sub> = +25°C)               |                      | •                                                                                                                                                             |      | •    | •    | •     |

| VIN quiescent current                                 | Ivin                 | EN = 'HI', no switching                                                                                                                                       |      | 1.5  | 3.5  | mA    |

| VIN shutdown supply current                           | IVIN_SD              | EN = 'LO'                                                                                                                                                     |      |      | 15   | μΑ    |

| FEEDBACK VOLTAGE & ERROR AM                           | //PLIFIER            |                                                                                                                                                               |      |      |      |       |

| Reference voltage at FB                               | VREF                 |                                                                                                                                                               | 594  | 600  | 606  | mV    |

| Unity gain bandwidth (Note 1)                         |                      |                                                                                                                                                               | 14   |      |      | MHz   |

| Open loop gain (Note 1)                               |                      |                                                                                                                                                               | 80   |      |      | dB    |

| FB pin leakage current                                |                      |                                                                                                                                                               |      |      | 100  | nA    |

| Output sourcing and sinking current (Note 1)          |                      | C <sub>comp</sub> = 20 pF                                                                                                                                     |      | 5    |      | mA    |

| Slew rate (Note 1)                                    |                      |                                                                                                                                                               |      | 5    |      | V/μs  |

| OVER CURRENT PROTECTION & Z                           | ERO CROSSI           | NG                                                                                                                                                            |      |      |      |       |

| Over-current limit on high-side FET                   |                      | When $I_{out}$ exceeds this threshold for 4 consecutive cycles, $V_{IN}=3.3$ V, $V_{OUT}=1.5$ V with 1 $\mu$ H inductor, $F_{sw}=1.1$ MHz, $T_A=25^{\circ}$ C | 7.6  | 8.2  | 8.8  | A     |

| Hiccup time duration                                  | t <sub>hiccup</sub>  | F <sub>sw</sub> = 1.1 MHz                                                                                                                                     |      | 14.5 |      | ms    |

| Zero crossing comparator internal offset (Note 1)     |                      | PGND-SWN, Automatic CCM/DCM mode                                                                                                                              | -4.5 | -3.0 | -1.5 | mV    |

| LOGIC PINS:I/O VOLTAGE AND CU                         | RRENT                |                                                                                                                                                               |      | •    |      | •     |

| EN high threshold voltage                             |                      |                                                                                                                                                               | 1.1  | 1.18 | 1.30 | V     |

| EN hysteresis                                         |                      |                                                                                                                                                               |      | 0.18 | 0.24 | V     |

| EN input pull up resistor                             |                      |                                                                                                                                                               |      | 1.2  |      | MΩ    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Guaranteed by design, not production tested.

# **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = V_{IN} = 3.3 \text{ V}, T_A = T_J = -40 ^{\circ}\text{C to } + 125 ^{\circ}\text{C}. \text{ Typical values are at } T_A = 25 ^{\circ}\text{C}, PGND = GND \text{ unless otherwise noted})$

| Parameter                                               | SYMBOL            | Test Conditions                                                          | Min  | Тур                | Max  | Unit |  |

|---------------------------------------------------------|-------------------|--------------------------------------------------------------------------|------|--------------------|------|------|--|

| LOGIC PINS:I/O VOLTAGE AND CURRENT                      |                   |                                                                          |      |                    |      |      |  |

| PS mode threshold voltage                               | PS <sub>THS</sub> | Level 1 to Level 2                                                       |      | 0.05               |      | V    |  |

|                                                         |                   | Level 2 to Level 3                                                       |      | 1.3                |      |      |  |

| PS source current                                       | I <sub>PS</sub>   | 7 μA pull-up current when enabled                                        |      | 7                  |      | μΑ   |  |

| INTERNAL BST DIODE                                      |                   |                                                                          |      |                    |      |      |  |

| Reverse-bias leakage current                            |                   | V <sub>BST</sub> = 6.6 V, V <sub>IN</sub> = 3.3 V, T <sub>A</sub> = 25°C |      |                    | 1    | μΑ   |  |

| SOFT STOP                                               |                   |                                                                          |      |                    |      |      |  |

| Output discharge on-resistance                          |                   | EN = 0, V <sub>IN</sub> = 3.3 V, V <sub>OUT</sub> = 0.5 V                |      | 36                 |      | Ω    |  |

| TIMERS: SOFT-START                                      |                   |                                                                          |      |                    |      | •    |  |

| Soft-Start ramp-up time Tss                             |                   | Rising from V <sub>SS</sub> = 0 V to V <sub>SS</sub> = 0.6 V             |      | 1.5                |      | ms   |  |

| Delay after EN asserting                                |                   | EN = 'HI'                                                                |      | 0.5                |      | ms   |  |

| Switching Frequency Control                             |                   | FCCM mode<br>Frequency setting = 1.1 MHz                                 | 0.99 | 1.10               | 1.21 | MHz  |  |

| PWM                                                     |                   |                                                                          |      |                    |      |      |  |

| Minimum OFF time                                        |                   | FCCM mode or<br>Automatic CCM/DCM mode                                   |      | 100                | 140  | ns   |  |

| PWM ramp amplitude (Note 1)                             |                   | 2.9 V< V <sub>IN</sub> < 6.0 V                                           |      | V <sub>IN</sub> /4 |      | V    |  |

| Maximum duty cycle, FCCM mode or Automatic CCM/DCM mode |                   | F <sub>SW</sub> = 1.1 MHz                                                | 84%  | 89%                |      |      |  |

| THERMAL SHUTDOWN                                        |                   |                                                                          | •    | •                  |      | •    |  |

| Thermal shutdown threshold (Note 1)                     |                   |                                                                          | 130  | 140                | 150  | °C   |  |

| Thermal shutdown hysteresis (Note 1)                    |                   |                                                                          |      | 40                 |      | °C   |  |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

1. Guaranteed by design, not production tested.

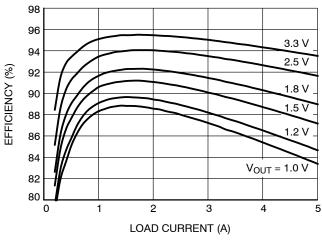

# **TYPICAL CHARACTERISTICS**

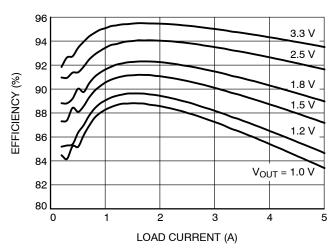

Figure 3. Efficiency at Vin = 5.0 V FCCM Operation Mode

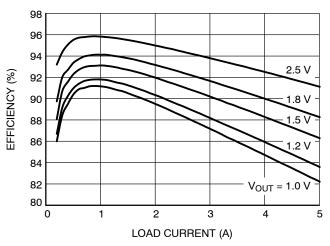

Figure 4. Efficiency at Vin = 5.0 V Auto CCM/DCM Operation Mode

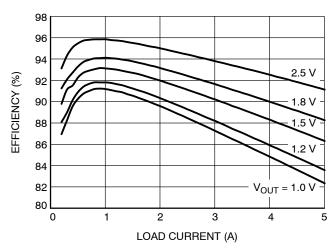

Figure 5. Efficiency at Vin = 3.3 V FCCM Operation Mode

Figure 6. Efficiency at Vin = 3.3 V Auto CCM/DCM Operation Mode

# **DETAILED DESCRIPTION**

#### Overview

NCP3136 is a low input voltage high performance synchronous buck converter with two integrated N-MOSFETs. NCP3136's output voltage range is from 0.6 V to 0.84 x Vin and it has wide input voltage range from 2.9 V to 5.5 V. The features of NCP3136 include supporting pre-bias start-up to protect sensitive loads, cycle-by-cycle over-current limiting and short circuit protection, power good monitor, over voltage and under voltage protection, built in output discharge and thermal shutdown.

NCP3136 provides two operation modes to fit various application requirements. The automatic CCM/DCM mode operation provides reduced power loss and increases the efficiency at light load. The adaptive power control architecture enables smooth transition between light load and heavy load while maintaining fast response to load transients.

#### **Operation Mode**

In forced continuous conduction mode (FCCM), the high-side FET is ON during the on-time and the low-side FET is ON during the off-time. The switching is synchronized to an internal clock thus the switching frequency is fixed.

In Automatic CCM/DCM mode, the high-side FET is ON during the on-time and low-side FET is ON during the off-time until the inductor current reaches zero. An internal zero-crossing comparator detects the zero crossing of the inductor current from positive to negative. When the inductor current reaches zero, the comparator sends a signal to the logic circuitry and turns off the low-side FET.

When the load is increased, the inductor current is always positive and the zero-crossing comparator does not send any zero-crossing signal. The converter enters into continuous conduction mode (CCM) when no zero-crossing is detected for two consecutive PWM pulses. In CCM mode, the switching synchronizes to the internal clock and the switching frequency is fixed.

# **VDD Voltage**

The VDD voltage is supplied from VIN via an intrenal resistor. Meanwhile, it is also ok to short the VDD pin and VIN pins externally.

## Reference Voltage

The NCP3136 incorporates 600 mV reference voltage with 1.0% tolerance.

#### Internal Soft-Start

To limit the start-up inrush current, an internal soft start circuit is used to ramp up the reference voltage from 0 V to its final value linearly. The internal soft start time is 2.0 ms typically.

#### **Soft Stop**

Soft–Stop or discharge mode is always on during faults or disable. In this mode, disable (EN) causes the output to be discharged through an internal 40  $\Omega$  transistor inside of SW terminal. The time constant of soft–stop is a function of output capacitance and the resistance of the discharge transistor.

# **Automatic Power Saving Mode**

In Automatic CCM/DCM mode when the load current decreases, the converter will enter power saving mode operation. During power saving mode, the low-side MOSFET will turn off when the inductor current reaches zero. So the converter skips switching and operates with reduced frequency, which minimizes the quiescent current and maintains high efficiency.

# **Forced Continuous Conduction Mode**

When PS pin is floating or pulled high, NCP3136 is operating in forced continuous conduction mode in both light load and heavy load conditions. In this mode, the switching frequency remains constant over the entire load range, making it suitable for applications that need tight regulation of switching frequency at a cost of lower efficiency at light load.

#### **PROTECTIONS**

# **Under Voltage Lockout (UVLO)**

There is under-voltage lock out protection (UVLO) for VIN in NCP3136, which has a typical trip threshold voltage 2.8 V and trip hysteresis 130 mV for VIN. If UVLO is triggered, the device resets and waits for the voltage to rise up over the threshold voltage and restart the part. Please note this protection function DOES NOT trigger the fault counter to latch off the part.

# **Over Voltage Protection (OVP)**

When feedback voltage is above 17% (typical) of nominal voltage for over 1.7 µs blanking time, an OV fault is set. In this case, the converter de-asserts the PGD signal and performs the over-voltage protection function. The top gate drive is turned off and the bottom gate drive is turned on to discharge the output. The bottom gate drive will be turned off until VFB drops below the UVP threshold. The device enters a high-impedance state. This protection is latched.

# **Under Voltage Protection (UVP)**

Output under-voltage protection works in conjunction with the current protection described in the Over-current Protection sections. An UVP circuit monitors the feedback voltage to detect under-voltage event. The under-voltage limit is 17% (typical) below of nominal voltage at FB pin. If the feedback voltage is below this threshold over 11  $\mu$ s, an UV fault is set and both the high-side and the low-side FETs turn off. After a hiccup delay, the part tries to restart. This protection behavior is hiccup.

## **Power Good Monitor (PGD)**

NCP3136 provides window comparator to monitor the output voltage at FB pin. When the output voltage is within  $\pm 17\%$  of regulation voltage, the power good pin outputs a high signal. Otherwise, PGD stays low. The PGD pin is open drain 5 mA pull down output. During startup, PGD stays low until the feedback voltage is within the specified range for about 0.4 ms. If feedback voltage falls outside the tolerance band, the PG pin goes low after 10  $\mu$ s delay.

The PGD pin de-asserts as soon as the EN pin is pulled low or an under-voltage event on VDD is detected.

# **Over Current Protection (OCP)**

NCP3136 provides high-side MOSFET current limiting. When the current through the high-side FET exceeds 7.5 A, the high-side FET turns off and the low-side FET turns on until next PWM cycle. An over-current counter is triggered and starts to increment each occurrence of an over-current event. Both the high-side and the low-side FETs turn off when the OC counter reaches four. The OC counter resets if the detected current is less than 7.5 A after an OC event.

#### Pre-Bias Startup

In some applications the controller will be required to start switching when its output capacitors are charged anywhere from slightly above 0 V to just below the regulation voltage.

This situation occurs for a number of reasons: the converter's output capacitors may have residual charge on them or the converter's output may be held up by a low current standby power supply. NCP3136 supports pre-bias start up by holding low-side FETs off until soft start ramp reaches the FB pin voltage.

# **Thermal Shutdown**

The NCP3136 protects itself from over heating with an internal thermal monitoring circuit. When the die temperature goes beyond a threshold value 135°C, both the high-side and the low-side FETs turn off until the temperature falls 40°C below of the threshold value. Then the converter restarts.

#### **Application Note**

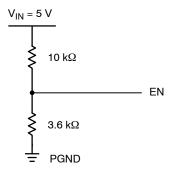

For higher output voltage application cases (Vout = 3.3 V), choose the inductor value not to be lower than 1  $\mu$ H to avoid over-current protection being triggered by inductor current ripple; For Vin = 5 V and Vout = 3.3 V case, add a voltage divider between Vin and EN to ensure that the part can start up without triggering UVP. Use Figure 7 as design reference for schematics. For other lower output voltage cases, it is not necessary to add this divider.

Figure 7. Voltage divider between VIN and EN for start-up in VIN = 5 V and VOUT = 3.3 V case

# **Layout Guidelines**

When laying out a power PCB for the NCP3136 there are several key points to consider.

Use four vias to connect the thermal pad to power ground. Separate the power ground and analog ground planes; connect them together at a single point.

Increase the thickness of PCB copper, it can help to lower the die temperature and improve the overall efficiency but meanwhile increase the cost of the board fabrication.

Use wide traces for the nodes conducting high current such as VIN, VOUT, PGND and SW.

Place feedback and compensation network components close to the IC.

Keep FB, COMP away from noisy signals such as SW,

Place VIN and VDD decoupling capacitors as close to the IC as possible.

| DOCUMENT NUMBER: | 98AON87551E      | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | QFN16, 3X3, 0.5P |                                                                                                                                                                                   | PAGE 1 OF 1 |  |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales