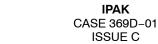

## **MECHANICAL CASE OUTLINE**

STYLE 3: PIN 1. ANODE

2. CATHODE

4. CATHODE

3 ANODE

STYLE 7: PIN 1. GATE 2. COLLECTOR

3. EMITTER

COLLECTOR

**DATE 15 DEC 2010**

STYLE 2:

PIN 1. GATE

3

STYLE 6: PIN 1. MT1 2. MT2 3. GATE

2. DRAIN

4. DRAIN

MT2

SOURCE

STYLE 1: PIN 1. BASE

3

STYLE 5: PIN 1. GATE

2. ANODE 3. CATHODE

ANODE

2. COLLECTOR

**EMITTER**

COLLECTOR

## NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

|     | INCHES    |       | MILLIMETERS |      |

|-----|-----------|-------|-------------|------|

| DIM | MIN       | MAX   | MIN         | MAX  |

| Α   | 0.235     | 0.245 | 5.97        | 6.35 |

| В   | 0.250     | 0.265 | 6.35        | 6.73 |

| С   | 0.086     | 0.094 | 2.19        | 2.38 |

| D   | 0.027     | 0.035 | 0.69        | 0.88 |

| E   | 0.018     | 0.023 | 0.46        | 0.58 |

| F   | 0.037     | 0.045 | 0.94        | 1.14 |

| G   | 0.090 BSC |       | 2.29 BSC    |      |

| Н   | 0.034     | 0.040 | 0.87        | 1.01 |

| J   | 0.018     | 0.023 | 0.46        | 0.58 |

| K   | 0.350     | 0.380 | 8.89        | 9.65 |

| R   | 0.180     | 0.215 | 4.45        | 5.45 |

| S   | 0.025     | 0.040 | 0.63        | 1.01 |

| ٧   | 0.035     | 0.050 | 0.89        | 1.27 |

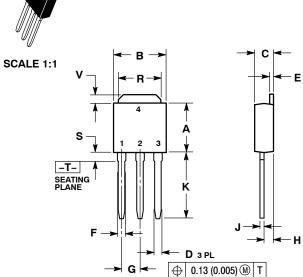

| Z   | 0 155     |       | 3 93        |      |

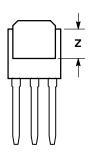

## **MARKING DIAGRAMS**

STYLE 4: PIN 1. CATHODE Integrated Circuits ANODE

GATE **Discrete** 4. ANODE YWW XXXXX ALYWW XXXXXXXX

xxxxxxxxx = Device Code Α = Assembly Location IL = Wafer Lot Υ = Year WW = Work Week

| DOCUMENT NUMBER: | 98AON10528D                 | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED |             |

|------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | IPAK (DPAK INSERTION MOUNT) |                                                                                                                                              | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.