**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# AND8010/D

# ECLinPS Lite™ MC100LVELT22 SPICE Model Kit

Prepared by Paul Shockman

**ON Semiconductor Logic Applications Engineering**

#### Introduction

The objective of this kit is to provide schematic and SPICE parameter information for performing system level interconnect modeling with the Low Voltage ECLinPS Lite Translator TTL to PECL "LVELT22" device. The LVELT22 device is a dual 1 Bit translator from LVTTL/LVCMOS levels to PECL levels. This kit contains model netlists and

## **ON Semiconductor®**

http://onsemi.com

## APPLICATION NOTE

transistor parameter descriptions for the Input and Output buffers, package models, and ESD protection networks for Input and Output circuits used by the LVELT22 device. These may be interconnected as subcircuits to simulate buffer signals.

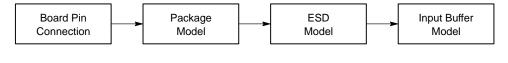

#### Subcircuit Interconnects for Input Pins

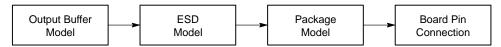

#### Subcircuit Interconnects for Output Pins

#### Figure 1. Input and Output Models

#### Input and Output Buffers

The LVTTL–LVPECL Translator subcircuits use SPICE level 3 netlists in circuit buffer models LVTTLIN and LVTTLOUT. All inputs and outputs are protected by ESD "Electro Static Discharge" protection circuitry. If the user would like to just simulate the output behavior, LVTTLOUT circuit can be stimulated with internal signals levels:

| Voltage Internal Input Low  | VIIL | VCC-1.1 |

|-----------------------------|------|---------|

| Voltage Internal Input High | VIIH | VCC-0.8 |

#### Package

The MC100LVELT22 is only packaged in the 8 pin SOIC case outline. The coupled transmission line package model, LINES, may to be added to all external pins. In this subcircuit model, all external board side connections of input, output, and supply pins are called N\*\*O and all internal chip side connections of input, output, and supply pins are referred to as N\*\*I as shown in Table 1.

Table 1.

| 8 Pin SOIC Package Model |                  |                  |  |  |

|--------------------------|------------------|------------------|--|--|

| Pin Connection           | Outside to Board | Internal to Chip |  |  |

| 1                        | N01O             | N01I             |  |  |

| 2                        | N02O             | N02I             |  |  |

| 3                        | N03O             | N03I             |  |  |

| 4                        | N04O             | N04I             |  |  |

| 5                        | N05O             | N05I             |  |  |

| 6                        | N06O             | N06I             |  |  |

| 7                        | N07O             | N07I             |  |  |

| 8                        | N08O             | N08I             |  |  |

The LINES model considers the capacitance to be lumped. Minimum (fastest) useable edge rate is 0.076 NS.

### AND8010/D

#### Modeling

The bias driver schematics for VCS and V1 generation are not included in this kit, as they are unnecessary for interconnection simulation. In addition their detailed netlist modeling would result in a relatively large increase in simulation time. Alternatively the internal reference voltages should be driven with ideal constant voltage sources. This model kit is intended for simulations within the specified power supply range. If supply voltages drop below minimum specification, VCS and V1 can no longer be assumed to be constant. Thus, this model kit should not be used for power up or power down simulations. LVPECL outputs should be terminated properly, such as through ohms to VTT=VCC-2V.

The common global nodes are as follows:

```

*100 VCC

*200 VEE

*300 VCS internal TTL reference = VEE+1.3V

*400 V1 internal TTL reference = 1.5

*10 IN

*5 QI VCC-1.1 TO VCC-0.8

*6

QIB VCC-0.8 TO VCC-1.1

*20 D

*21 DB

*60 Q

*62 QB

*1 to external PIN

*2 to internal chip CKT

*3 external PIN and internal chip CKT node

*LVTTLIN

.SUBCKT LVTTLIN 100 200 300 400 10 5 6

10

200

TN6

01 1

3

400 3

Q2 2

200

TN6

Q3 100 1

6

200

TN6

Q4 100 2

5

200

TN6

300 7

Q5 3

200

TN6

Q6

6

300

8

200

TN6

07

5

300 9

200

TN6

R1 100 1

266

* TC=0.26M, 0.9U

R2 100 1

266

* TC=0.26M, 0.9U

200 42

R3 7

* TC=0.26M, 0.9U

R4 8

200 42

* TC=0.26M, 0.9U

9 200 42

R5

* TC=0.26M, 0.9U

.ENDS LVTTLIN

.SUBCKT LVTTLOUT 100 200 300 20 21 60 62

Q1

62

20 1 200 TRANA

Q2

60

21 1

200 TRANA

03

1

300 2

200 TRANA

100 60 269

R1

* TC=0.26M, 0.9U

R2

100 62 269

* TC=0.26M, 0.9U

R3

2

200 112

* TC=0.26M, 0.9U

.ENDS LVTTLOUT

```

#### ESD

The ESD protection for the inputs pins D0 and D1 uses the subcircuit model ESDIN. In the ESDIN model, a diode (CBVCC) goes to  $V_{CC}$  with a parallel resistor of high value (75 k $\Omega$ ) and a diode pair (CBSUB devices) go to  $V_{EE}$ . The input has a series resistor. . SUBCKT ESDIN 100 200 1 2

D1 1 100 CBVCC D2 1 200 CBSUB

D3 1 200 CBSUB R1 1 VCC 75K \* TC=0.26M, 0.9U R2 1 2 93 .END ESDIN The ESD model for the PECL output pins (Q0, Q0bar, Q1, Q1bar) use subcircuit model ESDOUT. The ESDOUT is modeled as diode (CBVCC) to V<sub>CC</sub> and a diode pair (CBSUB devices) to V<sub>EE</sub>. .SUBCKT ESDOUT 100 200 1 D1 1 100 CBVCC D2 1 200 CBSUB D3 1 200 CBSUB . END ESDOUT .MODEL CBVCC D + ( IS = 1.00E15 CJO = 527fF Vj = 0.545 M = 0.32 BV = 14.5 + IBV = 0.1E6 XTI = 5 TT = 1nS ) .MODEL CBSUB D + ( IS = 1.00E15 CJO = 453fF TT = 1nS ) NPN .MODEL TN6 +(IS = 8.56E-18 BF = 120 NF = 1VAF = 30IKF = 10.5mAVAR = 5 + ISE = 4.48E-16 BR = 10 NE = 2IKR = 922uA+ IRB = 13.2uA RB = 291.4 RBM = 95.0 RE = 13.3 RC = 62.7 VJE = .9MJE = .4+ CJE = 29.9 fFXTB = 0.73+ CJC = 31.2fFVJC = .67MJC = .32 XCJC= .3 FC = .9 + CJS = 60.9 fFVJS = .6MJS = .4XTF = 10VTF = 1.4V ITF = 27.6mA + TF = 8pS TR = 1nS+ ISC=0 EG=1.11 XTI=5.2 PTF=0 KF=0 AF=1 NR = 1NC=2) .MODEL TRANA NPN +(IS = 2.09E - 17 BF = 120)NF = 1VAF = 30IKF = 25.7mA+ ISE = 1.09E-15 BR = 10 NE = 2 VAR = 5 IKR = 2.25mA + IRB = 32.2uA RB = 122.6 RBM = 42.2 RE = 5.44 RC = 32.8 + CJE = 67.4fFVJE = .9MJE = .4 XTB = 0.73 + CJC = 53.8fF VJC = .67 MJC = .32 XCJC= .3 + CJS = 103 fFVJS = .6MJS = .4 FC = .9 + TF = 8pS TR = 1nSXTF = 10 VTF = 1.4V ITF = 67.5mA + ISC=0 EG=1.11 XTI=5.2 PTF=0 KF=0 AF=1 NR=1 NC=2) 1.75 x 13.50 emitter (2 emitters) PACKAGE MODEL TRANSMISSION LINES \* CONNECT CHIP SIDE TO N\*\*I AND BOARD SIDE TO N\*\*O .SUBCKT LINES NO1I NO1O NO2I NO2O NO3I NO3O NO4I NO4O + N05I N050 N06I N060 N07I N070 N08I N080 N01M LO1WB NOli 1.367E-09 N010 L01 N01M 7.794E-10 C01 N01M 0 2.445E-13 1.287E-09 L02WB N02I N02M N02M N02O T-02 5.473E-10 N02M 0 C02 1.888E-13 LO3WB NO3I NO3M 1.287E-09 L03 N03M N030 5.473E-10 C03 N03M 0 1.901E-13 L04WB N04I N04M 1.367E-09 L04 N04M N04O 7.723E-10 N04M 2.443E-13 C04 0 L05WB N05I N05M 1.367E-09 L05 N05M N050 7.710E-10 C05 N05M 0 2.478E-13 LOGWB NOGI NOGM 1.287E-09 N06M N060 T-06 5.489E-10 C06 NOGM 0 1.916E-13

| L07WB       | N07I  | N07M  | 1.287E-09 |  |

|-------------|-------|-------|-----------|--|

| L07         | N07M  | N070  | 5.495E-10 |  |

| C07         | N07M  | 0     | 1.930E-13 |  |

| L08WB       | N08I  | N08M  | 1.367E-09 |  |

| L08         | N08M  | N080  | 7.786E-10 |  |

| C08         | N08M  | 0     | 2.451E-13 |  |

| K0102       | L01   | L02   | 0.1687    |  |

| K0102WB     | L01WB | L02WB | 0.3400    |  |

| C0102       | N010  | N020  | 3.674E-14 |  |

| K0103       | L01   | L03   | 0.0702    |  |

| K0103WB     | L01WB | L03WB | 0.1847    |  |

| K0203       | L02   | L03   | 0.1822    |  |

| K0203WB     | L02WB | L03WB | 0.3505    |  |

| C0203       | N020  | N030  | 3.521E-14 |  |

| K0204       | L02   | L04   | 0.0682    |  |

| K0204WB     | L02WB | L04WB | 0.1847    |  |

| К0304       | L03   | L04   | 0.1694    |  |

| K0304WB     | L03WB | L04WB | 0.3400    |  |

| C0304       | N030  | N040  | 3.675E-14 |  |

| K0305WB     | L03WB | L05WB | 0.1847    |  |

| K0405WB     | L04WB | L05WB | 0.3455    |  |

| K0406WB     | L04WB | LOGWB | 0.1847    |  |

| K0506       | L05   | L06   | 0.1697    |  |

| K0506WB     | L05WB | LOGWB | 0.3400    |  |

| C0506       | N050  | N060  | 3.720E-14 |  |

| K0507       | L05   | L07   | 0.0682    |  |

| K0507WB     | L05WB | L07WB | 0.1847    |  |

| K0607       | L06   | L07   | 0.1824    |  |

| K0607WB     | L06WB | L07WB | 0.3505    |  |

| C0607       | N060  | N070  | 3.570E-14 |  |

| K0608       | L06   | L08   | 0.0702    |  |

| K0608WB     | LOGWB | L08WB | 0.1847    |  |

| K0708       | L07   | L08   | 0.1691    |  |

| K0708WB     | L07WB | L08WB | 0.3400    |  |

| C0708       | N070  | N080  | 3.632E-14 |  |

| .ENDS LINES |       |       |           |  |

|             |       |       |           |  |

ECLinPS Lite and ECLinPS Plus are trademarks of Semiconductor Components Industries, LLC.

**ON Semiconductor** and **ON** are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death wits such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.