**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# AMIS-4168x Fault Tolerant CAN Transceiver

# Start-up Behavior

### Prepared by:

**ON** Semiconductor

### Introduction

This document discusses the start-up behavior of AMIS-41682.

### Schematic Diagram

# **ON Semiconductor®**

http://onsemi.com

# **APPLICATION NOTE**

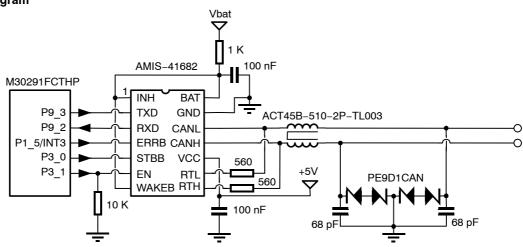

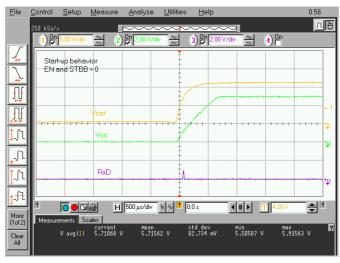

Figure 1. Application Diagram CANLSFT

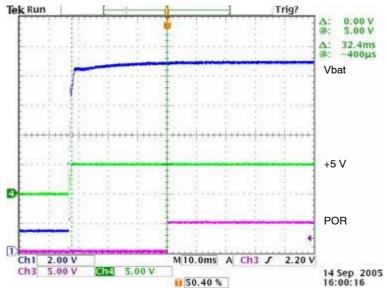

In Figure 1 the customer schematic diagram of the application is illustrated. The microcontroller is supplied from the same 5 V regulator. An internal POR keeps all I/O's in tri–state (HiZ) during 32 ms. See also Figure 2.

Figure 2. POR of the Microcontroller

### **Customer Observation**

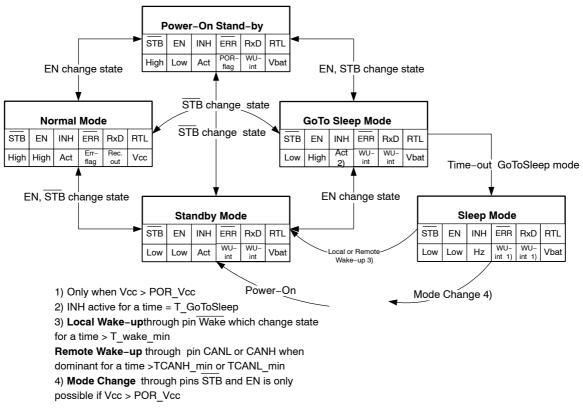

After start-up one would expect RXD = 1. This is based on the state diagram as illustrated in Figure 3.

Figure 3. State Diagram Low Power Modes

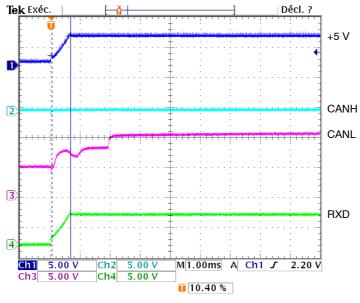

Because both EN = 0 and STBB = 0 the IC will enter stand-by mode. The RXD pin will output the WU detector. Because WAKEB is connected to Vbat (see Figure 1) and because there is no dominant state on the CAN-bus (see Figure 4) RXD is expected to stay "1".

Figure 4. Expected Start-up Behavior

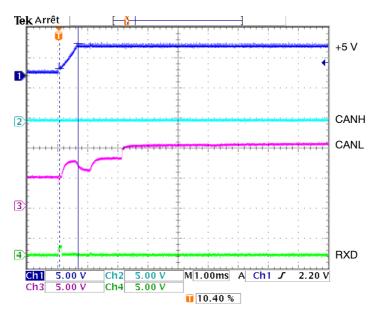

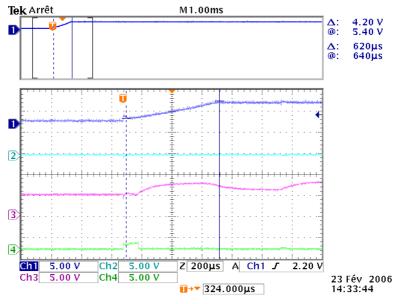

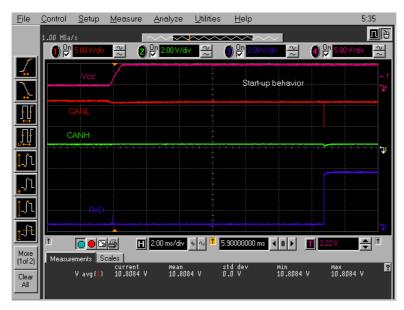

This expected behavior is only seen from time to time. In most cases the RXD stays low. This is illustrated in Figure 5. It looks like RXD is starting up correctly, but turns to zero after about hundred microseconds. Figure 6 is a zoom in.

Figure 5. Observed Start-up Behavior

Figure 6. Zoom In of Observed Start-up Behavior

### Observations

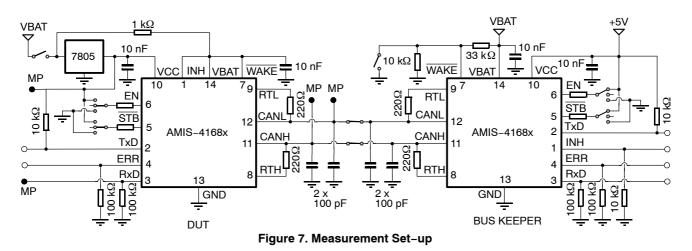

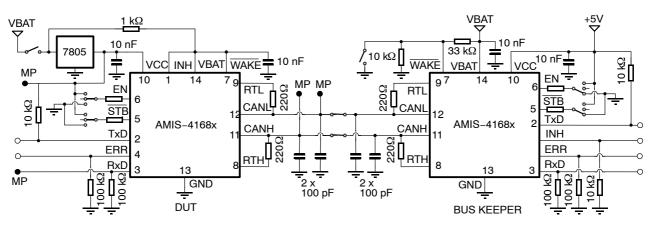

Figure 7 illustrates the used measurement set-up. Different switches allow isolation of the CAN-bus; to put EN and STBB to ground, VCC or floating; to create a wake-up and to switch on/off the power. A separate 5 V regulator ensures that the +5 V is powered up synchronous to Vbat. The left transceiver is the device under test (DUT). The transceiver on the right is used as buskeeper to put the

CAN-bus in a permanent dominant state. This IC is permanent supplied.

Used equipment:

- Oscilloscope type: Agillent Infiniium 600 MHz, 4 GSa/s

- Power supply: Thurlby Thandar Instruments PL320QMD

The oscilloscope plots are showing the signals measured on the different measurement points (MP).

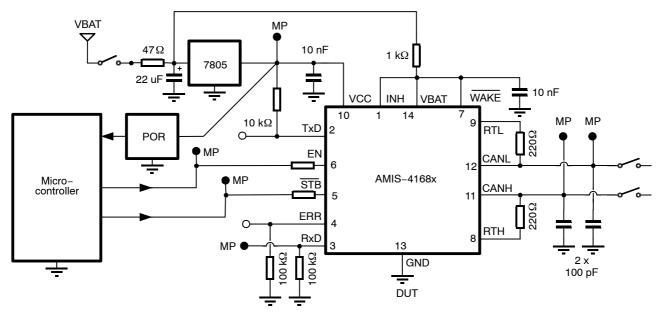

Figure 8. Power- up using set-up in Figure 7. The CAN-bus is in a permanent recessive state (CANL = VCC). RxD becomes high after power-up of VCC.

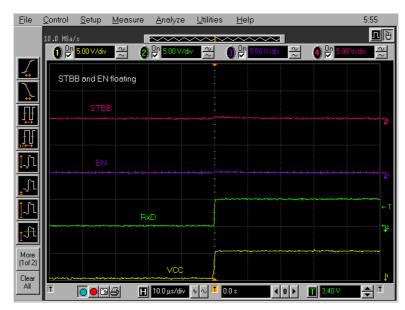

Figure 9. Power-up using set-up in Figure 7. Both STBB as EN are kept floating. The internal pull down resistors are keeping both levels low, also, during the rising edge of VCC. RxD becomes high after power-up of VCC.

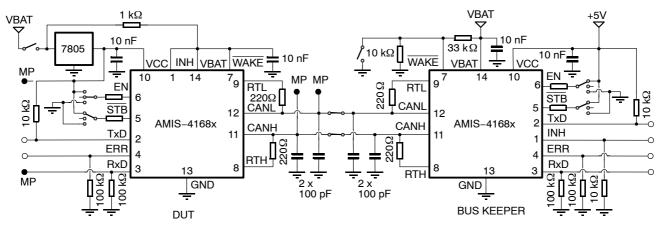

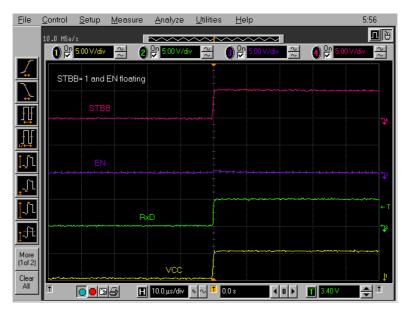

Figure 10. Measurement Set-up: Buskeeper in Stand-by State: EN = STBB = 0

Figure 11. Power-up using set-up in Figure 10. The CAN-bus is in a permanent recessing state (CANL = VBAT) with the buskeeper in stand-by state. RxD becomes high after power-up of VCC.

Figure 12. Measurement set–up: buskeeper in normal mode: EN = STBB = 1. For DUT EN = floating (internally pulled down) and STBB = 1.

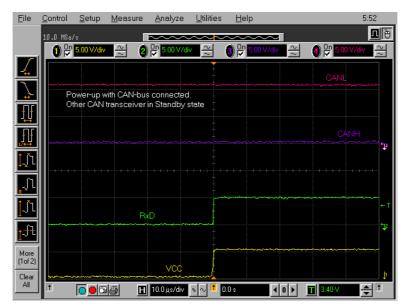

Figure 13. Power-up using set-up in Figure 12. The CAN-bus is in a permanent recessive state (CANL = VCC) with the buskeeper in normal mode.

STBB = 1 and EN is floating (pulled down internally). RxD becomes high after power-up of VCC.

Figure 15. Power-up using set-up in Figure 14. The CAN-bus is open. RxD becomes high after power-up of VCC.

### **Proposed Start-up Procedure**

Under very specific conditions (the individual power-on rise time and delay between Vcc and Vbat) the chance exists that RxD stays 0 after start-up. This very specific condition is illustrated in Figure 16.

Figure 16. RxD stays low under specific conditions for Vcc and Vbat rise times and delay.

By changing the power-on rise times and/or changing the delay between Vbat and Vcc, it is possible to increase the probability to have RxD = 1, but this probability can never be guaranteed to be one.

For that reason ON Semiconductor advises to perform a short initialization using the digital input pins STBB and EN as described in Table 1. See also Figure 3.

### **Table 1. Initialization Sequence**

| State                | STBB | EN | Duration            |  |

|----------------------|------|----|---------------------|--|

| Start-up             | х    | Х  | -                   |  |

| Power-on<br>stand-by | 1    | 0  | 6.4 μs              |  |

| Normal mode          | 1    | 1  | 5.8 μs              |  |

| GoTo sleep mode      | 0    | 1  | Time out GoTo sleep |  |

| Sleep mode           | 0    | 1  |                     |  |

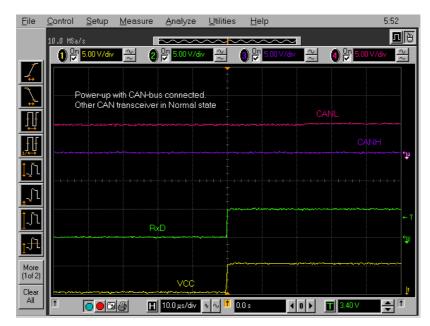

This sequence guarantees 100 percent that RxD = 1. Measurements were done using the test set-up illustrated in Figure 17. When the power is switched on the POR circuit is creating a "start-pulse" to the microcontroller triggering the sequence on the STBB and EN pins:

Figure 17. Measurement Set-up to Check the Initialization

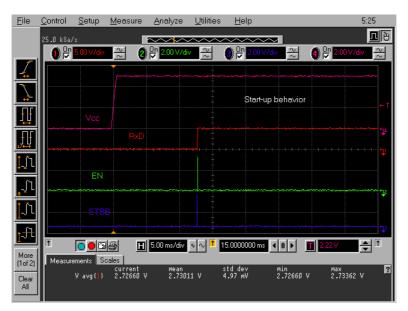

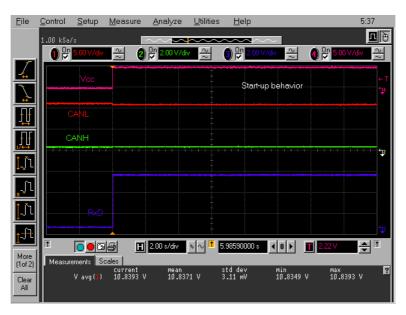

Figure 18. Start-up Behavior using the Proposed Sequence from Table 1

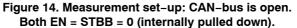

In Figure 18 the behavior is shown. Vcc comes up with a rise-time of about 600  $\mu$ s. After a POR delay of 13 ms STBB and EN are toggled. In return RxD switches high.

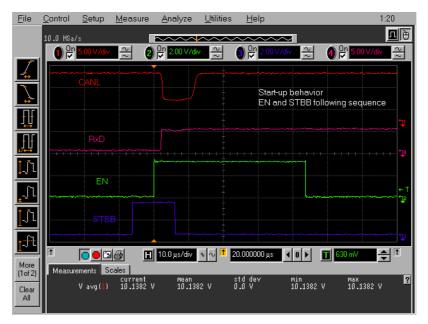

Figure 19 shows the influence on the CANL line.

| <u>F</u> ile     | <u>C</u> ontrol | <u>S</u> etup           | <u>M</u> easure    | <u>A</u> nalyze | <u>U</u> tilities | <u>H</u> elp           |                         |                                                   | 1:19       |

|------------------|-----------------|-------------------------|--------------------|-----------------|-------------------|------------------------|-------------------------|---------------------------------------------------|------------|

|                  | 50.0 kSa.       |                         |                    | $\sim$          | ~~~~              |                        | L                       |                                                   | <u>n</u> e |

|                  | <b>1 0</b> ₽⊓   | 5.00 V/div              | ₩ 2                | 0n<br>2.00 V/di | ~                 | 3 0n ≥ 2.00 V/div      | 2 ()<br>1               | <sup>Jn</sup> <mark>5.00 V/di</mark>              |            |

| 4                | ·               |                         |                    |                 |                   |                        |                         |                                                   |            |

| 2                |                 |                         |                    |                 |                   | Start-up b<br>EN and S | eha∨ior<br>TBB followin | ia sequenc                                        | æ          |

| ĮĮ               |                 |                         |                    |                 |                   |                        |                         |                                                   | <b></b>    |

| <u>, j</u> j     |                 |                         |                    |                 |                   |                        |                         |                                                   |            |

| <u>1</u> 1       |                 |                         |                    |                 |                   |                        |                         |                                                   |            |

| <u>_</u> ]l      |                 | <u></u>                 |                    |                 |                   |                        | ··                      | ~ <del>~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~</del> |            |

| <u>[</u> ]]      |                 |                         |                    |                 |                   |                        |                         |                                                   |            |

| <u>1:</u> ft     | T T             |                         |                    | 2.00 ms/div     | 9 Q 1             | 5.00020000 ms 【        |                         | 30 mV                                             | *₽<br>€  1 |

| More<br>(1 of 2) | Measur          |                         | cales  <br>current | mean            |                   |                        | ain <b>L</b>            |                                                   | _          |

| Clear<br>All     |                 | V avg( <mark>1</mark> ) | 10.7279 V          | 10.723          | 79 V              | 0.0 V 1                | 10.7279 V               | max<br>10.7279 \                                  | , u        |

Figure 19. Start-up behavior using the proposed sequence from Table 1. Influence on the CANL line.

Figure 20. Zoomed in View of Figure 19

Because we enter the normal mode for 5.8  $\mu$ s, CANL is pulled–up via RTL to Vcc for a very short while: 9.6  $\mu$ s. This is about 1.2 Tbit (for baudrate = 125 kbit/s).

This short change in termination voltage level does not influence the communication on the bus because it stays a clean recessive level. (The CANL level is under all conditions above the maximum receiver threshold level = 3.4 V).

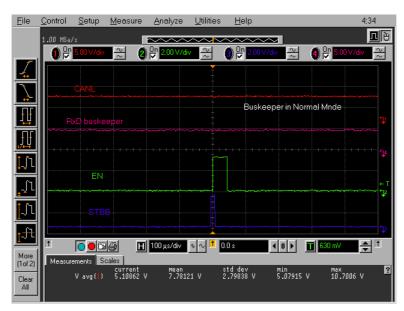

To evaluate this, the buskeeper is (re)connected to the CAN bus. (See Figures 10 and 12). With the buskeeper in stand-by mode, RxD\_buskeeper is monitored. As shown in Figure 21 no effect is observed. The CAN bus stays in recessive state and no wake-up is possible.

Figure 21. Buskeeper in stand-by mode. CANL termination switched from Vbat to Vcc for a short while (1.2 Tbits). No influence seen on RxD\_buskeeper.

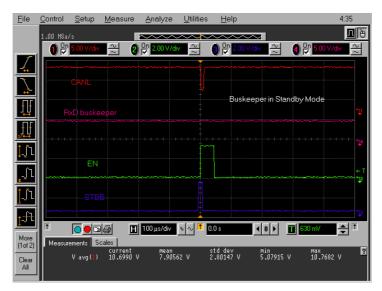

With the buskeeper in normal mode the bus will be terminated to Vcc and ground (respectively for CANL and CANH). As a result the short "change" in bus termination voltage will even not be observable. Also in this case RxD\_buskeeper is monitored. As shown in Figure 22 no effect is observed. The CAN bus stays in recessive state and RxD\_buskeeper is kept high.

Figure 22. Buskeeper in normal mode. CANL termination switched to Vcc. No influence seen on CANL and on RxD\_buskeeper.

Figures 23 and 24 are showing the influence on both CANL as CANH in a zoomed in and zoomed out time-scale. As can be seen the short change in CANL termination is hardly detectable on the oscilloscope (only in glitch mode), and for long time-base settings it can't be even observed.

Figure 23. CANL termination switched from Vbat to Vcc for a short while (1.2 Tbit). No influence seen CANH. RxD switches high after the POR time-out.

Figure 24. The CANL termination switched from Vbat to Vcc is not observable on a bigger time scale.

### Conclusion

Under very specific conditions of power-on rise time and delay between Vbat and Vcc, it is possible that RxD stays 0 after start-up.

To guarantee that always RxD = 1 after start-up, it is advised to run a short sequence using the digital input pins STBB and EN. The side effect of this sequence is that the transceiver enters Normal Mode for a few micro-seconds. This results in a short change in termination of the CANL line from Vbat to Vcc. The duration of this change in termination is about 1.2 Tbit for a given baud-rate = 125 kbit/s.

There is no effect on communication because the CANL level always stays above the receiver dominant threshold.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer applications by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product create a situation where personal nipury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use pay static copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative