**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# An Introduction to LDO Early Warning Function

### Abstract

In today's world of high speed, high power processors, new demands have been placed on the power source regulator. One example is the need to inform the processor in advance of an impending drop in supply voltage below a critical value. A common supervisory feature found in automotive LDOs is the Reset signal. When the input voltage is disconnected or lower than minimum operating voltage, the output voltage of regulator will decreases below the reset function threshold and the LDO activates a processor reset output. When an unanticipated Reset signal is received by the processor, important data is often lost because it has no time to save that data.

This application note describes in detail the LDO Early Warning feature, which prevents the aforementioned loss of data by monitoring the input voltage and warning the processor in advance of an impending condition where a Reset signal will occur.

### Introduction

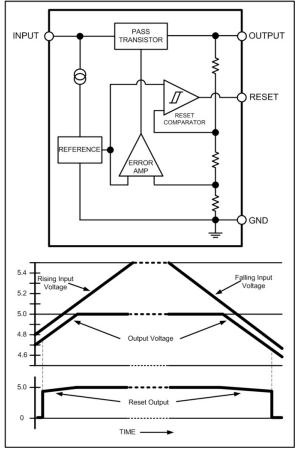

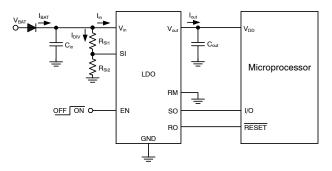

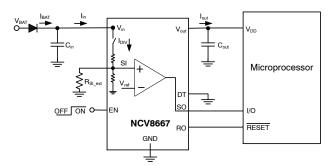

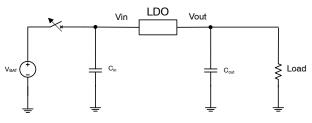

Low-dropout ("LDO") series regulators are often selected to power microprocessor ( $\mu$ P) devices in critical systems. LDO devices designed for these applications typically include a logic-level Reset output to interface with the processor. When the regulator output voltage is within tolerance limits, the Reset output will be high. When the output voltage falls below a preset or user-programmed level, either due to overload or low input voltage, the Reset output is asserted low. Often, assertion of the Reset output is delayed by interposing a timer between the comparator and output. The delay timer provides immunity to transient events that will not pose a threat to the system. Figure 1 depicts the block diagram and operating input-output waveforms of a basic LDO series regulator with Reset function.

Despite the control advantages afforded by LDO devices with integrated Reset functions, they may not protect the system against all potential consequences of loss or interruption of the regulator input voltage. If the input voltage drops below the minimum level required to maintain the output in regulation, an unanticipated Reset output state change can occur, which may reset the processor before critical data has been saved and/or benign system conditions established.

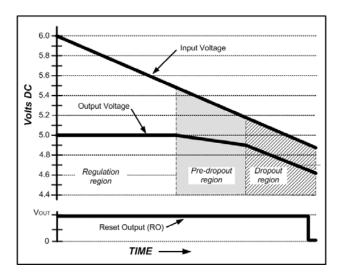

Figure 2 represents a graphical depiction of this scenario. LDO input voltage, output voltage, and Reset output (RO) are all plotted as a function of time during an input voltage ramp down. As input voltage decays, three distinct operational regions are encountered:

# **ON Semiconductor®**

http://onsemi.com

# **APPLICATION NOTE**

Figure 1. Basic LDO with Reset

<u>Regulation region</u>. Here, the input–output differential voltage ( $V_{IN} - V_{OUT}$ ) exceeds the LDO maximum dropout voltage and Vout is relatively independent of Vin.

<u>Pre-dropout region</u>. This region, which begins approximately where the decaying input-output differential voltage crosses the LDO maximum dropout voltage, is characterized by degraded line regulation. Vout may remain within the specified tolerance band, but exhibits a marked  $V_{IN}$  dependence.

<u>Dropout region</u>. From this point onward, the LDO is in dropout and Vout falls in lockstep with decaying  $V_{IN}$ . The LDO output is no longer in regulation and RO is asserted.

Figure 2. LDO Reaction to Decaying Input Voltage

One practical solution to this problem is the detection of  $V_{\rm IN}$  approaching the pre-dropout region, combined with an additional logic path between LDO and processor. This logic output allows the LDO regulator to provide the host processor with early warning of an impending unplanned assertion of the Reset output.

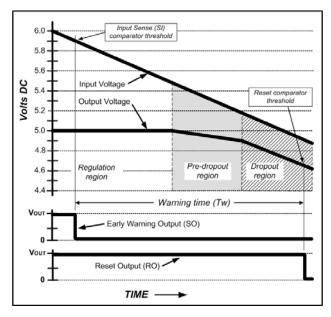

Figure 3. Early Warning Implemented by Input Voltage Detection

The processor can then be programmed to implement appropriate countermeasures to prevent loss of data or other undesirable consequential events. LDO regulator devices are now available with an integrated Early Warning  $V_{IN}$  monitoring function, typically consisting of a reference, comparator, and logical output driver.

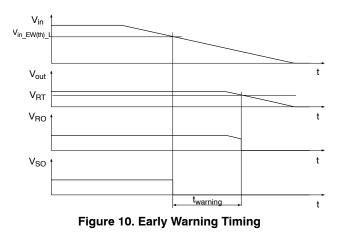

Figure 3 describes the operating characteristics of this feature during decay on the regulator input voltage, Vin. For this example, the input voltage sense (early warning)

output SO is designed to change state as  $V_{IN}$  crosses 5.9 V, and the Reset output (RO) is designed to change state when the regulator output voltage crosses 4.65 V. The consequential Warning time (labeled Twarning) is a direct function of the difference between the SI and Reset thresholds, and an inverse function of the rate of regulator input voltage decay.

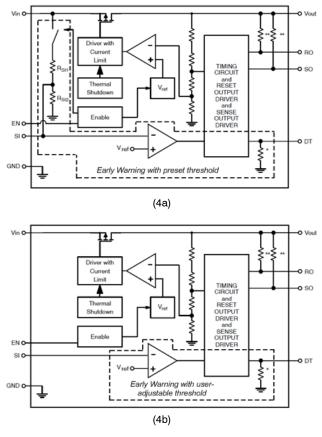

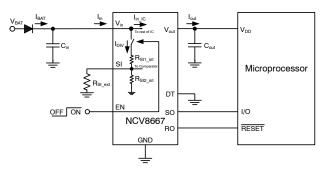

Figures 4a and 4b depict simplified block diagrams of an LDO regulator product family with integral early warning function, the NCV8667. In both figures, the elements that comprise the early warning function are outlined by a dashed line. The early warning input pin is labeled SI (sense in) and the early warning output logic–level pin is labeled SO (sense out).

Figure 4. LDO Devices Incorporating an Early Warning Function

The regulator of Figure 4a includes an internal resistor divider to scale the input sense (SI) threshold, whereas the regulator of Figure 4b does not. With the latter device, an external resistor divider is required to set the threshold. The internal divider resistance of 1 M $\Omega$  can achieve a lower quiescent current contribution than practical values of precision external resistors, and is switched out when the regulator is not enabled, markedly reducing standby current.

### New EW resistor divider idea

Consider Adjustable Early Warning Threshold option where is the EW threshold is adjusted by external EW resistor divider as shown in Figure 5. The values for  $R_{SI1}$  and  $R_{S12}$  are selected for a typical threshold (i.e. 1.25 V) on the SI pin according to eq.1 and eq.2 where Vin\_EW(th) is demanded value of input voltage at which Early Warning signal has to be generated. The higher the values of resistors  $R_{S11}$  and  $R_{S12}$  are, the lower is current flowing through the resistor divider. Because the divider is put outside the chip more quiescent current flows from the battery. The values of resistors are usually limited to few hundreds of kilohms (i.e. 200 k $\Omega$  or 250 k $\Omega$ ).

Figure 5. An LDO with External EW Divider

$$V_{in\_EW(th)\_Low} = 1.25 \left(1 + \frac{R_{Sl1}}{R_{Sl2}}\right)$$

(eq. 1)

$$R_{SI1} = R_{SI2} \left( \frac{V_{in\_EW(th)\_Low}}{1.25} - 1 \right)$$

(eq. 2)

The benefit of internal EW resistor divider is shown in following example. There is an LDO with external EW divider shown in Figure 5 and NCV8667 with internal EW divider shown in Figure 6.

Figure 6. NCV8667 with Internal EW Divider

### **Application Quiescent Current Reduction**

If  $V_{in EW_{th}}$  is required to be set to 5.9 V using an Ultra Low  $I_q$  LOO with external EW resistor divider then:

$R_{\rm SI1} = 200 \text{ k}\Omega \text{ } R_{\rm SI2} = 51 \text{ k}\Omega$

$I_{\rm BAT} = I_{\rm DIV} + I_{in} = 52.6 \; \mu {\rm A} + 28 \; \mu {\rm A} = 80.6 \; \mu {\rm A}$

\*  $I_{\rm DIV}$  is current flowing through external EW resistor divider,  $I_q$  is quiescent current of an LDO

The advantage of an internal (on chip) EW resistor divider is that these resistor values can be significantly higher than external resistors and hence, lower quiescent current from batter. In the NCV8667/69 family the total internal EW divider resistance value is 1 M $\Omega$  (i.e.  $R_{SI\_int1} = 480 \text{ k}\Omega$  and  $R_{SI\_int2} = 520 \text{ k}\Omega$ ).

If  $V_{in\_EW\_th}$  is required to be set to 5.9 V using NCV8667 with internal EW divider only one external resistor  $R_{SI\_ext}$  is required:

$R_{SI ext} = 150 k\Omega$

$I_{BAT} = I_{in} = I_{DIV} + I_{in \ IC}^* = 50.6 \ \mu A$

\*  $I_{DIV}$  includes current flowing through EW resistor divider including also  $R_{SI\_ext}$  current,  $I_{in\_IC}$  is quiescent current of the rest of IC @Vin = 13.2 V

The quiescent current from battery is 30  $\mu$ A lower when the EW resistors are internal comparded to when they are external.

### Application Shutdown Current Reduction

Quiescent current savings become more apparent in shutdown mode. During shutdown, the internal EW resistor divider of the NCV8667 is disconnected from battery via an internal switch.

$I_{BAT} = I_{DIV} + I_{DIS} = 52.6 \ \mu A + 1 \ \mu A = 53.6 \ \mu A$

\*  $I_{DIV}$  is current flowing through external EW resistor divider,  $I_{DIS}$  is shutdown current of an LDO

In case of NCV8667 there is no current flowing through the EW resistor divider because it is disconnected from supply by an internal switch and then:

$I_{BAT} = I_{DIV} + I_{DIS} = 0 \ \mu A + 1 \ \mu A = 1 \ \mu A$

\*  $I_{DIV}$  is current flowing through internal EW resistor divider (~0  $\mu$ A in shutdown mode),  $I_{DIS}$  is shutdown current

The difference is 52.6  $\mu$ A which is significant reduction of battery current in shutdown mode.

### Setting EW threshold using R<sub>SI ext</sub>

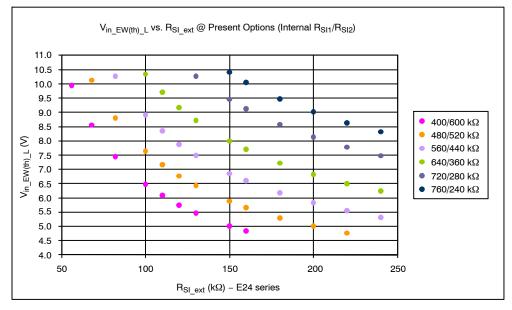

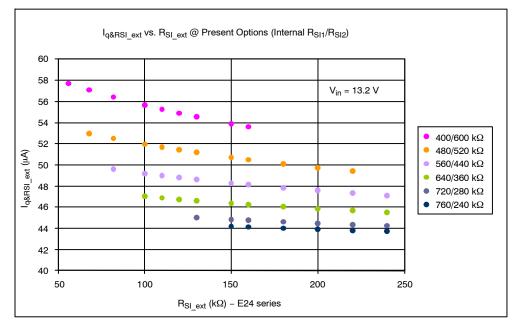

Preset Early Warning Threshold options can be adjusted externally using  $R_{SI\_ext}$  resistor connected between input monitor SI and GND as shown in Figure 6. The value for  $R_{SI\_ext}$  is recommended to be selected in range from 50 k $\Omega$ to 250 k $\Omega$  and the voltage of EW threshold can be set according to Figure 7. The higher the  $R_{SI\_ext}$  resistance is the lower the overall Quiescent Current of the application (see Figure 8) is. General formulas for calculation of  $V_{in\_EW(th)\_L}$  and  $R_{SI\_ext}$  for selected preset Early Warning options are described by eq.3 and eq.4.

## AND9120/D

Figure 7. Input Voltage EW Threshold Low vs.  ${\rm R}_{\rm SI\_ext}$  (calculated using E24 series)

Figure 8. Quiescent Current vs.  $\mathrm{R}_{\mathrm{SI}\_\mathrm{ext}}$  (calculated using E24 series)

### Twarning Calculation

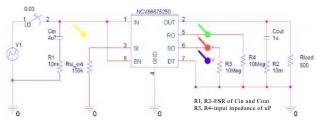

The EW function can be used for checking minimum supply voltage required for reliable operation of the NCV8667. An on-chip comparator is available to provide the special signal to microprocessor. If the battery is decreasing (e.g. supply connector disconnection) the uP receives the information via SO signal which can be processed by dedicated DI pin of the uP. EW topology is illustrated in Figure 9.

Figure 9. Early Warning Application Circuit

The early warning function compares a voltage defined by the user to an internal reference voltage (i.e. 1.25 V). Therefore the supervised voltage has to be scaled down by external or internal voltage divider in order to compare it. The timing of EW is shown in Figure 10.

When the input voltage decreases below preset EW threshold then SO output goes low. The input voltage drops continuously further and when output voltage decreases below reset threshold then RO output goes low as well causing uP reset. The time between assuring SO Low and RO Low is called  $T_{warning}$  and provides to uP time to finish

necessary tasks before ressiting.  $T_{warning}$  time can be calculated by eq.5.

$$T_{warning} = \frac{\left(V_{in\_EW(th)\_Low} - V1\right).Cin}{Iout} + \frac{Ln\left(\frac{Vrt - V1 + IoutR - \frac{I}{Cout}}{\frac{1}{Cout}\left(\frac{Iout(RCout - 1)}{RCout}\right)}\right)}{-\frac{Cin + Cout}{RCinCout}}$$

(eq. 5)

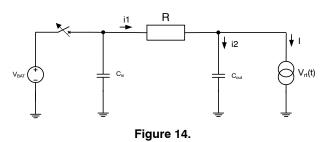

More details related to  $T_{warning}$  calculation are shown in the Appendix 1. The  $T_{warning}$  time depends on input and output capacitors values, EW threshold value and output load current. For better understanding see simplified schematic in Figure 11.

Figure 11. Simplified Schematic for T<sub>warning</sub> Calculation

**Operating Conditions:**

$$\begin{split} V_{in} &= 13.2 \ V \\ V_{EW\_th\_l} &= 5.89 \ V \\ V_{rt} &= 4.65 \ V \\ C_{in} &= 4.7 \ \mu F \\ C_{out} &= 1 \ \mu F \\ I_{out} &= 10 \ mA \end{split}$$

Using eq.5 for calculation the T<sub>warning</sub> is 890 ms.

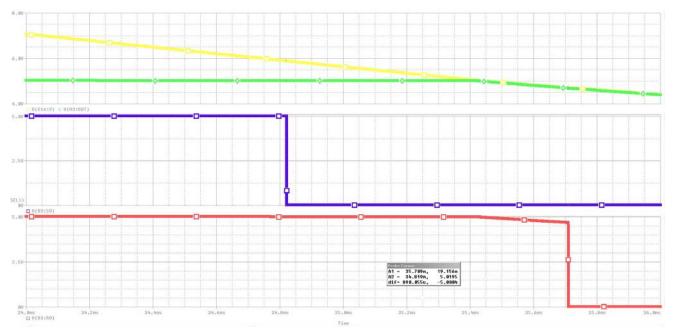

For determination of  $T_{warning}$  also PSpice model of NCV8667[2] can be used. The schematic and simulation results for  $T_{warning}$  can be seen in Figure 12 and Figure 13.

Figure 12. Simplified Schematic for T<sub>warning</sub> Calculation

# AND9120/D

Figure 13. PSpice Simulation Results for Twarning

### Conclusion

The NCV8667/69 families bring significant reduction of both quiescent and shutdown currents in the battery supplied applications, and hence, enable longer battery life thanks to unique idea of internal EW resistor divider and internal disconnect switch.

The EW threshold can be adjusted with just one external resistor which saves number of components required for EW function and space on PCB.

### **Reference:**

- 1. NCV8667 datasheet http://www.onsemi.com/pub\_link/Collateral/NCV 8667-D.PDF

- 2. PSpice model

- http://www.onsemi.com/PowerSolutions/supportD oc.do?type=models&rpn=NCV8667

# APPENDIX 1: CALCULATION OF Twarning

Schematic:

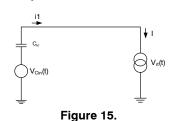

Step 1: Regulation and Pre-dropout region  $\Delta V = V_{in EW(th) Low} - V_1$  (Input voltage before dropout) Then  $V_1 = V_{out} + V_{DO}$  $t1 = \Delta V . C_{in}/I$

And  $I = I_{out} + I_a$

$$t1 = \frac{\left(V_{in\_EW(th)\_Low} - V1\right).Cin}{I}$$

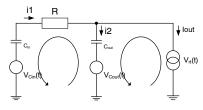

Step 2: Dropout region  $\Delta V = 5.3 V - V_{rt}$  (typ. 4.75 V)

Figure 16.

$V_{Cin}(0) = V1$  $V_{Cout}(0) = V1 - IR$ Iout = i1 + i2

1.

$$i1(p)R + \frac{i1(p)}{pCin} + \frac{V1}{p} - \frac{V1}{p} + \frac{IR}{p} - \frac{i2(p)}{pCout} = 0,$$

$i2(p) = lout - i1(p)$

$i1(p)\left(R + \frac{1}{pCin} + \frac{1}{pCout}\right) + lout\left(\frac{R}{p} - \frac{1}{pCout}\right) = 0$

$i1(p)\left(R + \frac{1}{pCin} + \frac{1}{pCout}\right) + lout\left(\frac{R}{p} - \frac{1}{pCout}\right) = 0 \Rightarrow$

$i1(p) = \frac{-lout(RCout - 1)}{RCout} + lout(P + \frac{Cin + Cout}{RCinCout})$

$\frac{1}{p + a} \Leftrightarrow e^{-at}$

$i1(t) = \frac{-lout(RCout - 1)}{RCout} e^{\frac{Cin + Cout}{RCinCout}t^2}$

$i2(t) = lout - i1(t)$

2.  $\frac{1}{pCout} i2(p) + \frac{V1}{p} - \frac{IR}{p} - \frac{Vrt}{p} = 0 \Rightarrow$

$Vrt(t) = \frac{1}{Cout} i2(t) + u1(t) - loutR$

$Vrt(t) = \frac{1}{Cout}\left(I - \frac{-lout(RCout - 1)}{RCout}e^{\frac{Cin + Cout}{RCinCout}t^2}\right) + V1(t)$

$\frac{Vrt - V1 + loutR - \frac{1}{Cout}}{\frac{1}{Cout}\left(\frac{lout(RCout - 1)}{RCout}\right)} = e^{\frac{Cin + Cout}{RCinCout}t} \Rightarrow t2$

$Ln\left(\frac{\frac{Vt - V1 + loutR - \frac{1}{Cout}}{RCinCout}}{\frac{1}{RCinCout}}\right) = t2$

$T_{warning} = \frac{(V_{in}EW(th)Low - V1).Cin}{lout} + \frac{Ln\left(\frac{Vt - V1 + loutR - \frac{1}{Cout}}{RCinCout}\right)}{-\frac{Cin + Cout}{RCinCout}}$

ON Semiconductor and 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without imitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and to vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

ON Semiconductor Website: www.onsemi.com

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

AND9120/D