**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

TND6199/D Rev. 0, SEPT – 2015

# Self Restoring Logic (SRL) Cell Targets Space Application Designs

© Semiconductor Components Industries, LLC, 2015 September, 2015 – Rev. 0

1

### Self Restoring Logic (SRL) Cell Targets Space Application Designs

#### Introduction

Circuit designs for space applications must address harsh radiation environments that impact Application Specific Integrated Circuit (ASIC) performance. Single high energy particles can disrupt integrated circuits if they strike sensitive circuit nodes. As feature sizes shrink and clock speeds increase, the impact becomes more significant. Semiconductor manufacturers have a variety of techniques to reduce or eliminate Single Event Effects (SEE). Some solutions include process modifications that reduce (but cannot eliminate) SEE. Here we will review Radiation Hardened by Design (RHBD) methods to improve immunity to Single Event Upsets: Triple Modular Redundancy (TMR) and Self Restoring Logic (SRL). Both methods share similar traits to provide fault tolerance for Single Event Upsets (SEUs) in ASICs. However, this paper reveals that the SRL design goes well beyond TMR in terms of demonstrated tolerance to SEUs, system performance, transistor count, and power. In short, SRL is a step beyond TMR for RHBD designs that demand fault tolerance, performance, and low power. Finally at the conclusion of this paper, it is shown that legacy SEU tolerant designs fail to provide SEU tolerance in circuits that operate at high speed; therefore if SEU tolerance is desired, there are only two options: TMR and SRL. SRL is shown to be superior herein.

#### Triple Modular Redundancy

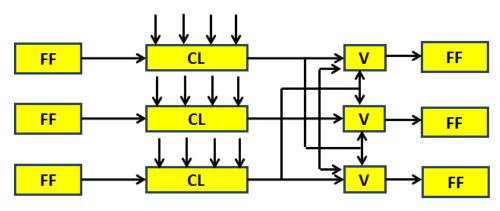

Triple Modular Redundancy (TMR) is a fault tolerant mitigation technique used to eliminate single event effects in semiconductor devices. A typical TMR implementation for single fault tolerance is shown in Figure 1.

Figure 1: Traditional TMR

Here, CL represents arbitrary combinational logic that performs addition, multiplication and more. Three voters (V) are required to eliminate the possibility that a fault to any one voter would drive an incorrect result for the entire redundant system. Each voter presents a single fault tolerant output. This design requires six flip flops (FF) and three voters which results in a larger die size and increased power consumption. Voters added to the data path and the increased area needed to accommodate triplication often reduces system performance. An additional flaw with this design is the lack of self-recovery within the flip flops which may remain

in an incorrect state as a result of single event effects. Any erroneous data contained in the flip flop is stored until at least the next clock edge latches new data. This allows a fault to remain in the TMR system until synchronously over-written which can lead to TMR failure.

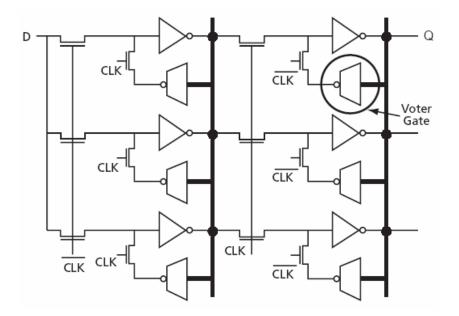

A second design implementation using the TMR methodology is shown in Figure 2. Here voters are placed in the feedback loop within the latch of the flip flop. Combinational logic is not shown for sake of simplicity.

Figure 2: TMR with voters in feedback paths

This is similar to Microsemi's fault tolerant FPGA offerings. The design consists of six latches (3 master, 3 slave) with one voter per latch, three more voters than the solution in Figure 1. Here the voters perform the self-recovery function eliminating the erroneous data flaw described above. While this approach does address self recovery in one form, it is achieved through the addition of circuitry (voters) when compared to classical TMR.

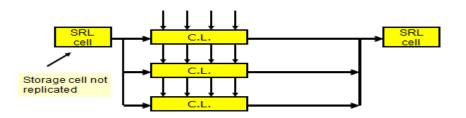

#### Self-Restoring Logic Cell

The SRL cell was designed to exceed the SEU mitigation goals of the TMR circuit. An asynchronous sequential circuit was created at the transistor level resulting in a fault tolerant flip-flop with superior features including:

- Single fault tolerance

- Three redundant storage elements

- Error correction of stored information and input data

- Self-recovery of internal faults

- Means to prevent fault propagation

- Observable internal nodes such that masked manufacturing faults are avoided

- Minimal performance overhead

- Design tool implementation (ASIC flow)

A typical design using the SRL cell is shown in Figure 3. Transistor level implementation results in a highly integrated cell. The feature set including error correction, data storage, and asynchronous self-recovery cannot be segregated into separate, discrete blocks. This results in a highly efficient solution when compared to traditional or even non-radiation hardened cell designs. Last, the SRL cell is enabled within the ON Semiconductor ASIC design tools providing circuit designers a quick and easy design solution.

SRL Design

Figure 3: SRL Design Implementation

#### Design Implementation Comparison (SRL vs. TMR)

Performing a transistor count comparison between two designs can be complex due to the numerous implementations that exist for latches and flip-flops. Here we assume that the TMR designs in figures 1 and 2 are pre-defined modules versus the SRL transistor level solution. As a result, the SRL realizes transistor-usage efficiencies up to 100% over TMR (See Table 1). Fewer transistors generally result in less power consumption, less silicon area and faster circuits.

| Design       | Number      | % increase |

|--------------|-------------|------------|

|              | Transistors | over SRL   |

| SRL Figure 3 | 60          | -          |

| TMR Figure 1 | 108         | 80%        |

| TMR Figure 2 | 120         | 100%       |

Table 1: Transistor Difference

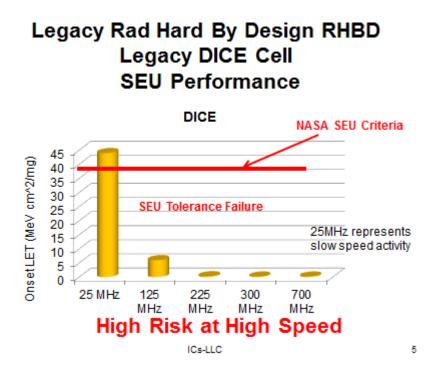

#### Radiation Test Comparison (SRL vs. DICE)

The SRL cell is a breakthrough design technology to mitigate SEU at high speed operation. The superiority of SRL was demonstrated using an ON Semiconductor 110nm test chip that included the SRL cell and legacy Dual Interlocked Cell (DICE). Radiation evaluation included Heavy Ion testing at Texas A&M University Cyclotron Institute, Total Ionizing Dose (TID) and Dose Rate testing at Boeing's Radiation Effects Laboratory and Neutron Testing at White-Sands Missile Range Fast-burst Reactor facility. While the focus of this testing is on the 110nm process, the SRL cell can be scaled to smaller technology nodes.

Figure 4 shows the SEU susceptibility of the DICE flip-flop design. Where it barely met the NASA SEU criteria at 25 MHz, the legacy design fails at low LET points when clocked at or above 125 MHz. DICE flip-flops are also very susceptible to shallow angle SEU.

Figure 4: DICE Performance at Various Clock Speeds

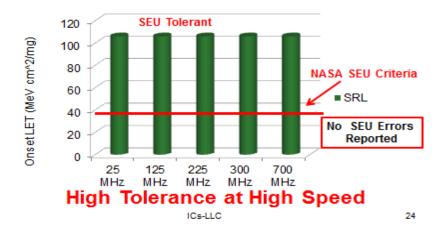

The SRL cell exhibited zero upsets up to and including an LET of 106 MeV cm<sup>2</sup>/mg through 700 MHz testing (See Figure 5). In addition, the SRL showed no upsets under shallow angle radiation.

## SRL's High SEU Tolerance

Figure 5: SRL SEU Tolerance

#### Conclusion

The SRL cell is a novel flip-flop architecture that provides superior SEU protection and better system performance while minimizing silicon area. A fault tolerant flip-flop fully integrated at the transistor level, SRL can protect against solid and transient faults equally. Internal fault detection can isolate manufacturing defects as well as hard and soft faults that occur during device operation. Currently implemented using ON Semiconductor's 110nm process node, the SRL cell is fully enabled within the design tool suite and can be scaled to sub-100nm technologies. Ideal for space electronics, other applications include autonomous vehicles, aerospace electronics and hardware security where errors may be induced into the system to compromise the application's integrity.

ON Semiconductor and the in are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative