## PORTABLE DESIGN

## Choosing the most appropriate portable product charging circuit solution

Which is right for your portable product design?

Steve Sheard and Tom Zemites — ON Semiconductor

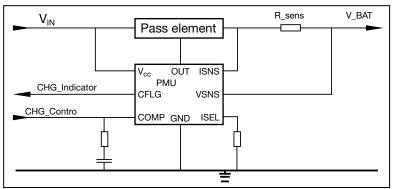

Portable products, such as DVD players, MP3 players, PDAs, cell phones, digital cameras, and digital camcorders can use one of five different topologies for the charging circuit design. Four of these solutions use an external pass element (see Figure 1); the fifth uses a fully integrated power management unit (PMU) This article will review the makeup of the external pass element and the control PMU, considering them together in design decisions.

This discussion will focus on a nominal 1-A charging circuit for a portable product. With charging currents below 500 mA the pass element is often integrated into the PMU, eliminating the external component completely. The four different topologies for the pass element are depicted in Figure 2.

*Figure 1.* All four available charging circuit topologies use a control power management unit (PMU) with an external pass element.

The selection of the pass element will depend on a number of different factors and the importance of each of them to the design. These include power losses, package design for thermal dissipation, multiple functions of the pass element and drive circuit configuration, component count with PCB footprint and package height, ESD tolerance, switching efficiency, and price.

ONLINE

**Power loss** in the pass element is an important component of circuit efficiency. The smaller the voltage drop is across the pass element, the lower the power loss will be. Topologies A and B both have Schottky diodes that tend to have a relatively high voltage drop across them, causing a higher loss (Vf = 400 mV at 1 A would be 400 mW, plus the loss in the MOSFET RDS-ON = 60 m $\Omega$  at 1 A would be 60 mW, for a total of 460 mW). Topology C is a low VCEsat BJT for which the designer also

has to consider the drive current losses and add them to the loss across the BJT (VCEsat = 70 mV at Ic = 1 A, Ib = 10 mA, and Rb = 200  $\Omega$  would have a total power loss of 120 mW). Topology D uses two modern trench MOSFETs in series where both devices add to the loss (RDS-ON = 60 m $\Omega$  at 1A would be 60 mW, for a total of 120 mW for the pair).

Package design of the pass element plays a major role in linear regulating charging-circuit thermal considerations. The heat caused during the linear regulation at 1 A in the ultrasmall package becomes very focused in one location on the PCB. One way to dissipate this heat is by using separate packaged components,

| A – MOSFET and<br>Schottky diode in<br>separate packages          | <b>B</b> – MOSFET and<br>Schottky diode in one<br>package | <b>C</b> – Low VCEsat<br>bipolar transistor<br>BJT | <b>D</b> – Dual MOSFETs<br>in one package                       |

|-------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|

| NTLJS3113P, WDFN2X2<br>NTHS4101P, ChipFET<br>NSR05XXMW2T1, SOD323 | NTHD3101FT1G, ChipFET<br>NTLJF3117P, WDFN2X2              | NSS12500UW3T2G, WDFN3<br>NSS20600CF8T1G, ChipFET   | NTLJD3115P, WDFN2X2<br>NTHD4102P, ChipFET<br>NTGD4161P, TS OP-6 |

Figure 2. Four different pass element topologies.

allowing the different elements to spread the heat evenly across the PCB (Topology A). The alternative is to use a single package device with the design focused around the package thermal resistance. New product portfolios of both BJTs and MOSFETs in the WDFN 2×2-mm package featuring exposed pad on the underside, dramatically decreasing thermal resistance. Rthja for the WDFN 2×2 package is 92°C/W compared to older packages such as the SC88 or TSOP6 with Rthja at 410°C/W and 130°C/ W, respectively.

**Multiple functions** of the pass element are becoming increasingly more important as the portable product designer adds more features. Topology D allows the pass element to be used as a switch to pass current back from the charged battery to another device or circuit. This configuration is often used for removable battery packs in laptop computers, where the same battery pack connector is used to charge the battery and power the laptop. Moreover, in cell phones, the battery can be used to drive external speakers, an MP3 player, Bluetooth headsets, and so on.

**PCB footprint, package height, and drive circuit configuration** play a major role as the designer tries to accommodate the ever-increasing challenge to fit more into less space. The fewer devices to be placed on the PCB and the smaller the components are, the small the final product will be. WDFN or UDFN packages feature a very thin profile (0.75 mm and 0.55 mm, respectively), small footprint (2×2 mm), and increased performance, representing the best solution for today

**ESD tolerance** is becoming more critical as portable products become smaller. The proximity of ESD charges close to or on connectors is becoming more prominent. Due to the structure of a BJT (HB >8,000 V), it is dramatically more ESD tolerant than a MOSFET (HB >300 V) and the need for external ESD protection is often eliminated, reducing component count. MOSFETs with integrated protection are now available to help in this respect.

**Switching efficiency** is important for circuits in which the losses caused by the switching time of the pass element would adversely affect the battery life. Switching charging circuits are being introduced that provide less power loss for a given area than the standard linear regulator. Topologies A, B, and D would all be suitable for this with the designer concentrating on the switching time (above 500 kHz) of the MOSFET for the selection.

**Price** is always a challenge. The older and larger packages tend to be the least expensive; for example, the SOT23 (3×3 mm) is one of the least expensive packages in the industry. Moving to smaller packages such as the ChipFET (3×2 mm) or modern WDFN (2×2 mm) packages provide smaller size and lower thermal resistance, but will have a higher price. Using older packages will tend to be the most cost-effective solution.

## Conclusion

The pressure for shorter and shorter periods between new product introductions has increased the pressure on the design engineer to reuse the charging circuit from a previous design. The manufacturers who employ this solution are leaving themselves open to their competition who are evaluating current technology and applying these new solutions to gain a significant performance advantage. The demand for smaller, thinner, faster, cooler, and more reliable products quickly changes the requirements in packaging and technology.

**Steve Sheard** *is marketing engineer and* **Tom Zemites** *is product marketing manager at ON Semiconductor (www.onsemi.com).*