# Audio Processor for AfterMaster HD

#### Introduction

BelaSigna<sup>®</sup> 300 AM is a DSP-based audio processor which is able to execute the AfterMaster HD algorithm within a system that also includes a host processor and/or external 12S- based mono or stereo A/D converters and D/A converters.

AfterMaster HD is an algorithm which processes audio signals in real-time to provide a significant increase in loudness, clarity, depth, and fullness.

BelaSigna 300 AM is specifically designed for use in applications requiring a solution to overcome the limitations of small or downward–facing speakers, including flat–screen televisions or headphones.

This datasheet describes only the specific information required to integrate BelaSigna 300 AM into an audio system.

For a more general description of the programmable BelaSigna 300 device from ON Semiconductor, please refer to the BelaSigna 300 datasheet.

#### **Key Features**

- Ultra-low-power: typically 4–8 mA when executing AfterMaster HD

- **Miniature Form Factor:** available in a miniature 3.63 mm x 2.68 mm x 0.92 mm (including solder balls) WLCSP package.

- Full Range of Configurable Interfaces: including a fast I<sup>2</sup>C-based interface for download and general configuration of the AfterMaster HD algorithm, a highly configurable PCM interface to stream data into and out of the device, a high-speed UART, an SPI port and 5 GPIOs

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

1

## ON Semiconductor®

www.onsemi.com

WLCSP-35 W SUFFIX CASE 567AG

#### MARKING DIAGRAM

BELASIGNA300 35-02-G XXXXYZZ

BELASIGNA300 = Device Code

35 = Number of Balls

02 = Revision of Die

G = Pb-Free

XXXX = Date Code

= Assembly Plant Identifier(May be Two Characters)

ZZ = Traceability Code

#### **ORDERING INFORMATION**

| Device         | Package            | Shipping <sup>†</sup> |

|----------------|--------------------|-----------------------|

| B300W35A109A1G | WLCSP<br>(Pb-Free) | 2500 / Tape &<br>Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## **Figures and Data**

**Table 1. ABSOLUTE MAXIMUM RATINGS**

| Parameter                                                | Min  | Max | Unit |

|----------------------------------------------------------|------|-----|------|

| Voltage at any input pin                                 | -0.3 | 2.0 | V    |

| Operating supply voltage (Note 1)                        | 0.9  | 2.0 | V    |

| Operating temperature range (Note 2)                     | -40  | 85  | °C   |

| Storage temperature range                                | -55  | 85  | °C   |

| Caution: Class 2 ESD Sensitivity, JESD22–A114–B (2000 V) |      |     |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Functional operation only guaranteed below 0°C for digital core (VDDC) and system voltages above 1.0 V.

- 2. Parameters may exceed listed tolerances when out of the temperature range 0 to 50°C.

#### **Electrical Performance Specifications**

The tests were performed at 20°C with a clean 1.8 V supply voltage. BelaSigna 300 AM was running in high voltage mode (VDDC = 1.8 V unless otherwise noted). The system clock (SYS\_CLK) was generated externally at 38 MHz.

Parameters marked as screened are tested on each chip. Other parameters are qualified but not tested on every part.

**Table 2. ELECTRICAL SPECIFICATIONS**

| Description                      | Symbol               | Conditions                       | Min  | Тур  | Max  | Units | Screened  |

|----------------------------------|----------------------|----------------------------------|------|------|------|-------|-----------|

| OVERALL                          |                      |                                  |      | •    |      | •     |           |

| Supply voltage                   | $V_{BAT}$            |                                  | 1.8  |      | 2.0  | V     | V         |

| Current consumption              | I <sub>BAT</sub>     | AfterMaster HD @ Fs= 48 kHz      | _    | 8    | _    | mA    | V         |

|                                  |                      | Fs = 44.1 kHz                    | _    | 7    | _    | mA    | V         |

|                                  |                      | Fs =16 kHz                       | -    | 3    | -    | mA    | V         |

|                                  |                      | Fs = 8 kHz                       | -    | 2    | -    | mA    |           |

| VREG (1 μF External Capacit      | tor) Measuremen      | t at VDDC = 1.0 V, Low voltage r | node |      |      |       |           |

| Regulated voltage output         | $V_{REG}$            |                                  | 0.95 | 1.00 | 1.05 | V     | V         |

| Regulator PSRR                   | $V_{REG\_PSRR}$      | 1 kHz                            | 50   | 55   | -    | dB    |           |

| Load current                     | I <sub>LOAD</sub>    |                                  | -    | _    | 2    | mA    |           |

| Load regulation                  | LOAD <sub>REG</sub>  |                                  | _    | 6.1  | 6.5  | mV/mA | V         |

| Line regulation                  | LINE <sub>REG</sub>  |                                  | _    | 2    | 5    | mV/V  |           |

| VDBL (1 μF External Capacit      | or) Measuremen       | t at VDDC = 1.0 V, Low voltage r | node |      |      |       |           |

| Regulated doubled voltage output | VDBL                 |                                  | 1.9  | 2.0  | 2.1  | V     | V         |

| Regulator PSRR                   | VDBL <sub>PSRR</sub> | 1 kHz                            | 35   | 41   | -    | dB    |           |

| Load current                     | I <sub>LOAD</sub>    |                                  | _    | -    | 2.5  | mA    |           |

| Load regulation                  | LOAD <sub>REG</sub>  |                                  | -    | 7    | 10   | mV/mA | V         |

| Line regulation                  | LINE <sub>REG</sub>  |                                  | -    | 10   | 20   | mV/V  |           |

| VDDC (1 μF External Capacit      | tor) Measuremen      | t at VDDC = 1.0 V, Low voltage r | node |      |      |       |           |

| Digital supply voltage output    | VDDC                 | Configured by a control register | 0.79 | 0.95 | 1.25 | V     | $\sqrt{}$ |

| VDDC output level adjustment     | VDDC <sub>STEP</sub> |                                  | 27   | 29   | 31   | mV    |           |

| Regulator PSRR                   | VDDC <sub>PSRR</sub> | 1 kHz                            | 25   | 25.5 | 26   | dB    |           |

| Load current                     | I <sub>LOAD</sub>    |                                  | _    | -    | 3.5  | mA    |           |

| Load regulation                  | LOAD <sub>REG</sub>  |                                  | _    | 3    | 12   | mV/mA | √         |

| Line regulation                  | LINE <sub>REG</sub>  |                                  | -    | 3    | 8    | mV/V  |           |

Table 2. ELECTRICAL SPECIFICATIONS (continued)

| Description                                 | Symbol                    | Conditions                      | Min           | Тур   | Max           | Units | Screened |

|---------------------------------------------|---------------------------|---------------------------------|---------------|-------|---------------|-------|----------|

| POWER-ON-RESET (POR)                        | •                         |                                 |               |       |               | •     |          |

| POR startup voltage                         | VDDC <sub>STARTUP</sub>   |                                 | 0.775         | 0.803 | 0.837         | V     |          |

| POR shutdown voltage                        | VDDC <sub>SHUTDOWN</sub>  |                                 | 0.755         | 0.784 | 0.821         | V     |          |

| POR hysteresis                              | POR <sub>HYSTERESIS</sub> |                                 | 13.8          | 19.1  | 22.0          | mV    |          |

| POR duration                                | T <sub>POR</sub>          |                                 | 11.0          | 11.6  | 12.3          | ms    |          |

| DIGITAL PADS                                |                           |                                 |               |       |               |       |          |

| Voltage level for high input                | V <sub>IH</sub>           |                                 | VBAT<br>* 0.8 | -     | -             | V     | √        |

| Voltage level for low input                 | V <sub>IL</sub>           |                                 | _             | -     | VBAT<br>* 0.2 | V     | √        |

| Voltage level for high output               | V <sub>OH</sub>           | 2 mA source current             | VDDO<br>* 0.8 | -     | -             | V     | √        |

| Voltage level for low output                | V <sub>OL</sub>           | 2 mA sink current               | _             | -     | VDDO<br>* 0.2 | V     | √        |

| Input capacitance for digital pads          | C <sub>IN</sub>           |                                 | -             | 4     | -             | pF    |          |

| Pull-up resistance for digital input pads   | R <sub>UP_IN</sub>        |                                 | 220           | 270   | 320           | kΩ    | √        |

| Pull-down resistance for digital input pads | R <sub>DOWN_IN</sub>      |                                 | 220           | 270   | 320           | kΩ    | √        |

| Sample rate tolerance                       | FS                        | Sample rate of 16 kHz or 32 kHz | -1            | ±0    | +1            | %     |          |

| Rise and fall time                          | Tr, Tf                    | Digital output pad              |               |       |               |       |          |

| ESD                                         |                           | Human Body Model (HBM)          |               |       | 2             | kV    |          |

|                                             |                           | Machine Model (MM)              |               |       | 200           | V     |          |

| Latch-up                                    |                           | V < GNDC, V > VBAT              |               |       | 200           | mA    |          |

| DIGITAL INTERFACES                          |                           |                                 |               |       |               |       |          |

| I2C baud rate                               |                           | System clock < 1.6 MHz          | _             | _     | 100           | kbps  |          |

|                                             |                           | System clock > 1.6 MHz          | -             | -     | 400           | kbps  |          |

| General-purpose UART baud rate              |                           | System clock ≥ 5.12 MHz         | _             | 1     | -             | Mbps  |          |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **Environmental Characteristics**

All BelaSigna 300 AM packages are Pb-free, RoHS-compliant and Green.

BelaSigna 300 AM parts are qualified against standards outlined in the following sections.

All BelaSigna 300 AM package options are Green (RoHS-compliant). Contact ON Semiconductor for supporting documentation.

#### **WLCSP Package Option**

The solder ball composition for the WLCSP package is SAC266.

**Table 3. WLCSP PACKAGE-LEVEL QUALIFICATION**

| Packaging Level                       |                               |

|---------------------------------------|-------------------------------|

| Moisture sensitivity level            | JEDEC Level 1                 |

| Thermal cycling test (TCT)            | –55°C to 150°C for 500 cycles |

| Highly accelerated stress test (HAST) | 85°C / 85% RH for 1000 hours  |

| High temperature stress test (HTST)   | 150°C for 1000 hours          |

## **Table 4. WLCSP BOARD-LEVEL QUALIFICATION**

| Board Level |                                                 |

|-------------|-------------------------------------------------|

| Temperature | -40°C to 125°C for 2500 cycles with no failures |

## **Mechanical Information and Circuit Design Guidelines**

BelaSigna 300 AM is available in a 2.68 x 3.63 mm ultra-miniature wafer-level chip scale package (WLCSP)

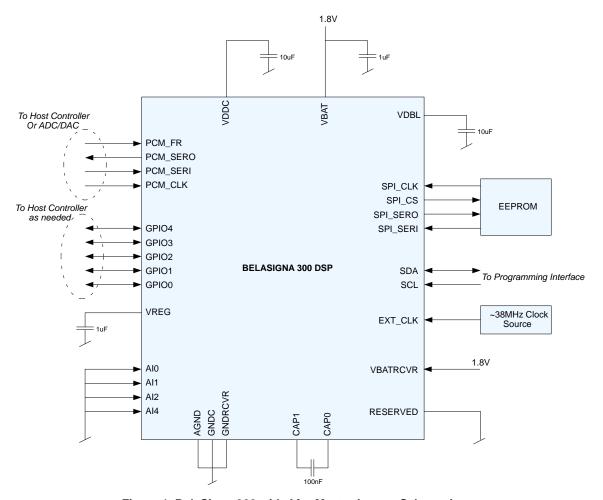

Figure 1. BelaSigna 300 with AfterMaster Layout Schematic

## **WLCSP Pin Out**

A total of 35 active pins are present on the BelaSigna 300 AM WLCSP package. They are organized in a staggered array. A description of these pins is given in Table 5.

# **Table 5. WLCSP PAD DESCRIPTIONS**

| Pad Index | BelaSigna 300 AM Pad Name | Description                                                             | I/O | A/D |

|-----------|---------------------------|-------------------------------------------------------------------------|-----|-----|

| A1        | GNDRCVR                   | Ground for output driver                                                | N/A | Α   |

| A5        | VBATRCVR                  | Power supply for output stage / NC for AfterMaster                      | ı   | Α   |

| B2        | RCVR_HP+                  | Extra output driver pad for high power mode / NC for AfterMaster*       | 0   | Α   |

| C3        | RCVR+                     | Output from output driver / NC for AfterMaster*                         | 0   | Α   |

| A3        | RCVR-                     | Output from output driver / NC for AfterMaster*                         | 0   | Α   |

| B4        | RCVR_HP-                  | Extra output driver pad for high power mode / NC for AfterMaster*       | 0   | Α   |

| B6        | CAP0                      | Charge pump capacitor pin 0                                             | N/A | Α   |

| C5        | CAP1                      | Charge pump capacitor pin 1                                             | N/A | Α   |

| A7        | VDBL                      | Doubled voltage                                                         | 0   | Α   |

| B8        | VBAT                      | Power supply                                                            | ı   | Α   |

| B10       | VREG                      | Regulated supply voltage / NC for AfterMaster*                          | 0   | Α   |

| A9        | AGND                      | Analog ground                                                           | N/A | Α   |

| A11       | Al4                       | Audio signal input 4 / NC for AfterMaster*                              | ı   | Α   |

| B12       | Al2/LOUT2                 | Audio signal input 2/output signal from preamp 2 / GND for AfterMaster* | I/O | Α   |

| A13       | AI1/LOUT1                 | Audio signal input 1/output signal from preamp 1 / GND for AfterMaster* | I/O | Α   |

| B14       | AI0/LOUT0                 | Audio signal input 0/output signal from preamp 0 / GND for AfterMaster* | I/O | Α   |

| D14       | GPIO[4]/LSAD[4]           | General-purpose I/O 4/low speed AD input 4                              | I/O | A/D |

| E13       | GPIO[3]/LSAD[3]           | General-purpose I/O 3/low speed AD input 3                              | I/O | A/D |

| C13       | GPIO[2]/LSAD[2]           | General-purpose I/O 2/low speed AD input 2                              | I/O | A/D |

| D12       | GPIO[1]/LSAD[1]/UART-RX   | General-purpose I/O 1/low speed AD input 1/and UART RX                  | I/O | A/D |

| E11       | GPIO[0]/UART-TX           | General-purpose I/O 0/UART TX                                           | I/O | A/D |

| C9        | GNDC                      | Digital ground                                                          | N/A | Α   |

| C11       | SDA (I2C)                 | I2C data                                                                | I/O | D   |

| D10       | SCL (I2C)                 | I2C clock                                                               | I/O | D   |

| E9        | EXT_CLK                   | External clock input/internal clock output                              | I/O | D   |

| D8        | VDDC                      | Core logic power                                                        | 0   | Α   |

| E7        | SPI_CLK                   | Serial peripheral interface clock                                       | 0   | D   |

| C7        | SPI_SERI                  | Serial peripheral interface input                                       | ı   | D   |

| D6        | SPI_CS                    | Serial peripheral interface chip select                                 | 0   | D   |

| E5        | SPI_SERO                  | Serial peripheral interface output                                      | 0   | D   |

| D4        | PCM_FR                    | PCM interface frame                                                     | I/O | D   |

| E3        | PCM_SERI                  | PCM interface input                                                     | I   | D   |

| D2        | PCM_SERO                  | PCM interface output                                                    | 0   | D   |

| C1        | PCM_CLK                   | PCM interface clock                                                     | I/O | D   |

|           |                           |                                                                         |     |     |

<sup>\*</sup>NC = Not Connected.

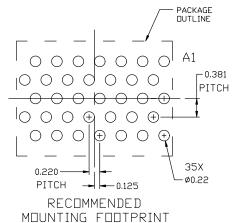

#### **WLCSP Assembly / Design Notes**

For PCB manufacture with BelaSigna 300 AM WLCSP, ON Semiconductor recommends solder—on—pad (SoP) surface finish. With SoP, the solder mask opening should be non—solder mask—defined (NSMD) and copper pad geometry will be dictated by the PCB vendor's design requirements.

Alternative surface finishes are ENiG and OSP; volume of screened solder paste (#5) should be less than 0.0008 mm<sup>3</sup>. If no pre–screening of solder paste is used, then following conditions must be met:

- 1. the solder mask opening should be >0.3 mm in diameter,

- 2. the copper pad will have 0.25 mm diameter, and

- 3. soldermask thickness should be less than 1 mil thick above the copper surface.

ON Semiconductor can provide BelaSigna 300 AM WLCSP land pattern CAD files to assist your PCB design upon request.

## **WLCSP Weight**

BelaSigna 300 AM WLCSP (B300W35A109XXG) has an average weight of 0.095 grams.

### **Digital Interfaces**

## General-Purpose Input Output (GPIO) Ports

BelaSigna 300 AM has five GPIO ports that can connect to external digital inputs such as push buttons, or digital outputs such as the control or trigger of an external companion chip (GPIO[0..4]). The direction of these ports (input or output) is configurable and each pin has an internal pull–up resistor when configured as a GPIO. A read from an unconnected pin will give a value of logic 1. Four of the five GPIO pins are multiplexed with an LSAD (see the Low–Speed A.D Converters section) and as such the functionality of the pin

can be either a GPIO or an LSAD depending on the configuration. Note that GPIO0 cannot be used as an LSAD.

## Inter-IC Communication (I<sup>2</sup>C) Interfaces

The I<sup>2</sup>C interface is an industry–standard interface that can be used for high–speed transmission of data between BelaSigna 300 AM and an external device. The interface operates at speeds up to 400 Kbit/sec for system clocks (EXT\_CLK) higher than 1.6 MHz. In product development mode, the I<sup>2</sup>C interface is used for application debugging purposes, communicating with the BelaSigna 300 AM development tools. The interface can be configured to operate in either master mode or slave mode.

#### Serial Peripheral Interface (SPI) Port

An SPI port is available on BelaSigna 300 AM for applications such as communication with a non-volatile memory (EEPROM). The I/O levels on this port are defined by the VBAT. The SPI port operates in master mode only, which supports communications with slave SPI devices.

The SPI port on BelaSigna 300 AM only supports master mode, so it will only communicate with SPI slave devices. When connecting to an SPI slave device other than a boot EEPROM, the SPI\_CS pin should be left unconnected and the slave device CS line should be driven from a GPIO to avoid BelaSigna 300 AM boot malfunction. When connecting to an SPI EEPROM for boot, the designer can choose to connect the SPI\_CS pin to the EEPROM or use a GPIO (high at boot) for a design with several daisy-chained SPI devices.

#### **PCM** Interface

BelaSigna 300 AM includes a highly configurable pulse code modulation (PCM) interface that can be used to stream audio signal data into and out of the device. The I/O levels on this port are defined by the voltage on the VBAT pin.

#### **Assembly Information**

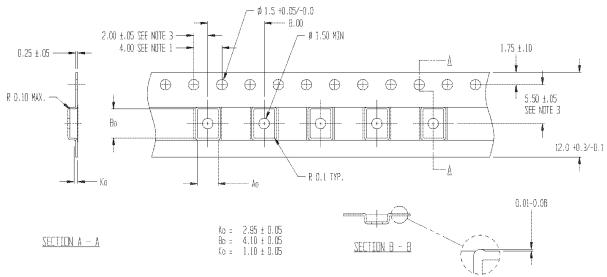

## CARRIER DETAILS 2.6 x 3.8 mm WLCSP

ON Semiconductor offers tape and reel packing for BelaSigna 300 AM WLCSP. The packing consists of a pocketed carrier tape, a cover tape, and a molded anti–static polystyrene reel. The carrier and cover tape create an ESD safe environment, protecting the components from physical and electrostatic damage during shipping and handling.

Quantity per Reel: 2500 units

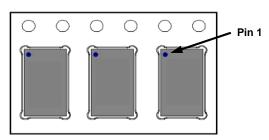

Pin 1 Orientation: Upper Left, Bumps down Tape Brand / Width: Advantek / 12 mm

Pocket Pitch: 8 mm P/N: BCB043

Cover Tape: 3M 2666 PSA 9.3 mm

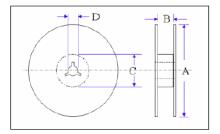

A = 13 inches B = 12 mm C = 4 inches D = 13 mm

Reel Brand / Width: Advantek Lokreel® / 13 in

Figure 2. Package Orientation on Tape for WLCSP Package Option

10 sprockets hole pitch cumulative tolerance  $\pm 0.1$ .

Camber in compliance with EIA 763.

Pocket position relative to sprocket hole measured as true position of pocket, not pocket hole.

Figure 3. WLCSP Carrier Tape Drawing

#### Sample Shipping Label

Figure 4. Sample Shipping Label

#### Re-Flow Information

The re-flow profile depends on the equipment that is used for the re-flow and the assembly that is being re-flowed. Information from JEDEC Standard 22-A113D and J-STD-020D.01 can be used as a guideline.

#### Electrostatic Discharge (ESD) Sensitive Device

**CAUTION:** ESD sensitive device. Permanent damage may occur on devices subjected to high–energy electrostatic discharges. Proper ESD precautions in handling, packaging and testing are recommended to avoid performance degradation or loss of functionality. Device is 2 kV HBM ESD qualified.

#### **Miscellaneous**

#### **Ordering Information**

To order BelaSigna 300 with AM, please contact your account manager and ask for part number B300W35A109A1G.

#### **Chip Identification**

Chip identification information can be retrieved by using the Communications Accelerator Adaptor (CAA) tool along with the protocol software provided by ON Semiconductor (see CAA instruction manual). For BelaSigna 300 AM, the key identifier components and values are as follows for the different package options:

| Package | Chip   | Chip    | Chip     |

|---------|--------|---------|----------|

| Option  | Family | Version | Revision |

| WLCSP   | 0x03   | 0x02    |          |

## **Support Software**

A set of tools is available at <a href="http://onsemi.com">http://onsemi.com</a> for downloading the proprietary AfterMaster HD algorithm to BelaSigna 300 AM. An AfterMaster HD image is supplied by ON Semiconductor, but must be downloaded to BelaSigna 300 AM upon boot.

#### **Training**

To facilitate development on the BelaSigna 300 AM platform, training is available upon request. Contact your account manager for more information.

#### **Company or Product Inquiries**

For more information about ON Semiconductor products or services visit our Web site at <a href="http://onsemi.com">http://onsemi.com</a>.

**DATE 20 OCT 2022**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. COPLANARITY APPLIES TO THE SPHERICAL CROWNS OF THE SOLDER BALLS.

|     | MILLIMETERS |       |       |  |

|-----|-------------|-------|-------|--|

| DIM | MIN.        | N□M.  | MAX.  |  |

| Α   | 0.832       | 0.882 | 0.932 |  |

| A1  | 0.182       | 0.207 | 0.232 |  |

| A2  | 0.650       | 0.675 | 0.700 |  |

| b   | 0.244       | 0.269 | 0.294 |  |

| С   | 0.125 BSC   |       |       |  |

| D   | 3.633 BSC   |       |       |  |

| E   | 2.680 BSC   |       |       |  |

| еD  | 0.250 BSC   |       |       |  |

| eЕ  | 0.433 BSC   |       |       |  |

\* For additional information on our Pb-free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SDLDERRM/D.

|                            |                                        | ISSUE C                            |

|----------------------------|----------------------------------------|------------------------------------|

| B                          |                                        | PIN A1<br>REFERENCE                |

| 2X 0.10 C 2X 0.10 C        | TOP VIEW                               |                                    |

| 0.10 C  0.05 C  NOTE 3  A1 | SIDE VIEW                              | A2<br>A<br>A<br>SEATING<br>C PLANE |

| E<br>D<br>C -<br>B<br>A    |                                        | 0.05 C A B 0.03 C                  |

|                            | <br>1413121110987654321<br>BOTTOM VIEW |                                    |

| DOCUMENT NUMBER: | 98AON31202E        | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | WLCSP35, 3.63X2.68 |                                                                                                                                                                                 | PAGE 1 OF 1 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves brisefin and of 160 m are trademarked so defined values of services and of the confined values and of the values of the confined values and of the values of the confined values and of the values of the v special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales