データシート No.N7109 をさしかえてください。

# LB11826

http://onsemi.jp

## モノリシックデジタル集積回路 OA用3相プラシレス モータドライバ

## 概要

LB11826は、3相ブラシレスモータドライバであり、LBP,PPC等のドラムモータ,紙送りモータ等の駆動に最適である。ダイレクトPWM駆動により、パワーロスの少ない駆動が可能である。LB11825Mと組み合わせることにより、外部から入力するクロック周波数(FG周波数相当)に応じた任意のモータ回転数制御を実現できる。

#### 特長

- ・3相バイポーラ駆動(30V,2.5A)。

- ・ダイレクトPWM駆動。

- ・出力下側キックバック吸収用ダイオード内蔵。

- ・速度ディスクリ + PLL速度制御方式。

- ・速度ロック検知出力。

- ・正逆転切替え回路内蔵。

- ・電流制限回路,過熱保護回路,モータ拘束保護回路等の各種保護回路内蔵。

#### 絶対最大定格/Ta=25

| かし カナスノ くんこ 1日 / 1 は一とし |                     |          |              |      |

|-------------------------|---------------------|----------|--------------|------|

| 項目                      | 記号                  | 条件       | 定格値          | unit |

| 最大電源電圧                  | V <sub>CC</sub> max |          | 30           | ٧    |

| 最大出力電流                  | Io max              | T 500ms  | 2.5          | Α    |

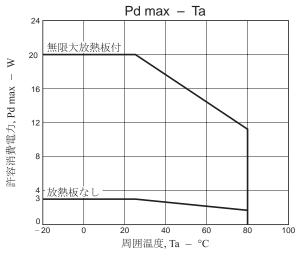

| 許容消費電力                  | Pd max1             | IC単体     | 3            | W    |

|                         | Pd max2             | 無限大放熱板付き | 20           | W    |

| 動作周囲温度                  | Topr                |          | - 20 ~ + 80  |      |

| 保存周囲温度                  | Tstg                |          | - 55 ~ + 150 |      |

最大定格を超えるストレスは、デパイスにダメージを与える危険性があります。最大定格は、ストレス印加に対してのみであり、推奨動作条件を超えての機能 的動作に関して意図するものではありません。推奨動作条件を超えてのストレス印加は、デパイスの信頼性に影響を与える危険性があります。

## 許容動作範囲/Ta=25

| 項目      | 記号   | 条件 | 定格値    | unit |

|---------|------|----|--------|------|

| 最大電圧範囲1 | VCC  |    | 9.5~28 | V    |

| 定電圧出力電流 | IREG |    | 0~-30  | mA   |

| LD出力電流  | ILD  |    | 0 ~ 15 | mA   |

## LB11826

## 電気的特性/Ta=25 ,VCC=VM=24V

| 項目          | 記号                    | 条                                      | 件        | min      | typ      | max      | unit  |

|-------------|-----------------------|----------------------------------------|----------|----------|----------|----------|-------|

| 電源電流1       | I <sub>CC</sub> 1     |                                        |          |          | 23       | 30       | mA    |

| 電源電流2       | I <sub>CC</sub> 2     | ストップ時                                  |          |          | 3.5      | 5        | mA    |

| 出力部         |                       |                                        |          |          |          |          |       |

| 出力飽和電圧1     | V <sub>0</sub> sat1   | I <sub>0</sub> =1.0A,                  |          |          | 2.0      | 2.5      | V     |

|             |                       | V <sub>0</sub> (SINK) + V <sub>0</sub> | (SOURCE) |          |          |          |       |

| 出力飽和電圧2     | V <sub>0</sub> sat2   | I <sub>0</sub> =2.0A,                  |          |          | 2.6      | 3.2      | V     |

|             | I. II.                | V <sub>O</sub> (SINK) + V <sub>O</sub> | (SOURCE) |          |          | 400      | Δ.    |

| 出力リーク電流     | In leak               | ID= - 1.0A                             |          |          | 4.0      | 100      | μA    |

| 下側ダイオード順電圧1 | VD1                   | ID= - 1.0A                             |          |          | 1.2      | 1.5      | V     |

| 下側ダイオード順電圧2 | VD2                   | 10= - 2.0A                             |          |          | 1.5      | 2.0      | V     |

| 5V定電圧出力     | VDEO                  | I 5A                                   |          | 4.05     | 5.00     | 5.05     |       |

| 出力電圧        | VREG                  | I <sub>O</sub> = - 5mA                 | ,        | 4.65     | 5.00     | 5.35     | V     |

| 電圧変動        | ΔVREG1                | V <sub>CC</sub> =9.5 ~ 28\             |          |          | 30       | 100      | mV    |

| 負荷変動        | ∆VREG2                | I <sub>0</sub> = - 5 ~ - 20            | )mA      |          | 20       | 100      | mV    |

| ホールアンプ      |                       | 1                                      |          | T _      |          | T        | l .   |

| 入力バイアス電流    | IHB                   |                                        |          | - 2      | - 0.5    |          | μА    |

| 同相入力電圧範囲    | VICM                  |                                        |          | 1.5      |          | VREG-1.5 | V     |

| ホール入力感度     |                       |                                        |          | 80       |          |          | mVp-p |

| ヒステリシス幅     | ΔVIN                  |                                        |          | 15       | 24       | 42       | mV    |

| 入力電圧L H     | VSLH                  |                                        |          |          | 12       |          | mV    |

| 入力電圧H L     | VSHL                  |                                        |          |          | - 12     |          | mV    |

| PWM発振回路     |                       | 1                                      |          | 1        |          | ı        | 1     |

| 出力「H」レベル電圧  | V <sub>OH</sub> (PWM) |                                        |          | 2.5      | 2.8      | 3.1      | V     |

| 出力「」レベル電圧   | VOL(PWM)              |                                        |          | 1.2      | 1.5      | 1.8      | V     |

| 発振周波数       | f(PWM)                | C=3900pF                               |          |          | 18       |          | kHz   |

| 振幅          | V(PWM)                |                                        |          | 1.05     | 1.30     | 1.55     | Vp-p  |

| CSD回路       |                       |                                        |          |          |          |          |       |

| 動作電圧        | V <sub>OH</sub> (CSD) |                                        |          | 3.6      | 3.9      | 4.2      | V     |

| 外付けC充電電流    | ICHG                  |                                        |          | - 17     | - 12     | - 9      | μΑ    |

| 動作時間        | T(CSD)                | C=10µF,設計                              | 目標値      |          | 3.3      |          | S     |

| 電流制限動作      |                       |                                        |          |          |          |          |       |

| リミッタ電圧      | VRF                   | VCC-VM                                 |          | 0.45     | 0.5      | 0.55     | V     |

| 熱しゃ断動作      |                       |                                        |          |          |          |          |       |

| 熱しゃ断動作温度    | TSD                   | 設計目標値                                  | (接合温度)   | 150      | 180      |          |       |

| ヒステリシス幅     | ΔTSD                  | 設計目標値                                  | (接合温度)   |          | 50       |          |       |

| FGアンプ       |                       |                                        |          |          |          |          |       |

| 入力オフセット電圧   | V <sub>IO</sub> (FG)  |                                        |          | - 10     |          | 10       | mV    |

| 入力バイアス電流    | IB(FG)                |                                        |          | - 1      |          | 1        | μА    |

| 出力川レベル電圧    | V <sub>OH</sub> (FG)  | IFGO= - 0.2mA                          | ١        | VREG-1.2 | VREG-0.8 |          | V     |

| 出力「L」レベル電圧  | V <sub>OL</sub> (FG)  | IFGO=0.2mA                             |          |          | 0.8      | 1.2      | V     |

| FG入力感度      |                       | GAIN 100倍                              |          | 3        |          |          | mV    |

| 次段のシュミット幅   |                       | 設計目標値                                  |          | 100      | 180      | 250      | mV    |

設計目標値であり、測定は行なわない。

## LB11826

前ページより続く。

| 削ハーンより続く。    |                       |                   |          |          | 1        |      |  |

|--------------|-----------------------|-------------------|----------|----------|----------|------|--|

| 項目           | 記号                    | 条件                | min      | typ      | max      | unit |  |

| 動作周波数範囲      |                       |                   |          |          | 2        | kHz  |  |

| オープンループGAIN  |                       | f (FG)=2kHz       | 45       | 51       |          | dB   |  |

| 速度ディスクリ      |                       |                   |          |          |          |      |  |

| 出力川レベル電圧     | V <sub>OH</sub> (D)   | IDO= - 0.1mA      | VREG-1.0 | VREG-0.7 |          | V    |  |

| 出力「」レベル電圧    | V <sub>OL</sub> (D)   | IDO=0.1mA         |          | 0.8      | 1.1      | V    |  |

| カウント数        |                       |                   |          | 512      |          |      |  |

| PLL出力        |                       |                   |          |          |          |      |  |

| 出力川レベル電圧     | V <sub>OH</sub> (P)   | IPO= - 0.1mA      | VREG-1.8 | VREG-1.5 | VREG-1.2 | ٧    |  |

| 出力「」レベル電圧    | V <sub>OL</sub> (P)   | IPO=0.1mA         | 1.2      | 1.5      | 1.8      | ٧    |  |

| ロック検出        |                       |                   |          |          |          |      |  |

| 出力「」レベル電圧    | V <sub>OL</sub> (LD)  | ILD=10mA          |          | 0.15     | 0.5      | ٧    |  |

| ロック範囲        |                       |                   |          | 6.25     |          | %    |  |

| 積分器          |                       |                   |          |          |          |      |  |

| 入力バイアス電流     | IB(INT)               |                   | - 0.4    |          | 0.4      | μΑ   |  |

| 出力トリレベル電圧    | V <sub>OH</sub> (INT) | IINTO= - 0.2mA    | VREG-1.2 | VREG-0.8 |          | ٧    |  |

| 出力「」レベル電圧    | V <sub>OL</sub> (INT) | IINTO=0.2mA       |          | 0.8      | 1.2      | V    |  |

| オープンループGAIN  |                       | f(INT)=1kHz       | 45       | 51       |          | dB   |  |

| 利得帯域幅積       |                       | 設計目標値             |          | 450      |          | kHz  |  |

| 基準電圧         |                       | 設計目標値             | - 5%     | VREG/2   | 5%       | V    |  |

| クロック入力端子     |                       |                   |          |          |          |      |  |

| 動作周波数範囲      | fosc                  |                   |          |          | 1        | MHz  |  |

| 「L」レベル端子電圧   | Voscl                 | IOSC= - 0.5mA     |          | 1.55     |          | ٧    |  |

| 「H」レベル端子電流   | IOSCH                 | Vosc=VoscL + 0.5V |          | 0.4      |          | mA   |  |

| スタート/ストップ端子  |                       |                   |          |          |          |      |  |

| 「H」レベル入力電圧範囲 | V <sub>IH</sub> (S/S) |                   | 3.5      |          | VREG     | ٧    |  |

| 「L」レベル入力電圧範囲 | V <sub>IL</sub> (S/S) |                   | 0        |          | 1.5      | ٧    |  |

| 入力オープン電圧     | V <sub>10</sub> (S/S) |                   | VREG-0.5 |          | VREG     | ٧    |  |

| ヒステリシス幅      | ΔVΙΝ                  |                   | 0.35     | 0.50     | 0.65     | V    |  |

| 「H」レベル入力電流   | I <sub>IH</sub> (S/S) | V(S/S)=VREG       | - 10     | 0        | 10       | μΑ   |  |

| 「L」レベル入力電流   | I <sub>IL</sub> (S/S) | V(S/S)=0V         | - 280    | - 210    |          | μΑ   |  |

| 正逆転端子        |                       |                   |          |          |          |      |  |

| 「H」レベル入力電圧範囲 | V <sub>IH</sub> (F/R) |                   | 3.5      |          | VREG     | V    |  |

| 「L」レベル入力電圧範囲 | V <sub>IL</sub> (F/R) |                   | 0        |          | 1.5      | V    |  |

| 入力オープン電圧     | V <sub>10</sub> (F/R) |                   | VREG-0.5 |          | VREG     | V    |  |

| ヒステリシス幅      | Δ۷ΙΝ                  |                   | 0.35     | 0.50     | 0.65     | V    |  |

| 「H」レベル入力電流   | I <sub>IH</sub> (F/R) | V(F/R)=VREG       | - 10     | 0        | 10       | μΑ   |  |

| 「L」レベル入力電流   | I <sub>IL</sub> (F/R) | V(F/R)=0V         | - 280    | - 210    |          | μА   |  |

|              |                       | •                 | •        | i i      | ·        |      |  |

設計目標値であり、測定は行わない。

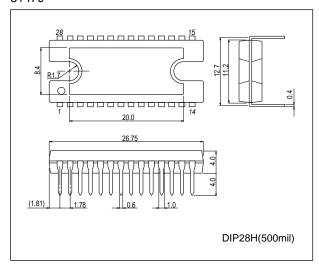

## 外形図

unit:mm (typ)

3147C

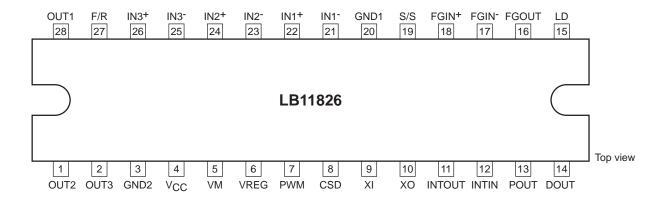

## ピン配置図

## 真理值表

|   | ソース       | F/R=「L」 |     |     |     | F/R=「H」 |     |

|---|-----------|---------|-----|-----|-----|---------|-----|

|   | シンク       | IN1     | IN2 | IN3 | IN1 | IN2     | IN3 |

| 1 | 0UT2→0UT1 | Н       | L   | Н   | L   | Н       | L   |

| 2 | 0UT3→0UT1 | Н       | L   | L   | L   | Н       | Н   |

| 3 | 0UT3→0UT2 | Н       | Н   | L   | L   | L       | Н   |

| 4 | 0UT1→0UT2 | L       | Н   | L   | Н   | L       | Н   |

| 5 | 0UT1→0UT3 | L       | Н   | Н   | Н   | L       | L   |

| 6 | 0UT2→0UT3 | L       | L   | Н   | Н   | Н       | L   |

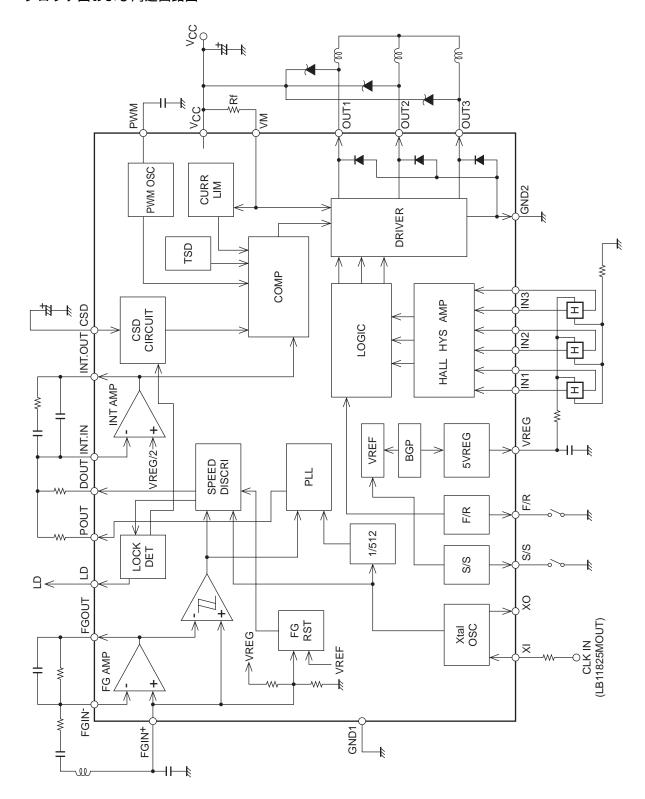

## ブロック図および周辺回路図

## 端子説明

| 端子討               | 说明                           |                                                                                           |                           |

|-------------------|------------------------------|-------------------------------------------------------------------------------------------|---------------------------|

| 端子<br>番号          | 端子名                          | 端子説明                                                                                      | 等価回路図                     |

| 28<br>1<br>2<br>3 | OUT1<br>OUT2<br>OUT3<br>GND2 | モータ駆動 出力端子。<br>出力 - V <sub>CC</sub> 間にショットキーダイオ<br>ードを接続する。<br>出力部のGND端子。                 | <u>Vcc</u> 300Ω VM 5      |

| 5                 | VM                           | 出力部の電源端子および出力電流検<br>出端子。<br>VCC間に低抵抗(Rf)を接続する。<br>IOUT=VRF/Rfで設定した電流値に出<br>力電流が制限される。     | 1 2 28                    |

| 4                 | VCC                          | 電源端子(出力部以外)。                                                                              |                           |

| 6                 | VREG                         | 安定化電源出力端子(5V出力)。<br>安定化のため、GND間にコンデンサ<br>を接続する(約0.1µF程度)。                                 | Vcc 6                     |

| 7                 | PWM                          | PWM発振周波数を設定する端子。<br>GND間にコンデンサを接続する。<br>C=3900pFで約18kHzに設定できる。                            | VREG 200Ω 7               |

| 8                 | CSD                          | 拘束保護回路の動作時間を設定する<br>端子。<br>CSD - GND間にコンデンサ(約10μF程<br>度)を付けることにより、約3.3秒の<br>保護動作時間を設定できる。 | VREG  300Ω  1kΩ  1kΩ  1kΩ |

次ページへ続く。

## 前ページより続く。

| 端子   | ジより続<br>端子名 | 端子説明                                                                                 | 等価回路図                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|-------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号   |             |                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9 10 | XI<br>XO    | クロック入力端子。<br>外部からクロック信号を(1MHz以下)<br>を抵抗(約5.1kΩ程度)を介してXI端<br>子に入力する。<br>XO端子はオープンとする。 | VREG  VREG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11   | INTOUT      | 積分アンプ出力端子(速度制御端子)。                                                                   | VREG  ONE OF THE PROPERTY OF T |

| 12   | INTIN       | 積分アンプ入力端子。                                                                           | VREG 300Ω 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13   | POUT        | PLL出力端子。                                                                             | VREG 300Ω 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

次ページへ続く。

## 前ページより続く。

|          | ジより続  | <.                                                                                       |                                                            |

|----------|-------|------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 端子<br>番号 | 端子名   | 端子説明                                                                                     | 等価回路図                                                      |

| 14       | DOUT  | 速度ディスクリ出力端子。<br>加速 "H",減速 "L"。                                                           | VREG  300Ω  14                                             |

| 15       | LD    | 速度ロック検知出力。<br>モータの回転数が速度ロック範囲内<br>(±6.25%)にある時、"L"となる。<br>耐圧30V max。                     | VREG (15)                                                  |

| 16       | FGOUT | FGアンプ出力端子。                                                                               | VREG (16) (16) (16) (17) (17) (17) (17) (17) (17) (17) (17 |

| 17<br>18 | FGIN+ | FGアンプ入力端子。 FGIN+とGND間にコンデンサ(約 0.1μF程度)を付けることにより、 ロジック回路部に初期リセットをかける。                     | VREG  20kΩ  FGリセット回路  18  300Ω  18  20kΩ  17)              |

| 19       | S/S   | スタート/ストップ制御端子。<br>「L」:0V ~ 1.5V<br>「H」:3.5V ~ VREG<br>オープン時、「H」レベルとなる。<br>ヒステリシス幅 約0.5V。 | VREG  \$22kΩ  2kΩ  2kΩ  19                                 |

#### 前ページより続く

| Hu.      | ンより約 | ι <b>`</b> ο          |                                       |

|----------|------|-----------------------|---------------------------------------|

| 端子<br>番号 | 端子名  | 端子説明                  | 等価回路図                                 |

| 20       | GND1 | GND端子(出力部以)。          |                                       |

| 22       | IN1+ | ホール入力端子。              | VREG                                  |

| 21       | IN1- | IN+>IN-で川、逆はLJとする。    |                                       |

| 24       | IN2+ | ホール信号は100mVp-p(差動)以上の | <b>1</b>                              |

| 23       | IN2- | 振幅が望ましい。ホール信号のノイ      | T — T                                 |

| 26       | IN3+ | ズが問題となる場合は、IN+,IN-間   | $(21)23(25)$ $300\Omega$ $(22)24(26)$ |

| 25       | IN3- | にコンデンサを接続する。          |                                       |

|          |      |                       | <b>★</b>                              |

|          |      |                       |                                       |

|          |      |                       | m m m                                 |

| 27       | F/R  | 正転/逆転 制御端子。           | VREG                                  |

|          |      | [L]:0V ~ 1.5V         |                                       |

|          |      | 「H」:3.5V ~ VREG       |                                       |

|          |      | オープン時、「H」レベルとなる。      |                                       |

|          |      | ヒステリシス幅 約0.5%。        | \$22kΩ                                |

|          |      |                       | 2kΩ                                   |

|          |      |                       | (27)                                  |

|          |      |                       |                                       |

|          |      |                       | ती ती ती ती                           |

#### LB11826の説明

#### 1.速度制御回路

本ICは、速度ディスクリ回路およびPLL回路の併用により速度制御を行っている。速度制御回路はFGの2周期に1回誤差信号を出力する(FGの1周期をカウント)。PLL回路はFGの1周期に1回位相誤差信号を出力する。

FGサーボ周波数は次の式で決まるので、FGパルス数,クロック周波数によりモータの回転数を設定する。

f<sub>FG</sub>(サーボ)=f<sub>CLK</sub>/512 f<sub>CLK</sub>:クロック周波数

本ICは、LB11825Mと組み合わせることにより、可変速制御が容易に実現できる。

## 2. 出力駆動回路

本ICは、出力での電力損失(パワーロス)を少なくするために、ダイレクトPWM駆動方式を採用している。出力Trは、オン時は常に飽和しており、出力がオンするデューティを変化させることにより、モータの駆動力を調整する。出力のPWMスイッチングは、下側出力Trで行っているため、OUT - VCC間にはショットキーダイオードを付ける必要がある(逆回復時間の短いダイオードを使用しないと、下側Trがオンする瞬間にスルー電流が流れるため)。OUT - GND間のダイオードは内蔵されている。出力電流が大きいときに問題となる場合(下側キックバック時の波形乱れ等)は、外付けに整流ダイオードまたはショットキーダイオードを付ける。

#### 3. 電流制限回路

電流制限回路は、 $I=V_{RF}/Rf(V_{RF}=0.5V \text{ typ},Rf:$ 電流検出抵抗)で決まる電流で制限(ピーク電流を制限)する。制限動作としては、出力のオンデューティが小さくなり、電流を抑える。

#### 4.パワーセーブ回路

本ICは、ストップ状態では消費電流を減少させるパワーセーブ状態となる。パワーセーブ状態では、大部分の回路のバイアス電流をカットすることにより行っている。パワーセーブ状態においても、5Vレギュレータ出力は出力される。

#### 5. 基準クロック

外部信号源(1MHz max)より、XI端子に直列に抵抗(参考値:約5.1kΩ程度)を介して入力する。XO端子はオープンとする。

入力信号源レベル

「L」レベル電圧 0V~0.8V 「H」レベル電圧 2.5V~5.0V

## 6.速度ロックの範囲

速度ロックの範囲は定速の±6.25%以内であり、モータの回転数がロック範囲内となると、LD端子が「L」となる(オープンコレクタ出力)。モータの回転数がロック範囲を外れた場合、速度の誤差に応じてモータ駆動出力のオンデューティが変化し、モータの回転数がロック範囲内となるように制御がかかる。

#### 7.PWM周波数に関して

PWM周波数はPWM端子に接続するコンデンサ容量C(F)により決まる。

$fPWM 1/(14400 \times C)$

PWM周波数は15k~25kHz程度が望ましい。

#### 8.ホール入力信号

ホール入力は、ヒステリシス幅(42mV max)以上の振幅の信号入力が必要である。ノイズ等の影響を考えると100mV以上の振幅の入力が望ましい。

#### 9.F/R切り替え

モータの回転方向の切り替えは、F/R端子で行うことができる。ただし、F/Rの切り替えをモータ回転状態で行う場合は、次のような注意が必要である。

- ・切り替え時のスルー電流に関しては、回路的に対策を行っている。ただし、切り替え時のVCC電圧の持ち上がり(モータ電流が瞬時的に電源に戻るため)により、定格電圧(30V)を超えないようにする必要がある。問題となる場合は、VCC GND間のコンデンサ容量を大きくする。

- ・切り替わり後のモータ電流が電流制限値以上の場合、下側Trはオフするが、上側Trではショートブレーキ状態となり、モータ逆起電圧およびコイル抵抗によって決まる電流が流れる。この電流が定格電流(2.5A)を超えないようにする必要がある(高い回転数でのF/R切り替えは危険である)。

## 10.拘束保護回路

モータ拘束時のICおよびモータの保護を行うため、拘束保護回路を内蔵している。スタート状態でLD出力が一定時間「H」(アンロック状態)であると、下側出力Trをオフする。時間設定は、CSD端子に接続するコンデンサ容量により行う。10μFの容量で約3.3秒の時間設定が可能である(ばらつき約±30%)。

設定時間(s) 0.33×C(μF)

使用するコンデンサに漏れ電流がある場合は、設定時間の誤差等に影響するため考慮が必要である。 拘束保護状態を解除するには、ストップ状態とするか、電源の再投入(ただし、ストップ状態のこと)が必要である。拘束保護回路を使用しない場合は、CSD端子をGNDに接続すること。

拘束保護を解除するときのストップ時間が短いと、コンデンサの電荷を放電しきれないため、再スタート時に拘束保護が動作する時間が設定より短くなる。よって、次の式を目安にストップ時間には余裕を持たせる必要がある(モータ起動過渡状態で再スタートするときも同様)。

ストップ時間(ms) 15×C(μF)

#### 11. 電源安定化

本ICは出力電流が大きいため、電源ラインが振られやすい。よって、V<sub>CC</sub>端子 - GND間には、安定化のために十分な容量のコンデンサを接続する必要がある。電源の逆接続による破壊防止の目的で、電源ラインにダイオードを挿入する場合は、電源ラインが特に振られやすくなるため、より大きな容量を選択する必要がある。

## LB11826

## 12. 積分アンプ周辺定数

積分アンプ部の外付け部品は、ノイズの影響を受けにくいようにできるだけIC近傍に配置すること。 モータからできるだけ離れた配置とすること。

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equ

ON Semiconductor及びONの口ゴはSemiconductor Components Industries, LLC (SCILLC)の登録商標です。SCILLCは持許、商標、著作権、トレードシークレット(営業秘密)と他の知的所有権に対する権利を保有します。SCILLCの製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLCは通告なしで、本書記載の製品の変更を行うことがあります。SCILLCは、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害に対して、いかなる責任も負うことはできません。SCILLCデータシートや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあり、実際の性能も時間の経過により変化する可能性があります。「標準的」パラメータを含むすべての動作パラメータは、で使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致します。SCILLCは、その特許権やその他の権利の下、いかなるライセンスも許諾しません。SCILLC製品は、人体への外科的移植を目的とするシステムへの使用、生命維持を目的としたアプリケーション、また、SCILLC製品の不具合による死傷等の事故が起こり得るようなアプリケーションをどへの使用を意図した設計はされておらず、また、これらを使用対象としておりません。お客様が、このような意図されたものではない、許可されていないアプリケーション用にSCILLC製品を購入または使用した場合、たとえ、SCILLCがその部品の設計または製造に関して過失があったと主張されたとしても、そのような意図せぬ使用、また未許可の使用に関連した死傷等から、直接、又は間接的に生じるすべてのクレーム、費用、損害、経費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、SCILLCとその役員、従業員、子会社、関連会社、代理店に対して、いかなる損害も与えないものとします。

SCILLCは雇用機会均等/差別撤廃雇用主です。この資料は適用されるあらゆる著作権法の対象となっており、いかなる方法によっても再販することはできません。