# Microphone Pre-Amplifier with Digital Output FAN3852

#### Description

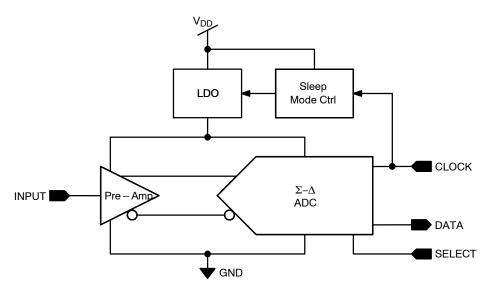

The FAN3852 integrates a pre-amplifier, LDO, and ADC that converts Electret Condenser Microphone (ECM) outputs to digital Pulse Density Modulation (PDM) data streams. The pre-amplifier accepts analog signals from the ECM and drives an over-sampled sigma delta Analog-to-Digital Converter (ADC) and outputs PDM data. The PDM digital audio has the advantage of noise rejection and easy interface to mobile handset processors.

The FAN3852 features an integrated LDO and is powered from the system supply rails up to 3.63 V, with low power consumption of only 0.85 mW and less than 20 µW in Power–Down Mode.

#### **Features**

- Optimized for Mobile Handset and Notebook PC Microphone Applications

- Accepts Input from Electret Condenser Microphones (ECM)

- Pulse Density Modulation (PDM) Output

- Standard 5-Wire Digital Interface

- Low Input Capacitance, High PSR, 20 kHz Pre-Amplifier

- Low-Power 1.5 μA Sleep Mode

- Typical 420 μA Supply Current

- SNR of 62 dB (A) for 16 dB Gain

- Total Harmonic Distortion 0.02%

- Input Clock Frequency Range of 1–4 MHz

- Integrated Low Drop-Out Regulator (LDO)

- Small 1.242 mm × 0.842 mm 6–Ball, 0.400 mm pitch standard WLCSP Package

1

• 1.5 kV HBM ESD on MIC Input

#### **Typical Applications**

- Electret Condenser Microphones with Digital Output

- Mobile Handset

- Headset Accessories

- Personal Computer (PC)

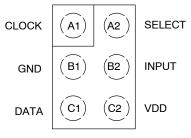

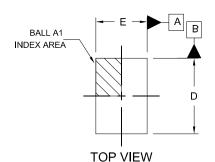

#### **PIN CONFIGURATION**

Top View

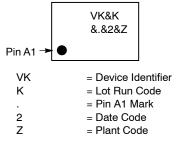

#### **MARKING DIAGRAM**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 2 of this data sheet.

#### **ORDERING INFORMATION**

| Part Number  | Operating Temperature Range | Package                                           | Packing Method <sup>†</sup> |

|--------------|-----------------------------|---------------------------------------------------|-----------------------------|

| FAN3852UC16X | –40°C to 85°C               | 6 Ball, Wafer-Level<br>Chip-Scale Package (WLCSP) | 3000 Units/Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

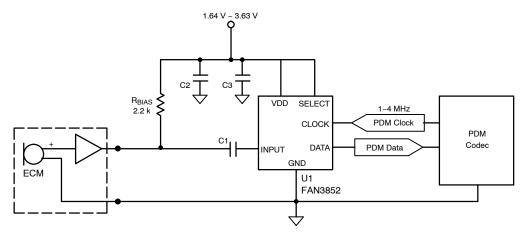

#### INTERNAL BLOCK DIAGRAM

Figure 1. Block Diagram

**Table 1. PIN DEFINITIONS**

| Pin # | Name   | Type   | Description                         |  |

|-------|--------|--------|-------------------------------------|--|

| A1    | CLOCK  | Input  | Clock Input                         |  |

| B1    | GND    | Input  | Ground Pin                          |  |

| C1    | DATA   | Output | PDM Output – 1 Bit ADC              |  |

| A2    | SELECT | Input  | Rising or Falling Clock Edge Select |  |

| B2    | INPUT  | Input  | Microphone Input                    |  |

| C2    | VDD    | Input  | Device Power Pin                    |  |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                                                       | Min. | Max.                  | Unit |

|-----------------|-----------------------------------------------------------------|------|-----------------------|------|

| $V_{DD}$        | DC Supply Voltage                                               | -0.3 | 4.0                   | V    |

| V <sub>IO</sub> | Digital I/O                                                     | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                 | Microphone Input                                                | -0.3 | 2.2                   |      |

| ESD             | Human Body Model, JESD22-A114, All Pins Except Microphone Input | ±8   |                       | kV   |

|                 | Human Body Model, JESD2-A114 - Microphone Input                 | ±1.5 |                       |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>1.</sup> This device is fabricated using CMOS technology and is therefore susceptible to damage from electrostatic discharges. Appropriate precautions must be taken during handling and storage of this device to prevent exposure to ESD.

#### **Table 3. RELIABILITY INFORMATION**

| Symbol                                                                                | Rating                                                                                                                     | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| TJ                                                                                    | T <sub>J</sub> Junction Temperature  T <sub>STG</sub> Storage Temperature Range  T <sub>RFLW</sub> Peak Reflow Temperature |      |      | +150 | °C   |

| T <sub>STG</sub>                                                                      |                                                                                                                            |      |      | +125 | °C   |

| T <sub>RFLW</sub>                                                                     |                                                                                                                            |      |      | +260 | °C   |

| θ <sub>JA</sub> Thermal Resistance, JEDEC Standard, Multilayer Test Boards, Still Air |                                                                                                                            |      | 90   |      | °C/W |

<sup>2.</sup>  $T_A = 25^{\circ}C$  unless otherwise specified

#### **Table 4. RECOMMENDED OPERATING CONDITIONS**

| Symbol              | Rating                                     | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------|------|------|------|------|

| T <sub>A</sub>      | T <sub>A</sub> Operating Temperature Range |      |      | +85  | °C   |

| $V_{DD}$            | V <sub>DD</sub> Supply Voltage Range       |      | 1.80 | 3.63 | ٧    |

| T <sub>RF-CLK</sub> | Clock Rise and Fall Time                   |      |      | 10   | ns   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Table 5. DEVICE SPECIFIC ELECTRICAL CHARACTERISTICS

|                                                                                     |                                                                     |      | FAN3852UC16X |      |                   |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------|------|--------------|------|-------------------|

| Symbol                                                                              | Value                                                               | Min. | Тур.         | Max. | Unit              |

| SNR                                                                                 | Signal-to-Noise Ratio<br>f <sub>IN</sub> = 1 kHz (1 Pa), A-Weighted |      | 62           |      | dB (A)            |

| e <sub>N</sub>                                                                      | e <sub>N</sub> Total Input RMS Noise<br>20 Hz to 20 kHz, A-Weighted |      | 5.74         | 6.80 | μV <sub>RMS</sub> |

| $V_{IN}$ Maximum Input Signal $f_{IN} = 1 \text{ kHz}$ , THD + N < 10%, Level = 0 V |                                                                     |      |              | 448  | mV <sub>PP</sub>  |

<sup>3.</sup> Guaranteed by characterization and/or design. Not production tested.

#### **Table 6. ELECTRICAL CHARACTERISTICS**

Unless otherwise specified, al limits are guaranteed for  $T_A$  = 25°C,  $V_{DD}$  = 1.8 V,  $V_{IN}$  = 94 dB (SPL) and  $f_{CLK}$  = 2.4 MHz. Duty Cycle = 50% and  $C_{MIC}$  = 15 pF

| Symbol             | Parameter                               | Condition                                                                                                                                         | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{DD}$           | Supply Voltage Range                    |                                                                                                                                                   | 1.64 | 1.80 | 3.63 | V    |

| I <sub>DD</sub>    | Supply Current                          | INPUT = AC Coupled to GND,<br>CLOCK = On, No Load                                                                                                 |      | 420  |      | μΑ   |

| I <sub>SLEEP</sub> | Sleep Mode Current                      | f <sub>CLK</sub> = GND                                                                                                                            |      | 1.50 | 8.0  | μΑ   |

| PSR                | Power Supply Rejection (Note 5)         | INPUT = AC Coupled to GND,<br>Test Signal on V <sub>DD</sub> = 217 Hz,<br>Square Wave and Broadband<br>Noise (Note 4), Both 100 mV <sub>P-P</sub> |      | -74  |      | dBFS |

| IN <sub>NOM</sub>  | Nominal Sensitivity (Note 6)            | INPUT = 94 dBSPL (1 Pa)                                                                                                                           |      | -26  |      | dBFS |

| THD                | Total Harmonic Distortion (Note 7)      | f <sub>IN</sub> = 1 KHz, INPUT = -26 dBFS                                                                                                         |      | 0.02 | 0.20 | %    |

| THD+N              | THD and Noise (Note 5)                  | 50 Hz $\leq$ f <sub>IN</sub> $\leq$ 1 kHz,<br>INPUT = -20 dBFS                                                                                    |      | 0.2  | 1.0  | %    |

|                    |                                         | f <sub>IN</sub> = 1 KHz, INPUT = -5 dBFS                                                                                                          |      | 1.0  | 5.0  |      |

|                    |                                         | f <sub>IN</sub> = 1 KHz, INPUT = 0 dBFS                                                                                                           |      | 5.0  | 10.0 |      |

| C <sub>IN</sub>    | Input Capacitance (Note 8)              | INPUT                                                                                                                                             |      | 1.3  |      | pF   |

| R <sub>IN</sub>    | Input Resistance (Note 8)               | INPUT                                                                                                                                             | >10  |      |      | GΩ   |

| V <sub>IL</sub>    | CLOCK & SELECT Input Logic<br>LOW Level |                                                                                                                                                   |      |      | 0.3  | ٧    |

# Table 6. ELECTRICAL CHARACTERISTICS (continued)

Unless otherwise specified, al limits are guaranteed for  $T_A$  = 25°C,  $V_{DD}$  = 1.8 V,  $V_{IN}$  = 94 dB (SPL) and  $f_{CLK}$  = 2.4 MHz. Duty Cycle = 50% and  $C_{MIC}$  = 15 pF

| Symbol                  | Parameter                                            | Condition                                                            | Min.                 | Тур. | Max.                 | Unit  |

|-------------------------|------------------------------------------------------|----------------------------------------------------------------------|----------------------|------|----------------------|-------|

| V <sub>IH</sub>         | CLOCK & SELECT Input Logic<br>HIGH Level             |                                                                      | 1.5                  |      | V <sub>DD</sub> +0.3 | V     |

| V <sub>OL</sub>         | Data Output Logic LOW Level                          |                                                                      |                      |      | 0.35*V <sub>DD</sub> | V     |

| V <sub>OH</sub>         | Data Output Logic HIGH Level                         |                                                                      | 0.65*V <sub>DD</sub> |      |                      | V     |

| V <sub>OUT</sub>        | Acoustic Overload Point (Note 8)                     | THD+N < 10%                                                          | 120                  |      |                      | dBSPL |

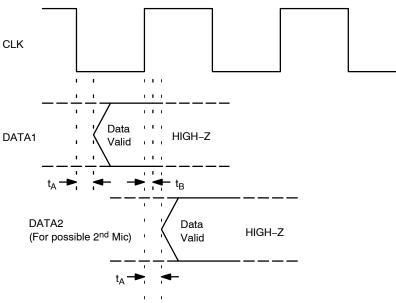

| t <sub>A</sub>          | Time from CLOCK Transition to<br>Data becoming Valid | On Falling Edge of CLOCK,<br>SELECT = GND, C <sub>LOAD</sub> = 15 pF | 18                   | 43   |                      | ns    |

| t <sub>B</sub>          | Time from CLOCK Transition to Data becoming HIGH-Z   | On Rising Edge of CLOCK,<br>SELECT = GND, C <sub>LOAD</sub> = 15 pF  | 0                    | 5    | 16                   | ns    |

| t <sub>A</sub>          | Time from CLOCK Transition to<br>Data becoming Valid | On Rising Edge of CLOCK, SELECT = $V_{DD}$ , $C_{LOAD}$ = 15 pF      | 18                   | 58   |                      | ns    |

| t <sub>B</sub>          | Time from CLOCK Transition to Data becoming HIGH-Z   | On Falling Edge of CLOCK, SELECT = $V_{DD}$ , $C_{LOAD}$ = 15 pF     | 0                    | 5    | 16                   | ns    |

| f <sub>CLK</sub>        | Input CLOCK Frequency (Note 9)                       | Active Mode                                                          | 1.0                  | 2.4  | 4.0                  | MHz   |

| CLK <sub>dc</sub>       | CLOCK Duty Cycle (Note 5)                            |                                                                      | 40                   | 50   | 60                   | %     |

| t <sub>WAKEUP</sub>     | Wake-Up Time (Note 10)                               | f <sub>CLK</sub> = 2.4 MHz                                           |                      | 0.35 | 2.00                 | ms    |

| t <sub>FALLASLEAP</sub> | Fall-Asleep Time (Note 11)                           | f <sub>CLK</sub> = 2.4 MHz                                           | 0                    | 0.01 | 1.00                 | ms    |

| C <sub>LOAD</sub>       | Load Capacitance on Data                             |                                                                      |                      |      | 100                  | pF    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 4. Pseudo-random noise with triangular probability density function. Bandwidth up to 10 MHz.

- 5. Guaranteed by characterization. Not production tested.

- 6. Assuming that 120 dB (SPL) is mapped to 0 dBFS.

- 7. Assuming an input of -42 dBV (maps to -26 dBFS, 94 dB\_SPL).

- 8. Guaranteed by design. Not production tested.

- 9. All parameters are tested at 2.4 MHz. Frequency range guaranteed by characterization.

- 10. Device wakes up when  $f_{CLK} \ge 300 \text{ kHz}$ .

- 11. Device falls asleep when f<sub>CLK</sub> ≤ 70 kHz.

$t_{\mbox{\scriptsize A}}$  – Microphone delay from clock edge to data assertion.

$t_{\mbox{\footnotesize{B}}}$  – Microphone delay from clock edge to high-impedance state.

$t_A > t_B$  to have interim HIGH-Z state in both signals.

Figure 2. Interface Timing

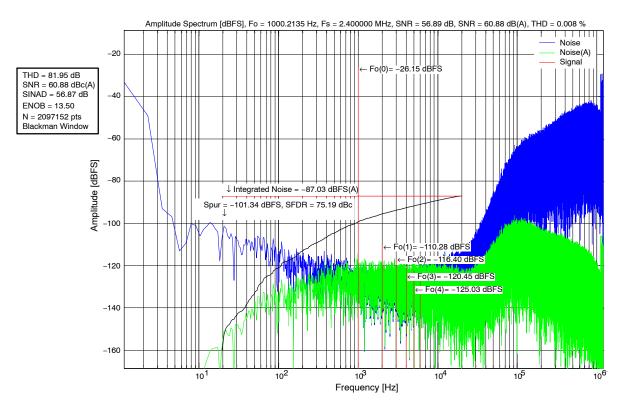

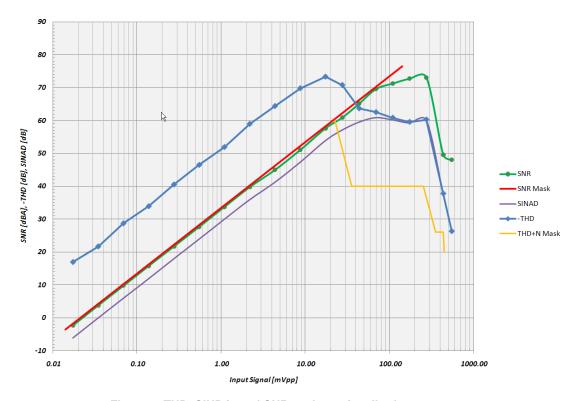

# TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V_{DD} = 1.8$  V,  $V_{IN} = 94$  dB (SPL),  $f_{CLK} = 2.4$  MHz and duty Cycle = 50%.

Figure 3. Noise vs. Frequency

Figure 4. THD, SINDA, and SNR vs. Input Amplitude

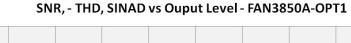

# TYPICAL PERFORMANCE CHARACTERISTICS (continued)

Unless otherwise specified, all limits are guaranteed for  $T_A = 25^{\circ}C$ ,  $V_{DD} = 1.8 \text{ V}$ ,  $V_{IN} = 94 \text{ dB (SPL)}$ ,  $f_{CLK} = 2.4 \text{ MHz}$  and duty Cycle = 50%.

Figure 5. THD, SINAD and SNR vs. Output Level

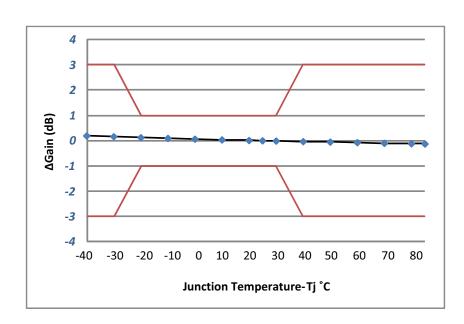

| Temp (°C) | Delta (dB) |

|-----------|------------|

| -40       | 0.1971     |

| -30       | 0.1644     |

| -20       | 0.1260     |

| -10       | 0.0954     |

| 0         | 0.0657     |

| 10        | 0.0359     |

| 20        | 0.0139     |

| 25        | 0.0000     |

| 30        | -0.0097    |

| 40        | -0.0344    |

| 50        | -0.0514    |

| 60        | -0.0739    |

| 70        | -0.0998    |

| 80        | -0.1183    |

| 85        | -0.1271    |

Figure 6.  $\Delta$  Gain vs. Temperature (Nominal Temperature = 25°C)

# **APPLICATIONS INFORMATION**

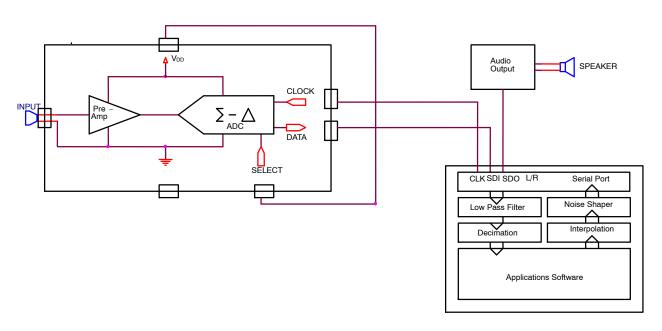

Figure 7. Mono Microphone Application Circuit

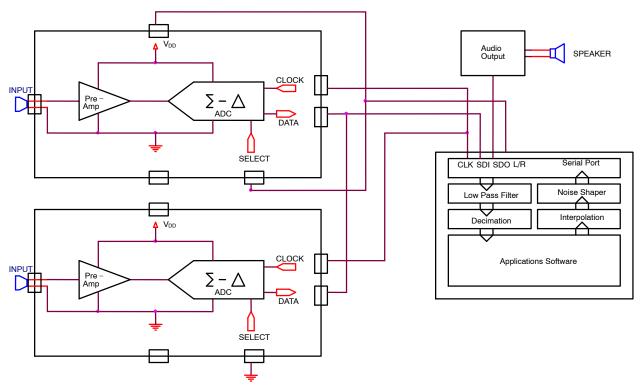

Figure 8. Stereo Microphone Application Circuit

# **APPLICATIONS INFORMATION (continued)**

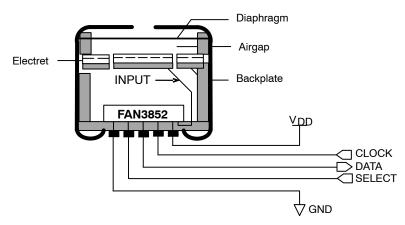

Figure 9. MIC Element Drawing

$A~0.1~\mu F$  decoupling capacitor is required for VDD. It can be located inside the microphone or on the PCB very close to the VDD pin.

Due to high input impedance, care should be taken to remove all flux used during the reflow soldering process.

A 100  $\Omega$  resistance is recommended on the clock output of the device driving the FAN3852 to minimize ringing and improve signal integrity.

For optimal PSR, route a trace to the VDD pin. Do not place a VDD plane under the device.

Figure 10. Example Hardware Implementation

**Table 7. RECOMMENDED COMPONENTS**

| Ref Des | Qty | Description of Options                                             | Package | Manufacturer            | Mfg PIN            |

|---------|-----|--------------------------------------------------------------------|---------|-------------------------|--------------------|

| U1      | 1   | FAN3852 Microphone Pre-Amplifier with Digital Output               | WLCSP6  | onsemi                  | FAN3852UC16X       |

| C1      | 1   | Input AC Coupling Capacitor;<br>1 nF/1000 pF, ≥ 6.3 V, low-leakage | 0402    | Johansen<br>Dielectrics | 500R07W102KV4T     |

|         |     |                                                                    | 0402    | Murata                  | GCM155R71H102KA37D |

|         |     |                                                                    | 0603    | Taiyo Yuden             | UMK107SD102KA-T    |

| C2      | 1   | 1 Primary VDD Decoupling Capacitor;                                | 0402    | Samsung                 | CL05B104KO5NNNC    |

|         |     | 0.1 μF, MLCC, ≥ 6.3 V                                              | 0402    | Yageo                   | CC0402KRX7R7BB104  |

|         |     |                                                                    | 0603    | AVX                     | 06033C104KAT4A     |

| СЗ      | 1   | Optional VDD Decoupling Capacitor;                                 | 0402    | Samsung                 | CL05B103KB5VPNC    |

|         |     | 0.01 μF, MLCC, ≥ 6.3 V                                             | 0402    | Murata                  | GCM155R71H103KA55J |

|         |     |                                                                    | 0603    | Yageo                   | CC0603KRX7R7BB103  |

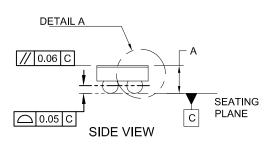

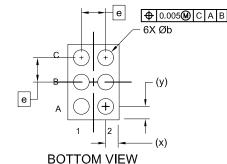

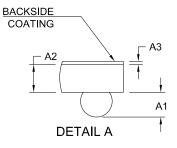

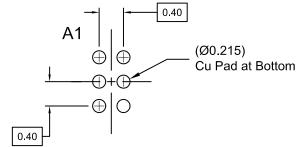

#### WLCSP6 1.242x0.842x0.457

CASE 567TS ISSUE A

**DATE 06 JUN 2019**

#### NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. DATUM C APPLIES TO THE SPHERICAL CROWN OF THE SOLDER BALLS

|     | MILLIMETERS |       |       |  |  |

|-----|-------------|-------|-------|--|--|

| DIM | MIN.        | NOM.  | MAX.  |  |  |

| Α   | 0.419       | 0.457 | 0.495 |  |  |

| A1  | 0.183       | 0.203 | 0.223 |  |  |

| A2  | 0.214       | 0.244 |       |  |  |

| А3  | 0.022       | 0.025 | 0.028 |  |  |

| b   | 0.24        | 0.26  | 0.28  |  |  |

| D   | 1.212       | 1.242 | 1.272 |  |  |

| Е   | 0.812       | 0.842 | 0.872 |  |  |

| е   | 0.40 BSC    |       |       |  |  |

| х   | 0.206       | 0.221 | 0.236 |  |  |

| у   | 0.206       | 0.221 | 0.236 |  |  |

# RECOMMENDED MOUNTING FOOTPRINT\* (NSMD PAD TYPE)

\* For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON13367G             | Electronic versions are uncontrolled except when accessed directly from the Document Report Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | WLCSP6 1.242x0.842x0.45 | 7                                                                                                                                                                           | PAGE 1 OF 1 |  |  |

onsemi and ONSemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales