# One Buck, One Boost and Four LDO PMIC

# **FAN53880**

### **General Description**

The FAN53880 is a low quiescent current PMIC for mobile power applications. The PMIC contains one buck, one boost, and four low noise LDOs.

The buck and boost converters can operate within a wide supply range of 2.5 V to 5.5 V. At moderate and light loads, Pulse Frequency Modulation (PFM) reduces current consumption while maintaining excellent transient response during load swings. At higher loads, the converters automatically switch to Pulse Width Modulation (PWM) control.

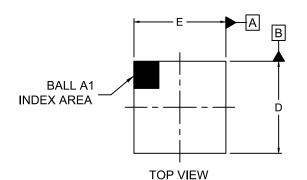

The FAN53880 is available in a 25-bump, 0.4 mm pitch, Wafer-Level Chip-Scale Package (WLCSP).

#### **Features**

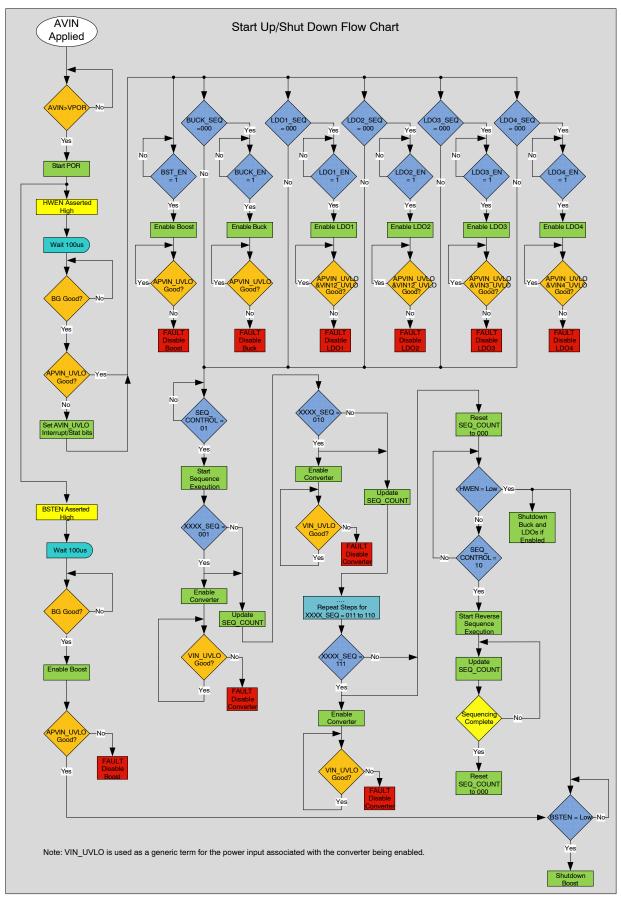

- Programmable Start-Up/Down Sequencing

- Programmable Output Voltages

- Soft-Start (SS) Inrush Current Limiting

- Fault Protection with Interrupt Reporting

- UVLO, OCP, OVP, UVP and OTP

- Low Current Standby and Shutdown Modes

- Buck Converter:

- ◆ Input Voltage Range: 2.5 V to 5.5 V

- Digitally Programmable Voltage Range: 0.6 V to 3.3 V

- ◆ 1200 mA Output Current Capability

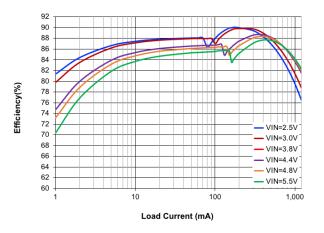

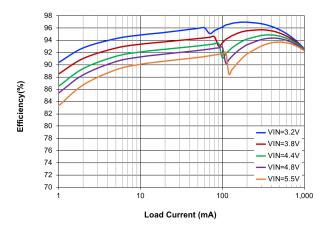

- ◆ 95% Efficiency

- Boost Converter:

- ◆ Input Voltage Range: 2.5 V to 5.5 V

- Digitally Programmable Voltage Range: 3.0 V to 5.7 V

- 1000 mA Output Current Capability

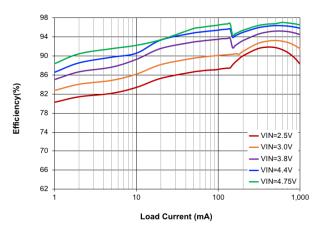

- ◆ 95% Efficiency

- Four LDOs:

- ◆ Input Voltage Range: 1.9 V to 5.5 V

- Digitally Programmable Voltage Range: 0.8 V to 3.3 V

- 300 mA Output Current Capability

#### **Applications**

- Smartphones and Tablets

- Compact Camera Modules

- USB On-The-Go

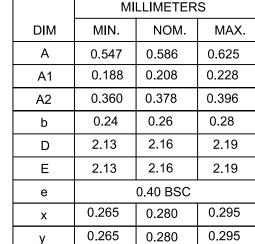

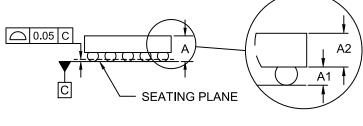

#### **MARKING DIAGRAM**

12 = Alphanumeric Device Marking

KK = Lot Run Code

X = Alphabetical Year Code Y = 2-weeks Date Code Z = Assembly Plant Code

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

NOTE: Some of the devices on this data sheet have been **DISCONTINUED**. Please refer to the table on page 2.

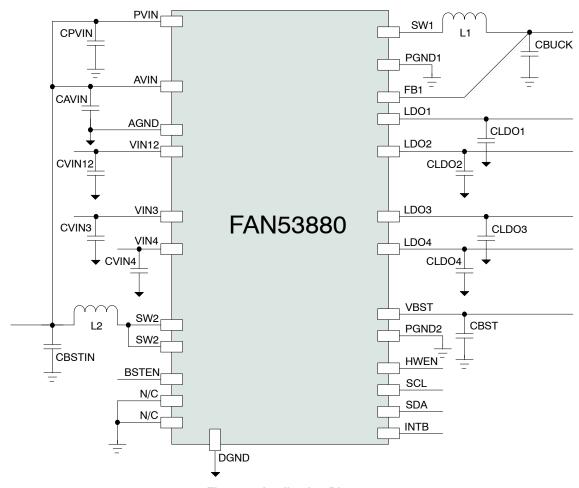

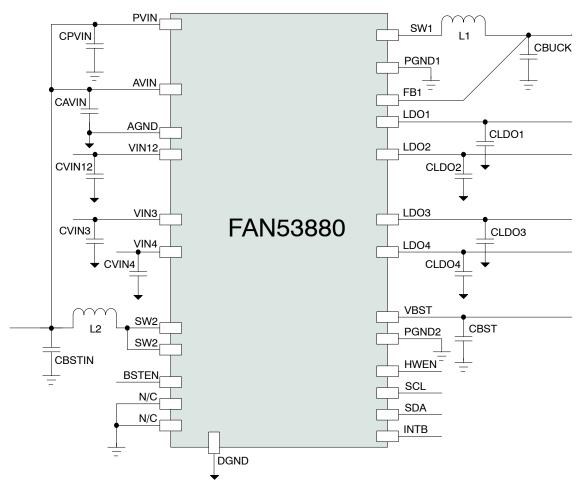

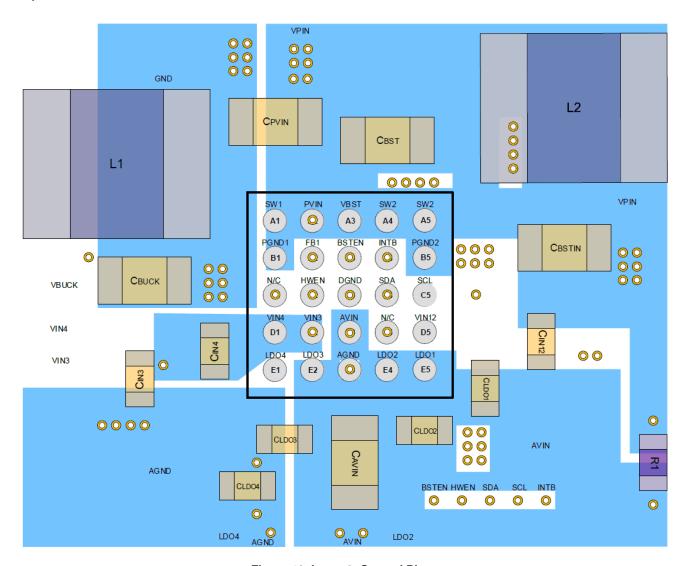

### **Application Diagram**

Figure 1. Application Diagram

### **PART NUMBERING**

#### **Table 1. ORDERING INFORMATION**

| Part Number    | Buck<br>V <sub>OUT</sub> | LDO1,2<br>V <sub>OUT</sub> | LDO3,4<br>V <sub>OUT</sub> | Boost<br>V <sub>OUT</sub> | I2C<br>Address | Temperature<br>Range | Package          | Packing<br>Method             | Device<br>Marking |

|----------------|--------------------------|----------------------------|----------------------------|---------------------------|----------------|----------------------|------------------|-------------------------------|-------------------|

| FAN53880UC002X | 1.1 V                    | 2.8 V                      | 1.8 V                      | 5.0 V                     | 7'h35          | –40°C to 85°C        | 25-Bump<br>WLCSP | Tape and<br>Reel <sup>†</sup> | LW                |

# **DISCONTINUED** (Note 1)

| FAN53880UC001X | 1.1 V | 2.8 V | 1.8 V | 5.0 V | 7'h35 | -40°C to 85°C | 25-Bump<br>WLCSP | Tape and<br>Reel <sup>†</sup> | LT |

|----------------|-------|-------|-------|-------|-------|---------------|------------------|-------------------------------|----|

|----------------|-------|-------|-------|-------|-------|---------------|------------------|-------------------------------|----|

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

<sup>1.</sup> **DISCONTINUED:** This device is not recommended for new design. Please contact your **onsemi** representative for information. The most current information on this device may be available on <a href="https://www.onsemi.com">www.onsemi.com</a>.

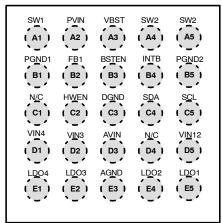

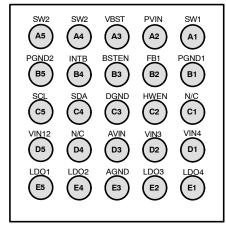

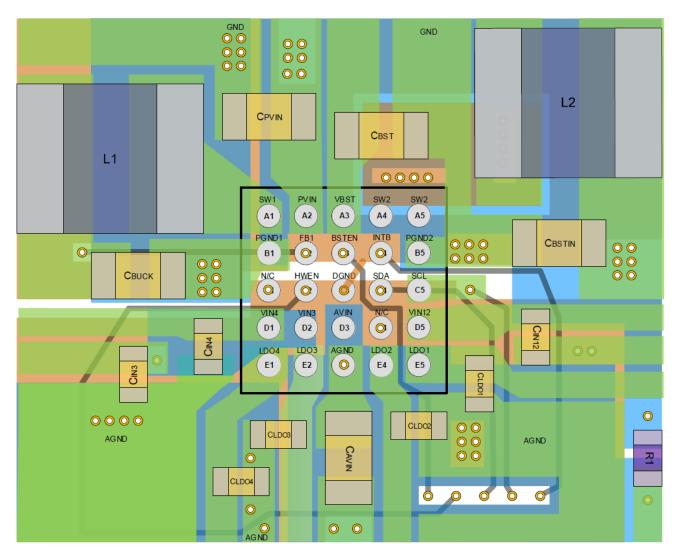

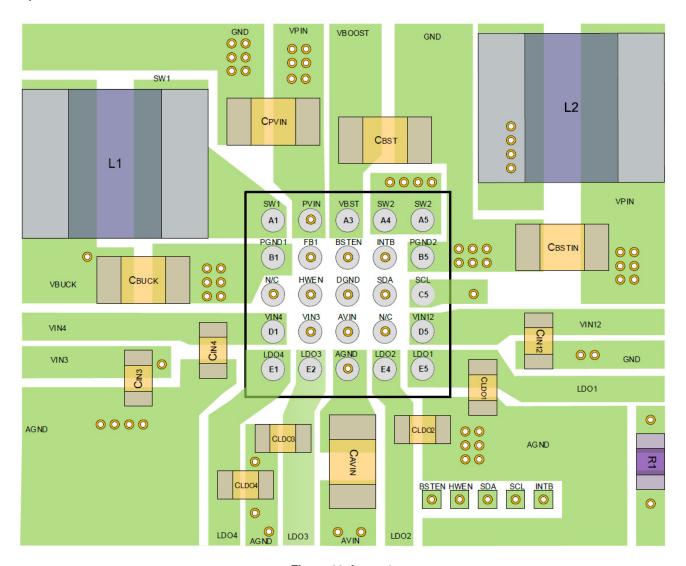

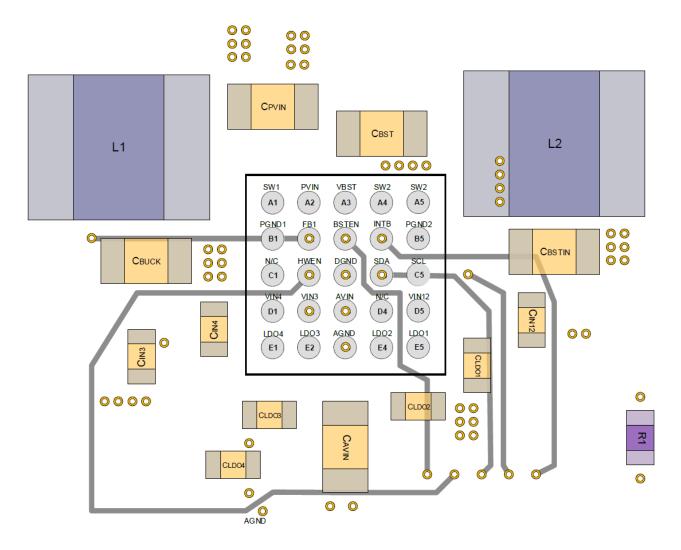

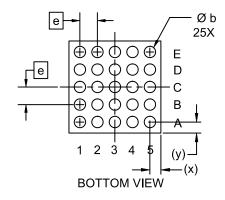

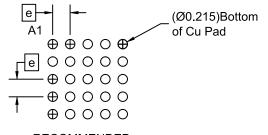

### **PRODUCT PIN ASSIGNMENTS**

### **Pin Configuration**

Figure 2. Pin Configuration

### **Pin Descriptions**

### **Table 2. PIN DEFINITION**

| Pin    | Pin Name | Description                                                                                                                                                                                                                                                                                                                                         |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1.    | SW1      | Switching node of the buck converter. Tie one lead of the inductor to this pin.                                                                                                                                                                                                                                                                     |

| A2     | PVIN     | Input power for the buck and boost converter. Bypass this pin with $C_{PVIN}$ close to the device pin. The voltage must be kept within 25 mV of AV $_{IN}$ .                                                                                                                                                                                        |

| АЗ     | VBST     | Boost output node. Locate C <sub>BST</sub> close to this pin                                                                                                                                                                                                                                                                                        |

| A4, A5 | SW2      | Switching node for the boost converter.                                                                                                                                                                                                                                                                                                             |

| B1     | PGND1    | Power ground connection for the buck converter. Connect directly to ground plane.                                                                                                                                                                                                                                                                   |

| B2     | FB1      | Feedback pin for the buck converter. Connect to C <sub>BUCK</sub> and keep trace away from noisy circuitry.                                                                                                                                                                                                                                         |

| В3     | BSTEN    | Enables the boost and critical circuits associated with the boost operation when asserted high. The BSTEN pin has an internal 2.8 $M\Omega$ pull-down and should always be connected to a logic high or low. Note: HWEN does not need to be high for Boost operation when BSTEN is high.                                                            |

| B4     | INTB     | I2C interrupt pin is active low indicating that an interrupt event has occurred.                                                                                                                                                                                                                                                                    |

| B5     | PGND2    | Power ground connection for the Boost converter. Connect directly to ground plane.                                                                                                                                                                                                                                                                  |

| C1     | N/C      | This pin is a no-connect within the device. It is recommended to tie this pin to ground, but is not necessary.                                                                                                                                                                                                                                      |

| C2     | HWEN     | HWEN pin is used to enable basic circuits necessary for controlling the power converter outputs. The HWEN pin has an internal 5 M $\Omega$ pull-down and should always be connected to a logic high or low.                                                                                                                                         |

| СЗ     | DGND     | Digital/Analog ground connection. Tie to inner layer power plane through via.                                                                                                                                                                                                                                                                       |

| C4     | SDA      | I2C Data pin. Node should be tied high through a pull up resistor.                                                                                                                                                                                                                                                                                  |

| C5     | SCL      | I2C Clock pin. Node should be tied high through a pull up resistor.                                                                                                                                                                                                                                                                                 |

| D1     | VIN4     | Input power pin for LDO4. Place C <sub>VIN4</sub> as close to this pin as possible.                                                                                                                                                                                                                                                                 |

| D2     | VIN3     | Input power pin for LDO3. Place C <sub>VIN3</sub> as close to this pin as possible.                                                                                                                                                                                                                                                                 |

| D3     | AVIN     | Analog power pin. Route trace from battery side of the boost inductor (L2) to the $AV_{IN}$ pin. Connect the $C_{AVIN}$ capacitor as close as possible to the pin. To create a low pass filter, a series resistor may be added between the inductor and $C_{AVIN}$ . The voltage must be kept within 25 mV of $PV_{IN}$ to ensure system stability. |

| D4     | N/C      | This pin is a no-connect within the device. It is recommended to tie this pin to ground, but is not necessary.                                                                                                                                                                                                                                      |

| D5     | VIN12    | This is the input power pin for LDO1 and LDO2. Place C <sub>VIN12</sub> as close to this pin as possible.                                                                                                                                                                                                                                           |

| E1     | LDO4     | This is the output pin for LDO4. Place C <sub>LDO4</sub> as close to this pin as possible.                                                                                                                                                                                                                                                          |

| E2     | LDO3     | This is the output pin for LDO3. Place C <sub>LDO3</sub> as close to this pin as possible.                                                                                                                                                                                                                                                          |

| E3     | AGND     | Analog ground is the analog circuitry ground. Tie this pin to the analog ground plane.                                                                                                                                                                                                                                                              |

| E4     | LDO2     | This is the output pin for LDO2. Place C <sub>LDO2</sub> as close to this pin as possible.                                                                                                                                                                                                                                                          |

| E5     | LDO1     | This is the output pin for LDO1. Place C <sub>LDO1</sub> as close to this pin as possible.                                                                                                                                                                                                                                                          |

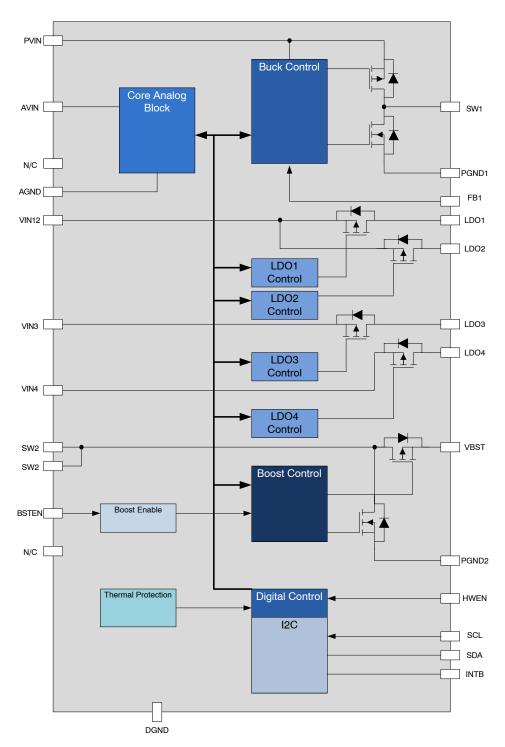

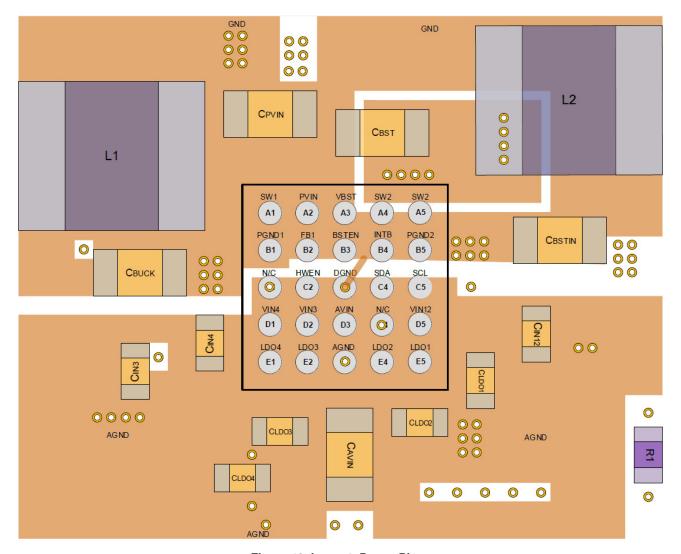

### PRODUCT BLOCK DIAGRAM

# **Block Diagram**

Figure 3. Block Diagram

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                          | Conditions                                                                                      | Min  | Тур | Max                                                              | Units |

|-------------------|------------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------------------------------------------------------------------|-------|

| V <sub>IN</sub>   | Input Voltage                      | AV <sub>IN</sub> , PV <sub>IN</sub> , V <sub>IN12</sub> , V <sub>IN3</sub> and V <sub>IN4</sub> | -0.3 |     | (Note 2)                                                         | V     |

| V <sub>SW1</sub>  | Voltage on SW1 Pin                 |                                                                                                 | -0.3 |     | (Note 2)                                                         | V     |

| V <sub>SW2</sub>  | Voltage on SW2 Pin                 |                                                                                                 | -0.3 |     | (Note 2)                                                         | V     |

| V <sub>CTRL</sub> | SDA and SCL Pins                   |                                                                                                 | -0.3 |     | (Note 2)                                                         | V     |

| V <sub>INTB</sub> | INTB Pins                          |                                                                                                 | -0.3 |     | $AV_{IN}$                                                        | V     |

|                   | other Pins                         |                                                                                                 | -0.3 |     | (Note 2)                                                         | V     |

| ESD               | Electrostatic Discharge Protection | Human Body Model                                                                                |      | 2.0 |                                                                  | kV    |

|                   | Level                              | Charged Device Model                                                                            |      | 500 | (Note 2)<br>(Note 2)<br>(Note 2)<br>(Note 2)<br>AV <sub>IN</sub> | V     |

| TJ                | Junction Temperature               |                                                                                                 | -40  |     | +150                                                             | °C    |

| T <sub>STG</sub>  | Storage Temp                       |                                                                                                 | -40  |     | +150                                                             | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 4. THERMAL PROPERTIES**

| Sym | lodr | Parameter                              | Typical | Unit |

|-----|------|----------------------------------------|---------|------|

| θ   | JA   | Junction-to-Ambient Thermal Resistance | 58      | °C/W |

NOTE: Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with two-layer 2s2p boards in accordance to JEDEC standard JESD51. Special attention must be paid not to exceed junction temperature T<sub>J(max)</sub> at a given ambient temperature T<sub>A</sub>.

#### **Table 5. RECOMMENDED OPERATING CONDITIONS**

| Symbol            | Parameter                     | Conditions                            | Min | Тур | Max  | Units |

|-------------------|-------------------------------|---------------------------------------|-----|-----|------|-------|

| AP <sub>VIN</sub> | Supply Voltage Range          | AV <sub>IN</sub> , PV <sub>IN</sub>   | 2.5 |     | 5.5  | V     |

| V <sub>IN12</sub> |                               | $V_{\text{IN}12}$                     | 2.5 |     | 5.5  | V     |

| V <sub>IN3</sub>  |                               | $V_{IN3}$                             | 1.9 |     | 5.5  | V     |

| $V_{IN4}$         |                               | $V_{IN4}$                             | 1.9 |     | 5.5  | V     |

| $P_{D}$           | Power Dissipation             | PD = (125°C - 85°C) / 58°C/W = 0.69 W |     |     | 0.69 | W     |

| T <sub>A</sub>    | Operating Ambient Temperature |                                       | -40 |     | 85   | °C    |

| $T_J$             | Junction Temperature          |                                       | -40 |     | 125  | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

<sup>2.</sup> Lesser of 6 V or AV $_{\rm IN}$  + 0.3 V.

### Table 6. ELECTRICAL CHARACTERISTICS

Minimum and maximum values are at AV<sub>IN</sub> = PV<sub>IN</sub> = 2.5 V to 5.5 V & PV<sub>IN</sub> > V<sub>BUCK</sub> + 350 mV and PV<sub>IN</sub> < V<sub>BST</sub> - 250 mV, V<sub>IN12</sub> = 2.5 V to 5.5 V & V<sub>IN3</sub>, V<sub>IN4</sub> > V<sub>LD03/4</sub> + 150 mV, V<sub>BUCK</sub> = 0.6 V to 3.3 V, V<sub>BST</sub> = 3.0 V to 5.7 V, V<sub>LD01</sub>, V<sub>LD02</sub>, V<sub>LD03</sub> and V<sub>LD04</sub> = 0.8 V to 3.3 V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, AV<sub>IN</sub>, PV<sub>IN</sub>, V<sub>IN12</sub> = 3.8 V, V<sub>IN3</sub>, V<sub>IN4</sub> = 1.95 V, V<sub>BUCK</sub> = 1.1 V, V<sub>BST</sub> = 5.0 V, V<sub>LD01</sub> and V<sub>LD02</sub> = 2.8 V, V<sub>LD03</sub> and V<sub>LD04</sub> = 1.8 V.

| Symbol                        | Parameter                                              | Conditions                                                                                                                                                     | Min               | Тур               | Max               | Units |

|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------|

| POWER SUPPLIE                 | S UVLO                                                 |                                                                                                                                                                |                   |                   |                   |       |

| V <sub>VIN UVLO_RISE</sub>    | Under-Voltage Lockout Thresh-                          | Rising AV <sub>IN</sub> or V <sub>IN12</sub>                                                                                                                   | 2.30              | 2.35              | 2.45              | V     |

| V <sub>VIN UVLO_FALL</sub>    | old                                                    | Falling AV <sub>IN</sub> or V <sub>IN12</sub>                                                                                                                  | 2.15              | 2.25              | 2.30              | V     |

| V <sub>VIN3/4</sub> UVLO_RISE |                                                        | Rising V <sub>IN3</sub> and V <sub>IN4</sub>                                                                                                                   | 1.80              | 1.85              | 1.95              | V     |

| V <sub>VIN3/4</sub> UVLO_FALL |                                                        | Falling V <sub>IN3</sub> and V <sub>IN4</sub>                                                                                                                  | 1.70              | 1.75              | 1.80              | V     |

| BUCK EC                       |                                                        |                                                                                                                                                                |                   |                   |                   | ı     |

| POWER SUPPLIE                 | S                                                      |                                                                                                                                                                |                   |                   |                   |       |

| IQ <sub>BK_PFM</sub>          | PFM Quiescent Current                                  | Total current on $PV_{IN}$ and $AV_{IN}$ when $AV_{IN}$ = $PV_{IN}$ = VHWEN, BUCK_EN bit = 1, PFM Mode, Non Switching, No Load, all other converters disabled. |                   | 36                |                   | μΑ    |

| R <sub>BK_DIS</sub>           | Output Discharge Resistance                            |                                                                                                                                                                | 80                | 100               | 120               | Ω     |

| PFM ↔ PWM THR                 | ESHOLDS                                                |                                                                                                                                                                |                   |                   |                   |       |

| I <sub>BK_PFM</sub>           | I <sub>OUT</sub> where part transitions into PFM       |                                                                                                                                                                |                   | 50                |                   | mA    |

| I <sub>BK_PWM</sub>           | I <sub>OUT</sub> value where part transitions into PWM |                                                                                                                                                                |                   | 120               |                   | mA    |

| BUCK V <sub>OUT</sub> ACCL    | JRACY                                                  |                                                                                                                                                                |                   |                   |                   |       |

| VO <sub>BK_ACC</sub>          | PFM Output Voltage Accuracy                            | $V_{OUT}$ = 0.6 V, $AV_{IN}$ = $PV_{IN}$ = 3.8 V, PFM Mode, $I_{OUT}$ = 0 A                                                                                    | -3                |                   | 3                 | %     |

|                               |                                                        | $AV_{IN} = PV_{IN} = 3.8 \text{ V}$ , No Load, PFM Mode, $V_{OUT} = 1.0125 \text{ V}$ to 3.3 V                                                                 | -2                |                   | 2                 | %     |

|                               | PWM Output Voltage Accuracy                            | $V_{OUT}$ = 0.6 V, $AV_{IN}$ = $PV_{IN}$ = 3.8 V, $PWM$ Mode, $I_{OUT}$ = 0 A                                                                                  | -3                |                   | 3                 | %     |

|                               |                                                        | $AV_{IN} = PV_{IN} = 3.8V$ , No Load, PWM Mode, $V_{OUT} = 1.0125 V$ to 3.3 V                                                                                  | -2                |                   | 2                 | %     |

| CURRENT LIMIT                 |                                                        |                                                                                                                                                                |                   |                   |                   |       |

| ILIM <sub>BK</sub>            | Peak Inductor Current Limit                            | Programmed to support 1.2 A DC load                                                                                                                            | 1600              | 1900              | 2200              | mA    |

| REGULATOR                     |                                                        |                                                                                                                                                                |                   |                   |                   |       |

| F <sub>BK_SW</sub>            | Switching Frequency                                    | $\begin{array}{c} PWM,\ I_{OUT}=0\ A,\ AV_{IN}=PV_{IN}=3.8\ V,\\ V_{OUT}=1.1\ V \end{array}$                                                                   | 2.25              | 2.5               | 2.75              | MHz   |

| RDS <sub>ON BK_P</sub>        | PMOS Resistance Ball-to-Ball                           | AP <sub>VIN</sub> = V <sub>GS</sub> = 3.8 V, Temp = 25°C                                                                                                       |                   | 0.125             | 0.200             | Ω     |

| RDS <sub>ON BK_N</sub>        | NMOS Resistance Ball-to-Ball                           | AP <sub>VIN</sub> = V <sub>GS</sub> = 3.8 V, Temp = 25°C                                                                                                       |                   | 0.085             | 0.140             | Ω     |

| VO <sub>BK_RNG</sub>          | Buck Output Voltage Range                              | When V <sub>OUT</sub> + 300 mV < AV <sub>IN</sub> & PV <sub>IN</sub>                                                                                           | 0.6               | 1.1               | 3.3               | ٧     |

| BUCK OUTPUT PI                | ROTECTION                                              |                                                                                                                                                                |                   |                   |                   |       |

| OVP <sub>BK_RS</sub>          | Rising Over Voltage Output<br>Threshold                | V <sub>IN</sub> = 3.8 V, V <sub>OUT</sub> = 1.1 V,<br>V <sub>OUT</sub> = 2.85 V                                                                                | Vtarget x 1.17    | Vtarget x 1.2     | Vtarget x 1.23    | V     |

|                               |                                                        | V <sub>OUT</sub> = 0.6 V                                                                                                                                       | Vtarget x 1.15    | Vtarget x 1.2     | Vtarget<br>x 1.25 | V     |

| OVP <sub>BK_FL</sub>          | Falling Over Voltage Output<br>Threshold               | V <sub>OUT</sub> = 0.6 V to 3.300V                                                                                                                             | Vtarget<br>x 1.04 | Vtarget x 1.10    | Vtarget x 1.14    | V     |

| UVP <sub>BK_FL</sub>          | Falling Under Voltage Output<br>Threshold              | V <sub>OUT</sub> = 0.6 V                                                                                                                                       | Vtarget<br>x 0.83 | Vtarget<br>x 0.90 | Vtarget<br>x 0.97 | V     |

|                               |                                                        | V <sub>IN</sub> = 3.8 V, V <sub>OUT</sub> = 1.1 V, 2.85 V                                                                                                      | Vtarget<br>x 0.86 | Vtarget<br>x 0.90 | Vtarget<br>x 0.93 | V     |

|                               |                                                        | -                                                                                                                                                              |                   | -                 | -                 |       |

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \ (\text{continued}) \\ \textbf{Minimum and maximum values are at AV}_{IN} = PV_{IN} = 2.5 \ V \ to 5.5 \ V \ \& PV_{IN} > V_{BUCK} + 350 \ mV \ and \ PV_{IN} < V_{BST} - 250 \ mV, \ V_{IN12} = 2.5 \ V \ to 5.5 \ V \ \& V_{IN3}, \ V_{IN4} > V_{LD03/4} + 150 \ mV, \ V_{BUCK} = 0.6 \ V \ to 3.3 \ V, \ V_{BST} = 3.0 \ V \ to 5.7 \ V, \ V_{LDO1}, \ V_{LDO2}, \ V_{LDO3} \ and \ V_{LDO4} = 0.8 \ V \ to 3.3 \ V, \ T_{A} = -40^{\circ}\text{C} \ to +85^{\circ}\text{C}, \ unless otherwise noted.} \end{array}$

| Symbol                    | Parameter                                   | Conditions                                                                                                                                                                                               | Min               | Тур               | Max               | Units |

|---------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------|

| ВИСК ОИТРИТ Р             | PROTECTION                                  |                                                                                                                                                                                                          |                   |                   |                   |       |

| UVP <sub>BK_RS</sub>      | Rising Under Voltage Output<br>Threshold    | V <sub>OUT</sub> = 0.6 V to 3.3 V                                                                                                                                                                        | Vtarget<br>x 0.90 | Vtarget<br>x 0.95 | Vtarget<br>x 0.99 | V     |

| OVP <sub>BK_TMR</sub>     | Over Voltage Output Protection Timer        | V <sub>OUT Target</sub> = 2.85 V, V <sub>OUT</sub> held at 3.65 V, INTB going high trigger                                                                                                               | 32                | 40                | 56                | μs    |

| UVP <sub>BK_TMR</sub>     | Under Voltage Output Protection Timer       | V <sub>OUT Target</sub> = 2.85 V, V <sub>OUT</sub> held at 2.05 V, Time to Output Disabled                                                                                                               | 32                | 40                | 56                | μs    |

| BOOST EC                  |                                             |                                                                                                                                                                                                          |                   |                   |                   |       |

| POWER SUPPLIE             | ES .                                        |                                                                                                                                                                                                          |                   |                   |                   |       |

| IQ <sub>BST_PFM</sub>     | Quiescent Current                           | Total current on PV <sub>IN</sub> and AV <sub>IN</sub> , V <sub>OUT</sub> = 5 V when V <sub>BSTEN</sub> = AV <sub>IN</sub> , VHWEN = 0, PFM Mode, Non Switching, No Load, all other converters disabled. |                   | 32                | 44                | μΑ    |

| IQ <sub>BST PT</sub>      | IQ in Auto Pass-Thru Mode                   | Total current on $PV_{IN}$ and $AV_{IN}$ when $V_{BSTEN} = AV_{IN}$ , $VHWEN = 0$ , No Load, all other converters disabled.                                                                              |                   | 39                | 90                | μΑ    |

| IQ <sub>BST_FPT</sub>     | IQ when part is in Forced<br>Pass-Thru Mode | Total current on $PV_{IN}$ and $AV_{IN}$ when $AV_{IN} = PV_{IN} = V_{BSTEN} = 3.8 \text{ V}$ , VHWEN = 0, BST_MODE bit = 1, No Load, all other converters disabled.                                     |                   | 18                |                   | μΑ    |

| R <sub>BST_DCHG</sub>     | Output Discharge Resistance                 |                                                                                                                                                                                                          | 80                | 100               | 120               | Ω     |

| PFM ↔ PWM THI             | RESHOLDS                                    |                                                                                                                                                                                                          |                   |                   |                   |       |

| I <sub>BST_PFM</sub>      | PFM Mode I <sub>OUT</sub> Threshold         |                                                                                                                                                                                                          |                   | 100               |                   | mA    |

| I <sub>BST_PWM</sub>      | PWM Mode I <sub>OUT</sub> Threshold         |                                                                                                                                                                                                          |                   | 130               |                   | mA    |

| BOOST V <sub>OUT</sub> AC | CURACY                                      |                                                                                                                                                                                                          |                   |                   |                   |       |

| VO <sub>BST_ACC</sub>     | PFM Output Voltage Accuracy                 | V <sub>IN</sub> = 3.8 V, No Load, PFM Mode                                                                                                                                                               | -3                |                   | 3                 | %     |

|                           | PWM Output Voltage Accuracy                 | V <sub>IN</sub> = 3.8 V, No Load, PWM Mode                                                                                                                                                               | -3                |                   | 3                 | %     |

| CURRENT LIMIT             |                                             |                                                                                                                                                                                                          |                   |                   |                   |       |

| I <sub>LIMBST</sub>       | Peak Inductor Current Limit                 | Programmed to support 1 A DC load                                                                                                                                                                        | 3.0               | 3.5               | 4.0               | Α     |

| REGULATOR                 |                                             |                                                                                                                                                                                                          |                   |                   |                   |       |

| F <sub>SW_BST</sub>       | PWM Switching Frequency                     | V <sub>IN</sub> = 3.8 V                                                                                                                                                                                  | 2.25              | 2.5               | 2.75              | MHz   |

| RDS <sub>ON BST_P</sub>   | PMOS Resistance Ball-to-Ball                | Temp = 25°C                                                                                                                                                                                              |                   | 65                | 120               | mΩ    |

| RDS <sub>ON BST_N</sub>   | NMOS Resistance Ball-to-Ball                | Temp = 25°C                                                                                                                                                                                              |                   | 50                | 100               | mΩ    |

| VO <sub>BST_RNG</sub>     | Boost Output Voltage Range                  | When PV <sub>IN</sub> < V <sub>BST</sub> and 2.5 V $\leq$ PV <sub>IN</sub> /AV <sub>IN</sub> $\leq$ 5.5 V                                                                                                | 3.0               | 5.0               | 5.7               | V     |

| BOOST OUTPUT              | PROTECTION                                  |                                                                                                                                                                                                          |                   |                   |                   |       |

| OVP <sub>BST_RS</sub>     | Rising Over Voltage Output<br>Threshold     | V <sub>AVIN</sub> = 3.8 V, V <sub>OUT</sub> = 5.0 V                                                                                                                                                      | Vtarget<br>x 1.16 | Vtarget<br>x 1.2  | Vtarget x 1.22    | V     |

| OVP <sub>BST_FL</sub>     | Falling Over Voltage Output<br>Threshold    |                                                                                                                                                                                                          | Vtarget<br>x 1.07 | Vtarget<br>x 1.1  | Vtarget<br>x 1.12 | V     |

| UVP <sub>BST_FL</sub>     | Falling Under Voltage Output<br>Threshold   | V <sub>AVIN</sub> = 3.8 V, V <sub>OUT</sub> = 5.0 V                                                                                                                                                      | Vtarget<br>x 0.78 | Vtarget<br>x 0.80 | Vtarget<br>x 0.82 | V     |

| UVP <sub>BST_RS</sub>     | Rising Under Voltage Output<br>Threshold    |                                                                                                                                                                                                          | Vtarget<br>x 0.88 | Vtarget<br>x 0.90 | Vtarget<br>x 0.93 | ٧     |

| OVP <sub>BST_TMR</sub>    | Over Voltage Output Protection Timer        | V <sub>OUT_Target</sub> = 5.0 V, V <sub>OUT</sub> held at 6.25 V, INTB going high trigger                                                                                                                | 32                | 40                | 56                | μs    |

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \ (\text{continued}) \\ \textbf{Minimum and maximum values are at AV}_{IN} = PV_{IN} = 2.5 \ V \ to 5.5 \ V \ \& PV_{IN} > V_{BUCK} + 350 \ mV \ and \ PV_{IN} < V_{BST} - 250 \ mV, \ V_{IN12} = 2.5 \ V \ to 5.5 \ V \ \& V_{IN3}, \ V_{IN4} > V_{LD03/4} + 150 \ mV, \ V_{BUCK} = 0.6 \ V \ to 3.3 \ V, \ V_{BST} = 3.0 \ V \ to 5.7 \ V, \ V_{LDO1}, \ V_{LDO2}, \ V_{LDO3} \ and \ V_{LDO4} = 0.8 \ V \ to 3.3 \ V, \ T_{A} = -40^{\circ}\text{C} \ to +85^{\circ}\text{C}, \ unless otherwise noted.} \end{array}$

| Symbol                 | Parameter                                 | Conditions                                                                                                                                                                                                                                | Min               | Тур              | Max               | Units |

|------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|-------------------|-------|

| BOOST OUTPUT           | PROTECTION                                |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| UVP <sub>BST_TMR</sub> | Under Voltage Output Protection Timer     | V <sub>OUT Target</sub> = 5.0 V, V <sub>OUT</sub> held at 4.00 V,<br>Time to Output Disabled                                                                                                                                              | 32                | 40               | 56                | μs    |

| _DO1/2 EC SPEC         | CS .                                      |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| QUIESCENT CUI          | RRENT                                     |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| IQ <sub>L12</sub>      | Quiescent Current, No Load                | $I_{OUT}$ = 0 A, Combined Current Measured at AV <sub>IN</sub> and V <sub>IN12</sub> when LDO1 is enabled only or LDO2 is enabled only, Buck and Boost are disabled, VHWEN = AV <sub>IN</sub>                                             |                   | 40               | 55                | μΑ    |

| VO <sub>L12_RNG</sub>  | LDO Output Voltage Range                  | When $V_{OUT}$ + 300 mV < $V_{IN12}$ and 2.5 V $\leq$ $V_{IN12} \leq$ 5.5 V                                                                                                                                                               | 0.8               | 2.8              | 3.3               | V     |

| VO <sub>L12_ACC</sub>  | Output Voltage Accuracy                   | $I_{OUT}$ = 300 mA, $AV_{IN}$ = $V_{IN12}$ = 3.8 V, $V_{OUT}$ = 0.8 V to 3.3 V                                                                                                                                                            | -2.0              |                  | +2.0              | %     |

| V <sub>L12_DO</sub>    | Dropout Voltage                           | V <sub>OUT</sub> = V <sub>OUT_TARGET</sub> - 100 mV, I <sub>OUT</sub> = 300 mA, V <sub>OUT_TARGET</sub> = 2.8 V                                                                                                                           |                   |                  | 250               | mV    |

| IO <sub>MAX_L12</sub>  | Max load current                          | $V_{OUT}$ + 0.3 V < $V_{IN12}$ and $V_{IN12}$ = 2.5 V to 4.5 V                                                                                                                                                                            | 300               |                  |                   | mA    |

| CURRENT LIMIT          |                                           |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| I <sub>LIM_L12</sub>   | Current Limit                             | $V_{OUT}$ + 500 mV < $V_{IN12}$ and 2.5 V $\leq$ $V_{IN12} \leq$ 4.5 V                                                                                                                                                                    | 150               | 180              | 210               | mA    |

|                        |                                           | $V_{OUT}$ + 500 mV < $V_{IN12}$ and 2.5 V $\leq$ $V_{IN12} \leq$ 4.5 V                                                                                                                                                                    | 360               | 420              | 480               | mA    |

| OUTPUT PROTE           | CTION                                     |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| OVP <sub>L12_RS</sub>  | Rising Over Voltage Output<br>Threshold   | $V_{AVIN} = V_{IN1/2} = 3.8 \text{ V}, V_{OUT} = 2.8 \text{ V}$                                                                                                                                                                           | Vtarget x 1.17    | Vtarget x 1.2    | Vtarget x 1.23    | V     |

| OVP <sub>L12_FL</sub>  | Falling Over Voltage Output<br>Threshold  | V <sub>AVIN</sub> = V <sub>IN1/2</sub> = 3.8 V, V <sub>OUT</sub> = 2.8 V                                                                                                                                                                  | Vtarget<br>x 1.07 | Vtarget<br>x 1.1 | Vtarget x 1.12    | V     |

| UVP <sub>L12_FL</sub>  | Falling Under Voltage Output<br>Threshold | V <sub>AVIN</sub> = V <sub>IN1/2</sub> = 3.8 V, V <sub>OUT</sub> = 2.8 V                                                                                                                                                                  | Vtarget<br>x 0.77 | Vtarget<br>x 0.8 | Vtarget<br>x 0.82 | V     |

| UVP <sub>L12_HS</sub>  | Rising Under Voltage Output<br>Threshold  | $V_{AVIN} = V_{IN1/2} = 3.8 \text{ V}, V_{OUT} = 2.8 \text{ V}$                                                                                                                                                                           | Vtarget<br>x 0.88 | Vtarget<br>x 0.9 | Vtarget<br>x 0.93 | V     |

| OVP <sub>L12_TMR</sub> | Over Voltage Output Protection Timer      | V <sub>OUT_Target</sub> = 2.8 V, V <sub>OUT</sub> held at 3.5 V, INTB going high trigger                                                                                                                                                  | 32                | 40               | 56                | μs    |

| UVP <sub>L12_TMR</sub> | Under Voltage Output Protection Timer     | V <sub>OUT Target</sub> = 2.8 V, V <sub>OUT</sub> held at 1.8 V,<br>Time to Output Disabled                                                                                                                                               | 32                | 40               | 56                | μs    |

| R <sub>L12_DCHG</sub>  | Output Discharge Resistance               |                                                                                                                                                                                                                                           | 80                | 100              | 120               | Ω     |

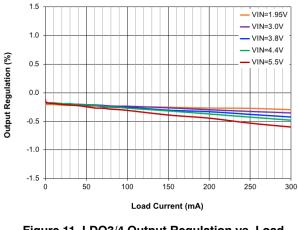

| _DO3/4 EC SPEC         | cs                                        |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| QUIESCENT CUI          | RRENT                                     |                                                                                                                                                                                                                                           |                   |                  |                   |       |

| IQ <sub>L34</sub>      | Quiescent Current, No Load                | $I_{OUT}$ = 0 A, Combined Current Measured at AV <sub>IN</sub> and V <sub>IN3</sub> when LDO3 is enabled or AV <sub>IN</sub> and V <sub>IN4</sub> when LDO4 is enabled. LDO1, LDO2, Buck and Boost are disabled, VHWEN = AV <sub>IN</sub> |                   | 38               | 50                | μΑ    |

| VO <sub>L34_RNG</sub>  | LDO3/4 Output Voltage Range               | $ \begin{array}{l} LDO3: \ V_{OUT} + 0.15 < V_{IN3} \ and \ V_{IN3} = 1.95 \\ V \ to \ 4.5 \ V, \ LDO4: \ V_{OUT} + 150 \ mV < V_{IN4} \\ and \ V_{IN4} = 1.95 \ V \ to \ 4.5 \ V \\ \end{array} $                                        | 0.8               | 1.8              | 3.3               | V     |

| VO <sub>L34_ACC</sub>  | Output Voltage Accuracy                   | I <sub>OUT</sub> = 300 mA, AV <sub>IN</sub> = 3.8 V, V <sub>IN3/4</sub> = 3.8                                                                                                                                                             | -2.5              |                  | +2.0              | %     |

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \ (\text{continued}) \\ \text{Minimum and maximum values are at AV}_{IN} = PV_{IN} = 2.5 \ V \ to 5.5 \ V \ \& PV_{IN} > V_{BUCK} + 350 \ \text{mV} \ \text{and} \ PV_{IN} < V_{BST} - 250 \ \text{mV}, V_{IN12} = 2.5 \ V \ \text{to} 5.5 \ V \ \& V_{IN3}, V_{IN4} > V_{LD03/4} + 150 \ \text{mV}, V_{BUCK} = 0.6 \ V \ \text{to} 3.3 \ V, V_{BST} = 3.0 \ V \ \text{to} 5.7 \ V, V_{LDO1}, V_{LDO2}, V_{LDO3} \ \text{and} \ V_{LDO4} = 0.8 \ V \ \text{to} 3.3 \ V, T_{A} = -40^{\circ}\text{C} \ \text{to} +85^{\circ}\text{C}, \text{unless otherwise noted}. \\ \textbf{Typical values are at T}_{A} = 25^{\circ}\text{C}, \ \text{AV}_{IN}, \ \text{PV}_{IN}, V_{IN12} = 3.8 \ \text{V}, V_{IN3}, V_{IN4} = 1.95 \ \text{V}, V_{BUCK} = 1.1 \ \text{V}, V_{BST} = 5.0 \ \text{V}, V_{LDO1} \ \text{and} \ V_{LDO2} = 2.8 \ \text{V}, V_{LDO3} \ \text{and} \ V_{LDO4} = 1.8 \ \text{V}. \\ \end{array}$

| Symbol                 | Parameter                                 | Conditions                                                                                                                                                                                                                                              | Min               | Тур               | Max               | Units |

|------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------|

| QUIESCENT CUF          | RRENT                                     |                                                                                                                                                                                                                                                         |                   | •                 |                   |       |

| V <sub>L34_DO</sub>    | Dropout Voltage                           | V <sub>OUT</sub> = V <sub>OUT</sub> TARGET - 100 mV, I <sub>OUT</sub> = 300 mA, V <sub>OUT</sub> TARGET = 1.8 V                                                                                                                                         |                   |                   | 150               | mV    |

| IO <sub>MAX_L34</sub>  | Max load current                          | $\begin{aligned} &V_{OUT} + 150 \text{ mV} < V_{IN3} \text{ and } V_{IN3} = 1.95 \text{ V} \\ &to 4.5 \text{ V}, \text{LDO4: } V_{OUT} + 150 \text{ mV} < V_{IN4} \\ &to 4.5 \text{ V}, \text{LDO4: } V_{OUT} + 150 \text{ mV} < V_{IN4} \end{aligned}$ | 300               |                   |                   | mA    |

| CURRENT LIMIT          |                                           |                                                                                                                                                                                                                                                         |                   |                   |                   |       |

| I <sub>LIM_L34</sub>   | Current Limit                             | $\begin{array}{l} V_{OUT} + 500 \text{ mV} < V_{IN3} \text{ and } V_{IN3} = 1.95 \text{ V} \\ \text{to 4.5 V, LDO4: } V_{OUT} + 500 \text{ mV} < V_{IN4} \\ \text{and } V_{IN4} = 1.95 \text{ V to 4.5 V} \end{array}$                                  | 150               | 180               | 210               | mA    |

|                        |                                           | $\begin{aligned} &V_{OUT} + 500 \text{ mV} < V_{IN3} \text{ and } V_{IN3} = 1.95 \text{ V} \\ &to 4.5 \text{ V}, \text{LDO4: } V_{OUT} + 500 \text{ mV} < V_{IN4} \\ &to 4.5 \text{ V}, \text{LDO4: } V_{OUT} + 500 \text{ mV} < V_{IN4} \end{aligned}$ | 360               | 420               | 480               | mA    |

| R <sub>L34_DCHG</sub>  | Output Discharge Resistance               |                                                                                                                                                                                                                                                         | 80                | 100               | 120               | Ω     |

| OUTPUT PROTE           | CTION                                     |                                                                                                                                                                                                                                                         |                   |                   |                   |       |

| OVP <sub>L34_RS</sub>  | Rising Over Voltage Output<br>Threshold   | V <sub>AVIN</sub> = 3.8 V, V <sub>IN3/4</sub> = 1.95V, V <sub>OUT</sub> = 1.8 V                                                                                                                                                                         | Vtarget x 1.17    | Vtarget x 1.2     | Vtarget x 1.23    | V     |

| OVP <sub>L34_FL</sub>  | Falling Over Voltage Output<br>Threshold  | V <sub>AVIN</sub> = 3.8 V, V <sub>IN3/4</sub> = 1.95V, V <sub>OUT</sub> = 1.8 V                                                                                                                                                                         | Vtarget x 1.07    | Vtarget x 1.1     | Vtarget x 1.12    | V     |

| UVP <sub>L34_FL</sub>  | Falling Under Voltage Output<br>Threshold | V <sub>AVIN</sub> = 3.8 V, V <sub>IN3/4</sub> = 1.95V, V <sub>OUT</sub> = 1.8 V                                                                                                                                                                         | Vtarget x 0.77    | Vtarget<br>x 0.80 | Vtarget<br>x 0.82 | V     |

| UVP <sub>L34_RS</sub>  | Rising Under Voltage Output<br>Threshold  | V <sub>AVIN</sub> = 3.8 V, V <sub>IN3/4</sub> = 1.95V, V <sub>OUT</sub> = 1.8 V                                                                                                                                                                         | Vtarget<br>x 0.88 | Vtarget<br>x 0.90 | Vtarget<br>x 0.93 | V     |

| OVP <sub>L34_TMR</sub> | Over Voltage Output Protection Timer      | V <sub>OUT_Target</sub> = 1.8 V, V <sub>OUT</sub> held at 2.25 V, INTB going high trigger                                                                                                                                                               | 32                | 40                | 56                | μs    |

| UVP <sub>L34_TMR</sub> | Under Voltage Output Protection Timer     | V <sub>OUT Target</sub> = 1.8 V, V <sub>OUT</sub> held at 1.35 V,<br>Time to Output Disabled                                                                                                                                                            | 32                | 40                | 56                | μS    |

| I/O LEVELS             |                                           |                                                                                                                                                                                                                                                         |                   |                   |                   |       |

| V <sub>IL</sub>        | HWEN Logic Low threshold                  |                                                                                                                                                                                                                                                         |                   |                   | 0.35              | V     |

| V <sub>IH</sub>        | HWEN Logic High threshold                 |                                                                                                                                                                                                                                                         | 1.2               |                   | V <sub>IN</sub>   | ٧     |

| $V_{IL}$               | BSTEN Logic Low threshold                 |                                                                                                                                                                                                                                                         |                   |                   | 0.25              | V     |

| $V_{IH}$               | BSTEN Logic High threshold                | AV <sub>IN</sub> = 4.5 V;                                                                                                                                                                                                                               | 1.05              |                   | V <sub>IN</sub>   | V     |

| $R_{PD}$               | HWEN and BSTEN Input<br>Resistance        | V <sub>IN</sub> = High or Low                                                                                                                                                                                                                           | 1                 | 4.4               |                   | МΩ    |

| V <sub>OL_INTB</sub>   | INTB                                      | Isink = 5 mA                                                                                                                                                                                                                                            |                   |                   | 0.3               | ٧     |

| I <sub>INTB</sub>      |                                           | V <sub>INTB</sub> = 5.5 V                                                                                                                                                                                                                               |                   |                   | 0.5               | μΑ    |

$\begin{array}{l} \textbf{Table 6. ELECTRICAL CHARACTERISTICS} \ (\text{continued}) \\ \text{Minimum and maximum values are at AV}_{IN} = PV_{IN} = 2.5 \ V \ to 5.5 \ V \ \& PV_{IN} > V_{BUCK} + 350 \ \text{mV} \ \text{and} \ PV_{IN} < V_{BST} - 250 \ \text{mV}, V_{IN12} = 2.5 \ V \ \text{to} 5.5 \ V \ \& V_{IN3}, V_{IN4} > V_{LD03/4} + 150 \ \text{mV}, V_{BUCK} = 0.6 \ V \ \text{to} 3.3 \ V, V_{BST} = 3.0 \ V \ \text{to} 5.7 \ V, V_{LDO1}, V_{LDO2}, V_{LDO3} \ \text{and} \ V_{LDO4} = 0.8 \ V \ \text{to} 3.3 \ V, T_{A} = -40^{\circ}\text{C} \ \text{to} +85^{\circ}\text{C}, \text{unless otherwise noted}. \\ \textbf{Typical values are at T}_{A} = 25^{\circ}\text{C}, \ \text{AV}_{IN}, \ \text{PV}_{IN}, V_{IN12} = 3.8 \ \text{V}, V_{IN3}, V_{IN4} = 1.95 \ \text{V}, V_{BUCK} = 1.1 \ \text{V}, V_{BST} = 5.0 \ \text{V}, V_{LDO1} \ \text{and} \ V_{LDO2} = 2.8 \ \text{V}, V_{LDO3} \ \text{and} \ V_{LDO4} = 1.8 \ \text{V}. \\ \end{array}$

| Symbol                 | Parameter                                       | Conditions                                                                                                                                                                                                                                    | Min  | Тур | Max  | Units |

|------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Q CONDITIONS           |                                                 |                                                                                                                                                                                                                                               |      |     |      |       |

| I <sub>Q AVIN</sub> SD | Shutdown Supply Current                         | Total current on AV <sub>IN</sub> when AV <sub>IN</sub> = 5.0 V and all xxx_EN bits = 0, xxx_SEQ bits = 000, HWEN = BSTEN = SDA = SCL = Low                                                                                                   |      |     | 5    | μΑ    |

| I <sub>Q PVIN</sub> SD |                                                 | Total current on $PV_{IN}$ when $PV_{IN} = 5.0 \text{ V}$ and all xxx_EN bits = 0, xxx_SEQ bits =000, HWEN = BSTEN = $S\overline{D}A$ = $SCL$ = Low                                                                                           |      |     | 1.5  | μΑ    |

| IQ VIN12_SD            |                                                 | Total current on V <sub>IN12</sub> when V <sub>IN12</sub> = 5.0 V and all xxx_EN bits = 0, xxx_SEQ bits = 000, HWEN = BSTEN = SDA = SCL = Low                                                                                                 |      |     | 1.5  | μΑ    |

| I <sub>Q VIN3_SD</sub> |                                                 | Total current on V <sub>IN3</sub> when V <sub>IN3</sub> = 5.0 V and all xxx_EN bits = 0, xxx_SEQ bits = 000, HWEN = BSTEN = SDA = SCL = Low                                                                                                   |      |     | 1.5  | μΑ    |

| I <sub>Q VIN4_SD</sub> |                                                 | Total current on V <sub>IN4</sub> when V <sub>IN4</sub> = 5.0 V and all xxx_EN bits = 0, xxx_SEQ bits = 000, HWEN = BSTEN = SDA = SCL = Low                                                                                                   |      |     | 1.5  | μΑ    |

| I <sub>Q_STBY</sub>    | Standby Supply Current                          | Total current on $PV_{IN}$ , $AV_{IN}$ , $V_{IN12}$ , $V_{IN3}$ and $V_{IN4}$ when = 5.0 V and all xxx_EN bits = 1 (Except BST_EN), xxx_SEQ bits =000, $AV_{IN}$ = $PV_{IN}$ = VHWEN = $V_{BSTEN}$ . LDO1-4 on, Buck on, Boost on             |      | 165 | 190  | μΑ    |

| Islp                   | Sleep Supply Current                            | Total current on $PV_{IN}$ , $AV_{IN}$ , $V_{IN12}$ , $V_{IN3}$ and $V_{IN4}$ when = 5.0 V and all xxx EN bits = 0, xxx SEQ bits =000, $AV_{IN} = P\overline{V}_{IN} = VHWEN$ , BSTEN = Low. LDO1-4 off, Buck off, Boost off, No I2C activity |      | 12  | 20   | μΑ    |

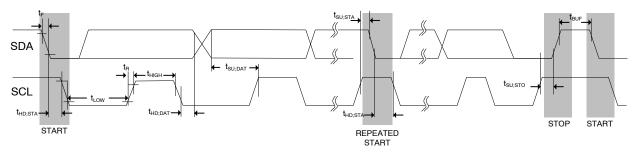

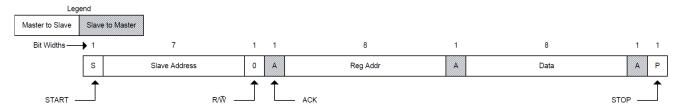

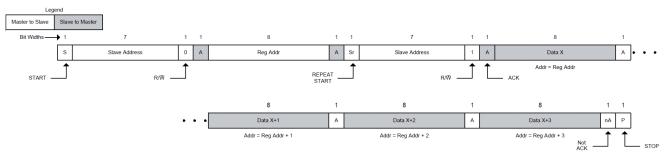

| C Timing and F         | Performance <sup>†</sup>                        |                                                                                                                                                                                                                                               |      |     |      |       |

| $V_{IL}$               | SDA and SCL Logic Low threshold                 |                                                                                                                                                                                                                                               | -0.5 |     | 0.4  | V     |

| V <sub>IH</sub>        | SDA and SCL Logic High threshold                |                                                                                                                                                                                                                                               | 1.2  |     | 5.5  | V     |

| $V_{OL}$               | SDA Logic Low Output                            | 3 mA Sink                                                                                                                                                                                                                                     |      |     | 0.4  | V     |

| I <sub>OL</sub>        | SDA Sink Current                                |                                                                                                                                                                                                                                               | 20   |     |      | mA    |

| fSCL                   | SCL Clock Frequency                             | Fast Mode Plus                                                                                                                                                                                                                                |      |     | 1000 | kHz   |

| tBUF                   | Bus-Free Time Between STOP and START Conditions | Fast Mode Plus                                                                                                                                                                                                                                | 0.5  |     |      | μs    |

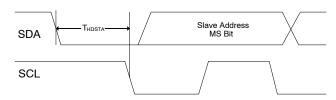

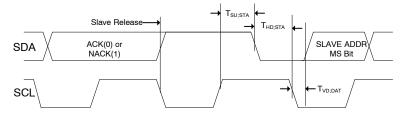

| tHD;STA                | START or Repeated START<br>Hold Time            | Fast Mode Plus                                                                                                                                                                                                                                | 260  |     |      | ns    |

| tLOW                   | SCL LOW Period                                  | Fast Mode Plus                                                                                                                                                                                                                                | 0.5  |     |      | μs    |

| tHIGH                  | SCL HIGH Period                                 | Fast Mode-Plus                                                                                                                                                                                                                                | 260  |     |      | ns    |

| tSU;STA                | Repeated START Setup Time                       | Fast Mode-Plus                                                                                                                                                                                                                                | 260  |     |      | ns    |

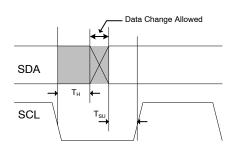

| tHD;DAT                | Data Hold Time                                  | Fast Mode Plus                                                                                                                                                                                                                                | 0    |     |      | ns    |

| tSU;DAT                | Data Setup Time                                 | Fast Mode Plus                                                                                                                                                                                                                                | 50   |     |      | ns    |

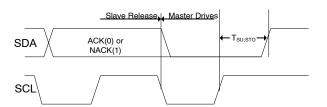

| tVD;DAT                | Data Valid Time                                 | Fast Mode Plus                                                                                                                                                                                                                                |      |     | 450  | ns    |

| tVD;ACK                | Data Valid Acknowledge Time                     | Fast Mode Plus                                                                                                                                                                                                                                |      |     | 450  | ns    |

#### Table 6. ELECTRICAL CHARACTERISTICS (continued)

Minimum and maximum values are at AV<sub>IN</sub> = PV<sub>IN</sub> = 2.5 V to 5.5 V & PV<sub>IN</sub> > V<sub>BUCK</sub> + 350 mV and PV<sub>IN</sub> < V<sub>BST</sub> - 250 mV, V<sub>IN12</sub> = 2.5 V to 5.5 V & V<sub>IN3</sub>, V<sub>IN4</sub> + 150 mV, V<sub>BUCK</sub> = 0.6 V to 3.3 V, V<sub>BST</sub> = 3.0 V to 5.7 V, V<sub>LDO1</sub>, V<sub>LDO2</sub>, V<sub>LDO3</sub> and V<sub>LDO4</sub> = 0.8 V to 3.3 V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C, AV<sub>IN</sub>, PV<sub>IN</sub>, V<sub>IN12</sub> = 3.8 V, V<sub>IN3</sub>, V<sub>IN4</sub> = 1.95 V, V<sub>BUCK</sub> = 1.1 V, V<sub>BST</sub> = 5.0 V, V<sub>LDO1</sub> and V<sub>LDO2</sub> = 2.8 V, V<sub>LDO3</sub> and V<sub>LDO4</sub> = 1.8 V.

| Symbol                         | Parameter                                                      | Conditions                  | Min  | Тур | Max | Units |

|--------------------------------|----------------------------------------------------------------|-----------------------------|------|-----|-----|-------|

| I <sup>2</sup> C Timing and Pe | erformance <sup>†</sup>                                        |                             |      |     |     |       |

| tR                             | SDA and SCL Rise Time                                          | Fast Mode Plus              |      |     | 120 | ns    |

| tF                             | SDA and SCL Fall Time                                          | Fast Mode Plus, VDD = 1.8 V | 6.55 |     | 120 | ns    |

| tSU;STO                        | Stop Condition Setup Time                                      | Fast Mode Plus              | 260  |     |     | ns    |

| Ci                             | SDA and SCL Input Capacitance                                  |                             |      |     | 10  | pF    |

| Cb                             | Capacitive Load for SDA and SCL                                |                             |      |     | 550 | pF    |

| t <sub>SP</sub>                | Pulse width of spikes which must be suppressed by input filter | SCL, SDA only               | 0    |     | 50  | ns    |

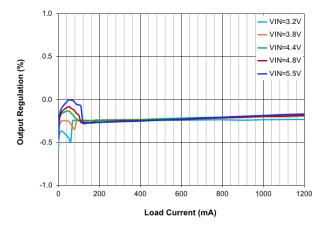

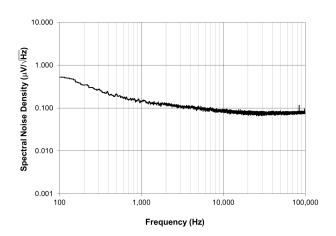

NOTES:Refer to Typical Characteristics waveforms/graphs for closed loop data and variation with input supply and temperature. Electrical specifications reflects open loop steady state data. System specifications reflects both steady state and dynamic close loop data associated with the recommended external components.

#### Guarantee Levels:

#### **Table 7. SYSTEM CHARACTERISTICS**

System Specifications are guaranteed by design and are not production tested. They reflect closed loop performance using the Recommended Layout and External Components. Minimum and Maximum values are at AV $_{\rm IN}$  = PV $_{\rm IN}$  = 2.5 V to 5.5 V & PV $_{\rm IN}$  > V $_{\rm BUCK}$  + 350 mV and PV $_{\rm IN}$  < V $_{\rm BST}$  - 250 mV, V $_{\rm IN12}$  = 2.5 V to 5.5 V & V $_{\rm IN}$  > V $_{\rm LD01/2}$  + 300 mV, V $_{\rm IN3}$ , V $_{\rm IN4}$  = 1.95 V to 5.5 V & V $_{\rm IN3}$ , V $_{\rm IN4}$  > V $_{\rm LD03/4}$  + 150 mV, V $_{\rm BUCK}$  = 0.6 V to 3.3 V, V $_{\rm BST}$  = 3.0 V to 5.7 V, V $_{\rm LD01}$ , V $_{\rm LD02}$ , V $_{\rm LD03}$  and V $_{\rm LD04}$  = 0.8 V to 3.3 V, T $_{\rm A}$  = -40°C to 85°C, unless otherwise noted. Typical values are at T $_{\rm A}$  = 25°C, AV $_{\rm IN}$  = PV $_{\rm IN}$  = V $_{\rm IN12}$  = 3.8 V, V $_{\rm IN3}$  = V $_{\rm IN4}$  = 1.95 V, V $_{\rm BUCK}$  = 1.1 V, V $_{\rm BST}$  = 5.0 V, V $_{\rm LD01}$  = V $_{\rm LD02}$  = 2.8 V, V $_{\rm LD03}$  = V $_{\rm LD04}$  = 1.8 V.

| Symbol                  | Parameter            | Conditions                                                                                                                                     | Min  | Тур | Max | Units |

|-------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------|

| SOFT START              |                      |                                                                                                                                                |      |     |     |       |

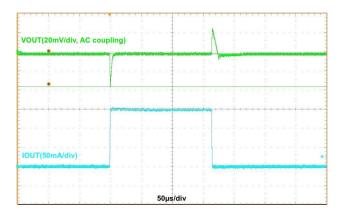

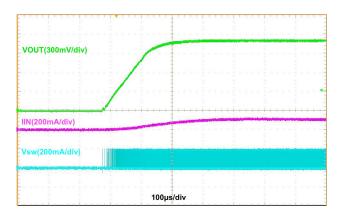

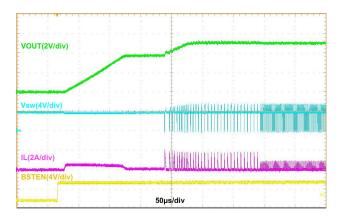

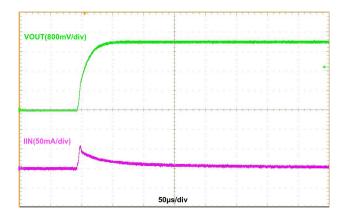

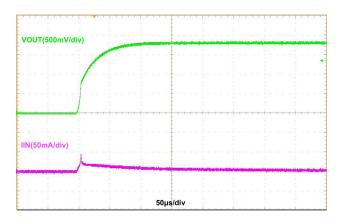

| T <sub>SS BK</sub>      | Soft-Start           | Time from enabling to 95% of $V_{OUT}$ Target of 1.1 V, $I_{OUT}$ = 300 mA and 1.2 A, Auto Mode, $C_{OUT}$ = 10 uF, $PV_{IN}$ = 3.0 V to 4.4 V |      | 300 | 480 | μs    |

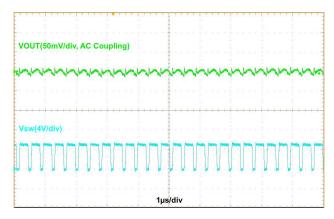

| RIPPLE                  |                      |                                                                                                                                                |      |     |     |       |

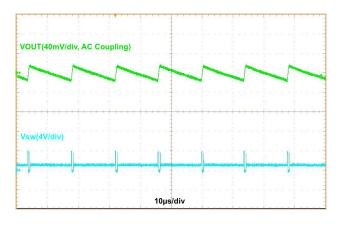

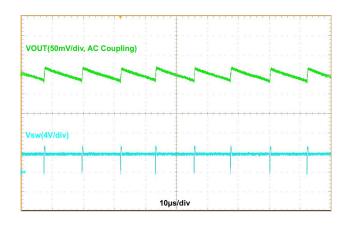

| V <sub>BK PFM_RPL</sub> | Output Ripple        | I <sub>OUT</sub> = 20 mA, PFM Mode                                                                                                             |      | 30  | 40  | mV    |

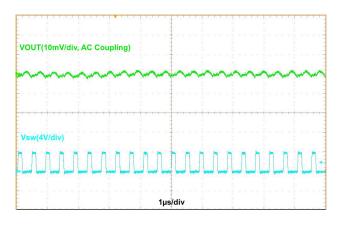

| V <sub>BK PWM_RPL</sub> |                      | I <sub>OUT</sub> = 200 mA, PWM Mode                                                                                                            |      |     | 10  | mV    |

| REGULATION & T          | TRANSIENT            |                                                                                                                                                |      |     |     |       |

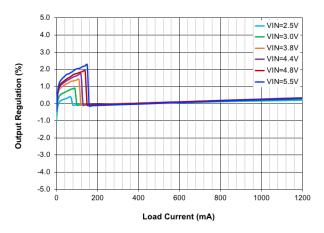

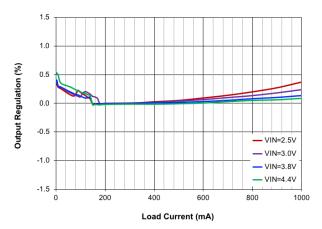

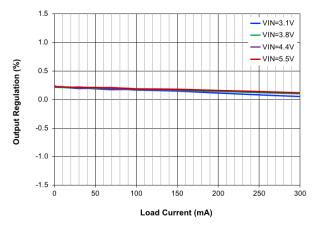

| REG <sub>BK_LOAD</sub>  | Load Regulation      | I <sub>OUT</sub> = 1 mA to 1200 mA, PWM Mode                                                                                                   | -1.5 |     | 1.5 | %     |

| REG <sub>BK_LINE</sub>  | Line Regulation      | $V_{\mbox{\footnotesize{IN}}}$ = 3.0 V to 4.4 V , $I_{\mbox{\footnotesize{OUT}}}$ = 50 mA, 300 mA, and 1200 mA, PWM Mode                       | -0.5 |     | 0.5 | %     |

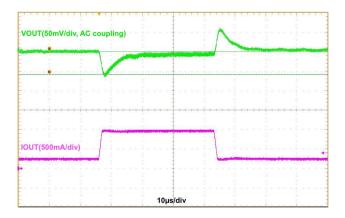

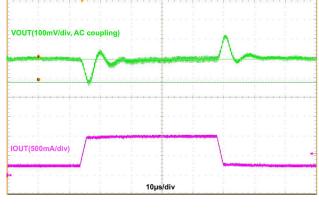

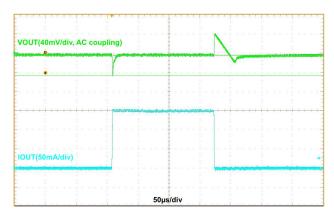

| V <sub>BK TR_LD</sub>   | Load Transient       | $I_{OUT}$ = 240 mA <-> 960 mA, $T_R$ = $T_F$ = 1 us, $V_{OUT}$ = 1.1 V, $PV_{IN}$ = 3.8 V, Auto Mode, Trecovery < 10 us                        |      |     | ±70 | mV    |

| I <sub>OUT</sub> MAX    |                      |                                                                                                                                                |      |     |     |       |

| IO <sub>MAX_BK</sub>    | I <sub>OUT</sub> Max |                                                                                                                                                | 1200 |     |     | mA    |

<sup>&</sup>lt;sup>†</sup> - Guaranteed by Design Only. Not Characterized or Production Tested.

### Table 7. SYSTEM CHARACTERISTICS (continued)