**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# Multi-Mode Buck Converter with LDO Assist for GSM / EDGE, 3 G/3.5 G and 4 G PAs

#### Description

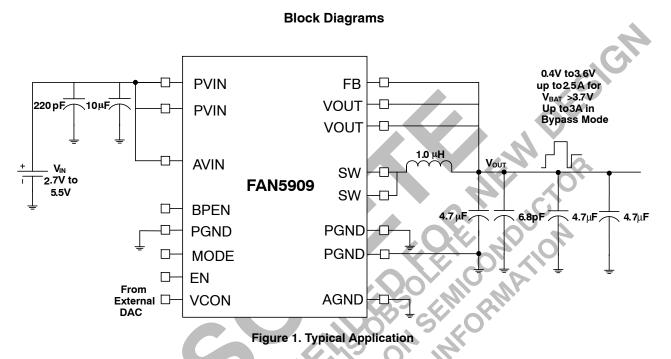

The FAN5909 is a high–efficiency, low–noise, synchronous, step–down, DC–DC converter optimized for powering Radio Frequency (RF) Power Amplifiers (PAs) in handsets and other mobile applications. Load currents up to 2.5 A are allowed, which enables GSM / EDGE, 3 G/3.5 G, and 4G platforms under very poor VSWR conditions.

The output voltage may be dynamically adjusted from 0.40 V to 3.60 V, proportional to an analog input voltage  $V_{CON}$  ranging from 0.16 V to 1.44 V, optimizing power-added efficiency. Fast transition times of less than 6  $\mu$ s are achieved, allowing excellent inter-slot settling.

An integrated LDO is automatically enabled under heavy load conditions or when the battery voltage and voltage drop across the DC-DC PMOS device are within a set range of the desired output voltage. This LDO-assist feature supports heavy load currents under the most stringent battery and V<sub>SWR</sub> conditions while maintaining high efficiency, low dropout, and superior spectral performance.

The FAN5909 DC–DC operates in PWM Mode with a 2.9 MHz switching frequency and supports a single, small form–factor inductor ranging from 1.0  $\mu$ H to 2.2  $\mu$ H. In addition, PFM operation is allowed at low load currents for output voltages below 1.5 V to maximize efficiency. PFM operation can be disabled by setting MODE pin to LOW.

When output regulation is not required, the FAN5909 may be placed in Sleep Mode by setting  $V_{CON}$  below 100 mV nominally. This ensures a very low I<sub>Q</sub> (<50 µA) while enabling a fast return to output regulation.

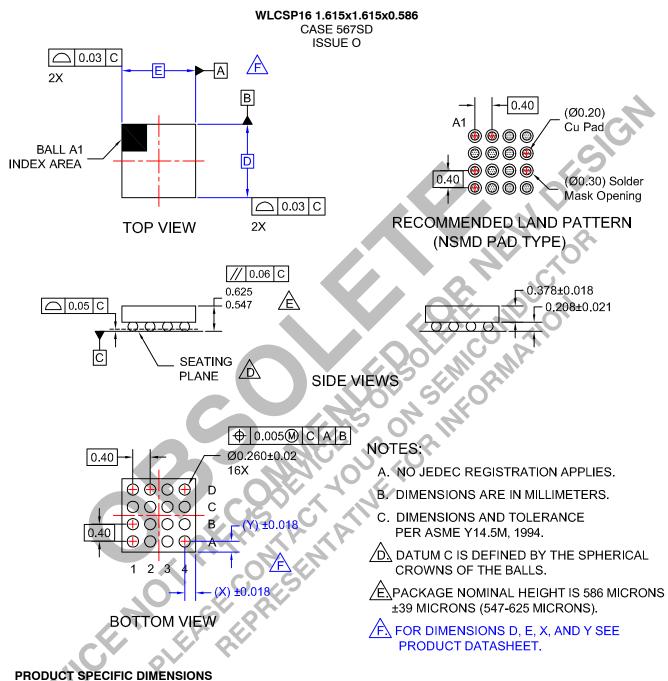

FAN5909 is available in a low profile, small form factor, 16 bump, Wafer–Level Chip–Scale Package (WLCSP) that is 1.615 mm x 1.615 mm. Only three external components are required: two 0402 capacitors and one 2016 inductor.

#### Features

- Solution Size < 9.52 mm<sup>2</sup>

- 2.7 V to 5.5 V Input Voltage Range

- V<sub>OUT</sub> Range from 0.40 V to 3.60 V (or V<sub>IN</sub>)

- Single, Small Form–Factor Inductor

- 29 mΩ Integrated LDO

- 100% Duty Cycle for Low-Dropout Operation

- Input Under-Voltage Lockout / Thermal Shutdown

- 1.615 mm x 1.615 mm, 16–Bump, 0.4 mm Pitch WLCSP

- 2.9 MHz PWM Mode

- 6 µs Output Voltage Step Response for early Tx

- Power–Loop Settling with 14 µF Load Capacitance

- Sleep Mode for ~50 μA Standby Current Consumption

- Forced PWM Mode

- Up to 95% Efficient Synchronous Operation in High Power Conditions

- ◆ 2.9 MHz PWM-Only Mode

- Auto PFM/PWM Mode

- 2.9 MHz PWM Operation at High Power and PFM Operation at Low Power and Low Output Voltage for Maximum Low Current Efficiency

#### Applications

- Dynamic Supply Bias for Polar or Linear GSM / EDGE PAs and 3 G/3.5 G and 4 G PAs

- Dynamic Supply Bias for GSM / EDGE Quad Band Amplifiers for Mobile Handsets and Data Cards

#### **ORDERING INFORMATION**

| Part Number | Output Voltage | Temperature Range | Package Pack                                                                         |               |

|-------------|----------------|-------------------|--------------------------------------------------------------------------------------|---------------|

| FAN5909UCX  | 0.4 V to PVIN  | –40°C to +85°C    | 1.615 mm x 1.615 mm, 16–Bump 0.4 mm Pitch,<br>Wafer–Level Chip–Scale Package (WLCSP) | Tape and Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

1. The three 4.7  $\mu\text{F}$  capacitors include the FAN5909 output capacitor and PA bypass capacitors.

2. Regulator requires only one 4.7 µF; the V<sub>OUT</sub> bus should not exceed 14 µF capacitance over DC bias and temperature.

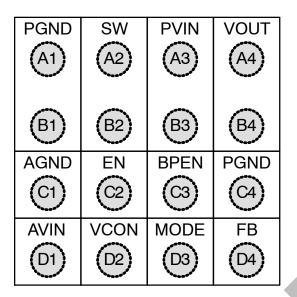

#### **Pin Configuration**

Figure 3. Bumps Face Down – Top–Through View

Figure 4. Bumps Face Up

#### **PIN DEFINITIONS**

| Pin #     | Name | Description                                                                                                                                                                                                                                 |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C1        | AGND | Analog ground, reference ground for the IC. Follow PCB routing notes for connecting this pin.                                                                                                                                               |

| A4, B4    | VOUT | Output voltage sense pin. Connect to V <sub>OUT</sub> to establish feedback path for regulation point. Connect together on PCB.                                                                                                             |

| D4        | FB   | Feedback pin. Connect to positive (+) pad of C <sub>OUT</sub> on V <sub>OUT.</sub>                                                                                                                                                          |

| C2        | EN   | Enables switching when HIGH; Shutdown Mode when LOW. This pin should not be left floating.                                                                                                                                                  |

| D2        | VCON | Analog control pin. Shield signal routing against noise.                                                                                                                                                                                    |

| D1        | AVIN | Analog supply voltage input. Connect to PVIN.                                                                                                                                                                                               |

| C3        | BPEN | Force Bypass Mode when HIGH; Auto Bypass Mode when LOW. This pin should not be left floating.                                                                                                                                               |

| D3        | MODE | When MODE is HIGH, the DC-DC permits PFM operation under low load currents and PWM operation<br>under heavy load currents. When MODE pin is set LOW, the DC-DC operates in forced PWM opera-<br>tion. This pin should not be left floating. |

| A3, B3    | PVIN | Supply voltage input to the internal MOSFET switches. Connect to input power source.                                                                                                                                                        |

| A2, B2    | SW   | Switching node of the internal MOSFET switches. Connect to output inductor.                                                                                                                                                                 |

| A1, B1,C4 | PGND | Power ground of the internal MOSFET switches. Follow routing notes for connections between PGND and AGND.                                                                                                                                   |

| OFM       | 0. 5 |                                                                                                                                                                                                                                             |

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Symbol           | Parameter                                                              |  | Min  | Max                    | Unit |

|------------------|------------------------------------------------------------------------|--|------|------------------------|------|

| V <sub>IN</sub>  | Voltage on AVIN, PVIN                                                  |  | -0.3 | 6.0                    | V    |

|                  | Voltage on Any Other Pin                                               |  | -0.3 | AV <sub>IN</sub> + 0.3 | 1    |

| Τ <sub>J</sub>   | Junction Temperature                                                   |  | -40  | +125                   | °C   |

| T <sub>STG</sub> | Storage Temperature                                                    |  | -65  | +150                   | °C   |

| ΤL               | Lead Soldering Temperature (10 Seconds)                                |  |      | +260                   | °C   |

| ESD              | Electrostatic Discharge Protection Level Human Body Model, JESD22-A114 |  | 2.0  | C                      | kV   |

|                  | Charged Device Model, JESD22-C101                                      |  | 1.0  |                        |      |

| LU               | Latch Up                                                               |  |      | JESD 78D               | -    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **Table 2. RECOMMENDED OPERATING CONDITIONS**

| Symbol                  | Parameter                                       | Min  | Тур | Max               | Unit |

|-------------------------|-------------------------------------------------|------|-----|-------------------|------|

| V <sub>IN</sub>         | Supply Voltage Range                            | 2.7  |     | 5.5               | V    |

| V <sub>OUT</sub>        | Output Voltage Range                            | 0.35 | ,C  | <v<sub>IN</v<sub> | V    |

| I <sub>OUT_BYPASS</sub> | Output Current in Bypass Mode (100% Duty Cycle) |      | 2   | 4.5               | А    |

| I <sub>OUT</sub>        | Output Current                                  |      |     | 3.0               | А    |

| L                       | Inductor                                        |      |     |                   | μH   |

| C <sub>IN</sub>         | Input Capacitor (Note 3)                        |      | 10  |                   | μF   |

| C <sub>OUT</sub>        | Output Capacitor (Note 4)                       |      | 4.7 |                   | μF   |

| T <sub>A</sub>          | Operating Ambient Temperature Range             | -40  |     | +85               | °C   |

| Т <sub>Ј</sub>          | Operating Junction Temperature Range            | -40  |     | +125              | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability. 3. The input capacitor must be large enough to limit the input voltage drop during GSM bursts, bypass transitions, and large output voltage

transitions.

4. Regulator requires only one 4.7  $\mu$ F; the V<sub>OUT</sub> bus should not exceed 14  $\mu$ F capacitance over DC bias and temperature.

#### **Table 3. DISSIPATION RATINGS**

| Symbol        | Parameter                                       | Min | Тур | Мах | Unit |

|---------------|-------------------------------------------------|-----|-----|-----|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Resistance (Note 5) |     | 40  |     | °C/W |

5. Junction-to-ambient thermal resistance is a function of application and board layout. This data is measured with four-layer 2s2p boards with vias in accordance to JESD51- JEDEC standard, Special attention must be paid not to exceed junction temperature T<sub>J(MAX)</sub> at a given

Table 4. ELECTRICAL CHARACTERISTICS, ALL MODES Recommended operating conditions, unless otherwise noted, circuit per Figure 1,  $V_{IN}$  = 2.7 V to 5.5 V,  $T_A$  = -40°C to +85°C. Typical values are given  $V_{IN}$  = 3.8 V at  $T_A$  = 25°C. L = 1 µH, Toko DFE201610C,  $C_{IN}$  = 10 µF 0402 TDK C1005X5R0J106MT,  $C_{OUT}$  = 3 x 4.7 µF 0402 TDK C1005X5R0J475KT.

| Symbol                   | Parameter                                           | Condition                                                                   | Min  | Тур                  | Мах  | Unit     |

|--------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|------|----------------------|------|----------|

| POWER SUPPI              | LIES                                                | -                                                                           | -    |                      |      |          |

| V <sub>IN</sub>          | Input Voltage Range                                 | $I_{OUT} \le 2.5 \text{ A}$                                                 | 2.7  |                      | 5.5  | V        |

| I <sub>SD</sub>          | Shutdown Supply Current                             | EN = 0 V, MODE = 0                                                          |      | 0.5                  | 3.0  | μA       |

| V <sub>UVLO</sub>        | Under Voltage Lockout Threshold                     | V <sub>IN</sub> Rising                                                      | 2.20 | 2.45                 | 2.60 | V        |

|                          |                                                     | Hysteresis                                                                  |      | 250                  | C    | mV       |

| LOGIC CONTR              | OL                                                  |                                                                             |      |                      |      |          |

| V <sub>IH</sub>          | Logic Threshold Voltage;                            | Input HIGH Threshold                                                        | 1.2  |                      | 2    | V        |

| V <sub>IL</sub>          | EN, BPEN, MODE                                      | Input LOW Threshold                                                         |      |                      | 0.4  | V        |

| I <sub>CTRL</sub>        | Logic Control Input Bias Current;<br>EN, BPEN, MODE | V <sub>IN</sub> or GND                                                      |      | 0.01                 | 1.00 | μΑ       |

| ANALOG CON               | TROL                                                |                                                                             |      |                      |      | <u>.</u> |

| V <sub>CON_LDO_EN1</sub> | V <sub>CON</sub> Forced Bypass Enter (Note 6)       | $V_{CON}$ Voltage that Forces Bypass;<br>$V_{IN} = 4.0 V - 4.75 V$          | 1.6  | 20                   |      | V        |

| V <sub>CON_LDO_EN2</sub> | V <sub>CON</sub> Forced Bypass Enter (Note 6)       | $V_{CON}$ Voltage that Forces Bypass; $V_{IN}\approx V_{OUT}$               | .0   | V <sub>IN</sub> /2.5 |      | V        |

| V <sub>CON_LDO_EX</sub>  | V <sub>CON</sub> Forced Bypass Exit                 | $V_{CON}$ Voltage that Exits Forced By-<br>pass; $V_{IN} = 2.70 V - 4.75 V$ |      | 0.                   | 1.4  | V        |

| $V_{con\_SL\_en}$        | V <sub>con</sub> Sleep Enter                        | V <sub>CON</sub> Voltage Forcing Low I <sub>Q</sub> Sleep<br>Mode           | 70   |                      |      | mV       |

| $V_{con\_SL\_ex}$        | V <sub>con</sub> Sleep Exit                         | V <sub>CON</sub> Voltage that Exits SLEEP Mode                              |      |                      | 125  | mV       |

| l <sub>Q</sub>           | DC-DC Quiescent Current in Sleep Mode               | V <sub>CON</sub> < 70 mV                                                    |      | 50                   | 80   | μA       |

| Gain                     | Gain in Control Range 0.16 V to 1.44 V              |                                                                             |      | 2.5                  |      |          |

| V <sub>OUT_ACC</sub>     | V <sub>OUT</sub> Accuracy                           | Ideal = 2.5 x V <sub>CON</sub>                                              | -50  |                      | +50  | mV       |

| LDO                      |                                                     | 7. 100 40                                                                   |      |                      |      |          |

| R <sub>FET</sub>         | LDO FET Resistance                                  |                                                                             |      | 29                   |      | mΩ       |

| $\Delta V_{OUT\_LDO}$    | LDO Dropout (Note 7)                                | I <sub>OUT</sub> = 2.0 A                                                    |      | 100                  |      | mV       |

| OVER TEMPER              | ATURE PROTECTION                                    |                                                                             |      |                      |      |          |

| T <sub>OTP</sub>         | Over-Temperature Protection                         | Rising Temperature                                                          |      | +150                 |      | °C       |

|                          |                                                     | Hysteresis                                                                  |      | +20                  |      | °C       |

| OSCILLATOR               |                                                     |                                                                             |      |                      |      |          |

| f <sub>SW</sub>          | Average Oscillator Frequency                        |                                                                             | 2.6  | 2.9                  | 3.2  | MHz      |

| DC-DC                    |                                                     |                                                                             |      |                      |      |          |

| R <sub>DSON</sub>        | PMOS On Resistance                                  | $V_{IN} = V_{GS} = 3.7 V$                                                   |      | 80                   |      | mΩ       |

|                          | NMOS On Resistance                                  | $V_{IN} = V_{GS} = 3.7 V$                                                   |      | 60                   |      |          |

| I <sub>LIMp</sub>        | P-Channel Current Limit (Note 8)                    |                                                                             | 1.50 | 1.90                 | 2.30 | Α        |

| I <sub>LIMn</sub>        | N-Channel Current Limit (Note 8)                    |                                                                             | 1.50 | 1.90                 | 2.30 | Α        |

| I <sub>Discharge</sub>   | Maximum Transient Discharge Current                 |                                                                             |      | 3.7                  | 4.5  | Α        |

| I <sub>LIMLDO</sub>      | LDO Current Limit                                   |                                                                             |      |                      | 4.5  | Α        |

6. Input voltages nominally exceeding the lesser of VIN/2.5 or 1.6 V force 100% duty cycle.

7. Dropout depends on LDO and DC-DC PFET R<sub>DSON</sub> and inductor DCR.

8. The current limit is the peak (maximum) current.

Guaranteed by design. Maximum values are based on simulation results with 50% COUT derating; not tested in production. Voltage tran-9. sient only. Assumes  $C_{OUT} = 3 \times 4.7 \ \mu\text{F}$  (1x4.7  $\mu\text{F}$  for regulator and 2x4.7  $\mu\text{F}$  for PA decoupling capacitors). 10. Protects part under short–circuit conditions

**Table 4. ELECTRICAL CHARACTERISTICS, ALL MODES** Recommended operating conditions, unless otherwise noted, circuit per Figure 1,  $V_{IN} = 2.7$  V to 5.5 V,  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C. Typical values are given  $V_{IN} = 3.8$  V at  $T_A = 25^{\circ}$ C. L = 1  $\mu$ H, Toko DFE201610C, C<sub>IN</sub> = 10  $\mu$ F 0402 TDK C1005X5R0J106MT, C<sub>OUT</sub> = 3 x 4.7  $\mu$ F 0402 TDK C1005X5R0J475KT.

| Symbol                | Parameter                              | Condition                                            | Min  | Тур  | Max  | Unit |

|-----------------------|----------------------------------------|------------------------------------------------------|------|------|------|------|

| DC-DC                 | -                                      |                                                      |      |      |      |      |

| V <sub>OUT_MIN</sub>  | Minimum Output Voltage                 | V <sub>CON</sub> = 0.16 V                            | 0.35 | 0.40 | 0.45 | V    |

| V <sub>OUT_MAX</sub>  | Maximum Output Voltage                 | V <sub>CON</sub> = 1.44 V, V <sub>IN</sub> = 3.9 V   | 3.55 | 3.60 | 3.65 | V    |

| DC-DC EFFIC           | IENCY                                  |                                                      |      |      |      | ~    |

| $\eta_{\text{Power}}$ | Power Efficiency, Low–Power Auto Mode, | V <sub>OUT</sub> = 3.1 V, I <sub>LOAD</sub> = 250 mA |      | 95   | C    | %    |

|                       | V <sub>IN</sub> = 3.7 V                | V <sub>OUT</sub> = 1.8 V, I <sub>LOAD</sub> = 250 mA |      | 90   |      |      |

|                       |                                        | V <sub>OUT</sub> = 0.5 V, I <sub>LOAD</sub> = 10 mA  |      | 65   | 2    |      |

#### OUTPUT REGULATION

| V <sub>OUT_RLine</sub>  | V <sub>OUT</sub> Line Regulation | $3.1 \le V_{IN} \le 3.7$                                        | ±5  | mV |

|-------------------------|----------------------------------|-----------------------------------------------------------------|-----|----|

| V <sub>OUT_RLoad</sub>  | V <sub>OUT</sub> Load Regulation | $20 \text{ mA} \le I_{OUT} \le 800 \text{ mA}$                  | ±25 | mV |

| V <sub>OUT_Ripple</sub> | V <sub>OUT</sub> Ripple          | PFM Mode, V <sub>IN</sub> = 3.7 V,<br>I <sub>OUT</sub> < 100 mA | 10  | mV |

|                         |                                  | PWM Mode, V <sub>IN</sub> = 3.7 V                               | 4   |    |

#### TIMING

| t <sub>SS</sub>       | Startup Time (Note 9)                                           |                                                                                                                                                                        |    | 50   | 60  | μs |

|-----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-----|----|

| <sup>t</sup> DC-DC_TR | V <sub>CON</sub> Step Response Rise Time (Note 9)               | From V <sub>CON</sub> to 95% V <sub>OUT</sub> , $\Delta$ V <sub>OUT</sub> $\leq$ 2.7 V (0.7 V - 3.4 V), R <sub>LOAD</sub> = 5 $\Omega$ , C <sub>OUT</sub> = 14 $\mu$ F | MA | 6.0  | 7.3 | μs |

| t <sub>DC-DC</sub> TF | V <sub>CON</sub> Step Response Fall Time (Note 9)               | From V <sub>CON</sub> to 5% V <sub>OUT</sub> , $\Delta$ V <sub>OUT</sub><br>2.7 V (3.4 V – 0.7 V), R <sub>LOAD</sub> = 200 $\Omega$ ,<br>C <sub>OUT</sub> = 14 $\mu$ F |    | 6.8  | 7.6 | μs |

| <sup>t</sup> DC-DC_CL | Maximum Allowed Time for Consecutive<br>Current Limit (Note 10) | V <sub>OUT</sub> < 1 V                                                                                                                                                 |    | 1500 |     | μs |

| <sup>t</sup> DCDC_CLR | Consecutive Current Limit Recovery Time (Note 10)               | 10.4                                                                                                                                                                   |    | 4800 |     | μs |

6. Input voltages nominally exceeding the lesser of VIN/2.5 or 1.6 V force 100% duty cycle.

7. Dropout depends on LDO and DC-DC PFET R<sub>DSON</sub> and inductor DCR.

8. The current limit is the peak (maximum) current.

9. Guaranteed by design. Maximum values are based on simulation results with 50% COUT derating; not tested in production. Voltage transient only. Assumes  $C_{OUT} = 3 \times 4.7 \ \mu\text{F}$  for regulator and 2x4.7  $\mu\text{F}$  for PA decoupling capacitors).

10. Protects part under short-circuit conditions

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

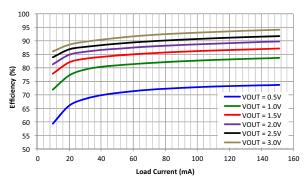

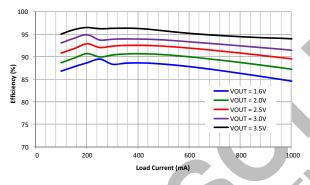

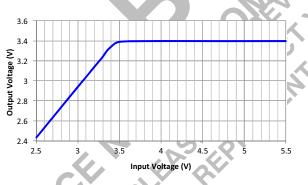

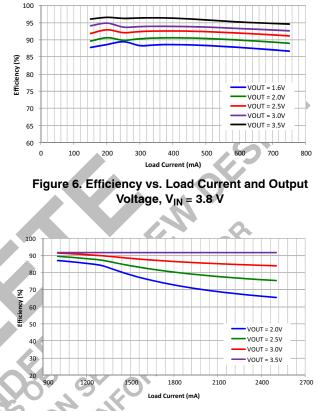

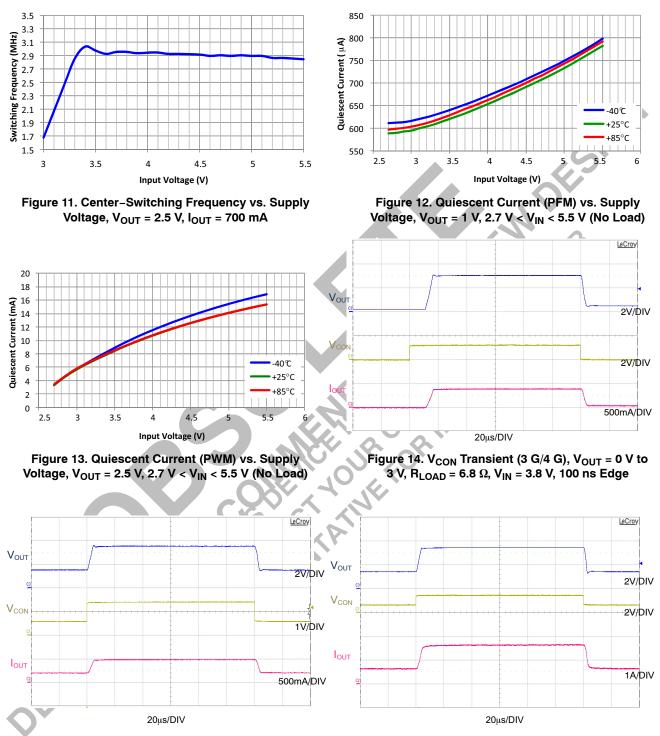

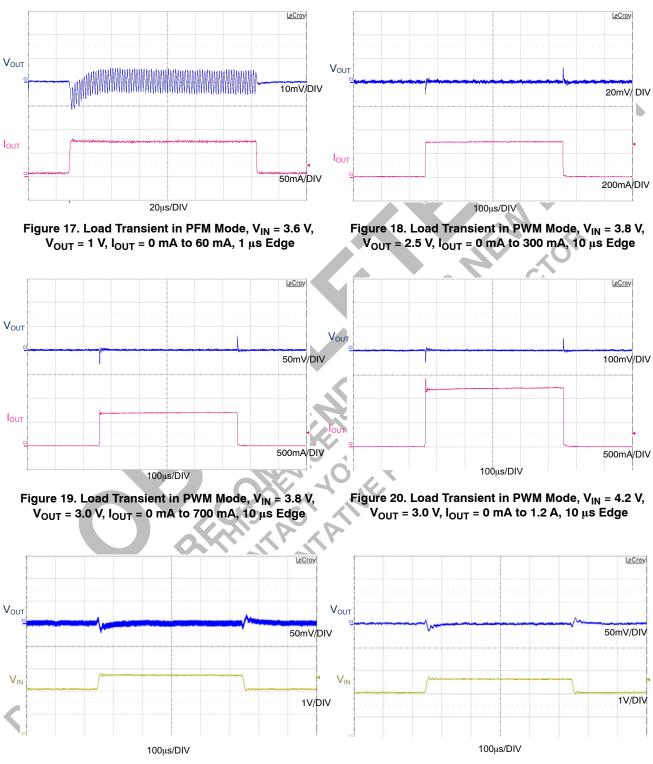

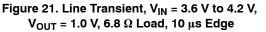

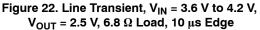

#### **Typical Characteristics**

Unless otherwise noted, V<sub>IN</sub> = EN = 3.7 V, L = 1.0  $\mu$ H, C<sub>IN</sub> = 10  $\mu$ F, C<sub>OUT</sub> = 3 x 4.7  $\mu$ F, and T<sub>A</sub> = +25°C.

Figure 5. Efficiency vs. Load Current and Output Voltage,  $V_{IN}$  = 3.8 V ,  $I_{OUT}$  = 10 mA to 150 mA

Figure 7. Efficiency vs. Load Current and Output Voltage,  $V_{IN}$  = 3.8 V,  $I_{OUT}$  = 100 mA to 1 A

Figure 9. Output Voltage vs. Supply Voltage,  $V_{OUT}$  = 3.4 V,  $I_{OUT}$  = 1.5 A,  $V_{IN}$  = 4.3 V to Dropout

Figure 8. Efficiency vs. Load Current and Output Voltage, V<sub>IN</sub> = 3.8 V, I<sub>OUT</sub> = 1 A to 2.5 A

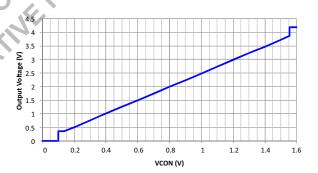

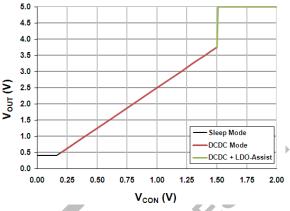

Figure 10. Output Voltage vs. V<sub>CON</sub> Voltage, V<sub>IN</sub> = 4.2 V, R<sub>LOAD</sub> = 6.8  $\Omega$ , 0.1 V < V<sub>CON</sub> < 1.6 V

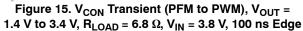

#### **Typical Characteristics**

Unless otherwise noted, V\_{IN} = EN = 3.7 V, L = 1.0  $\mu$ H, C<sub>IN</sub> = 10  $\mu$ F, C<sub>OUT</sub> = 3 x 4.7  $\mu$ F, and T<sub>A</sub> = +25°C.

Figure 16. V<sub>CON</sub> Transient (PWM), V<sub>OUT</sub> = 1.4 V to 3.4 V, R<sub>LOAD</sub> = 1.9  $\Omega$ , V<sub>IN</sub> = 4.2 V, 100 ns Edge

#### **Typical Characteristics**

Unless otherwise noted,  $V_{IN}$  = EN = 3.7 V, L = 1.0  $\mu$ H,  $C_{IN}$  = 10  $\mu$ F,  $C_{OUT}$  = 3 x 4.7  $\mu$ F, and  $T_A$  = +25°C.

#### **Operating Description**

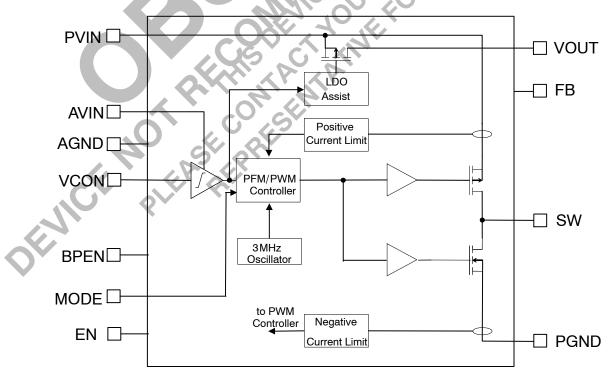

The FAN5909 is a high-efficiency, synchronous, step-down converter (DC-DC) with LDO-assist function.

The DC-DC converter operates with current-mode control and supports a wide range of load currents. High-current applications up to a 2.5 A DC output, such as mandated by GSM/EDGE applications, are allowed. Performance degradation due to spurs is removed by spreading the ripple energy through clock dither. A regulated Bypass Mode continues to regulate the output to the desired voltage as  $V_{IN}$  approaches  $V_{OUT}$ . The LDO offers a dropout voltage of approximately 100 mV under a 2 A load current.

The output voltage  $V_{OUT}$  is regulated to 2.5 times the input control voltage,  $V_{CON}$ , set by an external DAC. The FAN5909 operates in either PWM or PFM Mode, depending on the output voltage and load current.

In Pulse Width Modulation (PWM) Mode, regulation begins with on-state. A P-channel transistor is turned on and the inductor current is ramped up until the off-state begins. In the off-state, the P-channel is switched off and an N-channel transistor is turned on. The inductor current decreases to maintain an average value equal to the DC load current. The inductor current is continuously monitored. A current sense flags when the P-channel transistor current exceeds the current limit and the switcher is turned back to off-state to decrease the inductor current and prevent magnetic saturation. The current sense flags when the N-channel transistor current exceeds the current limit and redirects discharging current through the inductor back to the battery.

In Pulse Frequency Modulation (PFM) Mode, the FAN5909 operates in a constant on-time mode at low load currents. During on-state, the P-channel is turned on for a specified time before switching to off-state. In off-state, the N-channel switch is enabled until inductor current decreases to 0 A. The switcher enters three-state until a new regulation cycle starts.

PFM operation is allowed only in Low-Power Mode (MODE=1) for output voltages nominally less than 1.5 V. At low load currents, PFM achieves higher efficiency than PWM. The trade-off for efficiency improvement, however, is larger output ripple. Some applications, such as audio, may not tolerate the higher ripple, especially at high output voltages.

#### **Dynamic Output Voltage Transitions**

FAN5909 has a complex voltage transition controller that realizes 6  $\mu$ s transition times with a large output capacitor and output voltage ranges.

The transition controller manages five transitions:

- $\Delta V_{OUT}$  positive step

- $\Delta V_{OUT}$  negative step

- $\Delta V_{OUT}$  transition to or from 100% duty cycle

- $\Delta V_{OUT}$  transition at startup

In all cases, it is recommended that sharp  $V_{\rm CON}$  transitions be applied, letting the transition controller optimize the output voltage slew rate.

#### ∆V<sub>OUT</sub> Positive Step

After a  $V_{CON}$  positive step, the FAN5909 enters Current-Limit Mode, where  $V_{OUT}$  ramps with a constant slew rate dictated by the output capacitor and the current limit.

#### ∆V<sub>OUT Nega</sub>tive Step

After a  $V_{CON}$  negative step, the FAN5909 enters Current Limit Mode where  $V_{OUT}$  is reduced with a constant slew rate dictated by the output capacitor and the current limit.

#### V<sub>OUT</sub> Transition to or from Forced Bypass

The DC–DC is forced into 100% duty cycle for  $V_{CON}$  nominally greater than 1.6 V. This allows the output to be connected to the supply through both the low–resistance DC–DC and the LDO PFETs.

#### V<sub>OUT</sub> Transition at Startup

At startup, after the EN rising edge is detected, the system requires 25  $\mu$ s for all internal voltage references and amplifiers to start before enabling the DC–DC converter function.

# **MODE Pin**

The MODE pin enable Forced PWM Mode or Auto PFM / PWM Mode. When the MODE pin is toggled HIGH (logic 1), the FAN5909 operates in PFM for  $V_{OUT} \le 1.5$  V under light-load conditions and PWM for heavy-load conditions. If the MODE pin is set LOW (logic = 0), it operates in Forced PWM Mode.

#### Auto PFM / PWM Mode (MODE = 1)

Auto PFM/PWM Mode is appropriate for 3 G/3.5 G and 4 G applications.

#### Forced PWM Mode (MODE = 0)

Forced PWM Mode is appropriate for applications that demand minimal ripple over the entire output voltage range.

#### DC-DC - LDO-Assist

The LDO–assist function maintains output regulation when  $V_{IN}$  approaches  $V_{OUT}$ , enables fast transition times under heavy loads, and minimizes PCB space by enabling a smaller inductor to be employed by using the LDO to provide a portion of the necessary load current.

The LDO-assist function limits the maximum current that the DC-DC may supply by shunting current away from the DC-DC under heavy loads and high duty cycles. In addition, the LDO-assist enables a seamless transition into 100% duty cycle, ensuring both low output ripple and constant output regulation. Since the LDO-assist function limits the maximum current supplied by the DC-DC, PCB area is minimized by enabling a lower current capable, and thus smaller form factor, inductor to be used.

#### DC-DC – Sleep Mode

The Sleep Mode minimizing current while enabling rapid return to regulation. Sleep Mode is entered when  $V_{CON}$  is held below 70 mV for at least 40 µs. In this mode, current consumption is reduced to under 50 µA. Sleep Mode is exited after ~12 µs when  $V_{CON}$  is set above 125 mV.

#### **Application Information**

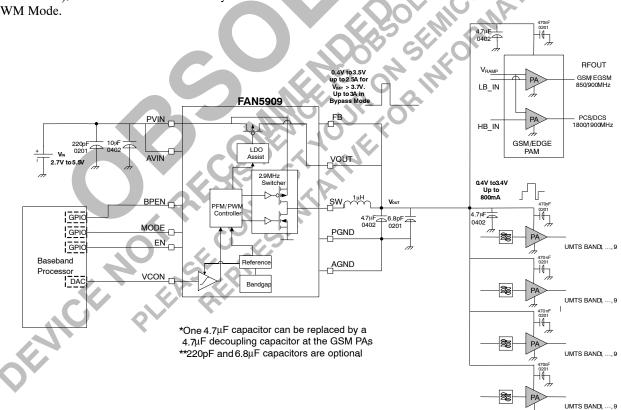

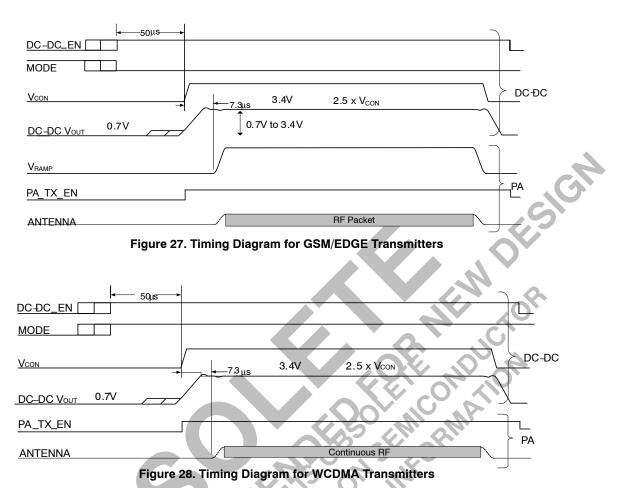

Figure 26 illustrates the FAN5909 in a GSM / EDGE / WCDMA transmitter configuration, driving multiple GSM / EDGE and 3 G/3.5 G and 4 G PAs. Figure 27 presents a timing diagram designed to meet GSM specifications.

#### **DC Output Voltage**

The output voltage is determined by  $V_{CON}$  provided by an external DAC or voltage reference:

$$V_{OUT} = 2.5 \times V_{CON}$$

(eq. 1)

The FAN5909 provides regulated V<sub>OUT</sub> only if V<sub>CON</sub> falls within the typical range from 0.16 V to 1.44 V. This allows V<sub>OUT</sub> to be adjusted between 0.4 V and 3.6 V. If V<sub>CON</sub> is less than 0.16 V, V<sub>OUT</sub> is clamped to 0.40 V. In Auto PFM/PWM Mode, the FAN5909 automatically switches between PFM and PWM. In Forced PWM Mode (MODE = 0), the FAN5909 automatically switches into PWM Mode.

Figure 25. Output Voltage vs. Control Voltage

The FAN5909 is designed to support voltage transients of  $6 \mu s$  when configured for GSM/EDGE applications (MODE=0) and driving a load capacitance of approximately 14  $\mu$ F. Figure 28 shows a timing diagram for WCDMA applications.

Figure 26. Typical Application Diagram with GSM/EDGE/WCDMA Transmitters

#### Inductor Selection

The FAN5909 operates at 2.9 MHz switching frequency, allowing 1.0  $\mu$ H or 1.5  $\mu$ H inductors to be used in designs. For applications requiring the smallest possible PCB area, use a 1.0  $\mu$ H 2012 inductor or a 1.0  $\mu$ H 2016 inductor for optimum efficiency performance.

| Inductor | Description                                                      |

|----------|------------------------------------------------------------------|

| L        | 1.0 μH ±20%, 2.1 A, 2012 Case Size<br>Cyntec: PSK20121T-1R0MS-63 |

|          | 1.0 μH ±20%, 2.2 A, 2016 Case Size<br>Toko: DFE201610R-H-1R0M    |

#### **Capacitor Selection**

The minimum required output capacitor  $C_{OUT}$  should be one (1) 4.7 µF, 6.3 V, X5R with an ESR of 10 m $\Omega$  or lower and an ESL of 0.3 nH or lower in parallel after inductor L1. Larger case sizes result in increased loop parasitic inductance and higher noise. One 4.7 µF capacitor should be used as a decoupling capacitor at the GSM/EDGE PA V<sub>CC</sub> pin and another 4.7 µF capacitor should be placed at V<sub>CC</sub> pin of the 3 G/4 G PA. A 6.8 pF capacitor may be added in parallel with  $C_{OUT}$  to reduce the capacitor's parasitic inductance.

#### **Table 6. RECOMMENDED CAPACITOR VALUES**

| Capacitor        | Description                                                        |

|------------------|--------------------------------------------------------------------|

| C <sub>IN</sub>  | 10 μF, ±20%, X5R, 6.3 V, 0402<br>(1005 metric) TDK C1005X5R0J106M  |

| C <sub>OUT</sub> | 4.7 μF, ±20%, X5R, 6.3 V, 0402<br>(1005 metric) TDK C1005X5R0J475K |

#### **PCB Layout and Component Placement**

- The key point in the placement is the power ground (PGND) connection shared between the FAN5909, CIN, and COUT. This minimizes the parasitic inductance of the switching loop paths.

- Place the inductor away from the feedback pins to prevent unpredictable loop behavior.

- Ensure the traces are wide enough to handle the maximum current value, especially in Bypass Mode.

- Ensure the vias are able to handle the current density. Use filled vias if available.

#### PACKAGE DIMENSIONS

| D             | E               | Х      | Y      | Unit |

|---------------|-----------------|--------|--------|------|

| 1.615 ± 0.030 | $1.615\pm0.030$ | 0.2075 | 0.2075 | mm   |

Industries, LLC

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor haves, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such uninten

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative