Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="https://www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="https://www.onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized applications, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an equif prese

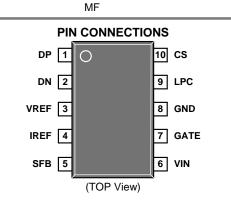

# **Compact Secondary-Side Adaptive Charging Controller Synchronous Rectifier Control**

FAN6290QF/FAN6290QH are highly integrated, secondary-side power adaptor controllers compatible with the Quick Charge 3.0 (QC3.0) protocol. Internally adopted synchronous rectifier control helps for less BOM counts as well as for easy design.

The internal two operational amplifiers control adaptive constant output voltage and adaptive constant output current. The outputs of the two amplifiers are tied together in open-drain configuration.

FAN6290QF/FAN6290QH enables adaptor output voltage and current adjustment when Quick Charge 3.0 protocol is acknowledged. According to request from a battery charger of a Portable Device, output voltage is adjusted up to 12 V. When a portable device that implements noncompliant protocols is attached, it just maintains the default output, (5 V) for safety of the portable device.

FAN6290QF/FAN6290QH incorporates adaptive output over-voltage and under-voltage protections to improve system reliability.

# Features

- Compatible with Quick Charge 3.0 (QC3.0) Protocol

- Auto-detection supporting 2.4 A Apple products

- Internal Synchronous Rectifier Control Circuit

- Secondary-Side Constant Voltage (CV) and Constant Current (CC) Regulation with Two Operational Amplifiers

- Small Current Sensing Resistor (30 m $\Omega$ ) for High Efficiency

- Protections for Safe Operation ; Output Over-Voltage-Protection, Output Under-Voltage-Protection for QC2.0, Data line (D+/D-) Over-Voltage-Protection

- Built-in output capacitor bleeding function for fast discharging during change of output mode

- Built-in Cable-Drop Compensation

# **Typical Applications**

- Battery Chargers for Smart Phones, Feature Phones, and Tablet PCs

- AC-DC Adapters for Portable Devices that Require CV/CC Control

# **ON Semiconductor®**

www.onsemi.com

SOP-10

# ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 17 of this data sheet.

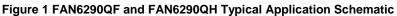

Figure 2. FAN6290QF and FAN6290QH Function Block Diagram

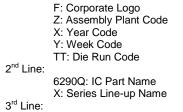

# PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name | Description                                                                                                                                                                                                                  |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DP       | Communication Interface Positive Terminal. This pin is tied to the USB D+ data line input.                                                                                                                                   |

| 2       | DN       | Communication Interface Negative Terminal. This pin is tied to the USB D- data line input.                                                                                                                                   |

| 3       | VREF     | Output Voltage Sensing Terminal. Non-inverting terminal of the internal CV loop amplifier. This pin is used for constant voltage regulation.                                                                                 |

| 4       | IREF     | Constant Current Amplifying Signal. The voltage on this pin represents the amplified current sense signal, also used for constant current regulation. It is tied to the internal CC loop amplifier's non-inverting terminal. |

| 5       | SFB      | Secondary Feedback. Common output of the open-drain operation amplifiers. Typically an opto-<br>coupler is connected to this pin to provide feedback signal to the primary-side PWM controller.                              |

| 6       | VIN      | Input Voltage. This pin is tied to the output of the adaptor not only to monitor output voltage but also to supply internal bias. IC operating current, and MOSFET gate-drive current are supplied through this pin.         |

| 7       | GATE     | Gate Drive Output. Totem-pole output to drive an external SR MOSFET.                                                                                                                                                         |

| 8       | GND      | Ground.                                                                                                                                                                                                                      |

| 9       | LPC      | SR MOSFET Drain Voltage Detection. This pin detects the voltage on the secondary winding for Synchronous Rectifier control.                                                                                                  |

| 10      | CS       | Current Sensing Amplifier Negative Terminal. Output current is sensed through this terminal for green mode control, cable drop compensation, and constant current control.                                                   |

#### Series Line-up Table

| Name      | Output Voltage and its Nominal Output Current |                        |                          | UVP Operation |

|-----------|-----------------------------------------------|------------------------|--------------------------|---------------|

| Name      | V <sub>o</sub> = 3.6 ~ 6 V                    | $V_{0} = 6.2 \sim 9 V$ | $V_{\rm O}$ = 9.2 ~ 12 V | OVP Operation |

| FAN6290QF | 3.0 A                                         | 2.0 A                  | 1.5 A                    | Pull-down SFB |

| FAN6290QH | 3.0 A                                         | 3.0 A                  | 2.0 A                    | Reduce CC     |

#### MAXIMUM RATINGS (Note 1,2,3)

| Rating                                                 | Symbol             | Value       | Unit |

|--------------------------------------------------------|--------------------|-------------|------|

| VIN Pin Input Voltage                                  | V <sub>IN</sub>    | 20          | V    |

| SFB Pin Input Voltage                                  | V <sub>SFB</sub>   | 20          | V    |

| IREF Pin Input Voltage                                 | V <sub>IREF</sub>  | -0.3 to 6   | V    |

| VREF Pin Input Voltage                                 | V <sub>VREF</sub>  | -0.3 to 6   | V    |

| CS Pin Input Voltage                                   | V <sub>CS</sub>    | -0.3 to 6   | V    |

| DP Pin Input Voltage                                   | V <sub>DP</sub>    | -0.3 to 14  | V    |

| DN Pin Input Voltage                                   | V <sub>DN</sub>    | -0.3 to 14  | V    |

| LPC Pin Input Voltage                                  | V <sub>LPC</sub>   | -0.3 to 6.5 | V    |

| GATE Pin Input Voltage                                 | V <sub>GATE</sub>  | -0.3 to 6   | V    |

| Power Dissipation (T <sub>A</sub> =25°C)               | PD                 | 0.68        | W    |

| Operating Junction Temperature                         | TJ                 | -40 to 150  | °C   |

| Storage Temperature Range                              | T <sub>STG</sub>   | -40 to 150  | °C   |

| Lead Temperature, (Soldering, 10 Seconds)              | TL                 | 260         | °C   |

| Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 (Note 4) | ESD <sub>HBM</sub> | 3           | kV   |

| Charged Device Model, JESD22-C101 (Note 4)             | ESD <sub>CDM</sub> | 1.75        | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device 1. functionality should not be assumed, damage may occur and reliability may be affected.

2.

All voltage values, except differential voltages, are given with respect to the GND pin. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Meets JEDEC standards JS-001-2012 and JESD 22-C101. 3.

4.

# THERMAL CHARACTERISTICS (Note 5)

| Rating                                                          | Symbol           | Value | Unit |

|-----------------------------------------------------------------|------------------|-------|------|

| Thermal Characteristics,<br>Thermal Resistance, Junction-to-Air | R <sub>eJA</sub> | 142   | °C/W |

| Thermal Reference, Junction-to-Top                              | $R_{\psi JT}$    | 21    |      |

5.  $T_A=25^{\circ}C$  unless otherwise specified.

#### **RECOMMENDED OPERATING RANGES** (Note 6)

| Rating                 | Symbol            | Min  | Max | Unit |

|------------------------|-------------------|------|-----|------|

| VIN Pin Input Voltage  | V <sub>IN</sub>   | 0    | 16  | V    |

| SFB Pin Input Voltage  | V <sub>SFB</sub>  | 0    | 16  | V    |

| IREF Pin Input Voltage | VIREF             | 0    | 1   | V    |

| VREF Pin Input Voltage | V <sub>VREF</sub> | 0    | 3.5 | V    |

| CS Pin Input Voltage   | V <sub>CS</sub>   | -0.1 | 0   | V    |

| DP Pin Input Voltage   | V <sub>DP</sub>   | 0    | 6   | V    |

| DN Pin Input Voltage   | V <sub>DN</sub>   | 0    | 6   | V    |

| LPC Pin Input Voltage  | V <sub>LPC</sub>  | 0    | 5   | V    |

| GATE Pin input Voltage | V <sub>GATE</sub> | 0    | 5.5 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses 6. beyond the Recommended Operating Ranges limits may affect device reliability.

# ELECTRICAL CHARACTERISTICS

V<sub>IN</sub>=5 V, LPC=1.5 V, LPC width=2 µs at T<sub>J</sub>= -40~125 °C, F<sub>LPC</sub>=100 kHz, unless otherwise specified.

| Parameter                                                                                               | Test Conditions                                                            | Symbol                        | Min  | Тур  | Max  | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|------|------|------|------|

| /IN Section                                                                                             |                                                                            |                               |      |      |      |      |

| Continuous Operating Voltage <sup>(7)</sup>                                                             |                                                                            | V <sub>IN-OP</sub>            |      |      | 16   | V    |

| Operating Supply Current                                                                                | V <sub>IN</sub> =5 V, V <sub>CS</sub> = -60 mV                             | I <sub>IN-OP-5V</sub>         |      | 8    |      | mA   |

| Operating Supply Current                                                                                | V <sub>IN</sub> =12 V, V <sub>CS</sub> = -60 mV                            | I <sub>IN-OP-12V</sub>        |      | 8    |      | mA   |

| 5 V Green Mode Operating Supply Current                                                                 | V <sub>IN</sub> =5 V, V <sub>CS</sub> =0 mV                                | I <sub>IN-Green</sub>         |      | 1.2  | 1.6  | mA   |

| VIN-UVP Section                                                                                         |                                                                            | 11                            |      | •    | 1    |      |

| Voltage difference between GND and CS for fixed UVP current ( $I_{O^-UVP.typ}$ =217 mA)                 | Only for FAN6290QH                                                         | $V_{\text{CS-UVP}}$           | 3.0  | 6.5  | 10.0 | mV   |

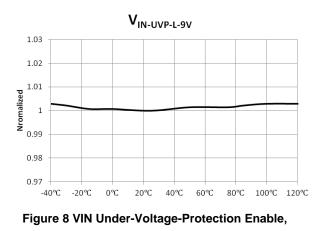

| $V_{IN}$ Under-Voltage-Protection Enable, 9 V                                                           | For QC2.0 9 V Mode                                                         | VIN-UVP-L-9V                  | 5.00 | 5.50 | 6.00 | V    |

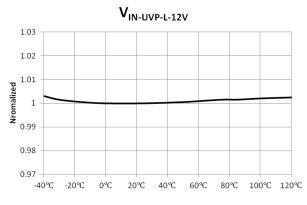

| $V_{IN}$ Under-Voltage-Protection Enable, 12 V                                                          | For QC2.0 12 V Mode                                                        | VIN-UVP-L-12V                 | 7.50 | 8.00 | 8.50 | V    |

| $V_{IN}$ Under-Voltage-Protection Disable, 9 V                                                          | For QC2.0 9 V Mode                                                         | V <sub>IN-UVP-H-9V</sub>      | 5.50 | 6.00 | 6.50 | V    |

| V <sub>IN</sub> Under-Voltage-Protection Disable, 12 V                                                  | For QC2.0 12 V Mode                                                        | V <sub>IN-UVP-H-12V</sub>     | 8.00 | 8.50 | 9.00 | V    |

| CC Mode UVP Debounce Time                                                                               |                                                                            | t <sub>D-VIN-UVP</sub>        | 45   | 60   | 75   | ms   |

| VIN-OVP Section                                                                                         |                                                                            | 11                            |      | •    | 1    |      |

| Output Over-Voltage Protection through V_IN Pin at V_0=3.6 ~ 5 V                                        |                                                                            | V <sub>IN-OVP-5V</sub>        | 5.5  | 6.0  | 6.5  | V    |

| Output Over-Voltage Protection through $V_{\rm IN}$ Pin at $V_0{=}5.2 \sim 6~V$                         |                                                                            | V <sub>IN-OVP-6V</sub>        | 8.1  | 8.4  | 8.7  | V    |

| Output Over-Voltage Protection through $V_{\text{IN}}$ Pin at $V_{\text{O}}{=}6.2$ ~ 9 V                |                                                                            | V <sub>IN-OVP-9V</sub>        | 10.3 | 10.8 | 11.3 | V    |

| Output Over-Voltage Protection through $V_{\text{IN}}$ Pin at $V_{\text{0}}\text{=}9.2$ ~ 12 V          |                                                                            | V <sub>IN-OVP-12V</sub>       | 13.6 | 14.4 | 15.0 | V    |

| OVP Debounce Time                                                                                       |                                                                            | t <sub>D-OVP</sub>            | 22   | 33   | 44   | μs   |

| Internal Bias Section                                                                                   |                                                                            |                               |      |      |      |      |

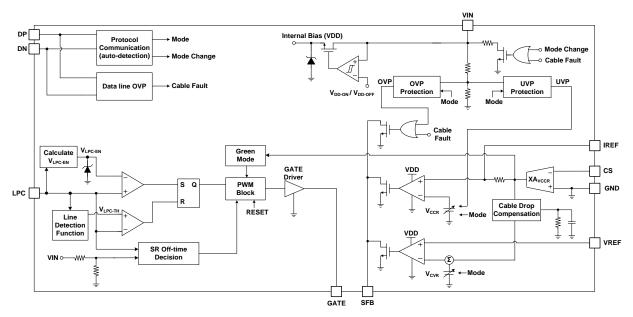

| Turn-On Threshold Voltage                                                                               | V <sub>IN</sub> Increases                                                  | V <sub>IN-ON</sub>            | 2.9  | 3.2  | 3.4  | V    |

| Turn-Off Threshold Voltage                                                                              | $V_{\text{IN}}$ Decreases after $V_{\text{IN}} \!\!=\!\! V_{\text{IN-ON}}$ | $V_{\text{IN-OFF}}$           | 2.8  | 2.9  | 3.0  | V    |

| Hysteresis of Turn-Off Threshold Voltage                                                                | $V_{\text{IN}}$ Decreases after $V_{\text{IN}}{=}V_{\text{IN-ON}}$         | $V_{\text{IN-OFF-HYS}}$       |      | 0.3  |      | V    |

| Turn-On Debounce Time                                                                                   |                                                                            | $t_{\text{VIN-on-debounce}}$  |      |      | 50   | μs   |

| Turn-Off Debounce Time                                                                                  |                                                                            | $t_{\text{VIN-off-debounce}}$ |      |      | 200  | μs   |

| Output Voltage Releasing Latch Mode <sup>(8)</sup>                                                      |                                                                            | VLATCH-OFF                    | 1.5  | 2.0  | 2.5  | V    |

| Constant Current Sensing Section                                                                        |                                                                            |                               |      |      |      |      |

| Current-Sense Amplifier Gain <sup>(7)</sup>                                                             | V <sub>IN</sub> =5 V, V <sub>CS</sub> = -60 mV                             | A <sub>V-CCR</sub>            |      | 10   |      | V/V  |

| Voltage difference between GND and CS at $I_{0^{\text{-}NOMINAL}}{=}3.0~\text{A}$ of FAN6290QF $^{(8)}$ | I <sub>O</sub> =3.0~3.4 A, I <sub>OTYP</sub> =3.2 A (3 mV Offset)          | V <sub>CS-3.0A-QF</sub>       | 90.0 | 93.0 | 96.0 | mV   |

| Voltage difference between GND and CS at $I_{0^{-}NOMINAL}{=}2.0$ A of FAN6290QF $^{(8)}$               | I <sub>0</sub> =2.0~2.3 A, I <sub>0TYP</sub> =2.15 A (3 mV Offset)         | V <sub>CS-2.0A-QF</sub>       | 59.5 | 62.0 | 64.5 | mV   |

| Voltage difference between GND and CS at $I_{0^{\text{-}NOMINAL}}{=}1.5$ A of FAN6290QF $^{(8)}$        | I <sub>O</sub> =1.5~1.8 A, I <sub>OTYP</sub> =1.65 A (3 mV Offset)         | V <sub>CS-1.5A-QF</sub>       | 43.5 | 46.0 | 48.5 | mV   |

| Voltage difference between GND and CS at $I_{0^{-}NOMINAL}{=}3.0$ A of FAN6290QH $^{(8)}$               | I <sub>0</sub> =3.0~3.4 A, I <sub>0TYP</sub> =3.2 A (3 mV Offset)          | V <sub>CS-3.0A-QH</sub>       | 90.0 | 93.0 | 96.0 | mV   |

| Voltage difference between GND and CS at $I_{0^{-}NOMINAL}{=}2.0$ A of FAN6290QH $^{(8)}$               | I <sub>0</sub> =2.0~2.4 A, I <sub>0TYP</sub> =2.2 A (3 mV Offset)          | V <sub>CS-2.0A-QH</sub>       | 62.5 | 65.0 | 67.5 | mV   |

| Current-Sensing Input Impedance <sup>(8)</sup>                                                          |                                                                            | Z <sub>cs</sub>               | 4    |      |      | MΩ   |

| Voltage difference between GND and CS for Green Mode                                                    | R <sub>cs</sub> =30 mΩ                                                     | V <sub>CS-Green</sub>         | 2    | 5    | 8    | mV   |

ELECTRICAL CHARACTERISTICS (CONTINUED) onified

| Parameter                                                                                          | Test Conditions                                                                           | Symbol                              | Min   | Тур   | Max   | Unit |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|-------|-------|-------|------|

| Constant Current Sensing Section (contin                                                           | ued)                                                                                      | 1                                   |       |       |       |      |

| Voltage difference between GND and CS for Green Mode                                               | Only for under 4.8 V Mode of QC3.0, $R_{\text{CS}}\text{=}30\ \text{m}\Omega$             | V <sub>CS-Green-</sub><br>LowQC3.0  | 34    | 39    | 44    | mV   |

| Green Mode Enable Debounce Time                                                                    | After V <sub>CS</sub> <v<sub>CS-Green</v<sub>                                             | T <sub>Green-EN-</sub><br>Debounce  |       |       | 100   | μs   |

| Green Mode Disable Debounce Time                                                                   | After V <sub>CS</sub> >V <sub>CS-Green</sub>                                              | T <sub>Green-DIS-</sub><br>Debounce | 8     | 12    | 16    | ms   |

| Constant Voltage Sensing Section                                                                   |                                                                                           |                                     |       |       |       |      |

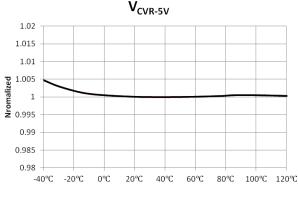

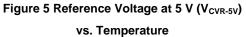

| Reference Voltage at 5 V                                                                           | $V_{IN}$ =5 V, $V_{CS}$ =0 V, $V_{DP}$ =0.6 V, $V_{DN}$ =0 V                              | V <sub>CVR-5V</sub>                 | 0.98  | 1.00  | 1.02  | V    |

| Reference Voltage at 9 V                                                                           | V <sub>IN</sub> =9 V, V <sub>CS</sub> =0 V, V <sub>DP</sub> =0.6 V, V <sub>DN</sub> =0 V  | V <sub>CVR-9V</sub>                 | 1.76  | 1.80  | 1.84  | V    |

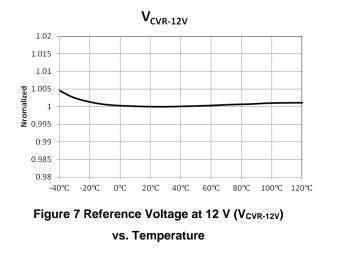

| Reference Voltage at 12 V                                                                          | V <sub>IN</sub> =12 V, V <sub>CS</sub> =0 V, V <sub>DP</sub> =0.6 V, V <sub>DN</sub> =0 V | V <sub>CVR-12V</sub>                | 2.335 | 2.400 | 2.465 | V    |

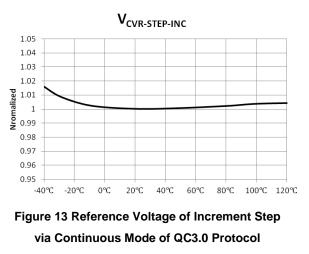

| Reference Voltage of Increment Step via<br>continuous mode of QC3.0 protocol                       | $V_{IN}$ =12 V, $V_{CS}$ =0 V, $V_{DP}$ =0.6 V, $V_{DN}$ =3.3 V                           | $V_{\text{CVR-STEP-INC}}$           | 35    | 40    | 45    | mV   |

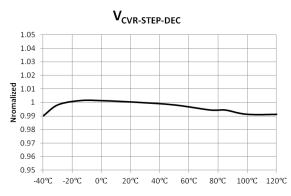

| Reference Voltage of Decrement Step via<br>Continuous Mode of QC3.0 Protocol                       | $V_{IN}$ =12 V, $V_{CS}$ =0 V, $V_{DP}$ =0.6 V, $V_{DN}$ =3.3 V                           | V <sub>CVR-STEP-DEC</sub>           | 35    | 40    | 45    | mV   |

| Reference Voltage Soft-drop Time <sup>(7)</sup>                                                    | During Mode change from V <sub>IN</sub> to Low V <sub>IN</sub> t <sub>CVR-Soft-drop</sub> |                                     |       | 40    |       | ms   |

| Cable Drop Compensation Section                                                                    |                                                                                           |                                     |       | •     |       |      |

| Cable Compensation Voltage <sup>(8)</sup>                                                          | V <sub>CS</sub> =-60 mV                                                                   | V <sub>COMR-CDC</sub>               | 64.5  | 68.0  | 71.5  | mV   |

| OVP Cable Compensation Voltage <sup>(8)</sup>                                                      | V <sub>cs</sub> =-60 mV                                                                   | V <sub>COMR-OVP</sub>               | 360   | 510   | 660   | mV   |

| Constant Current Amplifier Section                                                                 |                                                                                           |                                     |       | •     |       |      |

| Disable Constant Current Amplifier Time during Startup                                             | After V <sub>IN</sub> >V <sub>IN-ON</sub>                                                 | t <sub>Start-Dis-CC</sub>           | 1.3   | 2.5   | 6.0   | ms   |

| Internal Amplifier Transconductance <sup>(7)</sup>                                                 |                                                                                           | Gm <sub>cc</sub>                    |       | 3.5   |       | σ    |

| Internal Amplifier Dominant Pole <sup>(7)</sup>                                                    |                                                                                           | f <sub>P-CC</sub>                   |       | 10    |       | kHz  |

| Internal CC Amplifier Input Resistor                                                               |                                                                                           | R <sub>CC-IN</sub>                  | 8.50  | 13.75 | 19.00 | kΩ   |

| Constant Voltage Amplifier Section                                                                 |                                                                                           | 1                                   |       |       |       |      |

| Internal Amplifier Dominant Pole <sup>(7)</sup>                                                    |                                                                                           | f <sub>P-CV</sub>                   |       | 10    |       | kHz  |

| CV Bias Current <sup>(7)</sup>                                                                     |                                                                                           | I <sub>Bias-CV</sub>                |       |       | 30    | nA   |

| Bleeder Section                                                                                    |                                                                                           | 1                                   |       |       |       |      |

| Voltage difference between GND and CS to enable Bleeding $(I_{O-EN-BLD.typ}=0.42 \text{ A})^{(7)}$ | Decreasing V <sub>cs</sub> , R <sub>cs</sub> =30 m $\Omega$                               | $V_{\text{CS-EN-BLD}}$              | 8     | 12    | 16    | mV   |

| Debounce time to decide enable Bleeding <sup>(7)</sup>                                             | Decreasing V <sub>CS</sub> , R <sub>CS</sub> =30 m $\Omega$                               | t <sub>CS-EN-BLD</sub>              |       | 0.6   | 1.0   | ms   |

| VIN Pin Sink Current through when Bleeding <sup>(7)</sup>                                          | V <sub>IN</sub> =9 V                                                                      | $I_{VIN}$ -Sink                     | 200   |       |       | mA   |

| VIN Pin Internal MOSFET Parasitical Resistor <sup>(7)</sup>                                        |                                                                                           | $R_{DS\_on\_BLD}$                   |       |       | 40    | Ω    |

| Maximum Discharging Time when Bleeding <sup>(7)</sup>                                              | Disabling OVP & SR Gate                                                                   | t <sub>BLD-MAX</sub>                | 275   | 320   | 365   | ms   |

| Feedback Section                                                                                   |                                                                                           |                                     |       |       |       |      |

| Feedback Pin Maximum Sink Current                                                                  |                                                                                           | ISFB-Sink-MAX                       | 2     |       |       | mA   |

# ELECTRICAL CHARACTERISTICS (CONTINUED)

V<sub>IN</sub>=5 V, LPC=1.5 V, LPC width=2 µs at T<sub>J</sub>= -40~125 °C, F<sub>LPC</sub>=100 kHz, unless otherwise specified.

| Parameter                                            | Test Conditions                                   | Symbol                   | Min   | Тур   | Max   | Unit |

|------------------------------------------------------|---------------------------------------------------|--------------------------|-------|-------|-------|------|

| Protocol Section_Quick Charge 2.0 Interfa            | ce                                                | ·                        |       | •     |       |      |

| DP Low Threshold Voltage                             |                                                   | V <sub>DPL</sub>         | 0.24  | 0.25  | 0.28  | V    |

| DP High Threshold Voltage                            |                                                   | V <sub>DPH</sub>         | 1.95  | 2.05  | 2.15  | V    |

| DN Low Threshold Voltage                             |                                                   | V <sub>DNL</sub>         | 0.30  | 0.35  | 0.40  | V    |

| DN High Threshold Voltage                            |                                                   | V <sub>DNH</sub>         | 1.95  | 2.05  | 2.15  | V    |

| DP and DN High Debounce Time                         |                                                   | t <sub>BC1.2</sub>       | 1.0   | 1.2   | 1.4   | S    |

| DP Disconnect Debounce Time                          |                                                   | t <sub>DISCONNECT</sub>  | 5     | 10    | 15    | ms   |

| DN Low Debounce Time, VDN < VDNL                     |                                                   | t <sub>TOGGLE</sub>      |       |       | 1.0   | ms   |

| Mode-Change Debounce Time                            |                                                   | t <sub>V_CHANGE</sub>    | 20    | 40    | 60    | ms   |

| Blanking Time after Mode Change                      |                                                   | t <sub>V_REQUEST</sub>   | 60    |       | 100   | ms   |

| DP Pull Low Resistance                               |                                                   | R <sub>DP</sub>          | 300   | 1120  | 1500  | kΩ   |

| DN Pull Low Resistance                               |                                                   | R <sub>DN</sub>          | 14.25 | 19.53 | 24.80 | kΩ   |

| Protocol Section_Quick Charge 3.0 Interfa            | ce                                                |                          |       |       |       |      |

| Mode-Change Debounce Time                            | V <sub>DP</sub> =0.6, V <sub>DN</sub> =3.3 V      | t <sub>V_CHANGE</sub>    | 20    | 40    | 60    | ms   |

| Mode-Change Debounce Time for<br>Continuous Mode     | For T <sub>ACTIVE</sub> and T <sub>INACTIVE</sub> | t <sub>CONT_CHANGE</sub> | 100   | 150   | 200   | μs   |

| VIN Voltage Range for Continuous Mode <sup>(7)</sup> |                                                   | V <sub>IN_CONT_</sub>    | 3.6   |       | 12    | V    |

# Table 1. Quick Charge 3.0 & 2.0 Output Modes

| Mode   | V <sub>DP</sub> (Тур.) | V <sub>DN</sub> (Тур.) | V <sub>out</sub> |

|--------|------------------------|------------------------|------------------|

| Mode 1 | 0.6 V                  | 0 V                    | 5 V              |

| Mode 2 | 3.3 V                  | 0.6 V                  | 9 V              |

| Mode 3 | 0.6 V                  | 0.6 V                  | 12 V             |

| Mode 4 | 0.6 V                  | 3.3 V                  | Continuous Mode  |

| Mode 5 | 3.3 V                  | 3.3 V                  | Reserved         |

**ELECTRICAL CHARACTERISTICS** (CONTINUED) V<sub>IN</sub>=5 V, LPC=1.5 V, LPC width=2 µs at T<sub>J</sub>= -40~125 °C, F<sub>LPC</sub>=100 kHz, unless otherwise specified.

| V <sub>IN</sub> =5 V, LPC=1.5 V, LPC width=2 µs at T <sub>J</sub> = -40<br>Parameter | Test Conditions                                                  | Symbol                      | Min  | Тур   | Max                | Unit |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|------|-------|--------------------|------|

| Protocol Section_Auto Detection                                                      |                                                                  | •                           |      |       | I                  |      |

| Default DP Voltage when floating                                                     | 2.75 V Supply Mode                                               | V <sub>DP_2.75V</sub>       | 2.65 | 2.75  | 2.85               | V    |

| Default DN Voltage when floating                                                     | 2.75 V Supply Mode                                               | V <sub>DN 2.75V</sub>       | 2.65 | 2.75  | 2.85               | V    |

| DP Pin Output Impedance in Default Mode                                              | 2.75 V Supply Mode                                               | R <sub>DP 2.75V</sub>       | 23   | 28    | 33                 | kΩ   |

| DN Pin Output Impedance in Default Mode                                              | 2.75 V Supply Mode                                               | R <sub>DN_2.75V</sub>       | 23   | 28    | 33                 | kΩ   |

| Increment of VDP for exiting 2.75 V Supply<br>Mode                                   | Increment from $V_{DP_{-2.75V}}$                                 | V <sub>DP_INC</sub>         | 115  | 170   | 225                | mV   |

| Debounce time for exiting 2.75 V Supply<br>Mode                                      |                                                                  | t <sub>EXIT_MODE1</sub>     | 3    | 4     | 5                  | ms   |

| Delay time to recover to 2.75 V Supply Mode                                          | $V_{DP}$ < $V_{DPL}$ in BC1.2 Mode                               | $t_{REC_MODE1}$             | 3    | 4     | 5                  | sec  |

| Dutput Driver Section                                                                |                                                                  |                             |      |       |                    |      |

| Output Voltage Low                                                                   | V <sub>IN</sub> =5 V, I <sub>GATE</sub> =100 mA                  | V <sub>OL</sub>             |      | 0.16  | 0.25               | V    |

| Output Voltage High                                                                  | V <sub>IN</sub> =5 V                                             | V <sub>OH</sub>             | 4.5  |       |                    | V    |

| Rising Time <sup>(7)</sup>                                                           | V <sub>IN</sub> =5 V, C <sub>L</sub> =3300 pF,<br>GATE=1 V ~ 4 V | t <sub>R</sub>              |      | 20    | 35                 | ns   |

| Falling Time <sup>(7)</sup>                                                          | V <sub>IN</sub> =5 V, C <sub>L</sub> =3300 pF,<br>GATE=4 V∼ 1 V  | t <sub>F</sub>              |      | 9     |                    | ns   |

| Propagation Delay to OUT High (LPC<br>Trigger)                                       | V <sub>IN</sub> =5 V, GATE=1 V                                   | t <sub>PD-HIGH-LPC</sub>    |      | 44    | 80                 | ns   |

| Propagation Delay to OUT Low (LPC Trigger) <sup>(7)</sup>                            | V <sub>IN</sub> =5 V, GATE=4 V                                   | t <sub>PD-LOW-LPC</sub>     |      | 30    |                    | ns   |

| Gate Inhibit Time <sup>(7)</sup>                                                     |                                                                  | t <sub>INHIBIT</sub>        |      | 1.4   |                    | μs   |

| Internal RES Section                                                                 |                                                                  |                             |      |       |                    |      |

| Internal RES Ratio <sup>(7)</sup>                                                    | V <sub>IN</sub> =5~12 V                                          | K <sub>RES</sub>            |      | 0.150 |                    | V/V  |

| VIN Dropping Protection Ratio with Two<br>Cycle                                      | LPC Width=5 $\mu s, V_{IN}=5$ V to 3.5 V                         | K <sub>VIN-DROP</sub>       | 70   |       | 90                 | %    |

| Debounce Time for Disable SR when VIN<br>Dropping Protection                         |                                                                  | t <sub>SR_OFF</sub>         | 3.8  | 5.5   | 7.2                | ms   |

| LPC Section                                                                          |                                                                  |                             |      |       |                    |      |

| Linear Operation Range of LPC Pin Voltage <sup>(7)</sup>                             | $V_{\text{IN -OFF}} < V_{\text{IN}} \le 5 \text{ V}$             | V <sub>LPC</sub>            | 0.5  |       | V <sub>IN</sub> -1 | V    |

| LPC Sink Current                                                                     | V <sub>LPC</sub> =1 V                                            | I <sub>LPC-SINK</sub>       |      | 100   |                    | nA   |

| SR Enabled Threshold Voltage @High-Line                                              |                                                                  | V <sub>LPC-HIGH-H</sub>     |      |       | 1.58               | V    |

| Threshold Voltage on LPC Rising Edge<br>@High-Line <sup>(7)</sup>                    | V <sub>LPC-HIGH-H</sub> *0.875=V <sub>LPC-TH-H</sub>             | V <sub>LPC-TH-H</sub>       |      | 1.31  |                    | V    |

| SR Enabled Threshold Voltage @ Low-Line                                              | V <sub>LPC-HIGH-L-5.5V</sub> =V <sub>LPC-TH-L-5.5V</sub> / 0.875 | VLPC-HIGH-L-5.5V            |      |       | 0.86               | V    |

| Threshold Voltage on LPC Rising Edge @ Low-Line <sup>(7)</sup>                       | Spec.=0.45+0.05*V <sub>IN</sub> , V <sub>IN</sub> =5.5 V         | V <sub>LPC-TH-L-5.5V</sub>  |      | 0.725 |                    | V    |

| SR Enabled Threshold Voltage @ Low-Line                                              | V <sub>LPC-HIGH-L-9V</sub> =V <sub>LPC-TH-L-9V</sub> / 0.875     | V <sub>LPC-HIGH-L-9V</sub>  |      |       | 1.06               | V    |

| Threshold Voltage on LPC Rising Edge @ Low-Line <sup>(7)</sup>                       | Spec.=0.45+0.05*V <sub>IN</sub> , V <sub>IN</sub> =9 V           | V <sub>LPC-TH-L-9V</sub>    |      | 0.90  |                    | V    |

| SR Enabled Threshold Voltage @ Low-Line                                              | V <sub>LPC-HIGH-L-12V</sub> =V <sub>LPC-TH-L-12V</sub> / 0.875   | V <sub>LPC-HIGH-L-12V</sub> |      |       | 1.23               | V    |

| Threshold Voltage on LPC Rising Edge @ Low-Line <sup>(7)</sup>                       | Spec.=0.45+0.05*V <sub>IN</sub> , V <sub>IN</sub> =12 V          | V <sub>LPC-TH-L-12V</sub>   |      | 1.05  |                    | V    |

| Falling Edge Threshold Voltage to Trigger SR <sup>(7)</sup>                          |                                                                  | V <sub>LPC-TH-TRIG</sub>    |      | 70    |                    | mV   |

| Low-to-High Line Threshold Voltage on LPC Pin                                        | V <sub>IN</sub> =5.5 V                                           | V <sub>LINE-H-5.5V</sub>    | 1.84 | 1.93  | 2.02               | V    |

# ELECTRICAL CHARACTERISTICS (CONTINUED)

$V_{IN}$ =5 V, LPC=1.5 V, LPC width=2 µs at T<sub>J</sub>= -40~125 °C, F<sub>LPC</sub>=100 kHz, unless otherwise specified.

| Parameter                                                                 | Test Conditions                                                              | Symbol                              | Min                   | Тур  | Max  | Unit |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------|-----------------------|------|------|------|

| LPC Section (continued)                                                   |                                                                              | •                                   |                       |      |      |      |

| High-to-Low Line Threshold Voltage on LPC Pin                             | V <sub>IN</sub> =5.5 V                                                       | V <sub>LINE-L-5.5V</sub>            | 1.75                  | 1.83 | 1.91 | V    |

| Line Change Threshold Hysteresis                                          | VLINE-HYS-5.5V=VLINE-H-5.5V - VLINE-L-5.5V                                   | V <sub>LINE-HYS-5.5V</sub>          |                       | 0.1  |      | V    |

| Low-to-High Line Threshold Voltage on LPC Pin                             | V <sub>IN</sub> =9 V                                                         | V <sub>LINE-H-9V</sub>              | 2.05                  | 2.14 | 2.23 | V    |

| High-to-Low Line Threshold Voltage on LPC Pin                             | V <sub>IN</sub> =9 V                                                         | V <sub>LINE-L-9V</sub>              | 1.96                  | 2.04 | 2.12 | V    |

| Line Change Threshold Hysteresis                                          | VLINE-HYS-9V=VLINE-H-9V - VLINE-L-9V                                         | V <sub>LINE-HYS-9V</sub>            |                       | 0.1  |      | V    |

| Low -to-High Line Threshold Voltage on LPC Pin                            | V <sub>IN</sub> =12 V                                                        | V <sub>LINE-H-12V</sub>             | 2.23                  | 2.32 | 2.41 | V    |

| High-to-Low Line Threshold Voltage on LPC Pin                             | V <sub>IN</sub> =12 V                                                        | V <sub>LINE-L-12V</sub>             | 2.14                  | 2.22 | 2.30 | V    |

| Line Change Threshold Hysteresis                                          | V <sub>LINE-HYS-12V=</sub> V <sub>LINE-H-12V</sub> - V <sub>LINE-L-12V</sub> | V <sub>LINE-HYS-12V</sub>           |                       | 0.1  |      | V    |

| Higher Clamp Voltage                                                      |                                                                              | V <sub>LPC-CLAMP-H</sub>            | 5.4                   | 6.2  | 7.0  | V    |

| LPC Threshold Voltage to Disable SR Gate Switching                        | V <sub>IN</sub> =5 V. LPC=3 V↑                                               | V <sub>LPC-DIS</sub>                | V <sub>IN</sub> - 0.6 |      |      | V    |

| Enable V <sub>LPC-DIS</sub>                                               | Increasing $V_{IN}$                                                          | $V_{\text{EN-LPC-DIS}}$             | 4.30                  | 4.45 | 4.60 | V    |

| Disable V <sub>LPC-DIS</sub>                                              | Decreasing $V_{IN}$                                                          | V <sub>DIS-LPC-DIS</sub>            | 4.10                  | 4.25 | 4.40 | V    |

| Line Change Debounce from Low-Line to<br>High-Line                        |                                                                              | t <sub>LPC-LH-debounce</sub>        | 15                    | 23   | 31   | ms   |

| Line Change Debounce from High-Line to Low-Line <sup>(7)</sup>            |                                                                              | t <sub>LPC-HL-debounce</sub>        |                       | 15   |      | μs   |

| Internal Timing Section                                                   |                                                                              |                                     |                       |      |      |      |

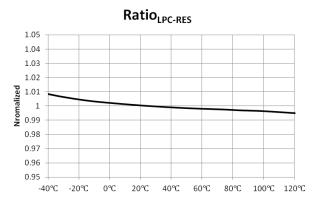

| Ratio between $V_{LPC} \& V_{RES}$                                        | $V_{IN}$ =5.5 V, $F_{LPC}$ =50 kHz, $K_{RES}$ =0.15                          | Ratio <sub>LPC-RES</sub>            | 3.88                  | 4.09 | 4.30 |      |

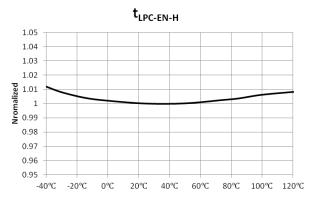

| Minimum LPC Time to Enable the SR Gate<br>@ High-Line                     | V <sub>LPC</sub> =3 V                                                        | t <sub>LPC-EN-H</sub>               | 150                   | 250  | 350  | ns   |

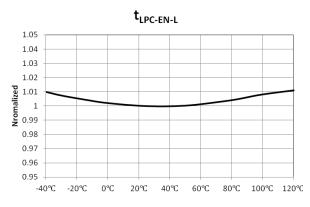

| Minimum LPC Time to Enable the SR Gate<br>@ Low-Line                      | $V_{LPC}$ =1.5 V                                                             | t <sub>LPC-EN-L</sub>               | 520                   | 620  | 720  | ns   |

| Minimum Gate Width <sup>(7)</sup>                                         |                                                                              | t <sub>MIN</sub>                    | 0.35                  | 0.50 | 0.65 | μs   |

| Minimum Gate Limit On-time                                                |                                                                              | t <sub>gate-limit-min</sub>         | 0.6                   | 1.0  | 1.4  | μs   |

| $t_{on-SR}(n+1)$ - $t_{on-SR}(n) < t_{gate-limit}$                        |                                                                              | t <sub>gate-limit</sub>             |                       | 500  |      | ns   |

| Limitation between LPC Rising Edge to<br>next LPC Rising Edge Max. Period |                                                                              | t <sub>MAX-PERIOD</sub>             | 28                    | 40   | 52   | μs   |

| Forced internal CT Reset Time <sup>(7)</sup>                              |                                                                              | t <sub>CT-RESET</sub>               |                       | 10   |      | ns   |

| Reverse Current Mode Section                                              |                                                                              | ·                                   |                       |      |      |      |

| Reverse Current Mode Entry Debounce<br>Time                               | V <sub>IN</sub> =5 V, V <sub>LPC</sub> =0 V                                  | T <sub>reverse-debounce</sub>       | 350                   | 500  | 650  | ms   |

| Operating Current during Reverse Current<br>Mode                          | $V_{IN}$ =5 V, $V_{LPC}$ =0 V                                                | I <sub>OP.reverse</sub>             |                       |      | 1.7  | mA   |

| Data Line Over-Voltage Protection                                         |                                                                              |                                     |                       |      |      |      |

| DP Pin Over-Voltage Protection                                            | Excepting 2.75 V Supply Mode                                                 | V <sub>DP-OVP</sub>                 | 4.10                  | 4.35 | 4.60 | V    |

| DN Pin Over-Voltage Protection                                            | Excepting 2.75 V Supply Mode                                                 | V <sub>DN-OVP</sub>                 | 4.10                  | 4.35 | 4.60 | V    |

| DP/DN Pin OVP Debounce Time                                               | V <sub>DN</sub> > V <sub>DN-SD</sub>                                         | t <sub>DN-DP-OVP-</sub><br>Debounce | 1.5                   | 3.0  | 4.5  | ms   |

Guaranteed by Design.

Guaranteed at -5° ~ 85°C.

# TYPICAL CHARACTERISTICS

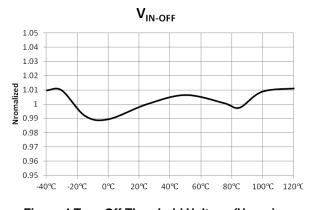

Figure 4 Turn-Off Threshold Voltage (V<sub>IN-OFF</sub>) vs. Temperature

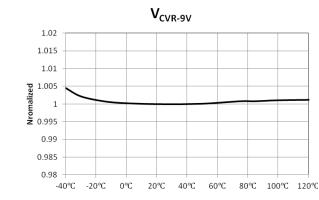

Figure 6 Reference Voltage at 9 V (V<sub>CVR-9V</sub>) vs. Temperature

9 V (V<sub>IN-UVP-L-9V</sub>) vs. Temperature

# **TYPICAL CHARACTERISTICS**

Figure 9 V<sub>IN</sub> Under-Voltage-Protection Enable,

<sup>(</sup>V<sub>CVR-STEP-INC</sub>) vs. Temperature

Figure 10 Minimum LPC Time to Enable the SR Gate @ Low-Line (t<sub>LPC-EN-L</sub>) vs. Temperature

Figure 12 Ratio between V<sub>LPC</sub> & V<sub>RES</sub> (Ratio<sub>LPC-RES</sub>) vs. Temperature

Figure 14 Reference Voltage of Decrement Step via Continuous Mode of QC3.0 Protocol

# (V<sub>CVR-STEP-DEC</sub>) vs. Temperature

# APPLICATIONS INFORMATION

| Table 2. Device Line-up Table |           |           |            |                  |  |  |  |

|-------------------------------|-----------|-----------|------------|------------------|--|--|--|

| Series<br>Name                | Output Vo | UVP       |            |                  |  |  |  |

| Name                          | 3.6~6.0 V | 6.2~9.0 V | 9.2~12.0 V | Operation        |  |  |  |

| FAN6290QF                     | 3.0 A     | 2.0 A     | 1.5 A      | Pull-down<br>SFB |  |  |  |

| FAN6290QH                     | 3.0 A     | 3.0 A     | 2.0 A      | Reduce<br>CC     |  |  |  |

#### Dovice Line-up Table Table 2

FAN6290QF and FAN6290QH implement different operation methods when the UVP is triggered. FAN6290QH reduces constant current level after triggering UVP. When a foldback level is performed on the system, resistive load is normally used. Since this reduced constant current is lower than the resistive load in the UVP, the output voltage is collapsed and foldback can be achieved. FAN6290QF pulls-down the SFB pin after UVP is triggered. And then, it enters Latch Mode Operation (Refer to Figure 22 and Figure 23). According to Latch Mode Operation, the output voltage is collapsed and foldback can be achieved.

#### **Protocols (Auto-detection)**

#### 2.75 V Supply Mode

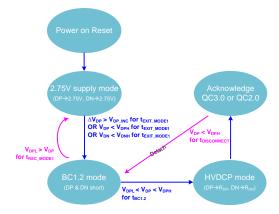

Some Apple products charge higher current when a dedicated charging port sources specific voltage on D+ and D- lines. FAN6290Q supports 2.75 V on D+ and Dlines, respectively. Apple products regard it as the attached charging port supports 2.4A, and it charges with maximum 2.4 A. Once FAN6290Q is enabled, D+ and D- supplies 2.75 V as default. Fairchild intelligent autodetection acknowledges BC1.2. As soon as BC1.2 gets started, FAN6290Q leaves 2.75 V supply mode immediately. After acknowledging QC3.0 or QC2.0, FAN6290Q does not return 2.75 V supply mode as long as a portable device is not detached.

Figure 15 Sequence of Auto-detection

### Quick Charge 3.0 (QC3.0) and Quick Charge 2.0 (QC2.0) Protocols

As described on Table 3, FAN6290Q supports up to 12 V (Class A) through QC3.0 protocol.

| Table 3.   | Output Mode of FAN6290Q according to Quick |

|------------|--------------------------------------------|

| Charge 3.0 |                                            |

| V <sub>DP</sub> | V <sub>DN</sub> | HVDCP Output Mode                             |

|-----------------|-----------------|-----------------------------------------------|

| 0.6 V           | 0 V             | 5 V Mode<br>(Backward compatible with QC2.0)  |

| 3.3 V           | 0.6 V           | 9 V Mode<br>(Backward compatible with QC2.0)  |

| 0.6 V           | 0.6 V           | 12 V Mode<br>(Backward compatible with QC2.0) |

| 0.6 V           | 3.3 V           | Continuous Mode                               |

| 3.3 V           | 3.3 V           | Reserve (Keep previous status)                |

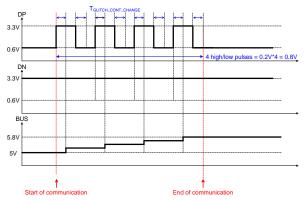

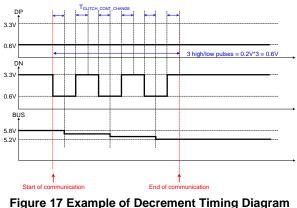

Within continuous mode, output-voltage can be increased or decreased with 200 mV step per an increment or decrement protocol, respectively. (Refer to Figure 16 and Figure 17 which are examples of increment and decrement). FAN6290O can enter continuous mode from any of 5 V, 9 V and 12 V modes. However, it can return to 5 V mode from continuous mode.

Figure 16 Example of Increment Timing Diagram (800 mV Increment from 5 V)

(600 mV Decrement from 5.8 V)

#### **Communication Function Description**

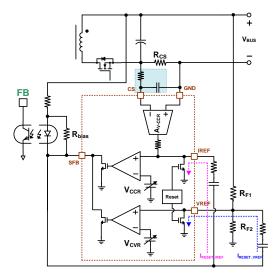

#### **Constant Voltage Control**

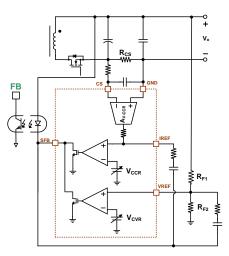

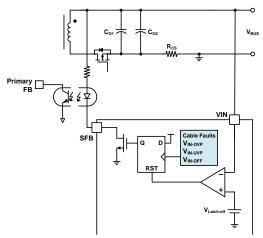

The internal constant voltage control block regulates adaptive output voltages. Output voltage is sensed through an external resistor divider. The sensed output voltage is connected to the VREF which is the noninverting input terminal of the internal operational amplifier. The inverting input terminal is connected to the internal voltage reference  $(V_{CVR})$  which can be adjusted according to the requested output voltage via Quick Charge 3.0 protocol. The amplifier and an internal switch operate as a shunt regulator. The output of the shunt regulator is connected to the external opto-coupler. and this pin is named as Secondary Feedback (SFB). To compensate output voltage regulation being stable, one capacitor and one resistor are connected typically between the SFB and VREF pins as shown in Figure 18. The output voltage can be derived as shown in equation (1) and the recommended ratio of the resistor divider is 5.

$$V_{O} = V_{CVR} \cdot \frac{R_{F1} + R_{F2}}{R_{F2}}$$

(1)

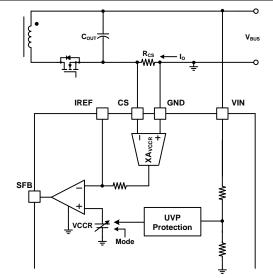

#### **Constant Current Control**

In order to support adaptive constant output current, FAN6290Q incorporates the constant-current control circuit internally. Output current is sensed via a currentsense resistor,  $R_{CS}$ , which is connected between the CS pin and GND pin. The sensed signal is internally amplified, and this amplified voltage is connected to the non-inverting input of the internal operation amplifier. Likewise the constant voltage amplifier circuit, it also plays a role as a shunt regulator to regulate the constant output current. In order to compensate output current regulation, one capacitor and one resistor are connected between IREF and SFB pins typically as the Figure 18. The constant output current is decided by the equation (2). 30 m $\Omega$  is typically used for the sense resistor.

$$I_{O\_CC} = \frac{1}{A_{V-CCR}} \cdot \frac{V_{CCR}}{R_{CS}}$$

(2)

Since CS pin senses small amounts of voltage, the sensing resistor should be positioned as close as possible to CS pin. Shown in Figure 18, an RC low pass filter can be added on the CS pin to be immunized from noise.

Figure 18 Constant Voltage and Constant Current Circuit

#### **Green Mode Operation**

In order to reduce power consumption at light-load conditions, FAN6290Q enters the green mode. When  $V_{CS}$  which is the voltage between CS and GND pins is smaller than  $V_{CS-Green}$  with longer duration than  $t_{Green-EN-Debounce}$ , FAN6290Q enters the green mode. Typical output current entering the green mode is 170 mA. While it operates in the green mode, some internal blocks are disabled such as Synchronous Rectifier control block. Therefore, the operating current can be reduced to 1.2 mA (typ.). It leaves green mode when  $V_{CS}$  is larger than  $V_{CS-Green}$  with longer duration that  $t_{Green-DIS-Debounce}$ .

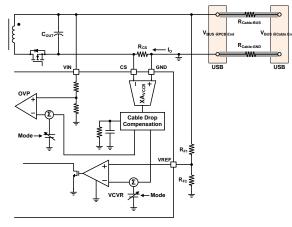

# **Cable Drop Compensation**

To regulate the output voltage constantly at the end of a cable regardless of output current, the cable drop compensation function is implemented. The weight of compensation is internally fixed. The compensated output voltage is described in equation (3).

$$V_{OUT-COMPENSATION} = V_{COMR-CDC} \cdot \frac{R_{F1} + R_{F2}}{R_{F2}} \cdot \frac{I_{OUT}}{2}$$

(3)

Output OVP also implements cable drop compensation. Ratio of cable drop compensation for output OVP is different with cable drop compensation for constant voltage regulation shown in equation (4).

$$V_{OVP} = V_{IN-OVP} + V_{COMR-OVP} \cdot \frac{I_{OUT}}{2}$$

(4)

Figure 19 Cable-Drop Compensation Block

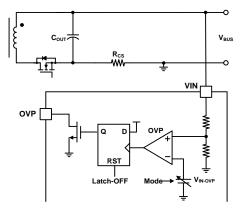

# **Output Over-Voltage Protection**

Figure 20 shows the output Over-Voltage Protection (OVP) block, which is adaptive according to output voltage status. Once the sensed output voltage via VIN pin is larger than  $V_{IN-OVP}$  longer than  $t_{D-OVP}$ , the internal OVP switch is enabled with latch mode. And the latch mode of FAN6290Q is reset when  $V_{IN} < V_{LATCH-OFF}$ . When FAN6290Q is compatible with FAN602,  $V_{S-UVP}$  of FAN602 can be triggered after releasing latch mode of FAN6290Q. According to protection mode of  $V_{S-UVP}$  of FAN602,  $V_{IN-OVP}$  of FAN6290Q is operated as Extended Auto-Restart mode or latch mode.

| Symbol       | V <sub>out</sub> Range | OVP Level (Typ.) |

|--------------|------------------------|------------------|

| VIN-OVP-5 V  | 3.6 V ~ 5.0 V          | 6.0 V            |

| VIN-OVP-6 V  | 5.2 V ~ 6.0 V          | 8.4 V            |

| VIN-OVP-9 V  | 6.2 V ~ 9.0 V          | 10.8 V           |

| VIN-OVP-12 V | 9.2 V ~ 12.0 V         | 14.4 V           |

Figure 20 Output Over-Voltage Protection Block

### **Output Under-Voltage Protection**

In order to support foldback level of each output mode, the output Under-Voltage Protection (UVP) function is incorporated. The UVP function can reduce power delivery during output soft-short fault. Figure 21 shows its implementation. Once VIN voltage is lower than  $V_{IN-1}$

$_{\rm UVP-L}$  longer than t<sub>D-VIN-UVP</sub>, the constant current level is reduced to 220 mA (typ.). FAN6290Q leaves UVP when VIN voltage is higher than V<sub>IN-UVP-H</sub>. While the UVP is operated, the synchronous rectifier control is disabled to avoid shoot-through. Some option versions enter the latch mode instead of reducing output current after triggering UVP. The UVP function is only enabled when QC2.0 protocol is accepted. For QC3.0 mode, UVP function is disabled.

| Table 3. | Under-Voltage | Protection | Threshold Level |

|----------|---------------|------------|-----------------|

| Tuble 0. | Under Voltage | 1101001011 |                 |

| Symbol                    | V <sub>out</sub> Range | UVP Level (Typ.) |

|---------------------------|------------------------|------------------|

| VIN-UVP-L-9V              | 9 V of QC2.0           | 5.50 V           |

| VIN-UVP-H-9V              | 9 0 0 002.0            | 6.00 V           |

| V <sub>IN-UVP-L-12V</sub> | 12 V of QC2.0          | 8.00 V           |

| V <sub>IN-UVP-H-12V</sub> |                        | 8.50 V           |

#### Figure 21 Output Under-Voltage Protection Block

# D+/D- Data Line Over-Voltage Protection

Even though severe fault is occurred between BUS and Ground, monitoring data line status also can protect USB fault condition indirectly because data lines (D+/D-) may be polluted at the same time with BUS line pollution. Therefore, FAN6290Q implements data line Over-Voltage-Protection. It can protect when the BUS and D+/D- are short-circuited with small impedance. When voltage on D+ line and/or D- line is higher than  $V_{DP-OVP}$  and/or  $V_{DP-OVP}$  longer than  $V_{DN-DP-OVP-Debounce}$ , Over-Voltage Protection is triggered. After detecting fault condition, FAN6290Q enters latch mode. When FAN6290Q releases the latch mode, FAN602 enters VS-UVP.

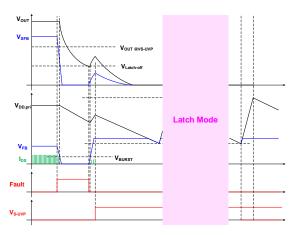

#### Latch Mode Operation

FAN6290Q implements latch mode operation to deliver fault conditions which are detected on secondary-side to primary-side. When one fault condition is triggered among cable fault Protections, over-voltage protection and under-voltage protection, SFB is started to be

pulled-down with latch mode. This latch mode is released when VIN voltage is lower than V<sub>Latch-off</sub> which is lower than V<sub>IN-OFF</sub>. As shown on Figure 23, after the Latch Mode is released, the primary-side controller leaves burst mode and starts switching again. Since the V<sub>Latch-off</sub> is much lower than output voltage level which triggers V<sub>S-UVP</sub> of the primary-side controller, after releasing latch mode, the primary-side controller triggers  $V_{S-UVP}$ . Therefore, throughout implementing the latch mode operation, the primary-side controller can trigger  $V_{S-UVP}$ , and the system can enter latch mode. When not only V<sub>IN-OVP</sub> and cable fault protection are triggered, but also VIN voltage is lower than  $V_{IN-OFF}$ , the latch mode is enabled, either. The latch mode operation for  $V_{IN-OFF}$ avoids that system becomes open-loop when  $V_{IN} < V_{IN-}$ OFF.

Figure 22 Conceptual Latch Mode Block

Figure 23 Waveform of Latch Mode Operation

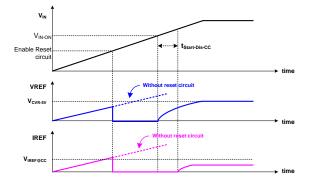

#### **Reset Circuit on VREF and IREF**

VREF and IREF pins are connected to  $V_{IN}$  through compensation circuits. When CV and CC amplifiers are not enabled, VREF and IREF pin voltages are also increased according to increased V<sub>IN</sub> voltage (dot lines on Figure 24). The voltages on VREF and IREF are higher than target threshold levels. The Reset circuit on VREF and IREF are implemented as each pin is connected to ground through internal switches. The IREF pin is additionally reset during t<sub>Start-Dis-CC</sub>. Reset circuit pulls-down current, and these currents (IRESET VREF and IRESET IREF) can flow through compensation circuits. If current flowing through the opto-coupler is large enough, the primary controller enters burst mode and triggers VS-UVP-H, because of this startup may fail. Rbias helps to decrease current flowing through the opto-coupler, to avoid startup failure. The Rbias design depends on compensation design, typically  $2 \sim 6 \ k\Omega$  is recommended.

**Figure 24 Reset Circuit Operation**

Figure 25 Reset Circuit and R<sub>bias</sub>

# **PCB Layout Guidelines**

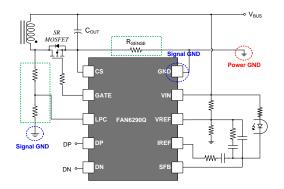

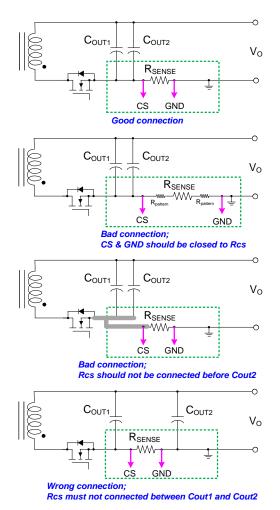

Printed Circuit Board (PCB) layout and design are very important for switching mode power supplies where the voltage and current change with high speed. Good PCB layout minimizes Electro-Magnetic Interference (EMI) and prevents excessive noise from surge or Electro-Static Discharging (ESD). As shown in Figure 27  $C_{OUT1}$  and  $C_{OUT2}$  are the output capacitors;  $Q_2$  is the secondary-side SR MOSFET. The following guidelines are recommended for layout designs.

- The main power flows through Q2, C<sub>OUT1</sub>, C<sub>OUT2</sub> and R<sub>CS</sub>. This power path should be separated with signal grounds which are connected to FAN6290Q. In addition, it is recommended that power ground is directly connected to Y-cap. Refer to Figure 26.

- The sensed voltage via R<sub>CS</sub> is very small value. In order to avoid offset voltage or avoid inducing switching noise on the sensed voltage, R<sub>CS</sub> should be connected between ground of C<sub>OUT2</sub> and power ground. And R<sub>CS</sub> should be positioned as close as possible to CS pin and GND pin. Refer to Figure 27.

- To avoid switching noise interference to Synchronous Rectifier operation, R<sub>LPC-H</sub> and R<sub>LPC-L</sub> should be close to FAN6290Q. And power path should be apart from LPC path.

Figure 26 Power and Signal Ground on the Secondary-Side

Figure 27 Examples of Sensing Resistor Connection

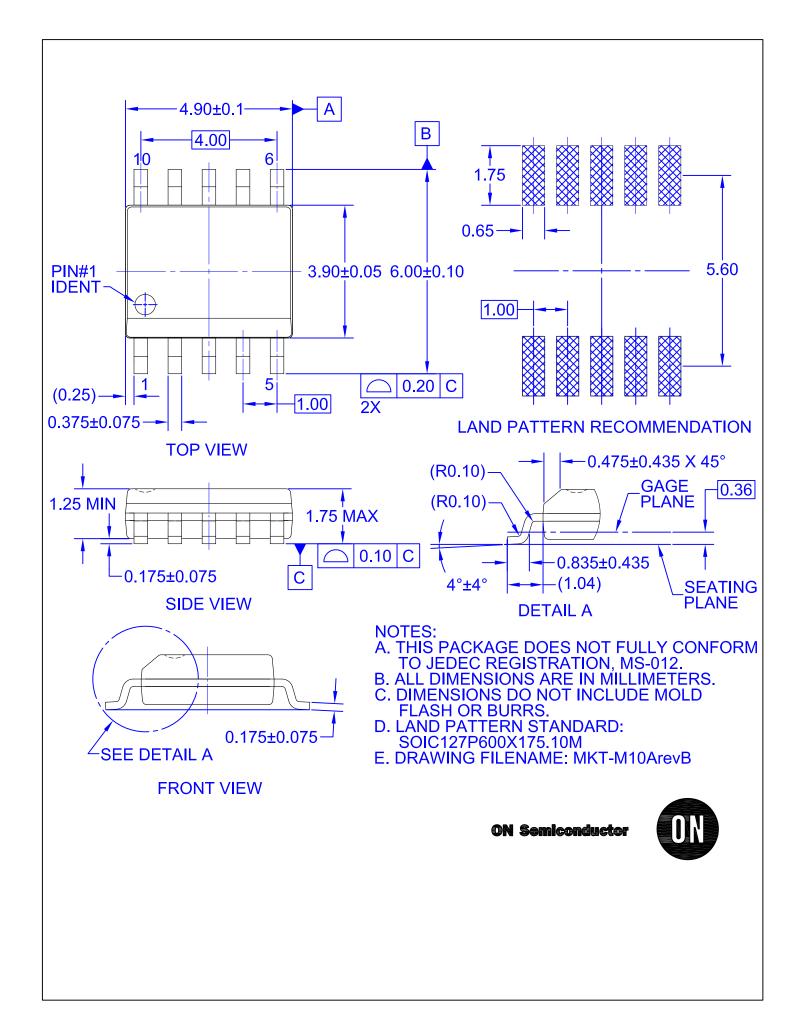

# ORDERING INFORMATION

| Part Number | Operating<br>Temperature Range | Package      | Packing Method |

|-------------|--------------------------------|--------------|----------------|

| FAN6290QFMX | -40°C to +125°C                | 10-Lead, SOP | Tape & Reel    |

| FAN6290QHMX | -40°C to +125°C                | 10-Lead, SOP | Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC