Is Now Part of

# **ON Semiconductor**®

# To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to <a href="mailto:Fairchild\_questions@onsemi.com">Fairchild\_questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized applications, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an equif prese

#### June 2015

# **FAN8841 Dual Half-Bridge Piezoelectric Driver with Step-up DC-DC Converter**

# Features

#### Step-up DC-DC Converter

- Integrated Step-up Power Switch up to 36 V

- Wide Operating Voltage Range of 2.7 to 5.5 V

- Adjustable Step-up Output Voltage by VCON

- . Adjustable Step-up Switch Current Limit

- Zero Current Detector (ZCD)

- Internal Soft-Start

- **Built-in Protection Circuit**

- Under-Voltage Protection (UVP)

- Over-Voltage Protection (OVP)

#### **Piezo Actuator Driver**

- Integrated Half-Bridge Switches (V<sub>DS</sub>=75 V)

- Dual Half-Bridge Piezoelectric Driver

- **Built-in Shutdown Function**

#### **Package Information**

Small 4.0 mm × 4.0 mm MLP

# **Applications**

**Piezoelectric Actuator**

# Description

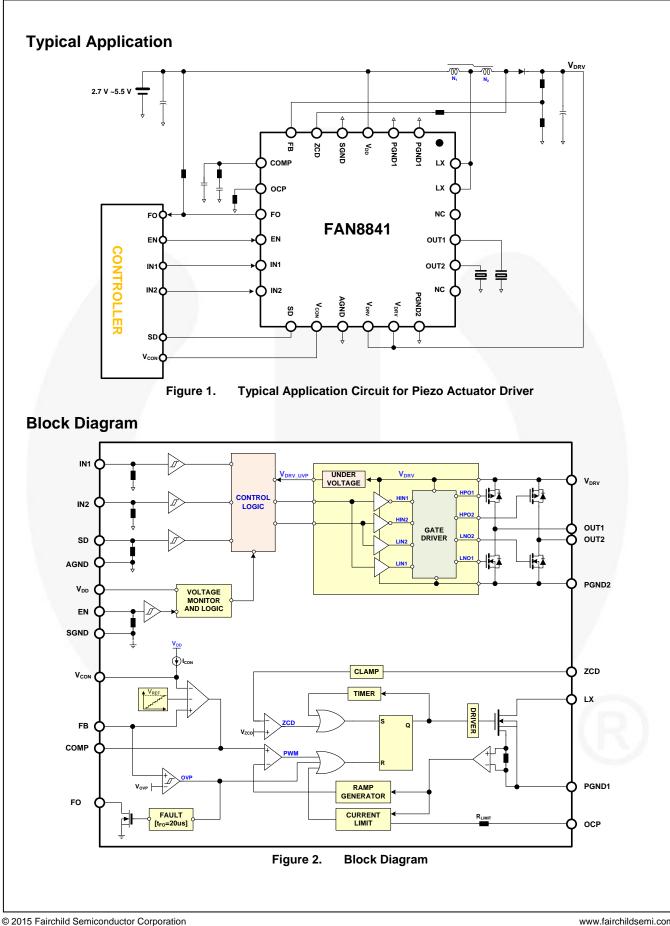

The FAN8841 is a single-chip piezoelectric actuator driver consisting of a step-up DC-DC converter with integrated 36 V boost switch and the dual half-bridge output stages. The step-up DC-DC converter operates in Critical Conduction Mode (CRM) in order to reduce switching loss at the DC-DC converter for high efficiency. It is optimized to work in a coupled-inductor configuration to provide output voltages in excess of 60 V. The step-up DC-DC converter has a soft-start capability that limits the inrush current during startup. Over-voltage protection and over-current protection are included. Under-voltage protection is used to disable the dual half-bridge gate driver when the step-up DC-DC converter output voltage is lower than the specified threshold voltage. The boost voltage is set using external resistors and analog voltage at the V<sub>CON</sub> pin and step-up current limit is programmable via the external resistor at the OCP pin. The output Half-bridge is integrated with 75 V P- and N-channel for the piezoelectric actuator driving. An open drain Fault-out (FO) signal indicates if an abnormal over-voltage has occurred.

| Ordering Information |                                |                                                           |                |  |  |  |

|----------------------|--------------------------------|-----------------------------------------------------------|----------------|--|--|--|

| Part Number          | Operating<br>Temperature Range | Package                                                   | Packing Method |  |  |  |

| FAN8841MPX           | -40°C to +125°C                | 24-Lead, 4.0 mm × 4.0 mm Molded Leadless<br>Package (MLP) | Tape & Reel    |  |  |  |

FAN8841 • Rev. 1.0

FAN8841 — Dual Half-Bridge Piezoelectric Driver with Step-up DC-DC Converter

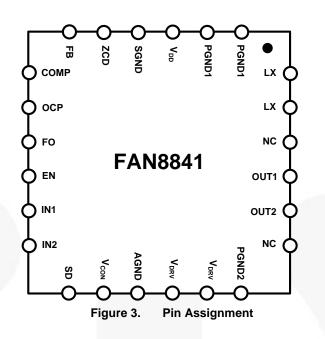

# **Pin Configuration**

# **Pin Definitions**

| Pin #  | Name             | Description                                                                   |  |  |  |

|--------|------------------|-------------------------------------------------------------------------------|--|--|--|

| 1, 2   | PGND1            | Power Ground 1. It is connected to the source of the step-up switch.          |  |  |  |

| 3      | V <sub>DD</sub>  | wer supply of step-up DC-DC converter.                                        |  |  |  |

| 4      | SGND             | nal Ground. The signal ground for step-up DC-DC converter circuitry.          |  |  |  |

| 5      | ZCD              | The input of the Zero Current Detection                                       |  |  |  |

| 6      | FB               | Step-up DC-DC converter output voltage feedback input.                        |  |  |  |

| 7      | COMP             | Output of the transconductance error amplifier.                               |  |  |  |

| 8      | OCP              | Sets Step-up DC-DC converter current limit                                    |  |  |  |

| 9      | FO               | Fault Output.                                                                 |  |  |  |

| 10     | EN               | Enable pin to turn on and off the overall system. (Active Low Shutdown Mode). |  |  |  |

| 11     | IN1              | Logic input for Half-Bridge 1                                                 |  |  |  |

| 12     | IN2              | Logic input for Half-Bridge 2                                                 |  |  |  |

| 13     | SD               | Shutdown input for H-Bridge 1 and 2. (Active Low Shutdown Mode).              |  |  |  |

| 14     | V <sub>CON</sub> | Control input for output voltage of step-up DC-DC converter                   |  |  |  |

| 15     | AGND             | Analog Ground. The signal ground for H-bridge driver circuitry                |  |  |  |

| 16, 17 | V <sub>DRV</sub> | Power supply of each H-bridge driver                                          |  |  |  |

| 18     | PGND2            | Power Ground 2. The power ground for Half-bridge driver                       |  |  |  |

| 19     | NC               | Not Connected                                                                 |  |  |  |

| 20     | OUT2             | Output for Half-bridge 2                                                      |  |  |  |

| 21     | OUT1             | Output for Half-bridge 1                                                      |  |  |  |

| 22     | NC               | Not Connected                                                                 |  |  |  |

| 23, 24 | LX               | Switch Node. This pin is connected to the inductor.                           |  |  |  |

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Para                                           | Min.                                  | Max. | Unit                 |      |  |

|------------------|------------------------------------------------|---------------------------------------|------|----------------------|------|--|

| V <sub>DRV</sub> | DC Link Input Voltage Drain-Source             | Voltage of each MOSFET                |      | 75                   | V    |  |

| V <sub>DD</sub>  | DC Supply Voltage for DC-DC Conv               | verter                                | -0.3 | 5.5                  | V    |  |

| VINPUT           | EN, SD, IN1, IN2, FB and COMP to               | SGND and AGND                         | -0.3 | V <sub>DD</sub> +0.3 | V    |  |

| V <sub>CON</sub> | V <sub>CON</sub> to SGND                       |                                       | -0.3 | V <sub>DD</sub> +0.3 | V    |  |

| V <sub>LX</sub>  | LX to PGND                                     |                                       | -0.3 | 40                   | V    |  |

|                  | Power Dissipation <sup>(2)</sup>               | 1S0P with thermal vias <sup>(3)</sup> |      | W                    |      |  |

| PD               |                                                | 1S2P with thermal vias <sup>(4)</sup> |      | 2.9                  | VV   |  |

| 0                |                                                | 1S0P with thermal vias <sup>(3)</sup> |      | 127                  | 0000 |  |

| $\theta_{JA}$    | Thermal Resistance Junction-Air <sup>(1)</sup> | 1S2P with thermal vias <sup>(4)</sup> |      | 43                   | °C/W |  |

| TA               | Operating Ambient Temperature Ra               | inge                                  | -40  | 125                  | °C   |  |

| TJ               | Operating Junction Temperature                 |                                       | -55  | 150                  | °C   |  |

| T <sub>STG</sub> | Storage Temperature Range                      |                                       | -55  | 150                  | °C   |  |

|                  |                                                | Human Body Model, JESD22-A114         |      | 2                    | KV   |  |

| ESD              | Electrostatic Discharge Capability             | Charged Device Model,<br>JESD22-C101  |      | 500                  | V    |  |

#### Notes:

1. All voltage values, except differential voltages, are given with respect to SGND, AGND and PGND pin.

2. JEDEC standard: JESD51-2, JESD51-3. Mounted on 76.2 x 114.3 x1.6 mm PCB (FR-4 glass epoxy material).

3. 1S0P with thermal via: one signal layer with zero power plane and thermal via.

4. 1S2P with thermal via: one signal layer with two power plane and thermal via.

# **Recommended Operating Conditions**

The Recommended Operating Conditions table defines the conditions for actual device operation. Recommended operating conditions are specified to ensure optimal performance. Fairchild does not recommend exceeding them or designing to Absolute Maximum Ratings.

| Symbol           | Parameter                                 | Min. | Max.            | Unit |

|------------------|-------------------------------------------|------|-----------------|------|

| V <sub>DRV</sub> | Supply Voltage for Half-Bridge Driver     | 13   | 60              | V    |

| $V_{LX}$         | Boost Switch Voltage                      |      | 36              | V    |

| V <sub>CON</sub> | Output Voltage Control of DC-DC Converter | 0.1  | V <sub>DD</sub> | V    |

| $V_{\text{DD}}$  | Operating Voltage for DC-DC Converter     | 2.8  | 5.0             | V    |

| R <sub>OCP</sub> | Current Limit Control Resistor            | 3.3  | 150             | kΩ   |

# **Electrical Characteristics**

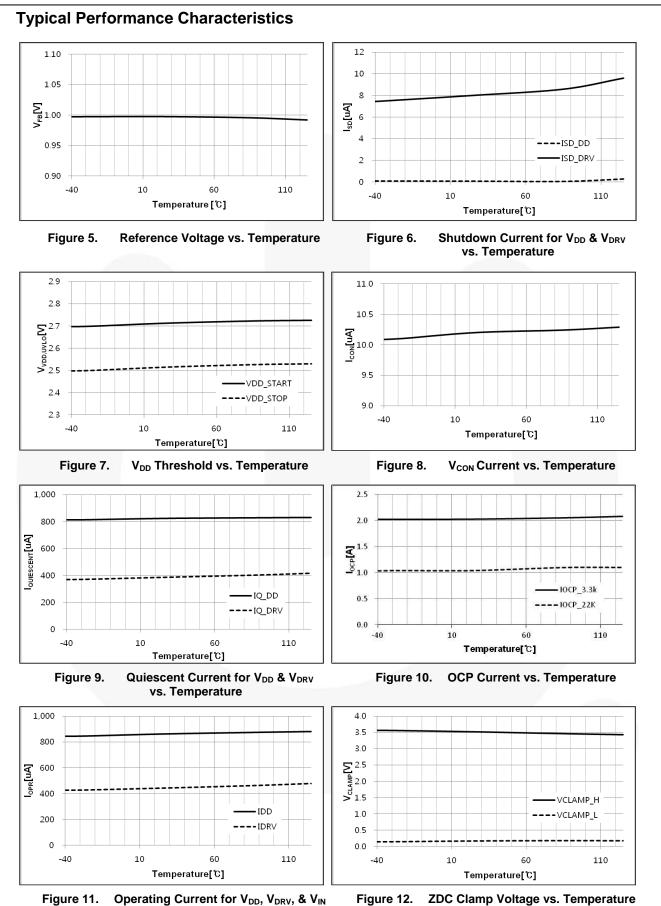

V<sub>DD</sub>=3.0 V, V<sub>DRV</sub>=60 V, and T<sub>A</sub>= -40°C to +125°C. Typical values T<sub>A</sub>=25°C, unless otherwise specified.

| Symbol               | Parameter Conditions                                 |                                                                 | Min.  | Тур. | Max. | Unit    |

|----------------------|------------------------------------------------------|-----------------------------------------------------------------|-------|------|------|---------|

| Power Sup            | ply Section                                          |                                                                 |       |      |      | <u></u> |

| I <sub>Q,DD</sub>    | Quiescent Current for V <sub>DD</sub> <sup>(5)</sup> | V <sub>EN</sub> =V <sub>COMP</sub> =V <sub>DD</sub> ,           |       | 800  | 1200 | μA      |

| I <sub>Q,DRV</sub>   | Quiescent Current for VDRV                           | V <sub>FB</sub> =1.0 V, V <sub>IN1</sub> =V <sub>IN2</sub> =0 V |       | 400  | 800  | μA      |

| I <sub>SD,DD</sub>   | Shutdown Current for V <sub>DD</sub>                 | V <sub>EN</sub> =0 V,                                           |       |      | 1    | μA      |

| I <sub>SD,DRV</sub>  | Shutdown Current for V <sub>DRV</sub>                | V <sub>DD</sub> = V <sub>DRV</sub> =3 V                         |       | 8    | 15   | μA      |

| V <sub>DDSTART</sub> | Start Threshold Voltage                              |                                                                 | 2.6   | 2.7  | 2.8  | V       |

| V <sub>DDUVHYS</sub> | V <sub>DD</sub> UVLO Hysteresis Voltage              |                                                                 | 0.10  | 0.2  |      | V       |

| Error Ampl           | ifier Section                                        |                                                                 |       | •    | •    |         |

| $V_{FB}$             | Feedback Reference Voltage                           | T <sub>A</sub> =25°C                                            | 0.99  | 1.00 | 1.01 | V       |

| I <sub>FB</sub>      | FB pin Bias Current                                  | V <sub>FB</sub> =0 V ~ 2 V                                      |       |      | 1    | μA      |

| $\Delta V_{FB1}$     | Feedback Voltage Line Regulation <sup>(6)</sup>      | $2.7 \text{ V} < \text{V}_{\text{DD}} < 5 \text{ V},$           |       | 0.5  | 1.5  | %/V     |

| Gm                   | Transconductance                                     | T <sub>A</sub> =25°C                                            |       | 800  |      | µmho    |

| Zero Curre           | nt Detect Section                                    |                                                                 |       |      |      |         |

| V <sub>ZCD</sub>     | Input Voltage Threshold <sup>(7)</sup>               |                                                                 | 1.65  | 1.83 | 2.00 | V       |

| V <sub>CLAMPH</sub>  | Input High Clamp Voltage                             | I <sub>DET</sub> =2.3 mA                                        | 3.0   | 3.5  | 4.0  | V       |

| V <sub>CLAMPL</sub>  | Input Low Clamp Voltage                              | I <sub>DET</sub> = -2.3 mA                                      | -0.30 | 0.12 | 0.50 | V       |

| I <sub>ZCD,SR</sub>  | Source Current Capability                            |                                                                 |       |      | -2.3 | mA      |

| I <sub>ZCD,SK</sub>  | Sink Current Capability                              |                                                                 |       |      | 2.3  | mA      |

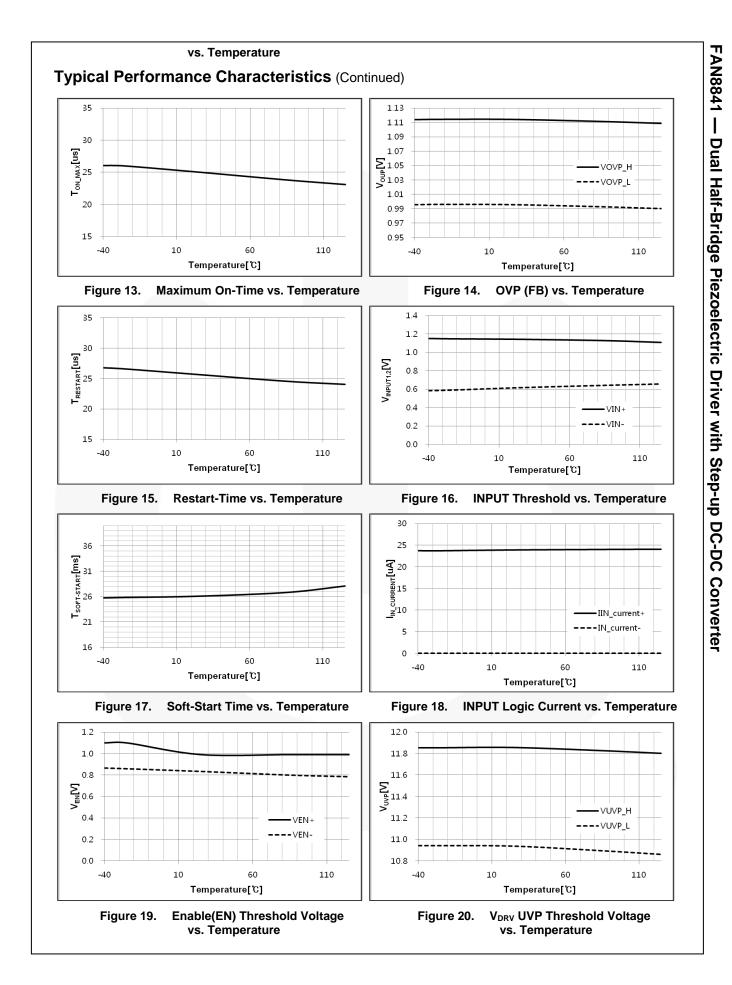

| t <sub>ZCD,D</sub>   | Delay From ZCD to Output Turn-On <sup>(7)</sup>      |                                                                 |       | 50   | 200  | ns      |

| Maximum (            | On-Time Section                                      |                                                                 |       |      |      |         |

| t <sub>ON,MAX</sub>  | Maximum On-Time                                      |                                                                 | 15    | 25   | 35   | μs      |

| Soft-Start 1         | Timer Section                                        |                                                                 |       |      | •    |         |

| t <sub>SS</sub>      | Internal Soft-Start                                  |                                                                 | 16    | 28   | 40   | ms      |

| Restart / Ma         | aximum Switching Frequency Limit Sec                 | ction                                                           |       |      |      |         |

| t <sub>RST</sub>     | Restart Timer                                        |                                                                 | 15    | 25   | 35   | μs      |

| f <sub>MAX</sub>     | Maximum Switching Frequency <sup>(7)</sup>           |                                                                 |       | 900  | 1000 | KHz     |

Notes:

5. This is only the V<sub>DD</sub> current consumption with no switching condition. It does not include gate-drive current.

6. The line regulation is calculated based on  $\frac{\Delta V_{\scriptscriptstyle OUT}}{\Delta V_{\scriptscriptstyle I\!N}} \times \frac{1}{V_{\scriptscriptstyle OUT}}$

7. This parameter, although guaranteed by design, is not tested in production.

# **Electrical Characteristics**

$V_{DD}$ =3.0 V,  $V_{DRV}$ =60 V, and  $T_{A}$ = -40°C to +125°C. Typical values  $T_{A}$ =25°C, unless otherwise specified.

| Symbol              | Parameter                                            | Conditions                                       | Min. | Тур. | Max. | Unit     |

|---------------------|------------------------------------------------------|--------------------------------------------------|------|------|------|----------|

| Current Lin         | nit Comparator Section                               |                                                  |      |      | 1    | <u> </u> |

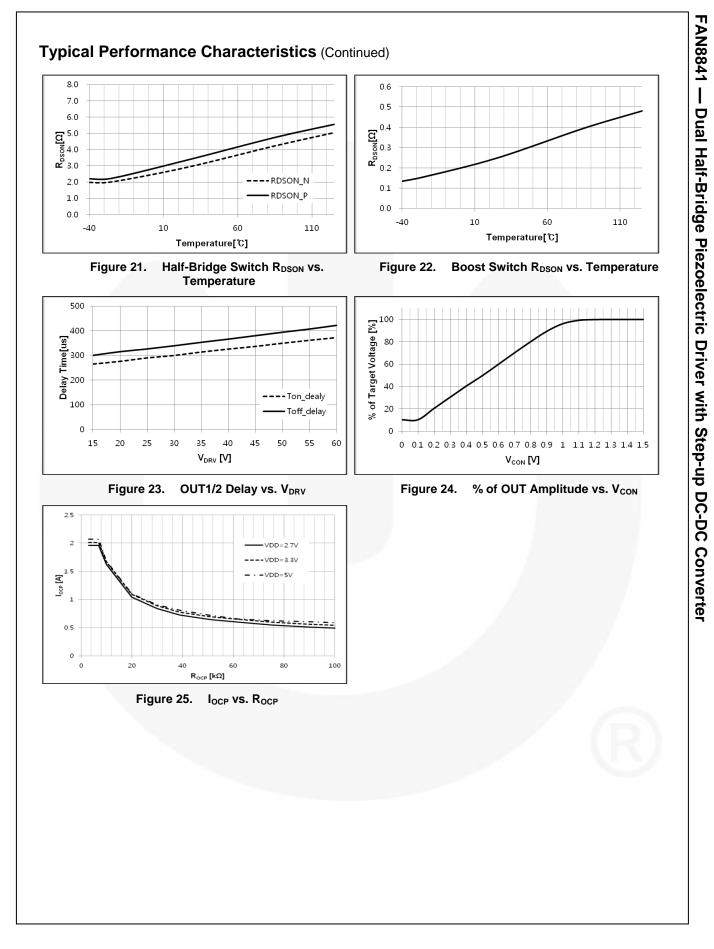

|                     |                                                      | R <sub>OCP</sub> =3.3 KΩ, V <sub>DD</sub> =3.3 V | 1.85 | 2.00 | 2.15 | Α        |

| IOCP                | OCP Trip Current                                     | R <sub>OCP</sub> =22 KΩ, V <sub>DD</sub> =3.3 V  | 0.9  | 1.0  | 1.1  | Α        |

| tcs_blank           | Comparator Leading-Edge Blanking Time <sup>(8)</sup> |                                                  | 80   | 130  | 180  | ns       |

| Step-up Ou          | tput Control Section                                 |                                                  |      |      | •    |          |

| I <sub>CON</sub>    | Internal Current Source for V <sub>CON</sub> Pin     |                                                  | 9.0  | 10   | 11   | μA       |

| V <sub>CON+</sub>   | Positive Going Threshold Voltage <sup>(8)</sup>      | T <sub>A</sub> =25°C                             |      | 1.0  |      | V        |

| V <sub>CON-</sub>   | Negative Going Threshold Voltage <sup>(8)</sup>      |                                                  |      | 0.1  |      | V        |

| Step-up Sw          | vitch Section                                        |                                                  |      |      |      |          |

| R <sub>DSON</sub>   | N-Channel On Resistance                              | V <sub>DD</sub> =3.3 V, T <sub>A</sub> =25°C     |      | 0.2  | 0.5  | Ω        |

| I <sub>LK_LX</sub>  | LX Leakage Current                                   | V <sub>LX</sub> =36 V                            |      |      | 1.0  | μA       |

| Logic (EN,          | IN1,IN2, SD) Section                                 |                                                  |      |      |      |          |

| V <sub>INPUT+</sub> | Input Logic High Threshold Voltage                   |                                                  | 1.34 |      |      | V        |

| VINPUT-             | Input Logic Low Threshold Voltage                    |                                                  |      |      | 0.5  | V        |

| I <sub>INPUT-</sub> | Input Low Current                                    | V <sub>EN</sub> =0 V                             |      |      | 1    | μA       |

| I <sub>INPUT+</sub> | Input High Current                                   | V <sub>EN</sub> =V <sub>DD</sub>                 | 16   | 24   | 32   | μA       |

| RINPUT              | Input Logic Pull-Down Resistance                     | V <sub>EN</sub> =V <sub>INPUT</sub> =3 V         |      | 125  |      | KΩ       |

| Full-Bridge         | Switch Section                                       |                                                  |      |      |      |          |

| R <sub>DS,ONP</sub> | Output Upper-Side On Resistance                      | T 0500                                           |      | 3.0  | 5.0  | Ω        |

| R <sub>DS,ONN</sub> | Output Low-Side On Resistance                        | T <sub>A</sub> =25°C                             |      | 3.0  | 5.0  | Ω        |

| t <sub>ON</sub>     | Turn-on Propagation Delay Time                       |                                                  |      | 300  |      | ns       |

| t <sub>OFF</sub>    | Turn-off Propagation Delay Time                      | V <sub>DRV</sub> =30 V, T <sub>A</sub> =25°C     |      | 330  |      | ns       |

| Protection          | (UVP, and OVP )                                      |                                                  |      |      |      |          |

| VUVP                | Under-Voltage Threshold of DC-DC Con.                |                                                  | 11   | 12   | 13   | V        |

| HYUVP               | Under-Voltage Hysteresis                             |                                                  |      | 1.0  |      | V        |

| V <sub>OVP</sub>    | OVP Threshold Voltage                                | ]                                                | 1.05 | 1.10 | 1.15 | V        |

| HYOVP               | OVP Hysteresis Voltage                               |                                                  |      | 0.1  |      | V        |

| t <sub>FO</sub>     | Fault Output Duration                                |                                                  |      | 20   | 30   | μs       |

| V <sub>FOL</sub>    | Fault Output Low Level voltage                       | R <sub>PU</sub> =50 KΩ, V <sub>PU</sub> =3 V     |      | 0.1  | 0.4  | V        |

Note:

8. This parameter, although guaranteed by design, is not tested in production.

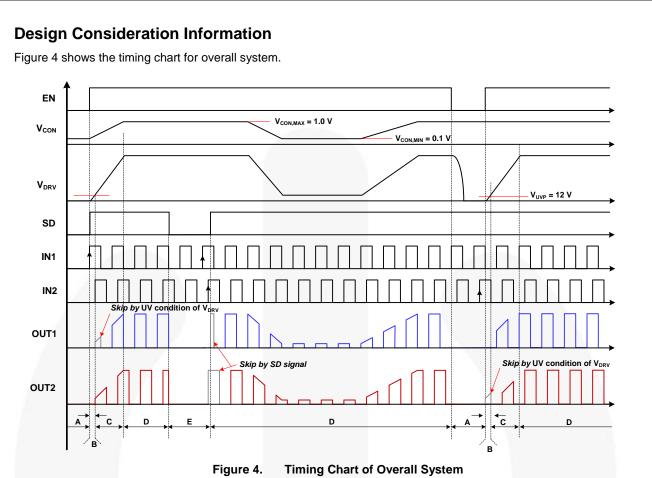

| Input |     |    | Output |      | Mode |       |                      |  |  |

|-------|-----|----|--------|------|------|-------|----------------------|--|--|

| IN1   | IN2 | EN | SD     | OUT1 | OUT2 | State | State DC-DC H-Bridg  |  |  |

| Х     | Х   | L  | Х      | L    | L    | А     | Whole System Disable |  |  |

| Х     | Х   | Н  | L      | L    | L    | E     | Active Disable       |  |  |

| L     | L   |    |        | L    | L    |       | Normal Operation     |  |  |

| L     | Н   | н  | н      | L    | Н    | D     |                      |  |  |

| Н     | L   |    |        | Н    | L    |       |                      |  |  |

| Н     | Н   |    |        | Н    | Н    |       |                      |  |  |

#### Notes:

9. X: Don't care (L or H).

10. EN: Whole system is disable mode when EN is LOW state. 11. Soft-start duration: C, under-voltage condition of  $V_{DRV}$ : **B**.

# **Functional Description**

The FAN8841 has a basic PWM controller for Step-up DC-DC converter topology in Critical Conduction Mode (CRM) and integrated Dual half-bridge drivers. To increase efficiency of the DC-DC converter, FAN8841 has a Zero Current Detection (ZCD) function for CRM control. It can reduce Step-up DC-DC converter switching loss at MOSFET turn on time. The FAN8841 Step-up DC-DC converter supports output voltage up to 36 V with the use of a commercial inductor since the absolute maximum voltage of internal switching FET V<sub>DS</sub> is 40 V. If the use requires a driving voltage higher than 36 V, it is recommended to use a coupled inductor, since the internal half-bridge absolute maximum voltage is 75 V.

The device architecture is that of a current mode controller with an internal sensing resistor connected in series with the NMOS switch. The voltage at the feedback pin tracks the output voltage at the cathode of the external Schottky diode. The internal error amplifier amplifies the difference between the feedback voltage and the internal reference voltage. Its error signal is applied to the input of a compensator and is compared to the current of the main switch which produces the appropriate duty cycle of the main switch in the inner loop. The amplified error voltage serves as a reference voltage to the internal PWM comparator. The PWM comparator resets the latch when the RAMP generator signal meets the error amp output level. The ZCD signal sets the latch and the SR latch turns on the FET switch. Since the comparator input contains information about the output voltage and the control loop is arranged to form a negative feedback loop, the value of the peak inductor current is adjusted to the driving power.

Every time the latch is reset, the FET is turned off and the current flow through the switch is terminated. The latch can be reset by other events as well. Over-current condition is monitored by the current limit comparator which resets the latch and turns off the switch instantaneously within each clock cycle.

## Soft Startup

The FAN8841 has a Soft Startup function to prevent inrush current during the Step-up DC-DC converter startup. When the EN pin voltage goes HIGH from LOW, the Step-up DC-DC converter is turned on, the COMP is pre-charged, and inverting input of the internal error amplifier reference voltage starts up gradually with regular slope. This time is typically 28 ms at the maximum  $V_{CON}$ .

## Adjustable V<sub>DRV</sub> Voltage (V<sub>CON</sub> Control)

The FAN8841 can control the Step-up DC-DC converter output voltage without changing the resistive feedback divider using the  $V_{CON}$  pin. The  $V_{CON}$  is controlled directly by the external DC voltage or external resistance value.  $V_{CON}$  control range is fixed from 0.1 to 1.0 V. If  $V_{CON}$  voltage decreases below 0.1 V or increases higher than 1.0 V,  $V_{DRV}$  voltage fixed on minimum or maximum voltage due to the internal clamp level. If the user wants a fixed  $V_{DRV}$  voltage, it is

recommended that the  $V_{\text{CON}}$  pin is connected with  $V_{\text{DD}}$  voltage.

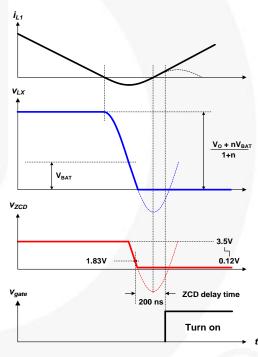

### Zero Current Detection (ZCD)

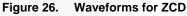

The Step-up DC-DC converter of the FAN8841 operates in CRM method with ZCD function. The ZCD is detected instantly when the inductor current goes to zero voltage switching operation. Once the boost inductor current becomes zero, the output capacitor of the main FET (Coss) and the magnetizing inductor of the coupled inductor (L1) resonate together, and the drain voltage of the main switch decreases, as shown in Figure 26. Since the ZCD pin can be connected to the switching diode anode, the FAN8841 detects when the diode anode voltage reaches its minimum value directly. The threshold voltage to detect the anode voltage inside the ZCD pin is typically 1.83 V. Therefore, the next switching begins after the anode voltage reaches 1.83 V, and has a 200 ns maximum delay to the next gate turn-on.

The resistor R<sub>ZCD</sub> is obtained as follows:

$$R_{ZCD} \ge \frac{(V_{DRV} + 0.7) - V_{CLAMPH}}{I_{ZCD}} \tag{1}$$

# **Over-Current Protection (OCP)**

The Over-Current Protection (OCP) function of the FAN8841 limits the inductor peak current of the Step-up DC-DC converter via an external resistor  $R_{OCP}$ . The adjustable current limit should be less than the rated saturation limit of the inductor by the user to avoid the damage to both the inductor and FAN8841.

#### **V**<sub>DRV</sub> Under-Voltage Protection

The driving voltage of the internal dual Half-bridge is received from the  $V_{DRV}$  pin. The internal 5 V LDO for driving the internal gate driver is also received from the  $V_{DRV}$  pin. For supplying a stable power to the internal gate driver,  $V_{DRV}$  has an under-voltage protection function. If the  $V_{DRV}$  voltage is less than 11 V typically, during normal operation, the internal gate driver is turned off. When the  $V_{DRV}$  voltage exceeds 12 V typically, the internal gate driver is turned on.

#### **Over-Voltage Protection (OVP)**

The FAN8841 features a unique  $V_{DRV}$  monitoring to maximize the safety when the feedback voltage is higher than the specified threshold voltage. The OVP comparator shuts down the output drive block when the voltage of the FB pin is higher than 1.1 V.

At the normal operating condition, Fault Out signal maintains on  $V_{DD}$  voltage, but the abnormal over-voltage has occurred at  $V_{DRV}$ , Fault Out signal goes low during typ. 20 µs.

# **Application information**

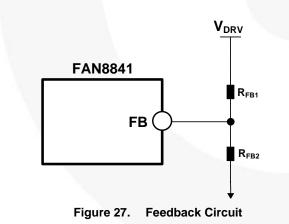

#### Setting the Output Voltage

The internal reference is 1.0 V (Typical) and it controlled by the V<sub>CON</sub> voltage. The output voltage is divided by the external resistor divider, R<sub>FB1</sub> and R<sub>FB2</sub> to the FB pin. The output voltage is given by:

$$V_{DRV} = V_{REF} \left( 1 + \frac{R_{FB1}}{R_{FB2}} \right)$$

(2)

#### **Inductor Selection**

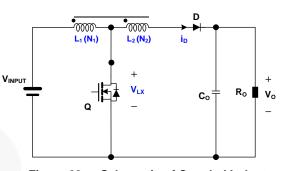

To prevent the absolute maximum voltage in the operating condition, the switching voltage  $V_{LX}$  should be lower than 36 V, as shown in Figure 28.

#### Figure 28. Schematic of Coupled Inductor Boost Converter

$V_{\text{LX}}$  is determined by the output voltage, input voltage and coupled inductor turn ratio. The  $V_{\text{LX}}$  voltage is calculated as follows:

$$V_{LX} = V_{INPUT} + \frac{V_O - V_{INPUT}}{n+1} = \frac{V_O + nV_{INPUT}}{n+1}$$

(3)

Therefore, the turn's ratio can be easily obtained as the following equations:

$$n = \frac{V_O - V_{LX}}{V_{LX} - V_{INPUT}} \tag{4}$$

To determine the turn's ratio, the input voltage variation has to be considered as well.

The inductor parameters are directly related to the device performance, saturation current and DC resistance. The lower the DC resistance, the higher efficiency. Usually a trade-off between inductor size, cost and overall efficiency is needed to make the optimum choice.

The inductor saturation current should be rated around 2 A at maximum power in the FAN8841. If to use a low saturation current inductor under 2 A due to inductor size, it is possible using the OCP level control.

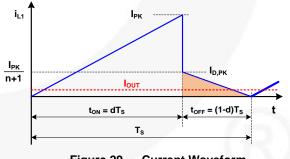

Figure 29. Current Waveform

In CRM operation, the inductance can be obtained from the slope of the inductor current, as shown in Figure 29. During FET turn off period, the inductor current flows through the diode. The diode peak current is expressed as follows:

$$I_{D,PK} = \frac{2I_{OUT}}{1-d} \tag{5}$$

r

And then, the peak current of the main switch is obtained as follows:

$$I_{PK} = \frac{2I_{OUT}(1+n)}{1-d}, \text{ or } I_{PK} = \frac{V_{INPUT}}{L_1} dT_s$$

(6)

The inductance value obtained as follows:

$$L_{1} = \frac{V_{INPUT} dT_{S}}{I_{PK}} = \frac{V_{INPUT} d(1-d)T_{S}}{2I_{OUT} (1+n)}$$

(7)

If a user wants a commercial inductor at output voltage under 35 V condition, n(turns ratio at using coupled inductor) should be substituted the value zero, (turns ratio at using coupled inductor).

#### **Output Capacitor Selection**

The value of the output capacitor can be selected based on the output voltage ripple requirements. Without consideration of the effect of Equivalent Series Resistance (ESR) as output capacitors, the output voltage ripple in a peak-to-peak manner is obtained as follows:

$$V_{ripple,pp} = \frac{\left(2d + \frac{(1-d)^2}{2}\right) \cdot I_{OUT} \cdot T_s}{2C_o}$$

(8)

where  $V_{ripple,pp}$  is the output voltage ripple in peak-topeak manner. Therefore, the output capacitance can be selected with the given output voltages ripple specification as follows:

$$C_{O} \ge \frac{\left(2d + \frac{(1-d)^{2}}{2}\right) \cdot I_{OUT} \cdot T_{s}}{2V_{ripple,pp}}$$

(9)

#### **Diode Selection**

The external diode used for the rectification is usually a Schottky diode. It's average forward current and reverse voltage maximum ratings should exceed the load current and the voltage at the output of the converter respectively.

A care should be taken to avoid any short circuit of  $V_{OUT}$  to GND, even with the IC disabled, since the diode can be instantly damaged by the excessive current.

4.00 2.80 18 13 0.05 C A 4.00 В 2X 19 \_\_\_\_\_12 4.00 2.80 4.00 24 0.20 0.80 PIN 1 6 QUADRANT-0.05 C -0.30 24X 2X TOP VIEW **RECOMMENDED LAND PATTERN** -0.75±0.05 0.10 C |// -0.15±0.05 ſ Uυ 0.08 C Ľ SIDE VIEW 0.025±0.025 SEATING PLANE BOTTOM VIEW PIN ONE OPTIONS 4.00±0.05 PIN #1 IDENT 2.70±0.05 (0.635) 4X 6 0.40±0.05 U NOTES: ł 24 A. CONFORMS TO JEDEC REGISTRATION 4.00±0.05 MO-220, VARIATION WGGD-6. 2.70±0.05 B. DIMENSIONS ARE IN MILLIMETERS.  $\mathcal{C}$ ( C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009. D. LAND PATTERN IPC REFERENCE : 19 QFN50P400X400X80-25W6N. (0.495) 4X (0.650) 4X

1

18

0.50

13

BOTTOM VIEW

Φ

0.23±0.05 24X

0.05M C

0.10 C A B

E. DRAWING FILENAME: MKT-MLP24Erev5.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC