# LC786820E

## USB-Host対応 オーディオ信号処理1チップLSI

ON Semiconductor®

[www.onsemi.jp](http://www.onsemi.jp)

### 概要

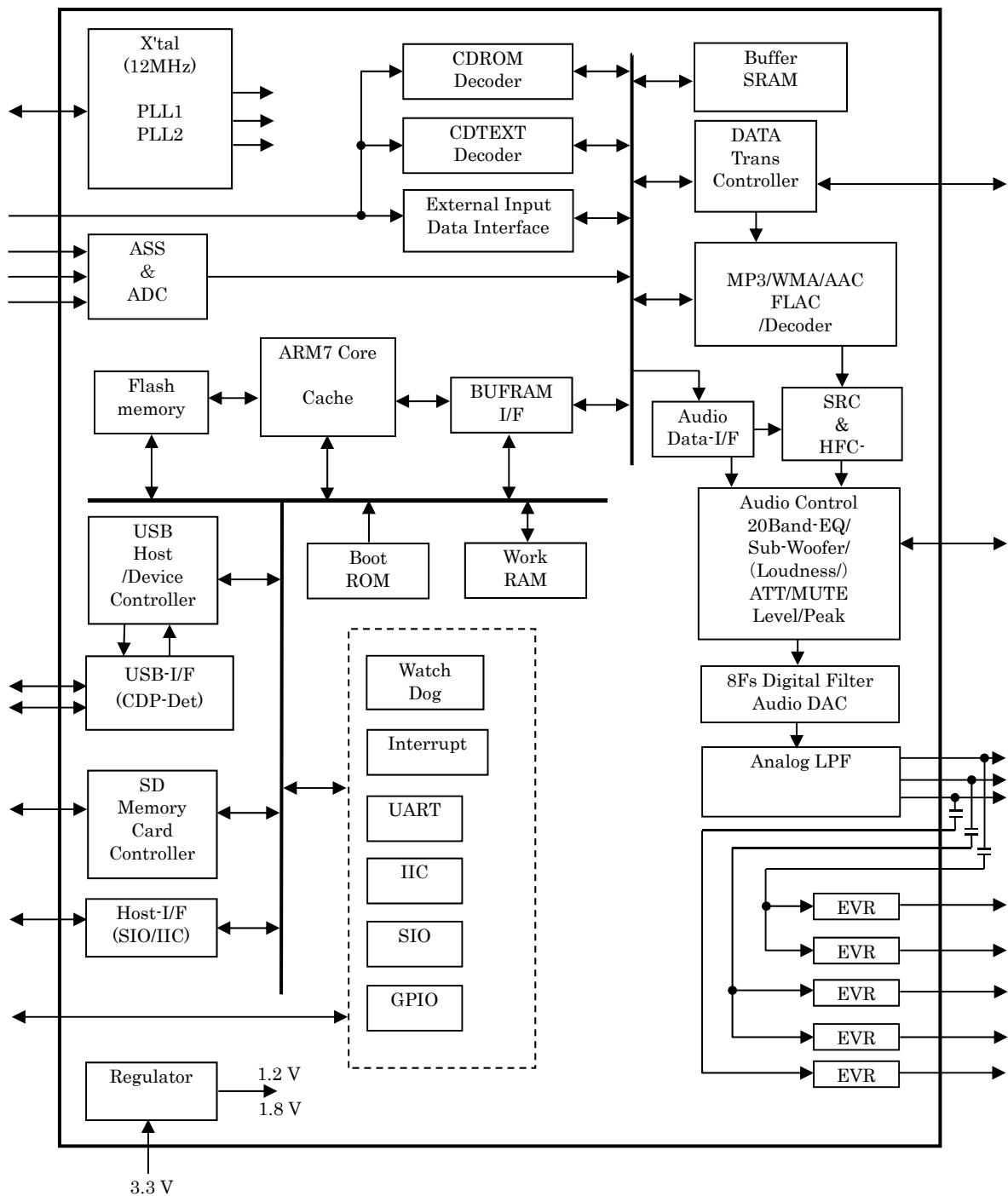

LC786820E は、ARM7TDMI-S™を搭載し、USB ホスト処理、SD カードホスト処理、圧縮オーディオデコード処理、オーディオ再生処理を 1 chip で実現する LSI である。また、ARM7TDMI-S™のプログラムコード / 各種データ保持のためにフラッシュメモリを内蔵し、USB ホスト処理や SD カードホスト処理、オーディオ再生処理等の複雑な制御を行うプログラムを格納しておくことで、外付けするメインマイコンの処理負担を軽減し、USB / SD カードのホスト処理を伴った高性能・多機能な圧縮オーディオプレーヤシステムを容易に実現する事が可能である。

### 機能

- USB ホスト / デバイス機能 (フルスピード : 12M bps),

SD メモリカードホスト機能

- MP3\*, WMA\*, AAC\*, FLAC\* の各デコード機能

- アナログ(ステレオ 3-ch)・デジタル 3-ch 入力

(サンプリングレート変換対応)のオーディオ入力機能

- 20 バンドディコライザ(ステレオ 1-ch), サブウーハー処理,

高域拡張フィルタなどの各種オーディオ処理機能

- 電子ボリューム出力 5-ch (LF, LR, RF, RR, SW 用)

または、DAC 出力 3-ch (Lch, Rch, SW)のオーディオ出力機能

- ARM7 を CPU コアとし、プログラム格納用にフラッシュメモリ搭載

- 動作電源電圧 : 3.3 V 単一電源

- 動作保証温度 : -40°C ~ +85°C

- パッケージ : QIP100E(14x20) 鉛フリー・ハロゲンフリー仕様品

PQFP100 14x20 / QIP100E

ARM®

\* MP3

MPEG Layer-3 Audio Coding

\* WMA

Windows Media Audio

\* AAC

Advanced Audio Coding

\* FLAC

Free Lossless Audio Codec

この製品は米国 SST 社(Silicon Storage Technology, Inc.)のライセンスを受けています。

# LC786820E

## 機能詳細

### 【圧縮オーディオ機能】

#### <オーディオ処理部>

- ・ MP3 デコード . . . ISO/IEC 11172-3, ISO/IEC 13818-3 に準拠

- 対応サンプリング周波数      MPEG1-Layer1/2/3 (32 kHz, 44.1 kHz, 48 kHz)

- MPEG2-Layer1/2/3 (16 kHz, 22.05 kHz, 24 kHz)

- MPEG2.5-Layer3 (8 kHz, 11.025 kHz, 12 kHz)

- 対応ビットレート      VBR 含む全ビットレートに対応

- MPEG ヘッダ読み出し対応

- ・ WMA デコード . . . WMA Ver.9.2 Standard 準拠

- 対応サンプリング周波数      8 kHz~48 kHz

- 対応ビットレート      5k~384k bps (VBR 対応)

- ・ AAC デコード . . . ISO/IEC 14496-3, 13818-7 準拠

- 対応プロファイル      MPEG4-AAC-LC(Low Complexity)

- 対応サンプリング周波数      8 kHz~48 kHz

- 対応ビットレート      モノラル : 8k~160k bps (VBR 対応)

ステレオ : 16k~320k bps (VBR 対応)

- ※使用条件により、サンプリング周波数は最大 96 kHz まで対応可能。

- ・ FLAC デコード . . . FLAC 1.3.0 準拠

- 対応フォーマット      ブロックサイズ : ~4608

量子化ビット数 : 8 / 16 / 24-bit per sample

- 対応サンプリング周波数      8 kHz~48 kHz

- 対応チャンネル      1/2-ch

### 【オーディオ処理機能】

#### <オーディオデータデジタル処理部>

- ・イコライザ機能

- 最大 20 バンド(ステレオ 1-ch) に対応し、未使用バンドは音声出力以外の処理にも使用可能

- ・サブウーハー用信号処理対応

- ・圧縮オーディオ再生時のサンプリング変換( $F_s = 32 / 44.1 / 48 \text{ kHz}$ )、高域拡張処理対応

- ・ミュート( $-\infty / -12 \text{ dB}$ )、アッテネータ

- ・ディエンファシスフィルタ

- ・レベル/ピークホールド回路搭載し、最大 8 データのホールド可能

- ・ノイズキャンセル/エコーキャンセル機能

- $F_s = 8 \text{ kHz}$  でのノイズキャンセル・エコーキャンセル機能を搭載。

- $F_s = 16 \text{ kHz}$  音声データの入出力に対応

#### <オーディオ入力処理部>

- ・アナログオーディオ入力 (ステレオ入力 3-ch に対応)

- シングルエンド入力 : 2-ch

- 差動入力 : 1-ch

- 入力ゲイン :  $-12.5 \text{ dB} \sim +18.5 \text{ dB}$  (1 dB ステップ)

- 24-bit 精度 AD コンバータ

- ・デジタルオーディオ入力 (ステレオ入力 最大 3-ch まで対応)

- デジタル 3 線 (LR クロック, ビットクロック, オーディオデータ)接続に対応し、

クロックはマスター/スレーブ対応が可能。

データフォーマットは、I2S/MSB フースト右詰め等の各種フォーマットに対応。

- 入力データは 8 kHz~96 kHz に対応し、サンプリングレート変換により再生に適した  $F_s$  に変換。

(再生  $F_s = 32 / 44.1 / 48 \text{ kHz}$  など)

# LC786820E

## <オーディオ出力処理部>

- ・アナログオーディオ出力 (ステレオ 1-ch 出力、及びサブウーハー出力[1-ch]に対応)

8 倍オーバーサンプリングデジタルフィルタ (24-bit 長)

オーディオ出力用 2 次 LPF 内蔵

- ・電子ボリューム/フェーダー

5ch 出力 (Lch-Front(LF) / Rear(LR), Rch-Front(RF) / Rear(RR), Sub-Woofe)対応

出力レンジ : 0 dB ~ -90 dB, -∞

- 0 dB ~ -32 dB : アナログ制御、0.25 dB ステップ

- 32 dB ~ -70 dB : アナログ制御、1 dB ステップ

- 70 dB ~ -90 dB : デジタルアップ/ダウン制御

- デジタル/アナログの複合制御により、ボリューム切替え時のノイズ発生を抑制

出力 5-ch 独立制御可能

- ・デジタルオーディオ出力

出力形式はデジタル 3 線で、I2S/MSB ファースト右詰め等の各種フォーマットに対応

LR クロック、ビットクロック、データ 1

クロックはマスター/スレーブ対応が可能

384Fs クロックの出力可能

## 【外部インターフェース機能】

### <USB ホスト/デバイス制御部>

- ・OpenHCI(Open Host Controller Interface) 1.0a 準拠

- ・Universal Serial Bus Specification 2.0 Full Speed 準拠

- ・4 種類の転送タイプをサポート (コントロール / バルク / インターラプト / アイソクロナス)

- ・2 Port に対応。 USB1 = Host / Device 切替対応、USB2 = Host 制御のみ。

- ・USB 充電対応 (USB1 側のみ)

USB バッテリ充電仕様 1.2 の CDP (Charging Downstream Port)検出対応。

但し、充電(電流供給)については非対応。

- ・PHY 部 プルダウン/プルアップ抵抗内蔵。

### <SD メモリカード制御部>

- ・Multimedia Card Specification v2.11 準拠

- ・Secure Digital Memory Card Physical Layer Specification v0.96 準拠

- ※使用に際しては使用契約が必要です。

## 【内蔵マイコン機能】

### <シーケンサ制御>

- ・USB, SD メモリカード再生/書き込み制御

USB / SD ファイル解析等

- ・オーディオ再生制御

圧縮オーディオ再生制御、各種フィルタ制御等

### <メインマイコン通信制御>

- ・通信フォーマットは、SIO(4 線)がメイン。

- ・メインマイコンでの発振停止・復帰等の直接制御が可能

- ・発振停止時でも、汎用ポート制御等の一部専用コマンド通信が可能

### <周辺インターフェース部>

- ・汎用入出力ポート 37 本 (他の機能と兼用、一部端子はクロック停止中の動作に対応)

- ・外部割込み端子 4 本 (他の機能と兼用)

- ・シリアルインターフェース

- SIO クロック同期 3 線式全二重タイプ 3-ch

- UART 全二重タイプ 2-ch

- IIC マスター機能 1-ch

### <プログラムメモリ部>

- ・内蔵シーケンサ用のプログラムメモリを搭載

外部インターフェース(USB 等)や、メインマイコンからのアップデートが可能

## **LC786820E**

### <その他>

- ウオッヂドッグタイマ

外部通知(端子出力)もしくは、内部リセット

- スリープモード (2種類)

- ①各種モジュール毎のクロック停止制御と CPU コアのみ低速クロック動作

- ②メインマイコン制御によるクロック全停止

### **【CD-DSP 接続補助機能】**

#### <CD-TEXT 处理部>

- CDTEXT データのバッファリング対応

- CDTEXT の任意の ID3 / ID4 からのバッファリング開始対応

- ※サブコード同期信号(SBSY, SFSY)及びシリアル転送(SBCK, PW)の 4 線接続が必要。

#### <CDROM 处理部>

- デコード処理は、最大 4 倍速まで対応

- CDROM モード 1 / モード 2 <Form1, 2> デコード対応

- CDROM デコードデータの外部出力対応

- ※3 線(LRCK, BCK, DATA)接続が必要。C2 エラーフラグの接続は任意。

### **【その他】**

#### <内部電源>

- 内部電源(内部用  $V_{DD} = 1.2$  V, Flash 用  $V_{DD} = 1.8$  V)用レギュレータ内蔵

# LC786820E

**絶対最大定格 / Ta = 25°C, DVSS = AVSS1 = AVSS2 = XVSS = 0 V**

| 項目     | 記号      | 端子名                             | 条件                              | 定格値             | Unit |

|--------|---------|---------------------------------|---------------------------------|-----------------|------|

| 最大電源電圧 | VDD max | DVDD, AVDD1, AVDD2, XVDD, VVDD2 |                                 | -0.3 ~ +3.95    | V    |

| 入力電圧   | VIN     | すべてのデジタル入力端子                    |                                 | -0.3 ~ DVDD+0.3 |      |

| 出力電圧   | VOUT    | 全てのデジタル出力/入出力端子                 |                                 | -0.3 ~ DVDD+0.3 |      |

| 許容消費電力 | Pd max  |                                 | Ta≤85°C<br>標準基板<br>装着時<br>(※参照) | 519             | mW   |

| 動作周囲温度 | Topr    |                                 |                                 | -40 ~ +85       | °C   |

| 保存周囲温度 | Tstg    |                                 |                                 | -40 ~ +125      |      |

(※)標準基板 : 114.3 mm × 76.1 mm × 1.6 mm、材質 : ガラスエポキシ樹脂

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。これらの定格値を超えた場合は、デバイスの機能性を損ない、ダメージが生じ、信頼性に影響を及ぼす危険性があります。

**許容動作範囲 / Ta = -40~85°C, DVSS = AVSS1 = AVSS2 = XVSS = 0 V**

| 項目         | 記号   | 端子名                                                                                                                                                                                                                                                                       | 条件 | MIN     | TYP  | MAX     | Unit |

|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|------|---------|------|

| 電源電圧       | VDD1 | DVDD, AVDD1, AVDD2, XVDD, VVDD2                                                                                                                                                                                                                                           |    | 3.00    |      | 3.60    | V    |

| 入力「H」レベル電圧 | VIH  | RESB, SIFCK, SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP04, GP05, GP06, GP07, GP10, GP11, GP12, GP13, GP14, GP15, JTMS, JTRSTB, JTCK, JTDI, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53               |    | Schmitt | 2.00 | VDD1    |      |

| 入力「L」レベル電圧 | VIL  | RESB, SIFCK, SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP04, GP05, GP06, GP07, GP10, GP11, GP12, GP13, GP14, GP15, JTMS, JTRSTB, JTCK, JTDI, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53, TEST0, TEST1 |    | Schmitt | 0.00 | 0.80    | V    |

| 発振周波数範囲    | FX   | XIN<br>XOUT                                                                                                                                                                                                                                                               |    | 発振回路    |      | 12.0000 | MHz  |

推奨動作範囲を超えるストレスでは推奨動作機能を得られません。推奨動作範囲を超えるストレスの印加は、デバイスの信頼性に影響を与える危険性があります。

# LC786820E

電気的特性 /  $T_a = -40 \sim 85^\circ\text{C}$ ,  $V_{DD1} = 3.0 \sim 3.6 \text{ V}$ ,  $DVSS = AVSS1 = AVSS2 = XVSS = 0 \text{ V}$

| 項目                 | 記号          | 端子名                                                                                                                                                                                                                                                                       | 条件                                                | MIN               | TYP | MAX   | Unit             |

|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------|-----|-------|------------------|

| 消費電流               | $I_{DD1}$   | DVDD, AVDD1, AVDD2, XVDD, VVDD2                                                                                                                                                                                                                                           |                                                   |                   | 100 | 150   | mA               |

| 入力<br>「H」レベル<br>電流 | $I_{IH}$    | RESB, SIFCK, SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP04, GP05, GP06, GP07, GP10, GP11, GP12, GP13, GP14, GP15, JTMS, JTRSTB, JTCK, JTDI, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53               | Schmitt<br>$V_{IN} = V_{DD1}$<br>内蔵プルダウン<br>抵抗OFF |                   |     | 10.00 |                  |

| 入力<br>「L」レベル<br>電流 | $I_{IL}$    | RESB, SIFCK, SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP04, GP05, GP06, GP07, GP10, GP11, GP12, GP13, GP14, GP15, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53, JTMS, JTRSTB, JTCK, JTDI, TEST0, TEST1 | Schmitt<br>$V_{IN} = 0 \text{ V}$                 | -10.00            |     |       | $\mu\text{A}$    |

| 出力<br>「H」レベル<br>電圧 | $V_{OH(1)}$ | GP04, GP05, GP06, GP07, GP12, GP13, GP14, GP15, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53                                                                                                    | CMOS<br>$I_{OH} = -2 \text{ mA}$                  | $V_{DD1}$<br>-0.6 |     |       | $\text{V}$       |

|                    | $V_{OH(2)}$ | SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP10, GP11, JTDO, JTRTCK                                                                                                                                                                                                                | CMOS<br>$I_{OH} = -4 \text{ mA}$                  |                   |     |       |                  |

| 出力<br>「L」レベル<br>電圧 | $V_{OL(1)}$ | GP04, GP05, GP06, GP07, GP12, GP13, GP14, GP15, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53                                                                                                    | CMOS<br>$I_{OL} = 2 \text{ mA}$                   |                   |     | 0.40  | $\text{V}$       |

|                    | $V_{OL(2)}$ | SIFDI, SIFDO, SIFCE, BUSYB, GP03, GP10, GP11, JTDO, JTRTCK                                                                                                                                                                                                                | CMOS<br>$I_{OL} = 4 \text{ mA}$                   |                   |     | 0.40  |                  |

| 内蔵<br>プルダウン<br>抵抗値 | $RPD$       | SIFDO, SIFCE, BUSYB, GP03, GP04, GP05, GP06, GP07, GP10, GP11, GP12, GP13, GP14, GP15, GP30, GP31, GP32, GP33, GP34, GP35, GP36, GP37, GP40, GP41, GP42, GP43, GP44, GP45, GP46, GP47, GP50, GP51, GP52, GP53                                                             |                                                   | 50                | 100 | 200   | $\text{k}\Omega$ |

## LC786820E

| 項目                  | 記号          | 端子名   | 条件       | MIN    | TYP   | MAX   | Unit |

|---------------------|-------------|-------|----------|--------|-------|-------|------|

| 出力<br>リーク<br>電流     | IOFF<br>(1) | AFILT | Hi-Z Out | -10.00 |       | 10.00 | μA   |

|                     | IOFF<br>(2) | SIFDO | Hi-Z Out | -10.00 |       | 10.00 |      |

| チャージ<br>ポンプ<br>出力電流 | IAFH        | AFILT |          |        | 195.0 |       | μA   |

|                     | IAFL        | AFILT |          |        | 195.0 |       |      |

(注意)

- SIFDO端子の3-State出力状態を使用する場合、必ず内蔵のプルダウン抵抗か外付のプルアップまたは、プルダウン抵抗を接続して使用すること。

製品パラメータは、特別な記述が無い限り、記載されたテスト条件に対する電気的特性で示しています。異なる条件下で製品動作を行った時には、電気的特性で示している特性を得られない場合があります。

# LC786820E

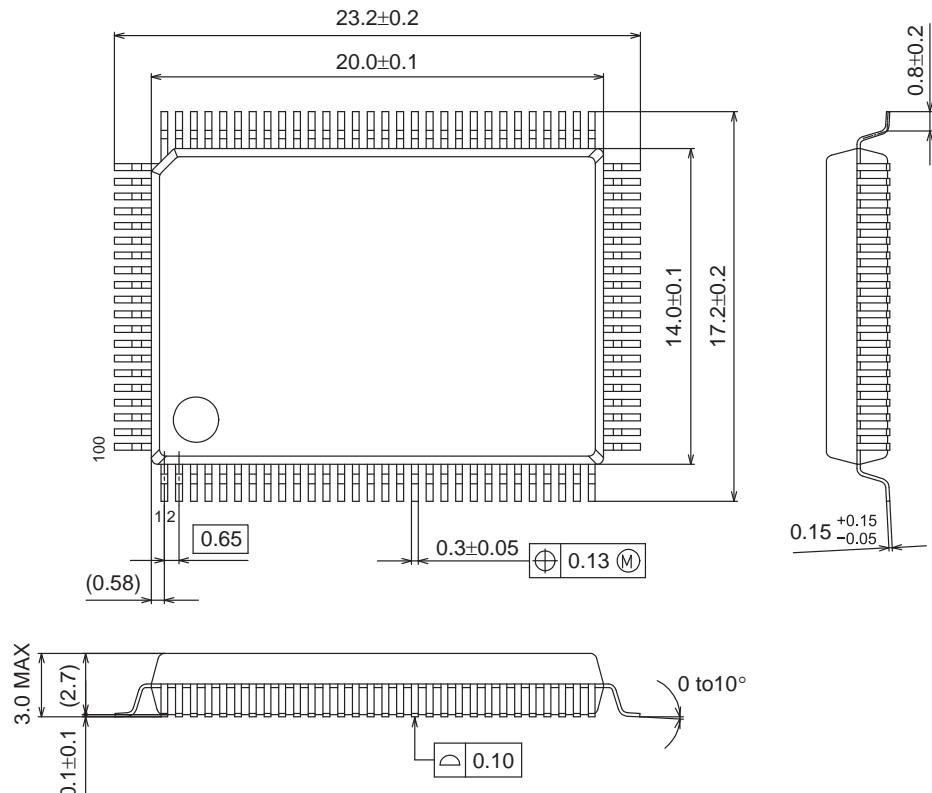

## 外形図

unit : mm

PQFP100 14x20 / QIP100E

CASE 122BV

ISSUE A

## SOLDERING FOOTPRINT\*

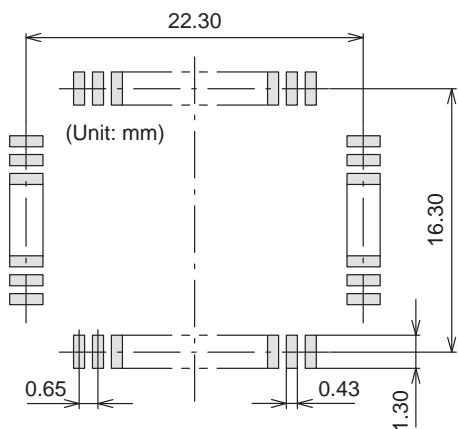

## GENERIC MARKING DIAGRAM\*

XXXXXX = Specific Device Code

Y = Year

M = Month

DDD = Additional Traceability Data

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present.

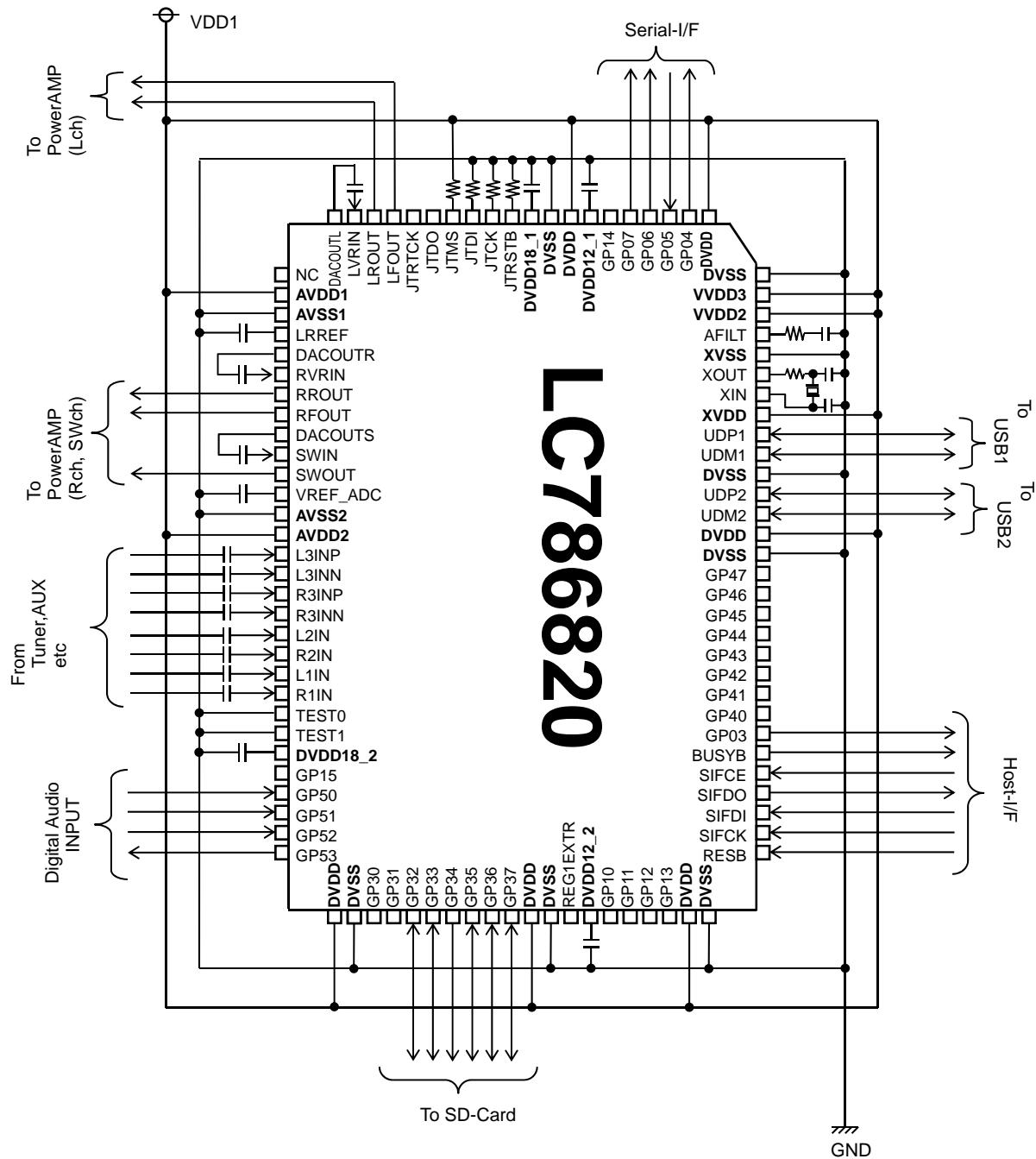

# LC786820E

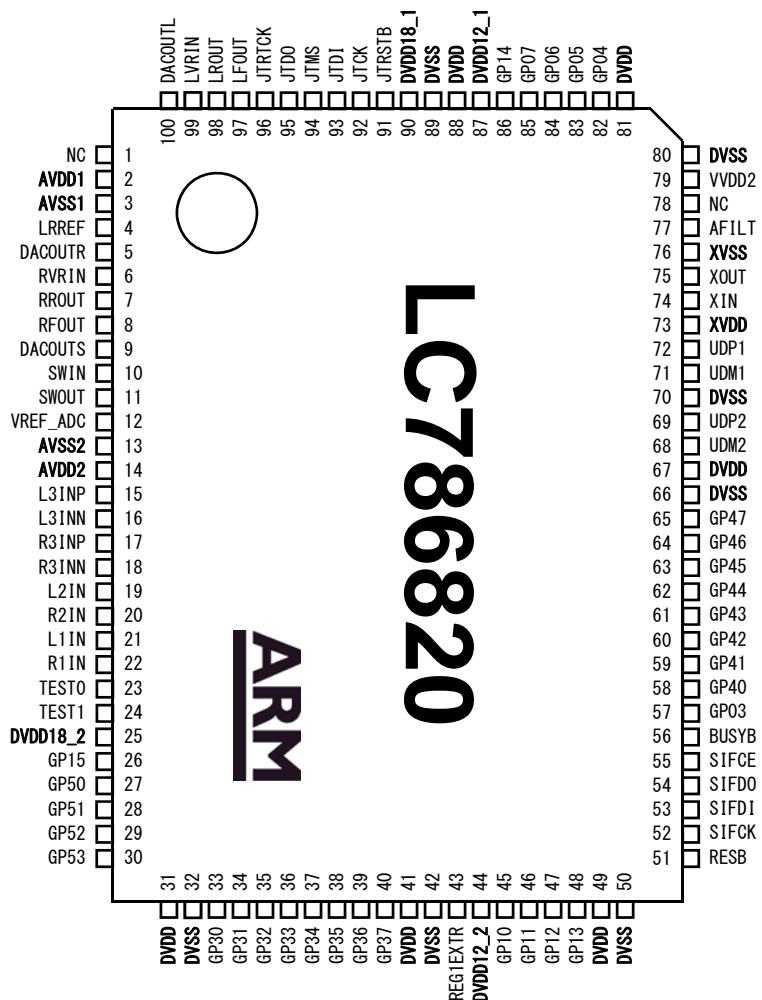

ピン配置図

# LC786820E

## 端子説明

| 端子 No. | 端子名      | I/O 形式 | リセット 状態 | 機能 説明                                                                                                                     |

|--------|----------|--------|---------|---------------------------------------------------------------------------------------------------------------------------|

| 1      | NC       | —      | —       | NCピン(オープン処理)                                                                                                              |

| 2      | AVDD1    | —      | —       | アナログ(ADC)用電源端子                                                                                                            |

| 3      | AVSS1    | —      | —       | アナログ(ADC)用接地端子(必ず0Vに接続すること)                                                                                               |

| 4      | LRREF    | AO     | AVDD1/2 | オーディオDAC / ポリウム用基準電圧用コンデンサ接続端子                                                                                            |

| 5      | DACOUTR  | AO     | 不定      | オーディオDAC Rch出力                                                                                                            |

| 6      | RVRIN    | AI     | 入力      | 電子ポリウム Rchポリウム入力                                                                                                          |

| 7      | RROUT    | AO     | 不定      | 電子ポリウム Rchリア出力                                                                                                            |

| 8      | RFOUT    | AO     | 不定      | 電子ポリウム Rchフロント出力                                                                                                          |

| 9      | DACOUTS  | AO     | 不定      | オーディオDAC サブウーハー出力                                                                                                         |

| 10     | SWIN     | AI     | 入力      | 電子ポリウム サブウーハーポリウム入力                                                                                                       |

| 11     | SWOUT    | AO     | 不定      | 電子ポリウム サブウーハー出力                                                                                                           |

| 12     | VREF_ADC | AO     | AVDD2/2 | オーディオADC用基準電圧用コンデンサ接続端子                                                                                                   |

| 13     | AVSS2    | —      | —       | アナログ(ADC)用接地端子(必ず0Vに接続すること)                                                                                               |

| 14     | AVDD2    | —      | —       | アナログ(ADC)用電源端子                                                                                                            |

| 15     | L3INP    | AI     | 入力      | ステレオ3用Lch差動入力(Positive) / シングルエンド入力                                                                                       |

| 16     | L3INN    | AI     | 入力      | ステレオ3用Lch差動入力(Negative)                                                                                                   |

| 17     | R3INP    | AI     | 入力      | ステレオ3用Rch差動入力(Positive) / シングルエンド入力                                                                                       |

| 18     | R3INN    | AI     | 入力      | ステレオ3用Rch差動入力(Negative)                                                                                                   |

| 19     | L2IN     | AI     | 入力      | ステレオ2用Lchシングルエンド入力                                                                                                        |

| 20     | R2IN     | AI     | 入力      | ステレオ2用Rchシングルエンド入力                                                                                                        |

| 21     | L1IN     | AI     | 入力      | ステレオ1用Lchシングルエンド入力                                                                                                        |

| 22     | R1IN     | AI     | 入力      | ステレオ1用Rchシングルエンド入力                                                                                                        |

| 23     | TEST0    | I      | 入力      | テストモード設定端子(必ず0Vに接続すること)                                                                                                   |

| 24     | TEST1    | I      | 入力      | テストモード設定端子(必ず0Vに接続すること)                                                                                                   |

| 25     | DVDD18_2 | AO     | H       | 内蔵レギュレータ用コンデンサ接続端子(Flash用1.8V)                                                                                            |

| 26     | GP15     | I/O    | 入力(L)   | プルダウン抵抗付き汎用入出力ポート<br>各種モニタ用出力                                                                                             |

| 27     | GP50     | I/O    | 入力(L)   | プルダウン抵抗付き汎用入出力ポート<br>オーディオ3線用LRクロック入出力1<br>ストリームデータ用LRクロック入力1<br>シリアル通信3用送信データ出力(GP34と排他)<br>USB1用過電流検出信号入力(GP44と排他)      |

| 28     | GP51     | I/O    | 入力(L)   | プルダウン抵抗付き汎用入出力ポート<br>オーディオ3線用ビットクロック入出力1<br>ストリームデータ用ビットクロック入出力1<br>シリアル通信3用マスタークロック出力(GP35と排他)<br>USB1用電源投入信号出力(GP45と排他) |

| 29     | GP52     | I/O    | 入力(L)   | プルダウン抵抗付き汎用入出力ポート<br>オーディオ3線用データ入出力1<br>ストリームデータ用データ入力1<br>シリアル通信3用受信データ入力(GP36と排他)<br>USB2用過電流検出信号入力(GP46と排他)            |

| 30     | GP53     | I/O    | 入力(L)   | プルダウン抵抗付き汎用入出力ポート<br>オーディオDAC用クロック(Fs384)入出力1<br>ストリームデータ用リクエストフラグ入出力1<br>USB2用電源投入信号出力(GP47と排他)                          |

| 31     | DVDD     | —      | —       | デジタル系電源端子                                                                                                                 |

| 32     | DVSS     | —      | —       | デジタル系接地端子(必ず0Vに接続すること)                                                                                                    |

次ページへ続く

## LC786820E

前ページより続く

| 端子<br>No. | 端子名      | I/O<br>形式 | リセット<br>状態 | 機能説明                                                                                                                             |

|-----------|----------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------|

| 33        | GP30     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART2データ送信 (GP46と排他)<br>外部割込み機能3 (GP13, GP31, GP43, GP47と排他)<br>オーディオ3線用LRクロック入出力2<br>ストリームデータ用LRクロック入力2    |

| 34        | GP31     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART2データ受信 (GP47と排他)<br>外部割込み機能3 (GP13, GP30, GP43, GP47と排他)<br>オーディオ3線用ビットクロック入出力2<br>ストリームデータ用ビットクロック入出力2 |

| 35        | GP32     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用データ1入出力<br>オーディオ3線用データ入出力2<br>ストリームデータ用データ入出力2                                                     |

| 36        | GP33     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用データ0入出力<br>オーディオDAC用クロック(Fs384)入出力2<br>ストリームデータ用リクエストフラグ入出力2                                       |

| 37        | GP34     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用クロック出力<br>シリアル通信3用送信データ出力 (GP50と排他)<br>CDサブコード同期信号(SBSY)入力 (GP44と排他)                               |

| 38        | GP35     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用コマンド入出力<br>シリアル通信3用マスタークロック出力 (GP51と排他)<br>CDサブコードフレーム同期信号(SFSY)入力 (GP45と排他)                       |

| 39        | GP36     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用データ3入出力<br>シリアル通信3用受信データ入力 (GP52と排他)<br>CDサブコードデータ(PW)入力 (GP46と排他)                                 |

| 40        | GP37     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>SDメモリカード用データ2入出力<br>CDサブコードデータ転送クロック(SBCK)出力 (GP47と排他)                                                      |

| 41        | DVDD     | —         | —          | デジタル系電源端子                                                                                                                        |

| 42        | DVSS     | —         | —          | デジタル系接地端子 (必ず0 Vに接続すること)                                                                                                         |

| 43        | REG1EXTR | AO        | 不定         | 内蔵レギュレータ用予備端子 (必ずオープン処理すること)                                                                                                     |

| 44        | DVDD12_2 | AO        | H          | 内蔵レギュレータ用コンデンサ接続端子 (内部用1.2 V)                                                                                                    |

| 45        | GP10     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART1データ送信 (GP06と排他)<br>IIC(マスター)クロック出力 (GP04, GP40と排他)                                                     |

| 46        | GP11     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART1データ受信 (GP07と排他)<br>IIC(マスター)データ入出力 (GP05, GP41と排他)                                                     |

| 47        | GP12     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能2 (GP42, GP46と排他)<br>クロック制御用入力1<br>ウォッチドッグタイマ状態モニタ出力                                                 |

| 48        | GP13     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能3 (GP30, GP31, GP43, GP47と排他)<br>クロック制御用入力2<br>ウォッチドッグタイマ状態モニタ出力                                     |

次ページへ続く

## LC786820E

前ページより続く

| 端子<br>No. | 端子名   | I/O<br>形式 | リセット<br>状態 | 機能説明                                                                                                                                |

|-----------|-------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 49        | DVDD  | —         | —          | デジタル系電源端子                                                                                                                           |

| 50        | DVSS  | —         | —          | デジタル系接地端子(必ず0Vに接続すること)                                                                                                              |

| 51        | RESB  | I         | —          | リセット入力("L"-active)<br>電源投入時、必ず"L"にすること                                                                                              |

| 52        | SIFCK | I         | 入力         | ホスト-I/F<br>シリアル通信1用データ転送クロック入力<br>IIC通信用データ転送クロック入力                                                                                 |

| 53        | SIFDI | I/O       | 入力         | ホスト-I/F<br>シリアル通信1用データ入力<br>IIC通信用データ入出力                                                                                            |

| 54        | SIFDO | I/O       | 入力         | ホスト-I/F<br>シリアル通信1用データ出力(CMOS or 3-State出力対応)<br>プルダウン抵抗付き汎用入出力ポート(GP00)                                                            |

| 55        | SIFCE | I/O       | 入力         | ホスト-I/F<br>シリアル通信1用イネーブル信号入力("H"-active)<br>プルダウン抵抗付き汎用入出力ポート(GP01)                                                                 |

| 56        | BUSYB | I/O       | 入力(L)      | ホスト-I/F<br>システムビジー信号出力("L"-active)<br>プルダウン抵抗付き汎用入出力ポート(GP02)<br>外部割込み機能0(GP40, GP44と排他)                                            |

| 57        | GP03  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>ウォッチドッグタイマ状態モニタ出力<br>USBデバイス検出フラグ出力<br>外部割込み機能1(GP14, GP41, GP45と排他)                                           |

| 58        | GP40  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能0(GP02, GP44と排他)<br>IIC(マスター)クロック出力(GP04, GP10と排他)<br>オーディオ3線用LRクロック入出力3<br>ストリームデータ用LRクロック入力3          |

| 59        | GP41  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能1(GP03, GP14, GP45と排他)<br>IIC(マスター)データ入出力(GP05, GP11と排他)<br>オーディオ3線用ビットクロック入出力3<br>ストリームデータ用ビットクロック入出力3 |

| 60        | GP42  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能2(GP12, GP46と排他)<br>ウォッチドッグタイマ状態モニタ出力<br>オーディオ3線用データ入出力3<br>ストリームデータ用データ入出力3                            |

| 61        | GP43  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能3(GP13, GP30, GP31, GP47と排他)<br>オーディオDAC用クロック(Fs384)入出力3<br>ストリームデータ用リクエストフラグ入出力3                       |

| 62        | GP44  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能0(GP02, GP40と排他)<br>USB1用過電流検出信号入力(GP50と排他)<br>CDサブコードブロック同期信号(SBSY)入力(GP34と排他)                         |

| 63        | GP45  | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能1(GP03, GP14, GP41と排他)<br>USB1用電源投入信号出力(GP51と排他)<br>CDサブコードフレーム同期信号(SFSY)入力(GP35と排他)                    |

次ページへ続く

## LC786820E

前ページより続く

| 端子<br>No. | 端子名      | I/O<br>形式 | リセット<br>状態 | 機能説明                                                                                                                                                                          |

|-----------|----------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 64        | GP46     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART2データ送信 (GP30と排他)<br>外部割込み機能2 (GP12, GP42と排他)<br>USB2用過電流検出信号入力 (GP52と排他)<br>外部エンファシスフラグ入力/出力 (GP14と排他)<br>CDサブコードデータ(PW)入力 (GP36と排他)                 |

| 65        | GP47     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART2データ受信 (GP31と排他)<br>外部割込み機能3 (GP13, GP30, GP31, GP43と排他)<br>USB2用電源投入信号出力 (GP53と排他)<br>CD_C2エラーフラグ入力 (GP14と排他)<br>CDサブコードデータ転送クロック(SBCK)出力 (GP37と排他) |

| 66        | DVSS     | —         | —          | デジタル系接地端子 (必ず0 Vに接続すること)                                                                                                                                                      |

| 67        | DVDD     | —         | —          | デジタル系電源端子                                                                                                                                                                     |

| 68        | UDM2     | I/O       | —          | USBデータ入出力2 D-信号接続                                                                                                                                                             |

| 69        | UDP2     | I/O       | —          | USBデータ入出力2 D+信号接続                                                                                                                                                             |

| 70        | DVSS     | —         | —          | デジタル系接地端子 (必ず0 Vに接続すること)                                                                                                                                                      |

| 71        | UDM1     | I/O       | —          | USBデータ入出力1 D-信号接続<br>充電検出 (CDP検出) 入出力1                                                                                                                                        |

| 72        | UDP1     | I/O       | —          | USBデータ入出力1 D+信号接続<br>充電検出 (CDP検出) 入出力1                                                                                                                                        |

| 73        | XVDD     | —         | —          | 発振回路用電源端子                                                                                                                                                                     |

| 74        | XIN      | I         | 発振         | 水晶発振子接続                                                                                                                                                                       |

| 75        | XOUT     | O         | 発振         | 水晶発振子接続                                                                                                                                                                       |

| 76        | XVSS     | —         | —          | 発振回路用接地端子 (必ず0 Vに接続すること)                                                                                                                                                      |

| 77        | AFILT    | AO        | 不定         | PLL2用チャージポンプ出力(フィルタ接続用)端子                                                                                                                                                     |

| 78        | NC       | —         | —          | NCピン (オープン処理)                                                                                                                                                                 |

| 79        | VVDD2    | —         | —          | PLL2用電源端子                                                                                                                                                                     |

| 80        | DVSS     | —         | —          | デジタル系接地端子 (必ず0 Vに接続すること)                                                                                                                                                      |

| 81        | DVDD     | —         | —          | デジタル系電源端子                                                                                                                                                                     |

| 82        | GP04     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>シリアル通信2用マスタークロック出力<br>IIC(マスター)クロック出力 (GP10, GP40と排他)                                                                                                    |

| 83        | GP05     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>シリアル通信2用受信データ入力<br>IIC(マスター)データ入出力 (GP11, GP41と排他)                                                                                                       |

| 84        | GP06     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>シリアル通信2用送信データ出力<br>UART1データ送信 (GP10と排他)                                                                                                                  |

| 85        | GP07     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>UART1データ受信 (GP11と排他)                                                                                                                                     |

| 86        | GP14     | I/O       | 入力(L)      | プルダウン抵抗付き汎用入出力ポート<br>外部割込み機能1 (GP03, GP41, GP45と排他)<br>ウォッヂドッヂタイマ状態モニタ出力<br>USBデバイス検出フラグ出力<br>外部エンファシスフラグ入力/出力 (GP46と排他)<br>CD_C2エラーフラグ入力 (GP47と排他)                           |

| 87        | DVDD12_1 | AO        | H          | 内蔵レギュレータ用コンデンサ接続端子 (内部用1.2 V)                                                                                                                                                 |

| 88        | DVDD     | —         | —          | デジタル系電源端子                                                                                                                                                                     |

| 89        | DVSS     | —         | —          | デジタル系接地端子 (必ず0 Vに接続すること)                                                                                                                                                      |

| 90        | DVDD18_1 | AO        | H          | 内蔵レギュレータ用コンデンサ接続端子 (Flash用1.8 V)                                                                                                                                              |

次ページへ続く

## LC786820E

前ページより続く

| 端子<br>No. | 端子名     | I/O<br>形式 | リセット<br>状態 | 機能説明                                         |

|-----------|---------|-----------|------------|----------------------------------------------|

| 91        | JTRSTB  | I         | 入力         | JTAG用リセット入力<br>(通常時、プルダウン処理、または0Vに接続すること)    |

| 92        | JTCK    | I         | 入力         | JTAG用クロック入力<br>(通常時、プルダウン処理、または0Vに接続すること)    |

| 93        | JTDI    | I         | 入力         | JTAG用データ入力<br>(通常時、プルダウン処理、または0Vに接続すること)     |

| 94        | JTMS    | I         | 入力         | JTAG用モード入力<br>(通常時、プルアップ処理、またはI/O用電源に接続すること) |

| 95        | JTDO    | O         | L          | JTAG用データ出力(通常時、オープンにすること)                    |

| 96        | JTRTCK  | O         | L          | JTAG用リターンクロック出力(通常時、オープンにすること)               |

| 97        | LFOUT   | AO        | 不定         | 電子ボリューム Lchフロント出力                            |

| 98        | LROUT   | AO        | 不定         | 電子ボリューム Lchリア出力                              |

| 99        | LVRIN   | AI        | 入力         | 電子ボリューム Lchボリューム入力                           |

| 100       | DACOUTL | AO        | 不定         | オーディオDAC Lch出力                               |

(注意)

① 使用端子に関して

- 未使用入力端子は、上記リストに対処指定の無いものについては、必ずGND(0V)に接地すること。

- 未使用出力端子は、上記リストに対処指定の無いものについては、オープン処理(何も接続しない)とすること。

- 未使用入出力端子は、上記リストに対処指定の無いものについては、以下の処理を行うこと。

入力設定

内蔵プルダウン抵抗をONとし、オープン処理すること。

内蔵プルダウン抵抗をOFFとする場合は、GND(0V)に接地、またはI/O用電源端子に接続すること。

但し、フェイルセーフの点から、個別に抵抗を介してプルアップ/プルダウン処理することを推奨する。

出力設定

オープン処理すること。

② 源端子に関して

- DVDD, AVDD1, AVDD2, XVDD, VVDD2端子には、必ず同電位を供給すること。

(供給電圧は、許容動作範囲の章を参照)

③リセット状態に関して

- 本LSIは、RESB端子を"L"にするだけでは内部リセットされないので、注意が必要。

リセットの詳細に関しては、「電源投入・リセット制御」の章を参照のこと。

④アナログソース(15~22ピン)未使用端子に関して

- アナログソース(15~22ピン)未使用端子は、入力カップリングコンデンサを介してGNDに接地するか、またはオープン処理(何も接続しない)とすること。

# LC786820E

ブロック図

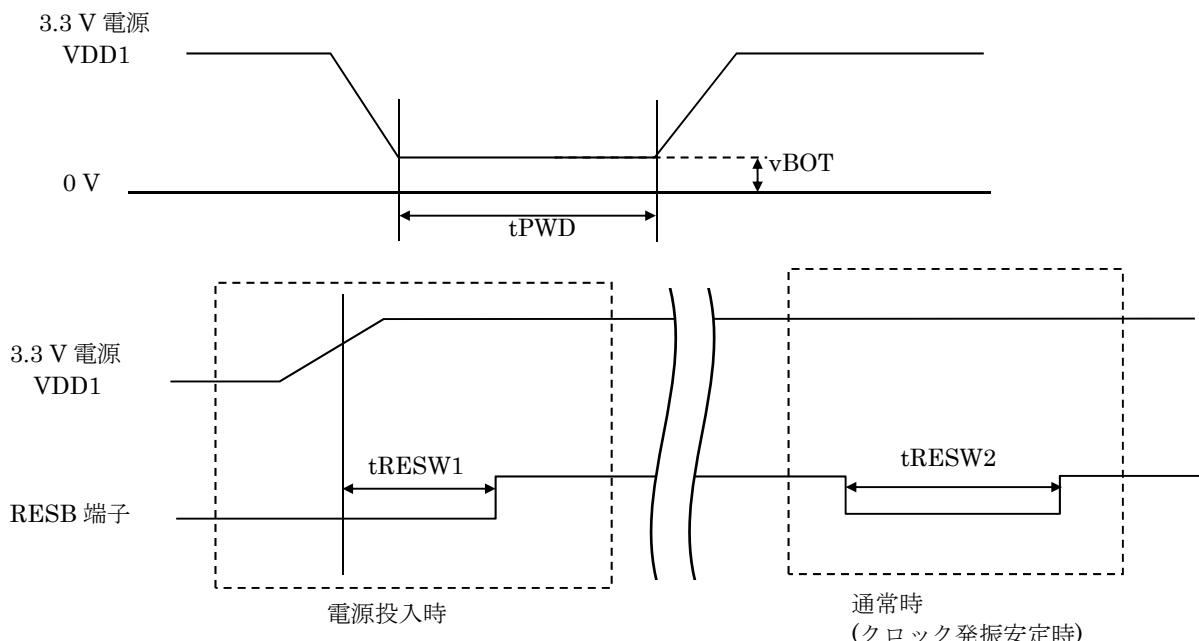

## 電源投入・リセット制御

## ・電源投入時の注意点

## ①リセット端子に関して

内蔵のフラッシュメモリの動作状態を確定させるため、RESB 端子は必ず "L" とする必要がある。

RESB 端子を "H" にして電源投入した場合、フラッシュメモリの動作状態が確定せず、本 LSI の動作が不安定になる場合がある。この場合、RESB 端子制御によるリセットでは復帰できなくなる為、電源投入時は必ず RESB 端子を "L" にすること。

## ②ボリューム出力に関して

電源投入時はボリューム出力は不定となるため、必ず外部でミュート等の対応を行うこと。

## ・パワーON/パワーダウン/リセットタイミング

| Parameter        | Symbol      | Min | Typ | Max | Unit |

|------------------|-------------|-----|-----|-----|------|

| 電源立ち下げ時間         | $t_{PWD}$   | 10  |     |     | ms   |

| 電源立ち下げ電圧         | $v_{BOT}$   | 0   |     | 0.2 | V    |

| リセット期間(電源投入時)    | $t_{RESW1}$ | 20  |     |     | ms   |

| リセット期間(通常時) (*1) | $t_{RESW2}$ | 1   |     |     | ms   |

\*1: 通常時のリセット期間は、クロック(発振子)が安定して発振した状態での期間である。

コマンド等によりクロック(発振子)を OFF 状態にした場合は、発振安定時間を考慮する必要がある。

## ・RESB 端子制御と内蔵フラッシュメモリについて

上記の通り、本 LSI が内蔵しているフラッシュメモリの動作状態のリセットは RESB 端子だけでは制御できず、パワーONリセットをする必要がある。従って、フラッシュメモリが暴走した場合など、電源ON状態でフラッシュメモリをリセットする必要が発生した時には、必ず電源を一旦オフしてパワーONリセットし直す必要がある。一方、RESB 端子によるリセット制御はフラッシュメモリ以外の回路に有効であり、RESB 端子を "L" とし、上記リセット期間に安定したクロックを供給する事で、フラッシュメモリ以外の回路が初期化される。尚、この時フラッシュメモリ自体はスタンバイ状態となり、メモリセルの状態は保持される。

# LC786820E

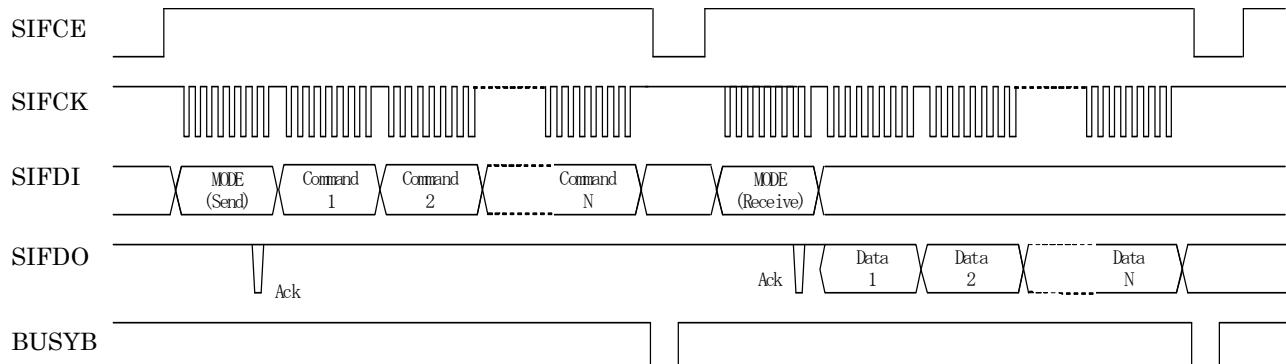

## マイコンインターフェース

ホストマイコンからの送受信は、SPI 系の同期式 SIO 通信にて行う。

データ転送フォーマットは、以下の通り。

- ModeCode 送信における M5~M0 のコードは、本 LSI の内蔵ソフト仕様に従うこと。

M5~M0 に入力されたデータと内部レジスタ値が一致した時に、SIFDO を "L"(Ack) として通信を許可する。

不一致の場合は、SIFDO を "H"(Nack) とし、通信は許可されない。

- コマンド送信であるかデータ受信であるかは、ModeCode 送信時の 7-bit 目のデータにより判定される。

"L" 入力ではコマンド送信、"H" 入力ではデータ受信となる。

- 内蔵マイコンの動作モード(通常/低速)により、通信タイミングのスペックが異なるので注意。

### ・ホストマイコンとの通信インターフェース

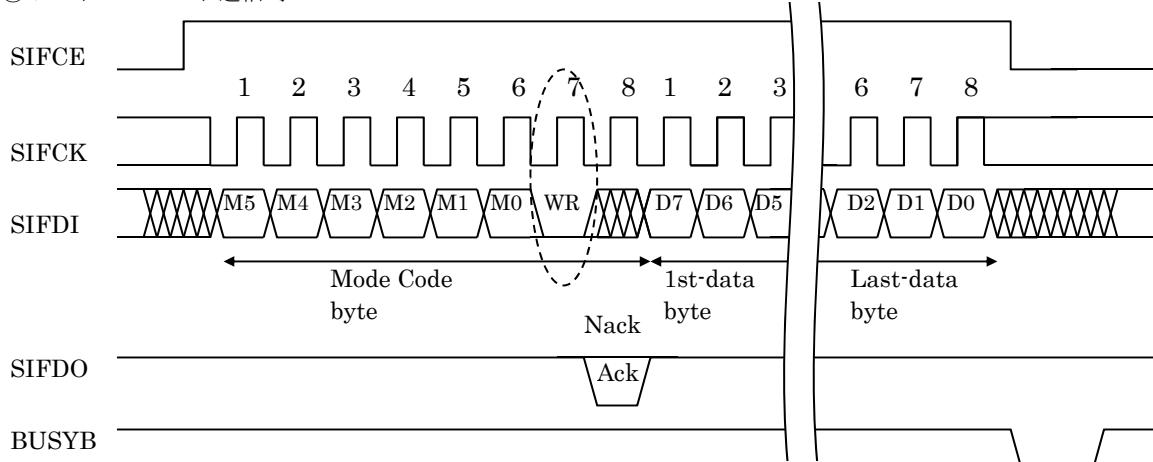

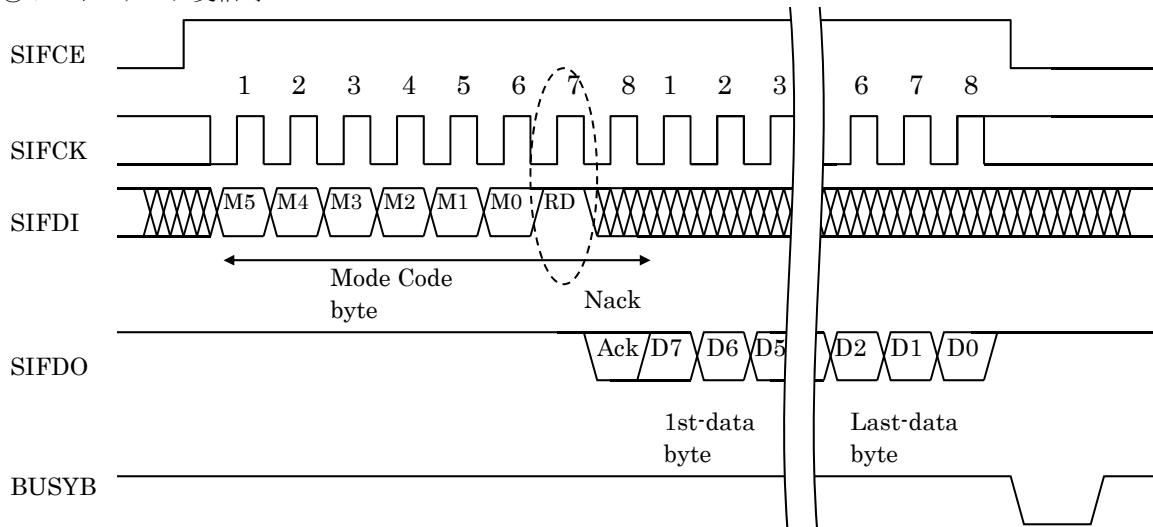

### ・ホストマイコンとの送受信フォーマット

#### ①ホスト : コマンド送信時

#### ②ホスト : データ受信時

## LC786820E

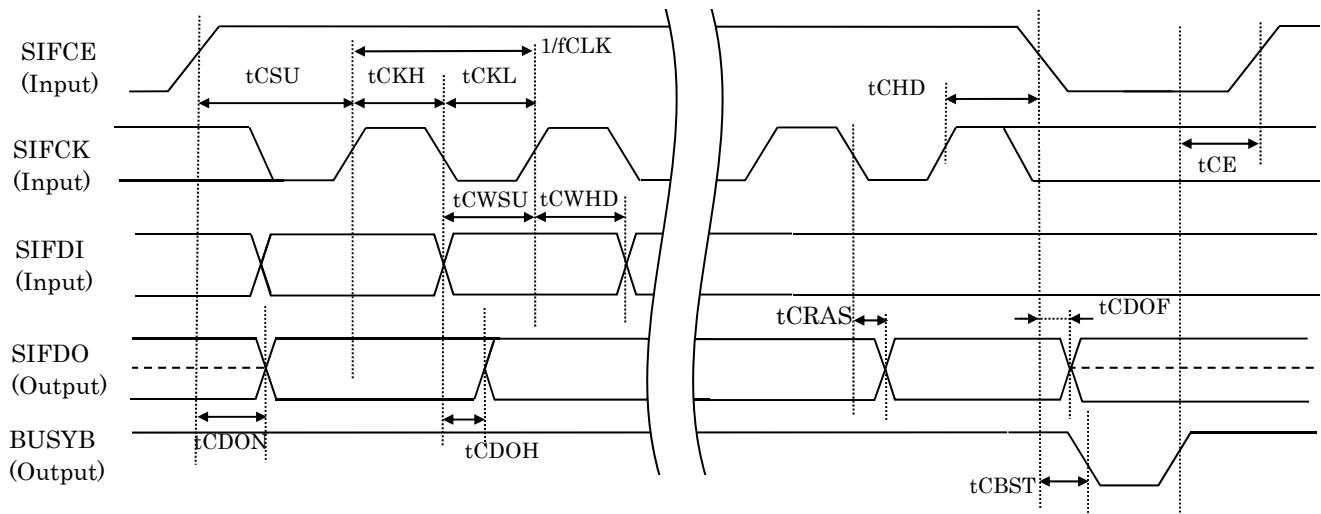

- ・ホストマイコンとの通信タイミング特性

| Parameter | Symbol            | Pin Names | Min          | Typ        | Max          | Unit |

|-----------|-------------------|-----------|--------------|------------|--------------|------|

| 転送クロック周波数 | fCLK              | SIFCK     |              |            | 3.3<br>0.725 | MHz  |

| ns        | 転送クロック "H" 期間     | tCKH      | SIFCK        | 150<br>690 |              |      |

|           | 転送クロック "L" 期間     | tCWL      | SIFCK        | 150<br>690 |              |      |

|           | 転送開始許可時間          | tCE       | BUSYB, SIFCE | 0<br>0     |              |      |

|           | 転送開始セットアップ時間      | tCSU      | SIFCE, SIFCK | 100<br>200 |              |      |

|           | 転送終了ホールド時間        | tCHD      | SIFCE, SIFCK | 100<br>200 |              |      |

|           | データ入力セットアップ時間     | tCWSU     | SIFDI, SIFCK | 75<br>75   |              |      |

|           | データ入力ホールド時間       | tCWHD     | SIFDI, SIFCK | 75<br>200  |              |      |

|           | データ出力 "H" レベル変化時間 | tCDOH     | SIFDO, SIFCK |            | 100<br>350   |      |

|           | データ出力確定時間         | tCRAS     | SIFDO, SIFCK |            | 100<br>350   |      |

|           | 出力ON確定時間 *1       | tCDON     | SIFDO, SIFCE |            | 100<br>100   |      |

|           | 出力OFF確定時間 *1      | tCDOF     | SIFDO, SIFCE |            | 150<br>150   |      |

|           | BUSYB "L" レベル確定時間 | tCBST     | BUSYB        |            | 150<br>350   |      |

※内蔵マイコン動作 上段 : 通常モード

下段 : 低速モード

注 1 : tCDON/tCDOF は、SIFDO 端子を 3-State 出力設定した場合のみ有効である。

## LC786820E

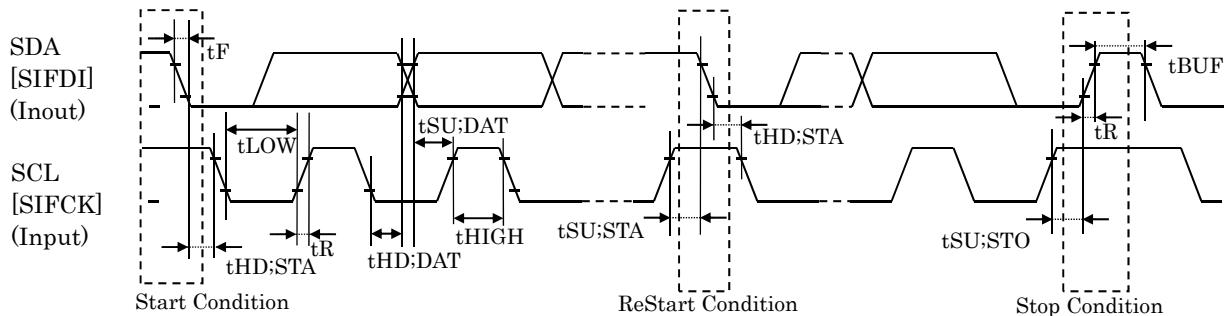

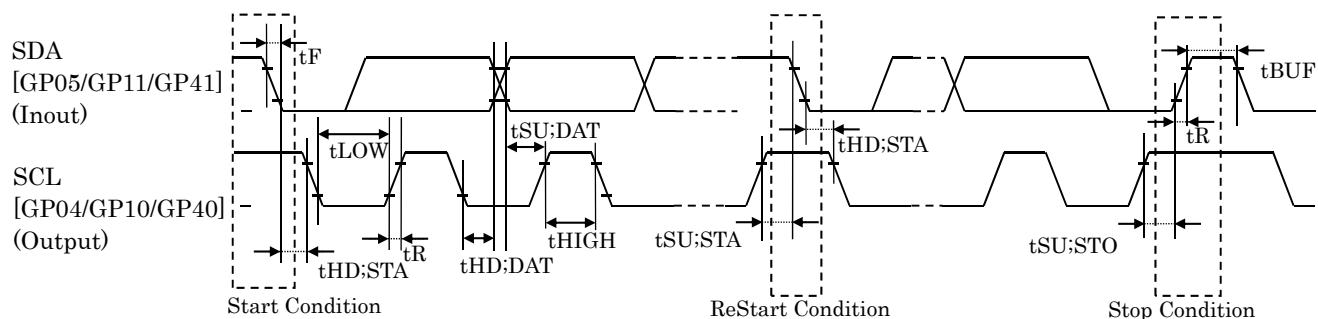

ホストマイコンからの送受信については、IICでの通信も可能である。

対応するモードは

標準モード : 100k bps

高速モード : 400k bps

であり、スレーブアドレスとしては 0x16(7-bit 値) となっている。

- ホストマイコンとの通信(IIC)タイミング条件

| Parameter               | Symbol  | 標準(100k bps) |     | 高速(400k bps) |          | Unit |

|-------------------------|---------|--------------|-----|--------------|----------|------|

|                         |         | Min          | Max | Min          | Max      |      |

| SCL周波数                  | fSCL    | 0            | 100 | 0            | 400      | kHz  |

| バス開放時間                  | tBUF    | 4.7          |     | 1.3          |          | μs   |

| SCL "L" 期間              | tLOW    | 4.7          |     | 1.3          |          | μs   |

| SCL "H" 期間              | tHIGH   | 4.0          |     | 0.6          |          | μs   |

| Start/ReStart条件ホールド時間   | tHD;STA | 4.0          |     | 0.6          |          | μs   |

| Start/ReStart条件セットアップ時間 | tSU;STA | 4.7          |     | 0.6          |          | μs   |

| SDAホールド時間               | tHD;DAT | 0            |     | 0            |          | μs   |

| SDAセットアップ時間             | tSU;DAT | 250          |     | 100          |          | ns   |

| SDA,SCLの立ち上り時間          | tR      |              |     | 1000         | 20+0.1Cb | ns   |

| SDA,SCLの立ち下り時間          | tF      |              |     | 300          | 20+0.1Cb | ns   |

| Stop条件セットアップ時間          | tSU;STO | 4.0          |     | 0.6          |          | μs   |

注 : C<sub>b</sub> は、各バスに接続された負荷のトータル容量 (単位 : pF)

なお、IICを使用する場合、SIFDO、SIFCE、BUSYB 端子については、以下の通り汎用入出力ポートとして使用可能である。

SIFDO : GP00

SIFCE : GP01

BUSYB : GP02

# LC786820E

## シリアル通信ポート

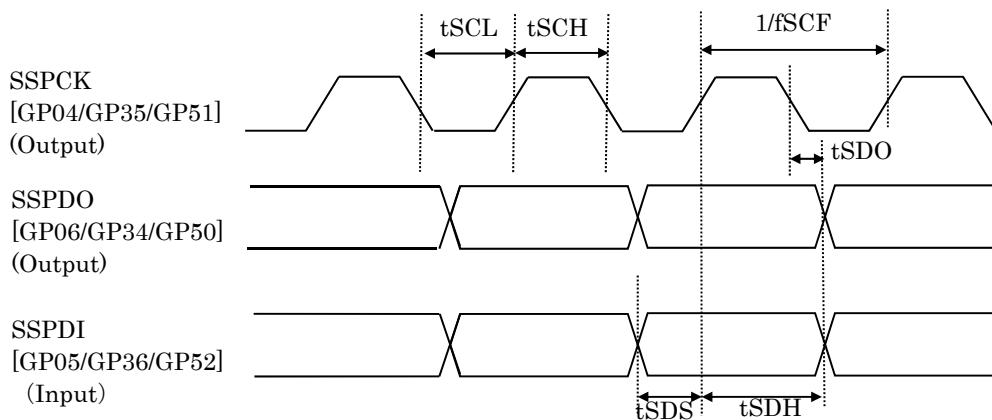

- シリアル通信(SIO)マスター モード入出力タイミング特性

| Parameter     | Symbol    | Signal Names | Min   | Typ | Max   | Unit |

|---------------|-----------|--------------|-------|-----|-------|------|

| SIOクロック周波数    | $f_{SCF}$ | SSPCK        | 0.008 |     | 5.0   | MHz  |

| SIOクロック "H"期間 | $t_{SCH}$ | SSPCK        | 100   |     | 62500 | ns   |

| SIOクロック "L"期間 | $t_{SCL}$ | SSPCK        | 100   |     | 62500 |      |

| データ出力確定時間     | $t_{SDO}$ | SSPDO,SSPCK  |       |     | 90    |      |

| データ入力セットアップ時間 | $t_{SDS}$ | SSPDI,SSPCK  | 50    |     |       |      |

| データ入力ホールド時間   | $t_{SDH}$ | SSPDI,SSPCK  | 75    |     |       |      |

注：内蔵マイコン(ARM7)を通常モードにて動作させた場合。

- シリアル通信(IIC)マスター モード入出力タイミング条件

| Parameter               | Symbol       | 標準(100k bps) |      | 高速(400k bps) |     | Unit    |

|-------------------------|--------------|--------------|------|--------------|-----|---------|

|                         |              | Min          | Max  | Min          | Max |         |

| SCL周波数                  | $f_{SCL}$    | 0            | 100  | 0            | 400 | kHz     |

| バス開放時間                  | $t_{BUF}$    | 4.7          |      | 1.3          |     | $\mu s$ |

| SCL "L" 期間              | $t_{LOW}$    | 4.7          |      | 1.3          |     | $\mu s$ |

| SCL "H" 期間              | $t_{HIGH}$   | 4.0          |      | 0.6          |     | $\mu s$ |

| Start/ReStart条件ホールド時間   | $t_{HD;STA}$ | 4.0          |      | 0.6          |     | $\mu s$ |

| Start/ReStart条件セットアップ時間 | $t_{SU;STA}$ | 4.7          |      | 0.6          |     | $\mu s$ |

| SDAホールド時間               | $t_{HD;DAT}$ | 0            |      | 0            |     | $\mu s$ |

| SDAセットアップ時間             | $t_{SU;DAT}$ | 250          |      | 100          |     | ns      |

| SDA, SCLの立ち上り時間         | $t_R$        |              | 1000 | $20+0.1C_b$  | 300 | ns      |

| SDA, SCLの立ち下り時間         | $t_F$        |              | 300  | $20+0.1C_b$  | 300 | ns      |

| Stop条件セットアップ時間          | $t_{SU;STO}$ | 4.0          |      | 0.6          |     | $\mu s$ |

注：Cb は、各バスに接続された負荷のトータル容量 (単位 : pF)

## LC786820E

USB端子特性 /  $T_a = -40 \sim 85^\circ\text{C}$ ,  $V_{DD1} = 3.0 \sim 3.6 \text{ V}$ ,  $DVSS = AVSS1 = AVSS2 = XVSS = 0 \text{ V}$

| Parameter         | Symbol   | Pin Names                       | Conditions                      | MIN   | TYP | MAX   | Unit          |

|-------------------|----------|---------------------------------|---------------------------------|-------|-----|-------|---------------|

| 入力「H」レベル電圧        | VIH(USB) | UDM1,<br>UDP1,<br>UDM2,<br>UDP2 |                                 | 2.0   |     |       | V             |

| 入力「L」レベル電圧        | VIL(USB) |                                 |                                 |       |     | 0.8   |               |

| 入力リード電流           | ILI      |                                 | 出力：オフ                           | -10.0 |     | 10.0  | $\mu\text{A}$ |

| 差分入力感度            | VDI      |                                 | $ (\text{UDP}) - (\text{UDM}) $ | 0.2   |     |       | V             |

| コモンモード電圧範囲        | VCM      |                                 | VDIレンジ含む                        | 0.8   |     | 2.5   | V             |

| 出力「H」レベル電圧        | VOH(USB) |                                 |                                 | 2.8   |     | 3.6   | V             |

| 出力「L」レベル電圧        | VOL(USB) |                                 |                                 | 0.0   |     | 0.3   | V             |

| 出力信号<br>クロスオーバー電圧 | VCR      |                                 |                                 | 1.3   |     | 2.0   | V             |

| USBデータ立ち上り時間      | TUR      |                                 | CL = 50 pF                      | 4.0   |     | 20.0  | ns            |

| USBデータ立ち下り時間      | TUF      |                                 |                                 | 4.0   |     | 20.0  |               |

| D+/D- プルダウン抵抗     | RPD      | UDP1                            |                                 | 14.25 |     | 24.8  | k $\Omega$    |

| D+ プルアップ抵抗        | RPUI     |                                 | アイドル時                           | 0.9   |     | 1.575 | k $\Omega$    |

| D- ソース電圧          | RPUR     |                                 | 受信時                             | 1.425 |     | 3.09  |               |

| VDM SRC           | VDM SRC  | UDM1                            |                                 | 0.5   |     | 0.7   | V             |

| VLGC_SRC          | VLGC_SRC |                                 |                                 | 0.8   |     | 2.0   | V             |

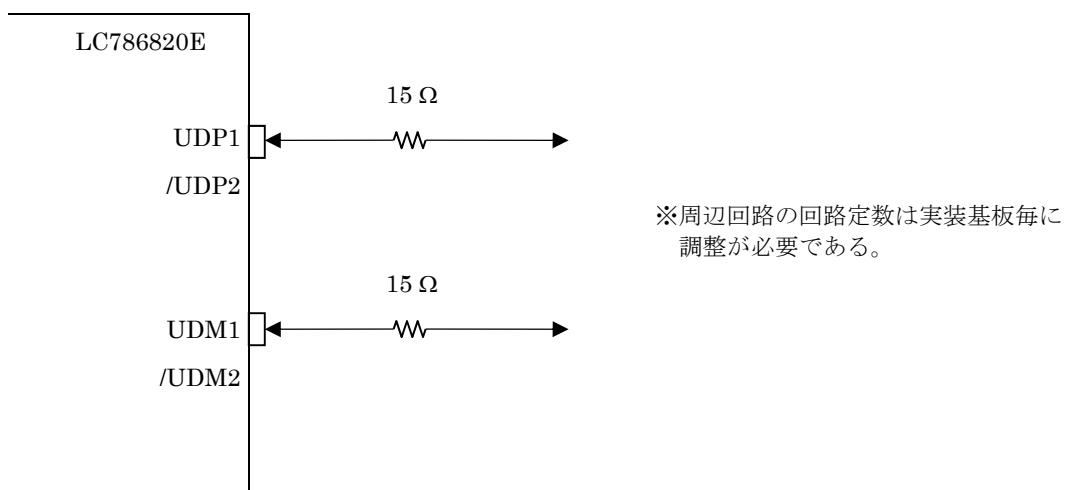

・ USB ポート参考周回路例

# LC786820E

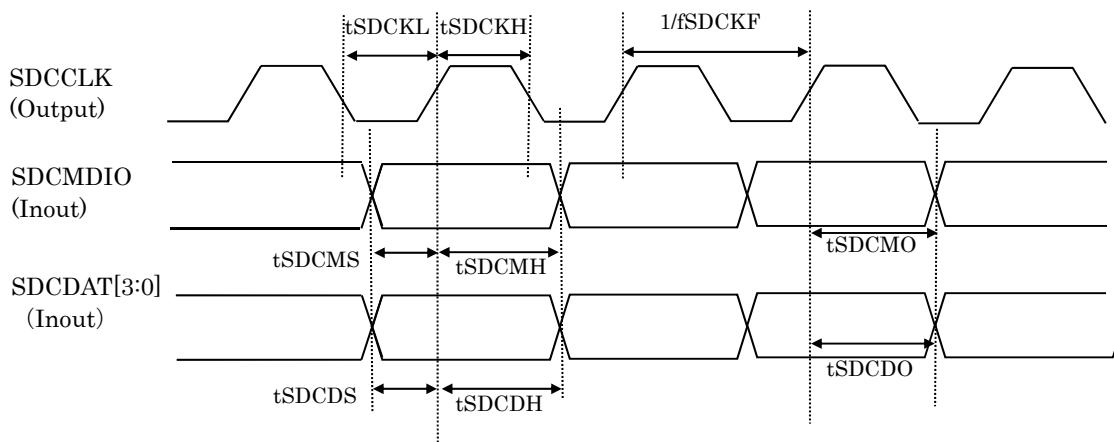

## SDメモリカードインターフェース

- SDメモリカード入出力タイミング特性

※信号名と端子との関係

|           |        |           |        |           |        |

|-----------|--------|-----------|--------|-----------|--------|

| SDCCLK    | : GP34 | SDCMDIO   | : GP35 | SDCDAT[3] | : GP36 |

| SDCDAT[2] | : GP37 | SDCDAT[1] | : GP32 | SDCDAT[0] | : GP33 |

| Parameter      | Symbol | Signal Names        | Min  | Typ  | Max  | Unit |

|----------------|--------|---------------------|------|------|------|------|

| SDCCLKクロック周波数  | fSDCKF | SDCCLK              |      | 6.0  |      | MHz  |

| SDCCLK "H"期間   | tSDCKH | SDCCLK              |      | 83.3 |      |      |

| SDCCLK "L"期間   | tSDCKL | SDCCLK              |      | 83.3 |      |      |

| コマンド入力セットアップ時間 | tSDCMS | SDCMDIO, SDCCLK     | 30.0 |      |      |      |

| コマンド入力ホールド時間   | tSDCMH | SDCMDIO, SDCCLK     | 30.0 |      |      |      |

| コマンド出力確定時間     | tSDCMO | SDCMDIO, SDCCLK     |      |      | 30.0 |      |

| データ入力セットアップ時間  | tSDCDS | SDCDAT[3:0], SDCCLK | 30.0 |      |      |      |

| データ入力ホールド時間    | tSDCDH | SDCDAT[3:0], SDCCLK | 30.0 |      |      |      |

| データ出力確定時間      | tSDCDO | SDCDAT[3:0], SDCCLK |      |      | 30.0 |      |

注：内蔵マイコン(ARM7)は通常モードにて使用すること。低速モードでは使用不可。

# LC786820E

## オーディオデータ入出力特性

### ・AC 電気的特性

/ Ta = 25°C, V<sub>DD1</sub> = 3.3 V, DVSS = AVSS1 = AVSS2 = XVSS = 0 V

F<sub>s</sub> = 44.1 kHz, 信号周波数 1 kHz, 測定帯域 = 10 Hz~20 kHz

| Parameter                    | Symbol | Pin Names                                                               | Conditions                           | Min    | Typ                               | Max    | Unit            |

|------------------------------|--------|-------------------------------------------------------------------------|--------------------------------------|--------|-----------------------------------|--------|-----------------|

| (入力セレクタ+ADC)                 |        |                                                                         |                                      |        |                                   |        |                 |

| フルスケール<br>アナログ入力レベル          | S/N    | L1IN,<br>R1IN,<br>L2IN,<br>R2IN,<br>L3INP,<br>L3INN,<br>R3INP,<br>R3INN |                                      | 2.605  | 2.805<br>(0.85×V <sub>DD1</sub> ) | 3.005  | V <sub>pp</sub> |

| 入力インピーダンス                    |        |                                                                         |                                      | 20     | 30                                |        | kΩ              |

| ゲイン設定レベル                     |        |                                                                         |                                      | -12    |                                   | 19     | dB              |

| ゲイン設定ステップ                    |        |                                                                         |                                      |        | 1                                 |        | dB              |

| ゲイン設定ステップ間誤差                 |        |                                                                         |                                      | -0.5   |                                   | 0.5    | dB              |

| Signal to Noise Ratio        |        |                                                                         | 0 dBデータ,<br>20 kHz-LPF,<br>Aフィルタ使用   | 90     | 95                                |        | dB              |

| Dynamic Range                |        |                                                                         | -60 dBデータ,<br>20 kHz-LPF,<br>Aフィルタ使用 | 90     | 95                                |        | dB              |

| Total Harmonic Distortion    |        |                                                                         | 入力条件 :<br>-3 dBFS                    |        | -85                               | -80    | dB              |

| Cross Talk1                  |        |                                                                         | チャンネル間                               |        | -100                              | -85    | dB              |

| Cross Talk2                  |        |                                                                         | ソース間                                 |        | -100                              | -85    | dB              |

| (ADC Digital Filter)         |        |                                                                         |                                      |        |                                   |        |                 |

| 通過域周波数                       |        |                                                                         | ±0.04 dB                             | 0      |                                   | 0.4535 | F <sub>s</sub>  |

| 阻止域周波数                       |        |                                                                         |                                      | 0.5465 |                                   |        | F <sub>s</sub>  |

| 通過域リップル                      |        |                                                                         |                                      |        |                                   | ±0.04  | dB              |

| 阻止域減衰量                       |        |                                                                         | >24.1 kHz                            | -69    |                                   |        | dB              |

| DCオフセットキャンセル用<br>HPFカットオフ周波数 |        |                                                                         |                                      |        | 0.00002                           |        | F <sub>s</sub>  |

| (オーディオDAC)                   |        |                                                                         |                                      |        |                                   |        |                 |

| フルスケール<br>アナログ出力レベル          | S/N    | DACOUTL,<br>DACOUTR,<br>DACOUTS                                         |                                      | 2.605  | 2.805<br>(0.85×V <sub>DD1</sub> ) | 3.005  | V <sub>pp</sub> |

| Signal to Noise Ratio        |        |                                                                         | 0 dBデータ,<br>20 kHz-LPF,<br>Aフィルタ使用   |        | 106                               |        | dB              |

| Dynamic Range                |        |                                                                         | -60 dBデータ,<br>20 kHz-LPF,<br>Aフィルタ使用 |        | 106                               |        | dB              |

| Total Harmonic Distortion    |        |                                                                         | 0 dBデータ,<br>20 kHz-LPF               |        | -85                               | -80    | dB              |

| Cross Talk                   |        |                                                                         | 0 dBデータ,<br>20 kHz-LPF               |        | -100                              | -85    | dB              |

| (DAC Digital Filter)         |        |                                                                         |                                      |        |                                   |        |                 |

| 通過域周波数                       |        |                                                                         | ±0.015 dB                            | 0      |                                   | 0.4535 | F <sub>s</sub>  |

| 阻止域周波数                       |        |                                                                         |                                      | 0.5465 |                                   |        | F <sub>s</sub>  |

| 通過域リップル                      |        |                                                                         |                                      |        |                                   | ±0.015 | dB              |

| 阻止域減衰量                       |        |                                                                         |                                      | -62    |                                   |        | dB              |

| DCオフセットキャンセル用<br>HPFカットオフ周波数 |        |                                                                         | -3dB                                 |        | 0.0000385                         |        | F <sub>s</sub>  |

# LC786820E

| Parameter     | Symbol | Pin Names                           | Conditions   | Min    | Typ  | Max   | Unit |

|---------------|--------|-------------------------------------|--------------|--------|------|-------|------|

| (電子ボリューム)     |        |                                     |              |        |      |       |      |

| 入力インピーダンス     |        | LVRIN,<br>RVRIN,                    |              | 7.5    | 10   |       | kΩ   |

|               |        | SWIN                                |              | 15     | 20   |       | kΩ   |

| ボリューム設定範囲     |        | LFOUT,<br>LROUT,<br>RFOUT,<br>RROUT |              | -70    |      | 0     | dB   |

| ミュートレベル       |        |                                     |              | 80     | 90   |       | dB   |

| ボリュームステップ     |        | SWOUT                               | 0 ~ -32 dB   |        | 0.25 |       | dB   |

|               |        |                                     | -32 ~ -70 dB |        | 1.0  |       | dB   |

| ボリューム設定ステップ誤差 |        | SWOUT                               | 0 ~ -32 dB   | -0.125 |      | 0.125 | dB   |

|               |        |                                     | -32 ~ -70 dB | -0.5   |      | 0.5   | dB   |

- オーディオデジタルデータ入出力機能

- オーディオ入出力 対応フォーマット

|    | モード                             | ビット長             | スロット長               | Fs384クロック          |

|----|---------------------------------|------------------|---------------------|--------------------|

| 入力 | IIS<br>MSBファースト右詰<br>MSBファースト左詰 | 16-bit<br>24-bit | 32 fs, 48 fs, 64 fs | 内部クロック<br>外部入力クロック |

|    | IIS<br>MSBファースト右詰<br>MSBファースト左詰 | 16-bit<br>24-bit | 32 fs, 48 fs, 64 fs | Fs384クロック<br>出力    |

| 出力 | IIS<br>MSBファースト右詰<br>MSBファースト左詰 | 16-bit<br>24-bit | 32 fs, 48 fs, 64 fs |                    |

|    |                                 |                  |                     |                    |

- 適用端子

|    | LRCK | BCK  | DATA | Fs384クロック |

|----|------|------|------|-----------|

| 入力 | GP30 | GP31 | GP32 | GP33      |

|    | GP40 | GP41 | GP42 | GP43      |

|    | GP50 | GP51 | GP52 | GP53      |

| 出力 | GP30 | GP31 | GP32 | GP33      |

|    | GP40 | GP41 | GP42 | GP43      |

|    | GP50 | GP51 | GP52 | GP53      |

注：各端子を同時にオーディオ入力に設定した場合、LSI の内部では以下の優先順位で処理される。

①GP30～33, ②GP40～43, ③GP50～53

例えば上記端子を全てオーディオ入力モードに設定した場合、実際にオーディオ処理されるのは GP30～33 で入力されたデータで、GP40～43, GP50～53 から入力されるデータは、LSI 内部では処理されない。

- その他

- オーディオ出力は、3 種類の Fs(32 kHz / 44.1 kHz / 48 kHz)に対応可能。

- 外部オーディオ入力時、GP14 / GP46 端子よりエンファシス信号の入力にも対応。

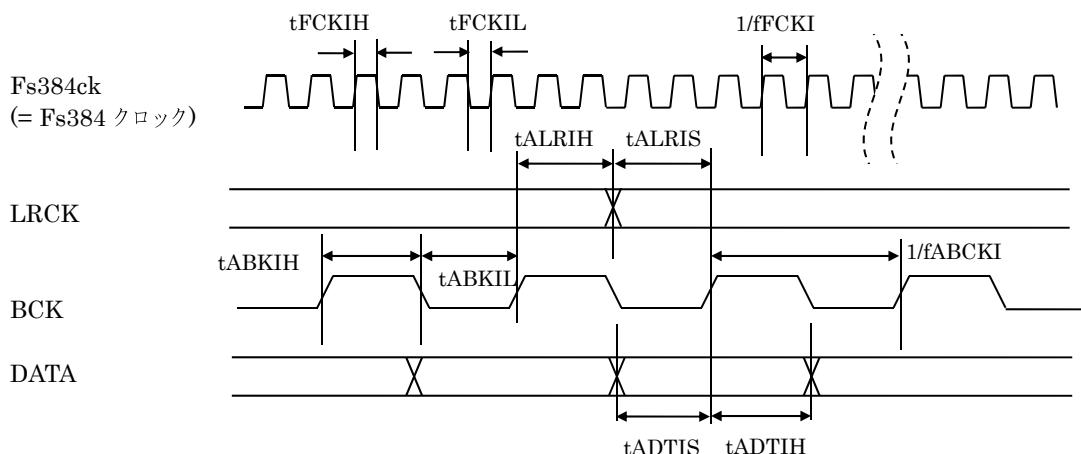

- オーディオデータ入力タイミング特性

## LC786820E

| Parameter       | Symbol | Signal Names | Min | Typ | Max  | Unit |

|-----------------|--------|--------------|-----|-----|------|------|

| Fs384クロック周波数    | fFCKI  | Fs384ck      |     |     | 20.0 | MHz  |

| Fs384クロック "H"期間 | tFCKIH | Fs384ck      | 20  |     |      | ns   |

| Fs384クロック "L"期間 | tFCKIL | Fs384ck      | 20  |     |      | ns   |

| ビットクロック周波数      | fABCKI | BCK          |     |     | 3.3  | MHz  |

| ビットクロック "H"期間   | tABKIH | BCK          | 120 |     |      | ns   |

| ビットクロック "L"期間   | tABKIL | BCK          | 120 |     |      | ns   |

| LRCK入力セットアップ時間  | tALRIS | LRCK, BCK    | 30  |     |      | ns   |

| LRCK入力ホールド時間    | tALRIH | LRCK, BCK    | 30  |     |      | ns   |

| DATA入力セットアップ時間  | tADTIS | DATA, BCK    | 30  |     |      | ns   |

| DATA入力ホールド時間    | tADTIH | DATA, BCK    | 30  |     |      | ns   |

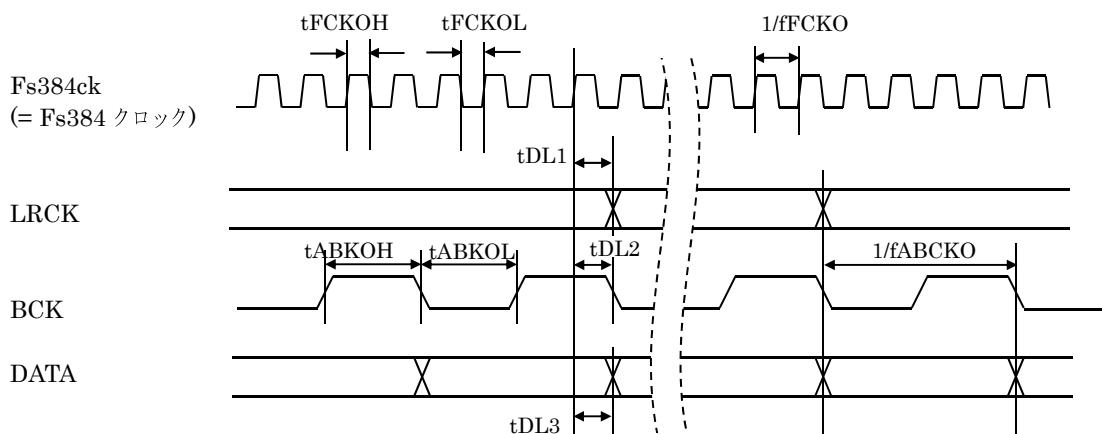

・オーディオデータ出力タイミング特性

| Parameter       | Symbol | Signal Names  | Min | Typ           | Max | Unit |

|-----------------|--------|---------------|-----|---------------|-----|------|

| Fs384クロック周波数    | fFCKO  | Fs384ck       |     | 16.9344<br>※1 |     | MHz  |

| Fs384クロック "H"期間 | tFCKOH | Fs384ck       |     | 29.5<br>※1    |     | ns   |

| Fs384クロック "L"期間 | tFCKOL | Fs384ck       |     | 29.5<br>※1    |     | ns   |

| ビットクロック周波数      | fABCKO | BCK           |     | 2.1168<br>※1  |     | MHz  |

| ビットクロック "H"期間   | tABKOH | BCK           |     | 236.2<br>※1   |     | ns   |

| ビットクロック "L"期間   | tABKOL | BCK           |     | 236.2<br>※1   |     | ns   |

| LRCK出力遅延時間      | tDL1   | LRCK, Fs384ck | 0   |               | 50  | ns   |

| BCK出力遅延時間       | tDL2   | BCK, Fs384ck  | 0   |               | 50  | ns   |

| DATA出力遅延時間      | tDL3   | DATA, Fs384ck | 0   |               | 50  | ns   |

※1：出力を  $F_s = 44.1 \text{ kHz}$  にして、出力フォーマットのスロット長を 48 fs に設定した場合。

# LC786820E

## ストリームデータ入出力機能

ストリームデータの入出力については、以下の 2 つの方法がある。

### ① 4 線方式

ストリーム入力 : STREQO="H" 出力期間に、STLRCKI/STBCKI/STDATI を入力する。4 線方式の場合、STLRCKI/STBCKI/STDATI(入力時)の各 3 線については、通常のオーディオ入出力フォーマットと同じように、STLRCKI(入力時)の 1 周期に 4 byte (32-bit) データの送受信を行う。

### ② 3 線方式

ストリーム入力 : STREQO="H" 出力期間に、STBCKI/STDATI を入力する。

ストリーム出力 : STREQI="H" 入力期間に、STBCKO/STDATO を出力する。

3 線方式の場合、STREQO の状態に応じてビットクロックとデータを入力、または STREQI の状態に応じてビットクロックとデータを出力するのみであり、データの転送単位は 2 byte (16-bit) となる。なお、ストリーム出力の 3 線方式においては、クロック(STBCKI)を入力してデータのみを出力させる事も可能である。

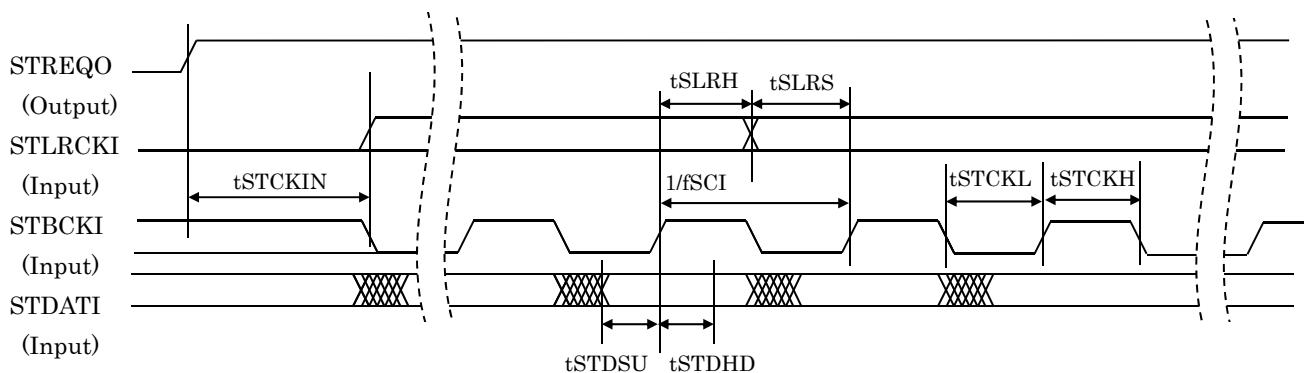

### ・ストリームデータ入力タイミング特性

※信号名と端子との関係

STREQO : GP33/GP43/GP53

STBCKI : GP31/GP41/GP51

STLRCKI : GP30/GP40/GP50

STDATI : GP32/GP42/GP52

注：各端子を同時にストリーム入力に設定した場合、LSI の内部では以下の優先順位で処理される。

①GP30～33, ②GP40～43, ③GP50～53

例えば上記端子を全てストリーム入力モードに設定した場合、実際にデータが処理されるのは GP30～33 で入力されたデータで、GP40～43, GP50～53 から入力されるデータは、LSI 内部では処理されない。

| Parameter       | Symbol  | Signal Names               | Min | Typ | Max  | Unit |

|-----------------|---------|----------------------------|-----|-----|------|------|

| STBCKIクロック周波数   | fSCI    | STBCKI                     |     |     | 4.24 | MHz  |

| ストリーム入力開始時間     | tSTCKIN | STREQO,<br>STBCKI, STLRCKI | 50  |     |      | ns   |

| STBCKI "H"期間    | tSTCKH  | STBCKI                     | 100 |     |      | ns   |

| STBCKI "L"期間    | tSTCKL  | STBCKI                     | 100 |     |      | ns   |

| STLRCKIセットアップ時間 | tSLRS   | STLRCKI, STBCKI            | 75  |     |      | ns   |

| STLRCKIホールド時間   | tSLRH   | STLRCKI, STBCKI            | 75  |     |      | ns   |

| STDATIセットアップ時間  | tSTDHSU | STDATI, STBCKI             | 75  |     |      | ns   |

| STDATIホールド時間    | tSTDHD  | STDATI, STBCKI             | 75  |     |      | ns   |

注：上図は STBCKI の立ち上り同期でデータ入力する場合。立ち下り同期でもタイミングは共通。

## LC786820E

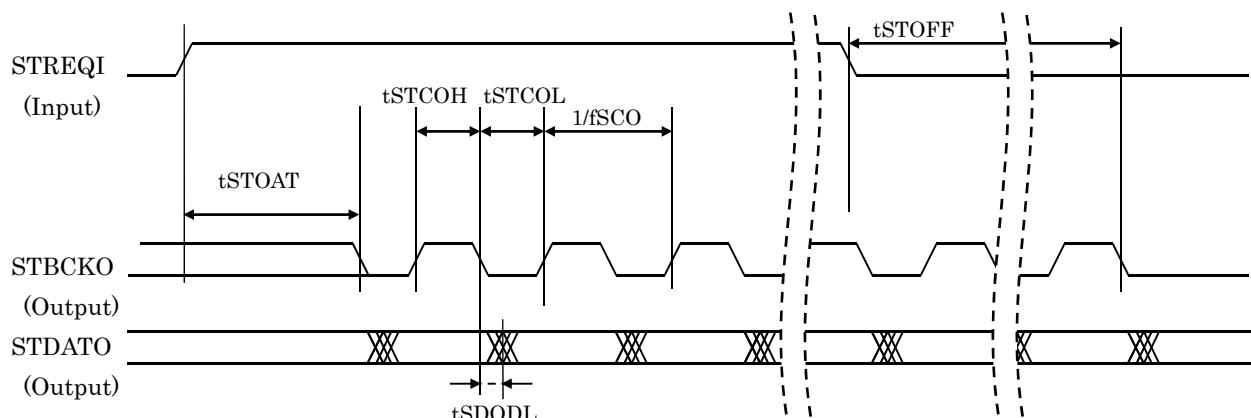

- ・ストリームデータ出力タイミング特性 : STBCK 出力モード

※信号名と端子との関係

STREQI : GP33/GP43/GP53

STBCKO : GP31/GP41/GP51

STDATO : GP32/GP42/GP52

| Parameter     | Symbol | Signal Names   | Min | Typ | Max             | Unit |

|---------------|--------|----------------|-----|-----|-----------------|------|

| STBCKOクロック周波数 | fSCO   | STBCKO         |     |     | 4.24            | MHz  |

| ストリーム出力開始時間   | tSTOAT | STREQI, STBCKO |     |     | (1/fSCO)<br>×48 | ns   |

| ストリーム出力停止時間   | tSTOFF | STREQI, STBCKO |     |     | (1/fSCO)<br>×48 | ns   |

| STBCKO "H"期間  | tSTCOH | STBCKO         | 100 |     |                 | ns   |

| STBCKO "L"期間  | tSTCOL | STBCKO         | 100 |     |                 | ns   |

| STDATO出力遅延時間  | tSDODL | STDATO, STBCKO | 0   |     | 50              | ns   |

注：上図は STBCKO の立ち下り同期でデータ出力する場合。立ち上り同期でもタイミングは共通。

## LC786820E

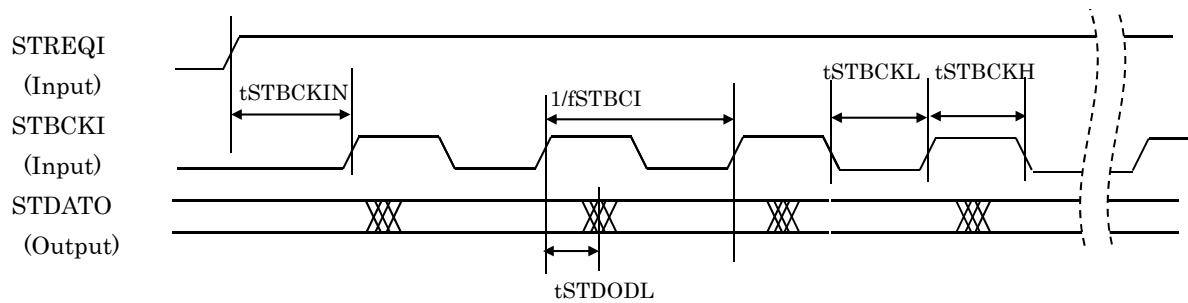

- ・ストリームデータ出力タイミング特性 : STBCKI 入力モード

※信号名と端子との関係

STREQI : GP33/GP43/GP53

STBCKI : GP31/GP41/GP51

STDATO : GP32/GP42/GP52

| Parameter     | Symbol   | Signal Names      | Min  | Typ | Max  | Unit |

|---------------|----------|-------------------|------|-----|------|------|

| STBCKIクロック周期  | fSTBCI   | STBCKI            |      |     | 1.25 | MHz  |

| STBCKI 入力開始時間 | tSTBCKIN | STREQI,<br>STBCKI | 1000 |     |      | ns   |

| STBCKI "H"期間  | tSTBCKH  | STBCKI            | 400  |     |      | ns   |

| STBCKI "L"期間  | tSTBCKL  | STBCKI            | 400  |     |      | ns   |

| STDATO 出力遅延時間 | tSTDODL  | STBCKI,<br>STDATO |      |     | 250  | ns   |

注：上図は STBCKI を "L" から開始する場合。

<補足>

クロック入力モードは 2 種類に対応し、データ出力タイミングは以下の通り変化する。

①STBCKI = "L" から開始する場合

STDATO は、STBCKI の立ち上りエッジに同期して出力される。

②STBCKI = "H" から開始する場合

STDATO は、STBCKI の立ち下りエッジに同期して出力される。

①, ②いずれのモードを使っても、出力タイミング特性は同じである。

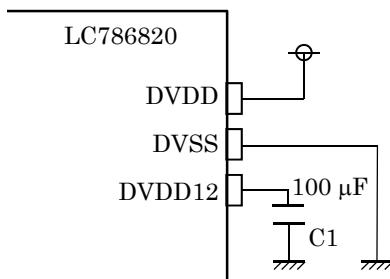

# LC786820E

内蔵レギュレータ特性 /  $T_a = -40\sim85^\circ\text{C}$ , DVSS = AVSS1 = AVSS2 = XVSS = 0 V

| Parameter | Symbol | Condition                       | Min  | Typ  | Max  | Unit |

|-----------|--------|---------------------------------|------|------|------|------|

| 出力電圧      | DVDD12 | $V_{DD1} = 3.0\sim3.6\text{ V}$ | 1.08 | 1.20 | 1.32 | V    |

| 負荷電流      | Iope   | $V_{DD1} = 3.3\text{ V}$        |      |      | 200  | mA   |

<補足> 負荷電流は、内蔵レギュレータ 2 箇所の合計値。

## 1.2 V レギュレータ周辺部参考回路

- ※ レギュレータ端子 2 箇所(No.44, 87)で同じ処理をすること

- ※ C1 は発振止めコンデンサである。

温度変化などにより容量値が変化すると発振の可能性があるため、動作温度範囲においては、低 ESR、かつ、容量値は 50  $\mu\text{F}$  以上を確保すること。(推奨は 100  $\mu\text{F}$ )

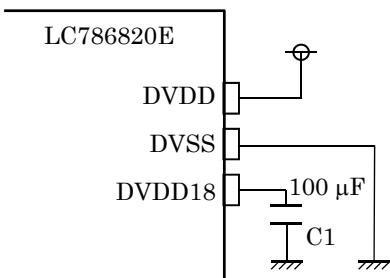

| Parameter | Symbol | Condition                       | Min  | Typ  | Max  | Unit |

|-----------|--------|---------------------------------|------|------|------|------|

| 出力電圧      | DVDD18 | $V_{DD1} = 3.0\sim3.6\text{ V}$ | 1.65 | 1.80 | 1.95 | V    |

| 負荷電流      | Iope   | $V_{DD1} = 3.3\text{ V}$        |      |      | 50   | mA   |

## 1.8 V レギュレータ周辺部参考回路

- ※ レギュレータ端子 No. 90 に対して本処理をすること

- ※ C1 は発振止めコンデンサである。

温度変化などにより容量値が変化すると発振の可能性があるため、動作温度範囲においては、低 ESR、かつ、容量値は 50  $\mu\text{F}$  以上を確保すること。(推奨は 100  $\mu\text{F}$ )

# LC786820E

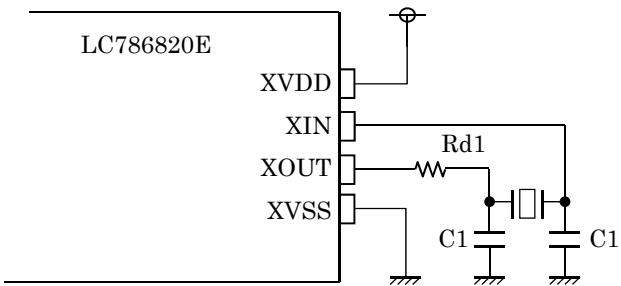

## 発振回路

### 発振回路参考例

- XIN / XOUT 接続発振子 : 12.0000 MHz

- ・システムメインクロック、USB 制御用

- ・推奨発振子

(株)日本電波工業

| 型番       | 発振周波数  | 推奨定数                   |

|----------|--------|------------------------|

| NX3225GA | 12 MHz | Rd1 = 1 kΩ, C1 = 12 pF |

### <注意>

- 発振回路特性はセット基板によって変わる可能性があるため、使用する発振子メーカーに問い合わせの上、上記各定数を決定すること。

- XIN / XOUT で使用する発振子の精度については USB 規格を満足する精度の発振子を使用すること。

- ノイズ等による発振クロックの乱れは誤動作の原因となる。これを防ぐために発振回路に使用する抵抗、コンデンサ等の部品はできる限り XIN / XOUT 端子近傍に配置し、配線長も最短となるよう考慮すること。

また、温度変化などにより外付け定数が変化すると発振精度に影響がでる可能性があるため、動作温度保証範囲においては外付け定数値が変わらないよう、部品選定には注意が必要である。

- XIN / XOUT の内部構成については、「アナログ端子内部等価回路」の項を参照のこと。

# LC786820E

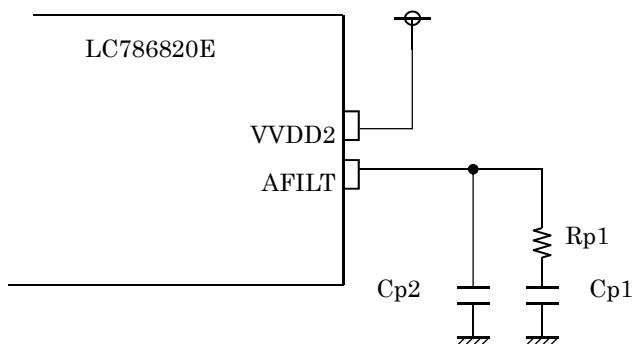

## PLL 回路

### PLL 回路参考例

#### ・PLLについて

LC786820E には、PLL1、PLL2 と 2 つの PLL を搭載している。

PLL1 が、システムクロック生成用、PLL2 が Audio クロック生成である。

#### ・PLL2 用外付けフィルタ定数

| PLL2 定数                                                                    |

|----------------------------------------------------------------------------|

| $Rp1 = 3.3 \text{ k}\Omega / Cp1 = 3300 \text{ pF} / Cp2 = 220 \text{ pF}$ |

#### 〈注意〉

- AFILT に接続する抵抗(Rp1)・容量(Cp1, Cp2)は、オーディオ生成用/システムクロック生成用の PLL のフィルタ回路である。

ノイズ等による発振クロックの乱れは誤動作の原因となる。これを防ぐために、フィルタ回路を構成する抵抗、コンデンサ等の部品はできる限り AFILT 端子近傍に配置し、配線長も最短となるよう考慮すること。

また、温度変化などによりフィルタ定数が変化すると PLL の発振が不安定となり、オーディオ再生クロックが不安定になるため、オーディオ信号の入力(ADC 動作)や出力 (各種フィルタ、DAC 動作) が不安定となり、オーディオ再生に影響が出る。

従って、動作温度保証範囲においてはフィルタ定数が変わらないよう、部品選定には注意が必要である。

- AFILT の内部構成については、「アナログ端子内部等価回路」の項を参照のこと。

# LC786820E

## アナログ端子内部等価回路

| 端子名<br>( ) 内端子番号                                                                                         | 内部等価回路 |

|----------------------------------------------------------------------------------------------------------|--------|

| LFOUT (97)<br>LROUT (98)<br>RROUT (7)<br>RFOUT (8)<br>SWOUT (11)                                         |        |

| LVRIN (99)<br>RVRIN (6)<br>SWIN (10)                                                                     |        |

| DACOUTL (100)<br>DACOUTR (5)<br>DACOUTS (9)                                                              |        |

| L1IN (21)<br>R1IN (22)<br>L2IN (19)<br>R2IN (20)<br>L3INP (15)<br>L3INN (16)<br>R3INP (17)<br>R3INN (18) |        |

| VREF_ADC (12)                                                                                            |        |

# LC786820E

| 端子名<br>( ) 内端子番号      | 内部等価回路 |

|-----------------------|--------|

| XIN (74)<br>XOUT (75) |        |

| AFILT (77)            |        |

| LRREF (4)             |        |

LC786820E

参考回路例

- ・オーディオ（アナログ）入力については、入力レベルを考慮すること。

- ・USB/レギュレータ/発振回路の参考回路の詳細に関しては、それぞれ P21、P29-P31 を参照のこと。

ARM 及び ARM ロゴ, ARM7TDMI-S は、ARM Limited (またはその子会社) の EU またはその他の国における登録商標または商標です。

\* MP3 (MPEG Layer-3 Audio Coding)

MPEG Layer-3 オーディオコーディング技術は、Fraunhofer IIS および Thomson から実施許諾されています。

本製品の供給は、Thomson および/または FraunhoferGesellschaft の関連知的財産権に基づいてライセンスを与えるものではありませんし、本製品を完成済みエンドユーザ製品またはすぐに使用可能な最終製品で使用する権利を暗示するものではありません。

当該使用には、独立したライセンスが必要です。詳細に関しては、<http://mp3licensing.com/> にアクセスしてください。

\* WMA (Windows Media Audio)

Windows Media™ は、米国 Microsoft Corporation の米国、及びその他の国における商標と登録商標です。

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

(参考訳)

ON Semiconductor 及び ON Semiconductor のロゴは ON Semiconductor という商号を使う Semiconductor Components Industries, LLC 若しくはその子会社の米国及び/または他の国における商標です。ON Semiconductor は特許、商標、著作権、トレードシークレット (営業秘密) と他の知的所有権に対する権利を保有します。ON Semiconductor の製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。[www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf) ON Semiconductor は通告なしで、本書記載の製品の変更を行うことがあります。ON Semiconductor は、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害など一切の損害に対して、いかなる責任も負うことはできません。お客様は、ON Semiconductor によって提供されたサポートやアプリケーション情報の如何にかかわらず、すべての法令、規制、安全性の要求あるいは標準の遵守を含む、ON Semiconductor 製品を使用したお客様の製品とアプリケーションについて一切の責任を負うものとします。ON Semiconductor データシートや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあります。実際の性能も時間の経過により変化する可能性があります。「標準的」パラメータを含むすべての動作パラメータは、ご使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致します。ON Semiconductor は、その特許権やその他の権利の下、いかなるライセンスも許諾しません。ON Semiconductor 製品は、生命維持装置や、いかなる FDA (米国食品医薬品局) クラス3の医療機器、FDA が管轄しない地域において同一もしくは類似のものと分類される医療機器、あるいは、人体への移植を対象とした機器における重要部品などへの使用を意図した設計はされておらず、また、これらを使用対象としておりません。お客様が、このような意図されたものではない、許可されていないアプリケーション用に ON Semiconductor 製品を購入または使用した場合、たとえ、ON Semiconductor がその部品の設計または製造に関して過失があったと主張されたとしても、そのような意図せぬ使用、また未許可の使用に関連した死傷等から、直接、又は間接的に生じるすべてのクレーム、費用、損害、経費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、ON Semiconductor とその役員、従業員、子会社、関連会社、代理店に対して、いかなる損害も与えないものとします。ON Semiconductor は雇用機会均等 / 差別撤廃雇用主です。この資料は適用されるあらゆる著作権法の対象となっており、いかなる方法によっても再販することはできません。