# LC88FC2H0A

## 16-bit Microcontroller 512K-byte Flash ROM / 24K-byte RAM

ON Semiconductor®

### 概要

- 12ビットADコンバータ16チャネル

- 赤外線リモコン受信回路

- CRC演算回路

- 内蔵リセット回路

[www.onsemi.jp](http://www.onsemi.jp)

### Performance

- 83.3 ns (12.0 MHz) VDD = 3.0~3.6 V Ta = -40~+85°C

- 100 ns (10.0 MHz) VDD = 2.7~3.6 V Ta = -40~+85°C

### Function Descriptions

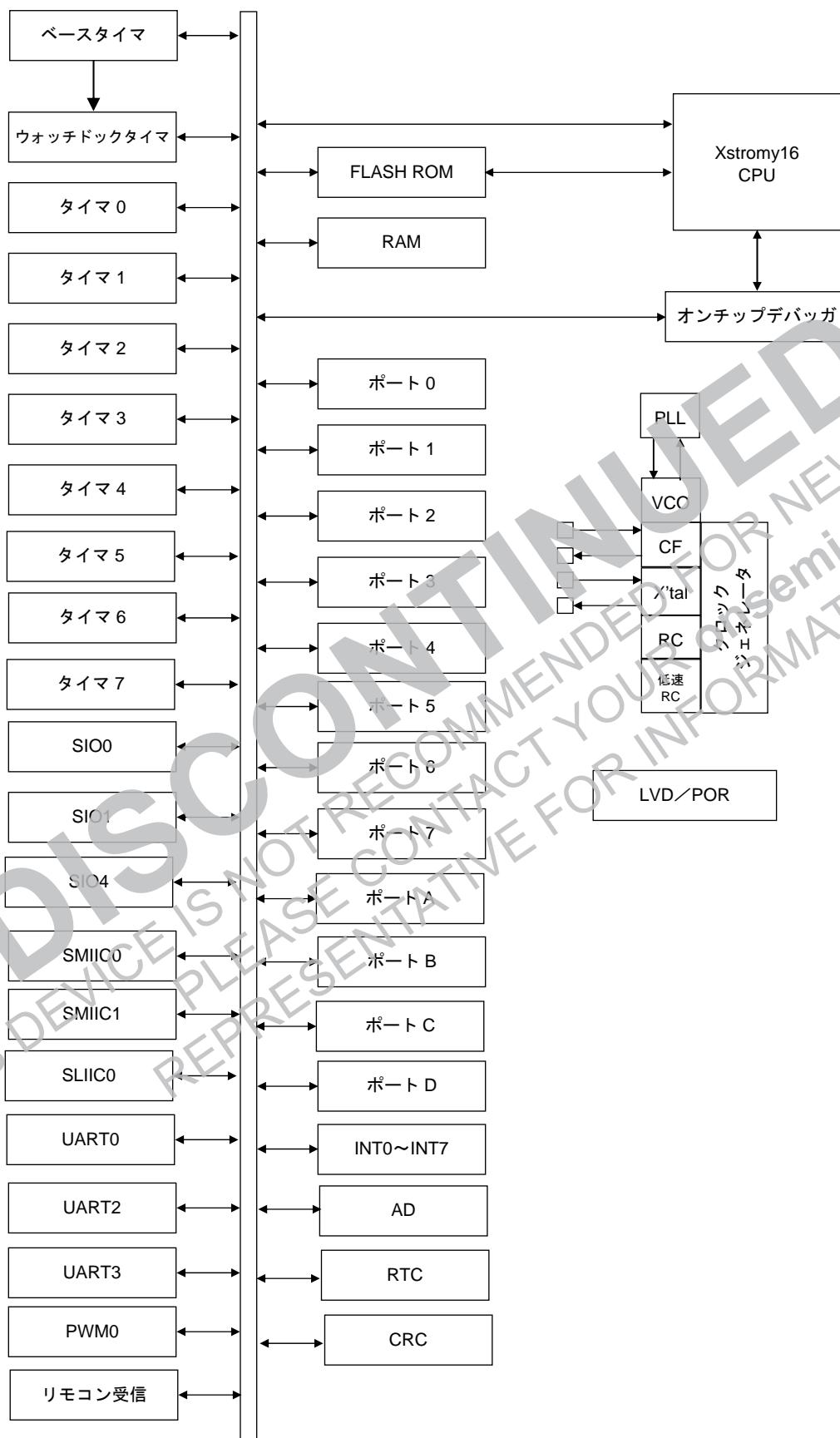

- Xstromy16 CPU

- 4G バイトのアドレス空間

- 汎用レジスタ : 16 ビット×16 本

- ポート

- I/O ポート 86

- 電源端子 8 (VSS1~VSS4, VDD1~VDD4)

- タイマ

- 16 ビットタイマ×8

- 時計用ベースタイマ

- シリアルインターフェース

- 自動転送機能付き同期式 SIO×3

- シングルマスター I<sup>2</sup>C / 同期式 SIC×2

- スレーブ I<sup>2</sup>C / 同期式 SIO

- 非同期式 SIO(UART)×3

- 周期可変 12 ビット PWM×2

- 12 ビット分解能×16 チャネル AD コンバータ

- ウオッチドッグタイマ

- 赤外線リモコン受信回路

- CRC 演算回路

- リアルタイムクロック

- システムクロック分周機能

- CF 発振回路、水晶発振回路、RC 発振回路

- 61 要因 14 ベクタ割り込み機能

- オンチップデバッガ機能

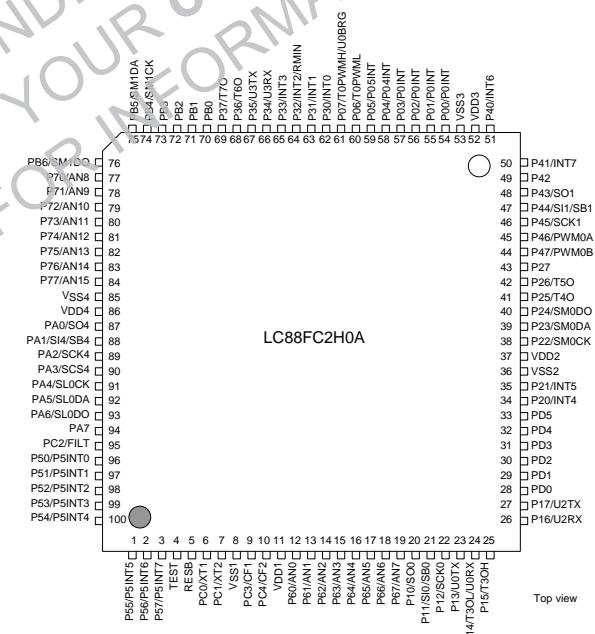

TQFP100 14x14 / TQFP100

ピン配置図 (Top view)

### Application

- ホームオーディオ、カーオーディオ、白物家電

この製品は米国 SST 社 (Silicon Storage Technology, Inc.) のライセンスを受けています。

### ORDERING INFORMATION

See detailed ordering and shipping information on page 48 of this data sheet.

## 機能詳細

### ■Xstromy16 CPU

- ・4Gバイトのアドレス空間

- ・汎用レジスタ：16ビット×16本

### ■フラッシュROM

- ・書き換え電源電圧：2.7～3.6V

- ・消去単位：2K バイト

- ・書き込み単位：2 バイト

- ・524288×8 ビット

### ■RAM

- ・24576×8 ビット

### ■最小命令サイクルタイム(tCYC)

- ・83.3ns(12.0MHz) V<sub>DD</sub>=3.0～3.6V

- ・100ns(10.0MHz) V<sub>DD</sub>=2.7～3.6V

### ■ポート

- ・ノーマル耐圧入出力ポート

1 ビット単位で入出力指定可能 86(P0n, P1n, P2n, P3n, P4n, P5n, P0n, P7n, PAn, PP0～PP6, PC2, PD0～PD5)

4 (PC0, PC1, PC3, PC4)

1 (RESB)

1 (TEST)

8 (VSS1～4, VDD1～4)

- ・発振/ノーマル耐圧入出力ポート

- ・リセット端子

- ・TEST 端子

- ・電源端子

### ■タイマ

- ・タイマ0：PWM/トグル出力可能な16ビットのタイマ

- ①5ビットプリスケーラ付き

- ②8ビットPWM×2、8ビットタイマ+8ビットPWM分割モード選択可能

- ③クロックソースをシステムクロック、OSC0、OSC1、内蔵RCから選択

- ・タイマ1：キャプチャレジスタ付き16ビットタイマ

- ①5ビットプリスケーラ付き

- ②8ビットタイマ×2chの分割可能

- ③クロックソースをシステムクロック、OSC0、OSC1、内蔵RCから選択

- ・タイマ2：キャプチャレジスタ付き16ビットタイマ

- ①4ビットプリスケーラ付き

- ②8ビットタイマ×2chに分割可能

- ③クロックソースをシステムクロック、OSC0、OSC1、外部イベントから選択

- ・タイマ3：PWM/トグル出力可能な16ビットタイマ

- ①8ビットプリスケーラ付き

- ②8ビットタイマ×2ch、8ビットタイマ+8ビットPWMの分割モード選択可能

- ③クロックソースをシステムクロック、OSC0、OSC1、外部イベントから選択

- ・タイマ4：トグル出力可能な16ビットタイマ

- ① クロックソースをシステムクロック、プリスケーラ0から選択

- ・タイマ5：トグル出力可能な16ビットタイマ

- ① クロックソースをシステムクロック、プリスケーラ0から選択

- ・タイマ 6：トグル出力可能な 16 ビットタイマ

- ①クロックソースをシステムクロック、プリスケーラ 0 から選択

- ・タイマ 7：トグル出力可能な 16 ビットタイマ

- ①クロックソースをシステムクロック、プリスケーラ 0 から選択

- \*プリスケーラ 0,1 は 4 ビットで構成されクロックソースをシステムクロック、OSC0, OSC1 から選択。

- ・ベースタイマ

- ①クロックは、OSC0(32.768kHz 水晶発振) , システムクロックの分周出力から選択できる。

- ②7 種類の時間での割り込み発生が可能。

## ■リアルタイムクロック (RTC)

- ① 西暦 2000 年 1 月 1 日から西暦 2799 年 12 月 31 までのカレンダー機能 (うるう年を含む)

- ② 秒, 分, 時, 日, 月, 年, 世紀の独立したカウンタ構成

## ■シリアルインターフェース

- ・SI00 : 8 ビット同期式 SIO

- ① LSB 先頭/MSB 先頭切り替え可能

- ② 8 ビット以下の通信可能 (1 ビット～8 ビットのビット指定可能)

- ③ 8 ビットボーレートジェネレータ内蔵 (転送クロック 4tCYC～512tCYC)

- ④ 連続データ自動転送機能 (9 ビット～32768 ビットのビット単位指定可能)

- ⑤ インターバル機能 (インターバル時間 0～64tSCK 単位で指定可能)

- ⑥ ウエークアップ機能

- ・SI01 : 8 ビット同期式 SIO

- ① LSB 先頭/MSB 先頭切り替え可能

- ② 8 ビット以下の通信可能 (1 ビット～8 ビットのビット指定可能)

- ③ 8 ビットボーレートジェネレータ内蔵 (転送クロック 4tCYC～512tCYC)

- ④ 連続データ自動転送機能 (9 ビット～32768 ビットのビット単位指定可能)

- ⑤ インターバル機能 (インターバル時間 0～64tSCK 単位で指定可能)

- ⑥ ウエークアップ機能

- ・SI04 : 8 ビット同期式 SIO

- ① LSB 先頭/MSB 先頭切り替え可能

- ② 8 ビット以下の通信可能 (1 ビット～8 ビットのビット指定可能)

- ③ 8 ビットボーレートジェネレータ内蔵 (転送クロック 4tCYC～512tCYC)

- ④ 連続データ自動転送機能 (9 ビット～32768 ビットのビット単位指定可能)

- ⑤ インターバル機能 (インターバル時間 0～64tSCK 単位で指定可能)

- ⑥ ウエークアップ機能

- ・SMIICO : シングルマスター I<sup>2</sup>C/8 ビット同期式 SIO

- モード 0 : Single-master のマスタモードによる通信

- モード 1 : 同期式 8 ビットシリアル I/O (データ MSB 先頭)

- ・SMIIC1 : シングルマスター I<sup>2</sup>C/8 ビット同期式 SIO

- モード 0 : Single-master のマスタモードによる通信

- モード 1 : 同期式 8 ビットシリアル I/O (データ MSB 先頭)

- ・SLIICO : スレーブ I<sup>2</sup>C/8 ビット同期式 SIO

- モード 0 : スレーブモードでの I<sup>2</sup>C 通信

- モード 1 : 同期式 8 ビットシリアル I/O (データ MSB 先頭)

注)外部クロックでのみ使用可能

## • UART0

- ①データ長 : 8 ビット (LSB ファースト)

- ②スタートビット : 1 ビット

- ③トップビット : 1 ビット

- ④parityビット : なし/偶数パリティ/奇数パリティ

- ⑤転送レート : 4/8 サイクル

- ⑥ボーレートソースクロック : P07 入力信号を 1 サイクルとして使用(TOPWMH をクロックソースとして使用可能)またはタイマ 4 周期

- ⑦全二重通信

(注) サイクルはボーレートクロックソースの 1 周期

## • UART2

- ①データ長 : 8 ビット (LSB ファースト)

- ②スタートビット : 1 ビット

- ③トップビット : 1/2 ビット

- ④parityビット : なし/偶数パリティ/奇数パリティ

- ⑤転送レート : 8~4096 サイクル

- ⑥ボーレートソースクロック : システムクロック/OSC0/OSC1/P26 入力信号

- ⑦ウェークアップ機能

- ⑧全二重通信

(注) サイクルはボーレートクロックソースの 1 周期

## • UART3

- ①データ長 : 8 ビット (LSB ファースト)

- ②スタートビット : 1 ビット

- ③トップビット : 1/2 ビット

- ④parityビット : なし/偶数パリティ/奇数パリティ

- ⑤転送レート : 8~4096 サイクル

- ⑥ボーレートソースクロック : システムクロック/OSC0/OSC1/P36 入力信号

- ⑦ウェークアップ機能

- ⑧全二重通信

(注) サイクルはボーレートクロックソースの 1 周期

## ■ AD コンバータ

- ①12/8 ビット分解能切り替え

- ②アナログ入力・16 チャネル

- ③コンパレータモード

## ■ PWM

### • PWM0 : 周期可変12ビットPWM×2チャネル (PWMOA, PWMOB)

- ① 2チャネル1組で構成され制御は独立

- ② クロックソースをシステムクロック, OSC1から選択可能

- ③ 8ビットプリスケーラ内臓 : TPWMR0=(プリスケーラ設定値+1) × クロック周期

- ④ 8ビット基本波PWM発生回路+4ビット付加パルス発生回路

- ⑤ 基本波PWMモード

- 基本波周期 16TPWMR0~256TPWMR0

- HIGHパルス幅 0~(基本波周期-TPWMR0)

- ⑥ 基本波+付加パルスモード

- 基本波周期 16TPWMR0~256TPWMR0

- 全体周期 基本波周期×16

- HIGHパルス幅 0~(基本波周期-TPWMR0)

## ■ CRC演算回路

**■ ウオッチドッグタイマ**

- ①ベースタイマ+内臓ウォッチドック専用カウンタにより動作する。

- ②割り込み、リセットの選択可能

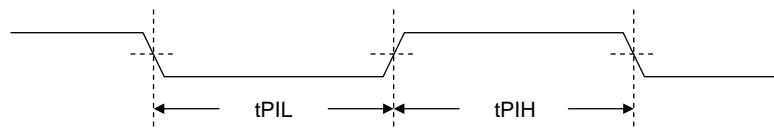

**■ 赤外線リモコン受信回路**

- ①ノイズ除去機能

(ノイズ除去フィルタの時定数：基準クロックに 32.768 kHz の水晶発振を選択した場合、約 120 µs)

- ②PPM (Pulse Position Modulation)、マンチェスター方式などの符号化方式に対応

- ③HOLD X モード解除機能

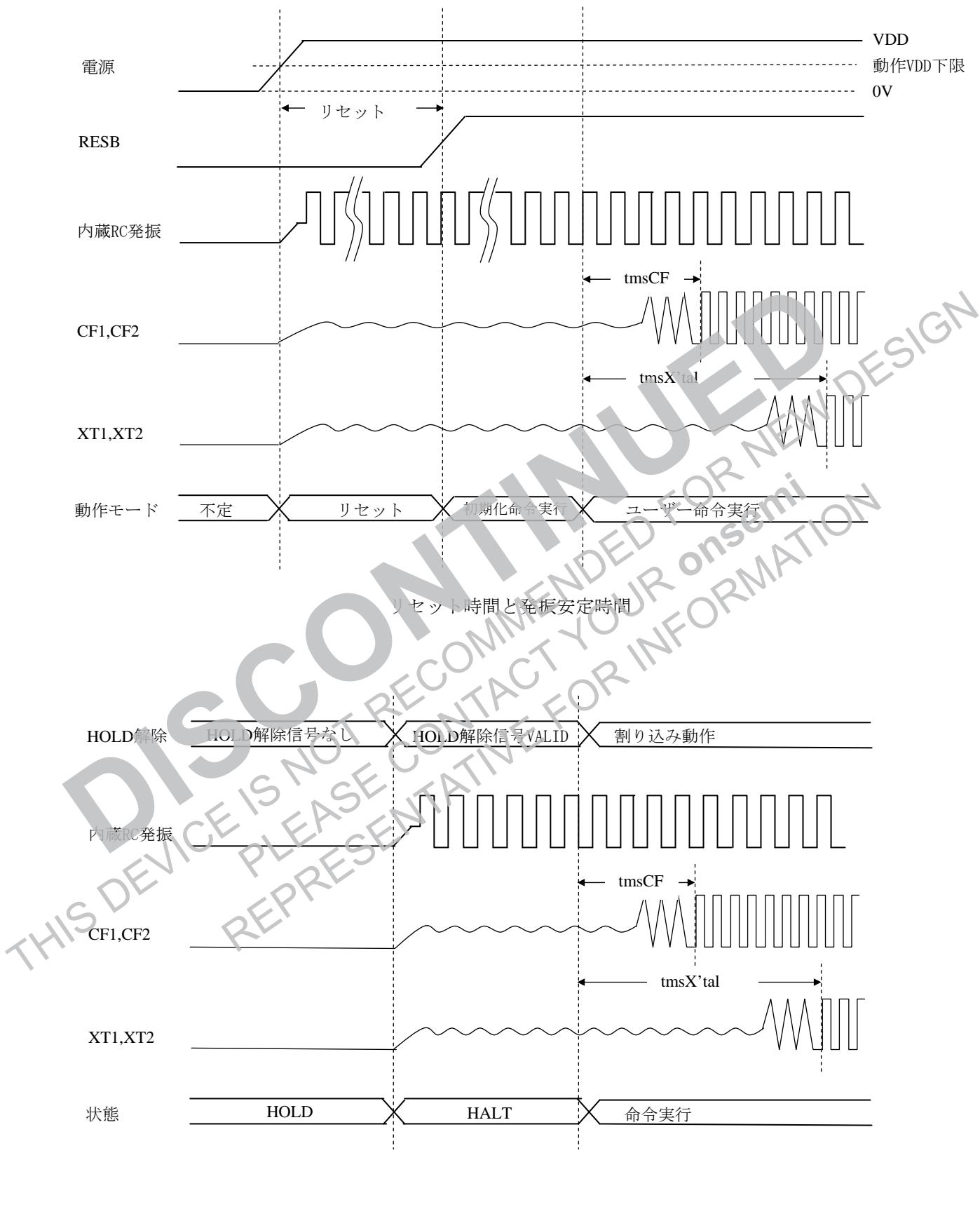

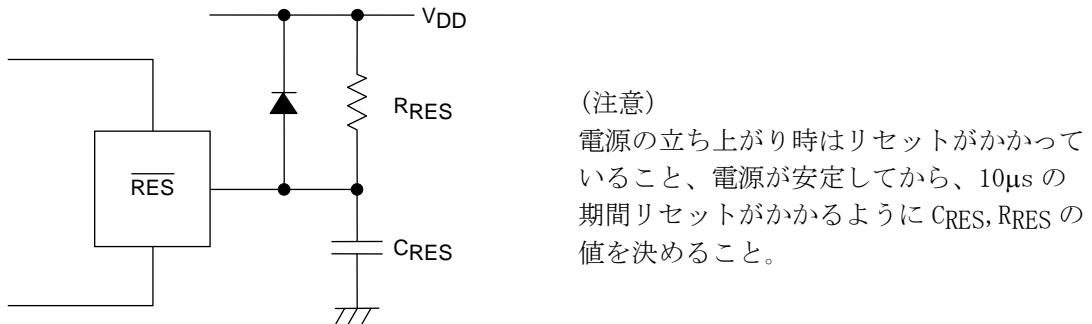

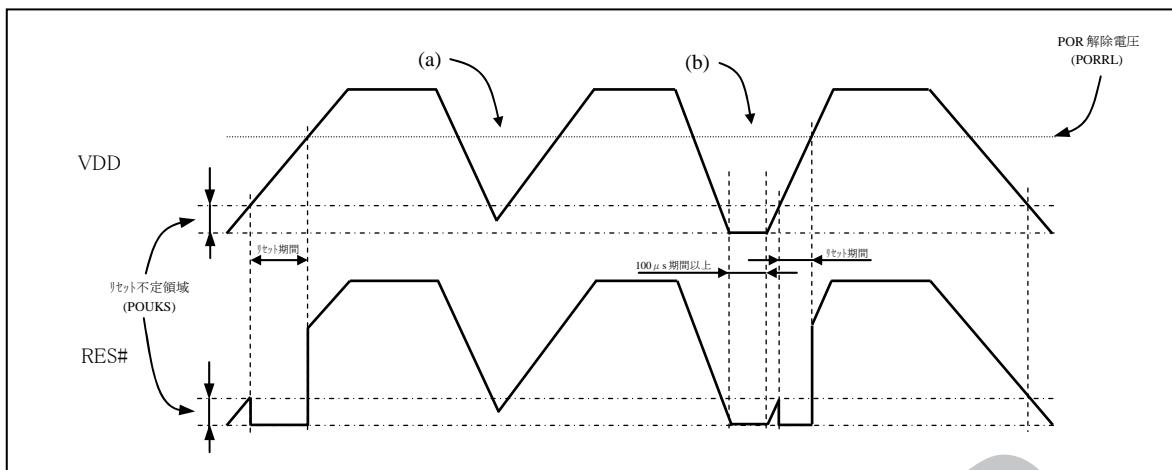

**■ 内蔵リセット回路**

- ・パワーオンリセット (POR) 機能

PORは電源投入時のリセットがかかります。

PORの解除レベルはオプションにて切り替え可能。

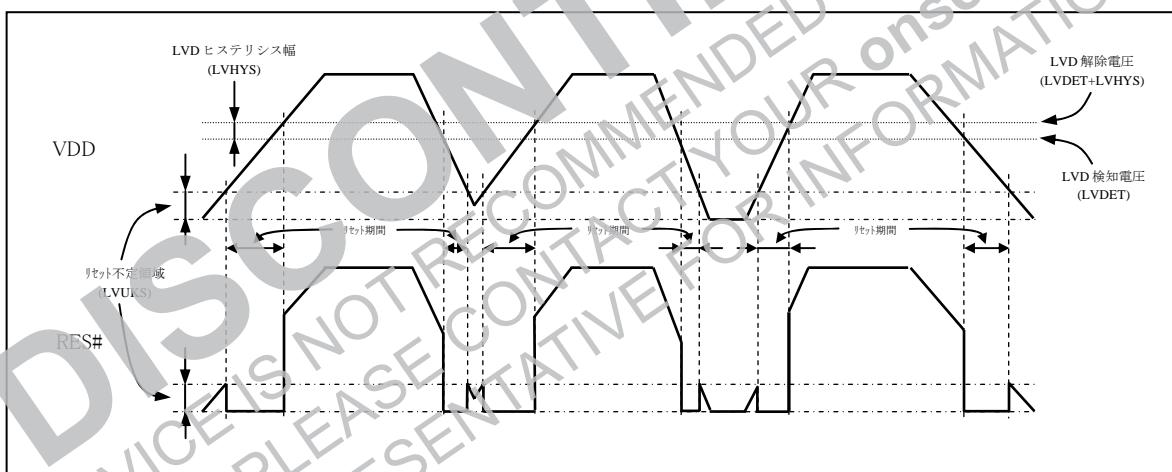

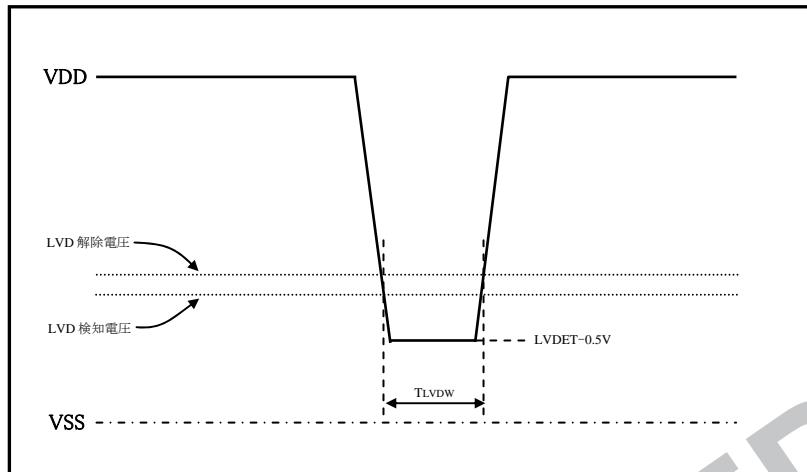

- ・低電圧検知リセット (LVD) 機能

LVDはPORとの併用により、電源投入時と電源低下時ともにリセットがかかります。

LVD機能の使用／不使用をオプションにて切り替え可能。

**■ 割り込み（周辺機能）**

- ・61要因 (33モジュール) 14ベクタ

- ①割り込みは3レベルの多重割り込み制御。割り込み処理中に、同一レベルまたは下位のレベルの割り込み要求が入っても受け付けない。

- ②2つ以上のベクタアドレスへの割り込み要求が同時に発生した場合、レベルの高いものが優先される。また、同一レベルでは飛び先ベクタアドレスの小さい方の割り込みが優先される。

| No. | ベクタ    | 割り込みモジュール                                 |

|-----|--------|-------------------------------------------|

| 1   | 08000H | ウォッチドックタイマ(1)                             |

| 2   | 08004H | ベースタイマ(2)                                 |

| 3   | 08008H | タイマ0(2)                                   |

| 4   | 0800CH | INT0(1)                                   |

| 5   | 08014H | INT1(1)                                   |

| 6   | 08018H | INT2(1) / タイマ1(2) / UART2(4)              |

| 7   | 0801CH | INT3(1) / タイマ2(4) / SMIIC0(1) / SLIIC0(1) |

| 8   | 08020H | INT4(1) / タイマ3(2) / 赤外線リモコン受信(4)          |

| 9   | 08024H | INT5(1) / タイマ4(1) / SI01(2)               |

| 10  | 0802CH | PWM0(1) / SMIIC1(1)                       |

| 11  | 08030H | ADC(1) / タイマ5(1) / SI04(2)                |

| 12  | 08034H | INT6(1) / タイマ6(1) / UART3(4)              |

| 13  | 08038H | INT7(1) / タイマ7(1) / SI00(2)               |

| 14  | 0803CH | ポート0(3) / ポート5(8) / RTC(1) / CRC(1)       |

- ・優先レベルを3レベル指定可能

- ・同一レベルではベクタアドレスの小さいものが優先

- ・( )の数字はモジュール内の要因数

## ■サブルーチンスタック：RAM領域

- PSWを自動退避するサブルーチンコール、割り込みベクタコール：6バイト

- PSWを自動退避しないサブルーチンコール：4バイト

## ■乗除算命令

- 16ビット×16ビット (実行時間：4tCYC)

- 16ビット÷16ビット (実行時間：18～19tCYC)

- 32ビット÷16ビット (実行時間：18～19tCYC)

## ■発振回路

- RC発振回路(内蔵) : システムクロック用

- CF発振回路 (Rf内蔵) : システムクロック用(OSC1)

- 水晶発振回路(Rf内蔵) : システムクロック用(OSC0)

- SLRC発振回路(内蔵) : システムクロック用(例外処理時)

- VCO 発振回路 : タイマ3, 4, 5, 6, 7用

## ■システムクロック分周機能

- 低消費電流動作可能

- システムクロックの1～128分周の設定が可能

## ■スタンバイ機能

- HALTモード：命令実行停止、周辺回路動作継続

①発振の停止は自動的には行わない。

②システムリセットまたは割り込みの発生により解除。

- HOLDモード：命令実行停止、周辺回路動作停止

①OSC1, RC発振, OSC0のいずれも自動的に停止する。

②HOLDモードを解除するには次の6つの方法がある。

- (1) リセット端子に「L」レベルを入力する。

- (2) INT0, INT1, INT2, INT3, INT4, INT5, INT6, INT7の少なくとも1つの端子に指定されたレベルを入力する。

- (3) ポート0で割り込み要因が成立する。

- (4) ポート5で割り込み要因が成立する。

- (5) SI00, SI01, SI04で割り込みが成立する。

- (6) UART2, UART3で割り込みが成立する。

- HOLDXモード：命令実行停止、OSC0で動作する周辺回路以外の動作停止

① OSC1, RC発振は自動的に停止する。

② OSC0は突入時の状態を維持する。

③ HOLDXモードを解除するには次の9つの方法がある。

- (1) リセット端子に「L」レベルを入力する。

- (2) INT0, INT1, INT2, INT3, INT4, INT5, INT6, INT7の少なくとも1つの端子に指定されたレベルを入力する。

- (3) ポート0で割り込み要因が成立する。

- (4) ポート5で割り込み要因が成立する。

- (5) ベースタイマ回路で割り込み要因が成立する。

- (6) SI00, SI01, SI04で割り込みが成立する。

- (7) UART2, UART3で割り込みが成立する。

- (8) 赤外線リモコン受信で割り込みが成立する

- (9) RTCで割り込みが成立する。

**■オンチップデバッガ機能**

- ・ターゲット基板に実装状態でソフトデバッグ可能

- ・ソースラインデバッグ機能、トレース機能、ブレークポイント設定、リアルタイム表示機能

- ・1ワイヤー通信

**■パッケージ**

- ・TQFP100(14×14)：『鉛フリー・ハロゲンフリー仕様品』

**■開発ツール**

- ・オンチップデバッガ : EOCUIF1 or EOCUIF2 + LC88FC2H0A

**■書き込み基板**

|                |          |

|----------------|----------|

| パッケージ          | 書き込み基板   |

| TQFP100(14×14) | W88F52TQ |

**■フラッシュライタ**

| メーカ                                                         | モデル                                     | 対応バージョン                                                        | デバイス       |

|-------------------------------------------------------------|-----------------------------------------|----------------------------------------------------------------|------------|

| フラッシュサポートグループカンパニー<br>(FSG)                                 | AF9709C                                 |                                                                |            |

|                                                             | AF9723/AF9723B(本体)<br>(安藤電気製含む)         |                                                                |            |

|                                                             | AF9833(ユニット)<br>(安藤電気製含む)               |                                                                |            |

| フラッシュサポートグループ<br>カンパニー<br>(FSG)<br>+<br>オン・セミコンダクター<br>(注1) | AF9101/AF9103(本体)<br>(FSG製)             | (注2)                                                           | LC88FC2H0A |

|                                                             | SIB88 Type A<br>(インターフェースドライバ)<br>(弊社製) |                                                                |            |

| オン・セミコンダクター                                                 | SKK Type C<br>(SanyoFWS)                | Application<br>Version 1.08 以降<br>Chip Data Version<br>2.46 以降 | LC88FC2H0A |

|                                                             | FWS-X16DI Type 2<br>(SanyoFWS)          | Application<br>Version 1.08 以降<br>Chip Data Version<br>2.45 以降 | LC88FC2H0A |

(AF シリーズについてのお問い合わせ先)

フラッシュサポートグループカンパニー（東亜エレクトロニクス株式会社）

TEL 053-459-1050

E-mail sales@j-fsg.co.jp

(注1) FSG 製オンボードプログラマ【AF9101/AF9103】と弊社から提供するシリアルインタフェースドライバ【SIB88-TypeA】をペアで使用することにより、PC-less のスタンドアローン・オンボード書き込みが社外製品でも可能。

(注2) 書き込み使用条件により専用の書き込み装置とプログラムが必要になるので、弊社またはFSG へお問い合わせください。

# LC88FC2H0A

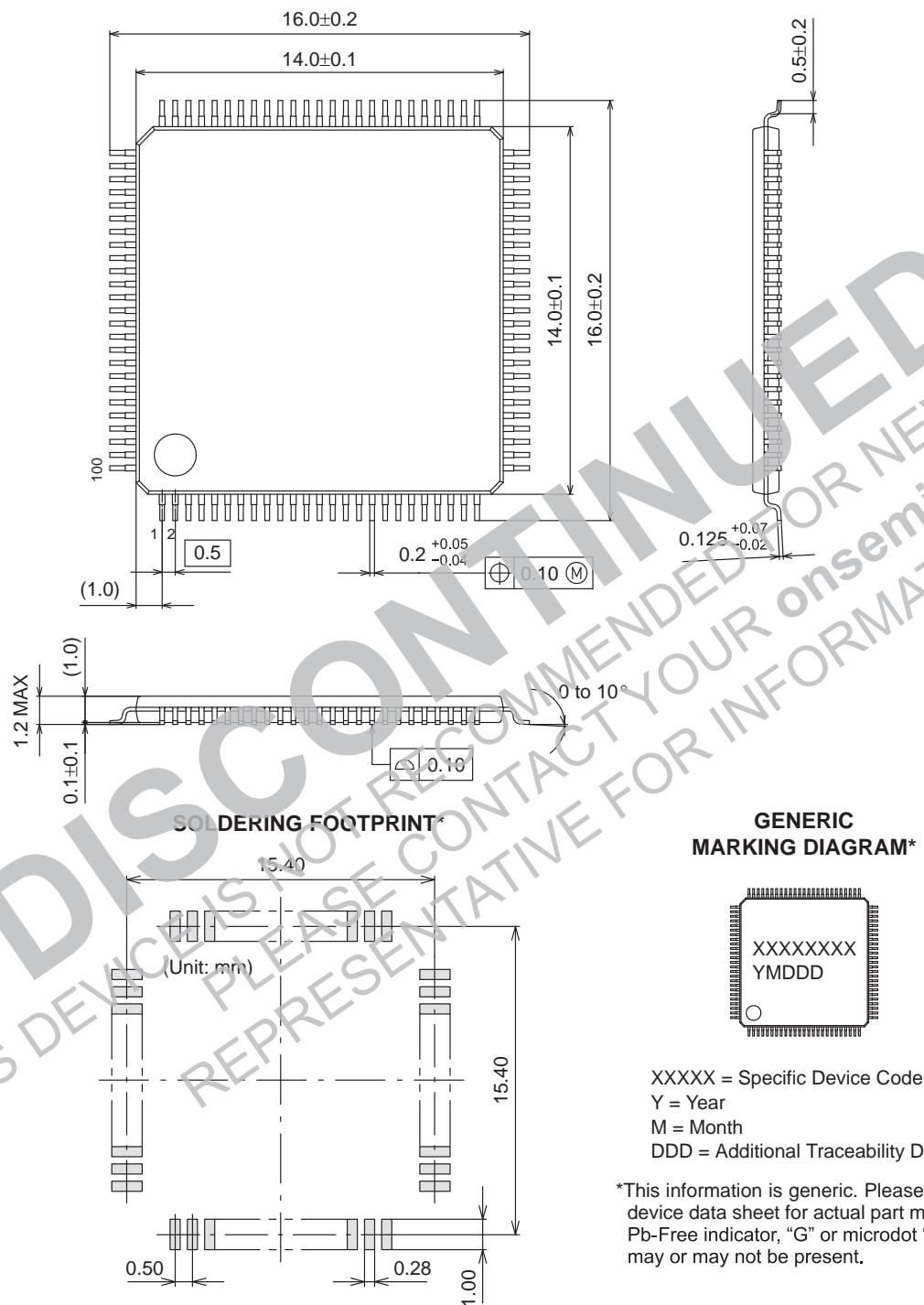

外形図

unit : mm

TQFP100 14x14 / TQFP100

CASE 932AY

ISSUE A

NOTE: The measurements are not to guarantee but for reference only.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

\*This information is generic. Please refer to device data sheet for actual part marking.

Pb-Free indicator, "G" or microdot "■", may or may not be present.

XXXXX = Specific Device Code

Y = Year

M = Month

DDD = Additional Traceability Data

# LC88FC2H0A

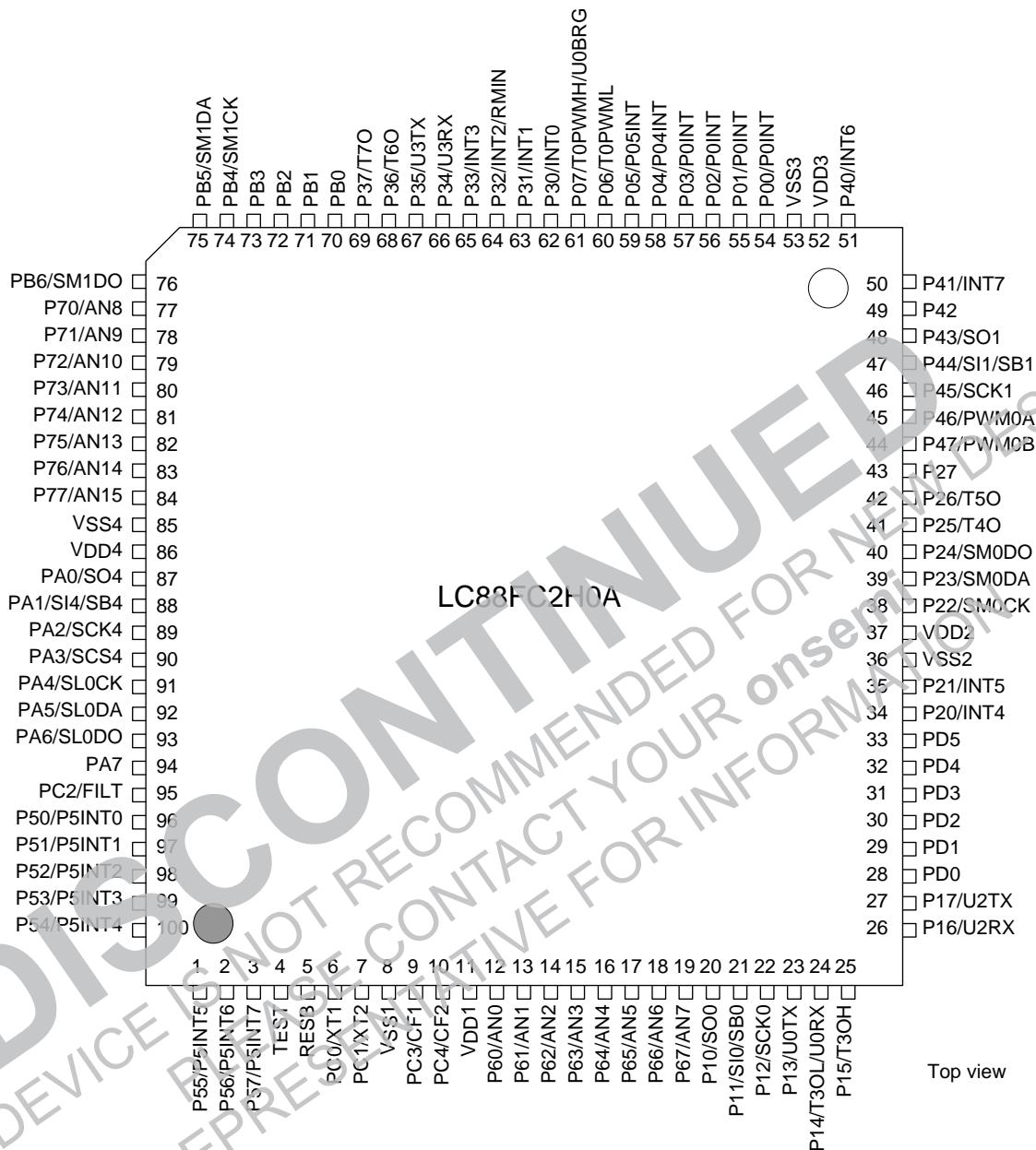

ピン配置図

TQFP100 (14×14) 『鉛フリー・ハロゲンフリー仕様品』

システムブロック図

## LC88FC2H0A

**端子機能表**

| 端子名                                                                          | I/O | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS1</sub> , V <sub>SS2</sub> ,<br>V <sub>SS3</sub> , V <sub>SS4</sub> | -   | 電源の一端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>DD1</sub> , V <sub>DD2</sub> ,<br>V <sub>DD3</sub> , V <sub>DD4</sub> | -   | 電源の+端子                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ポート 0                                                                        | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>HOLD 解除入力(P00～P03, P04, P05)</li> <li>ポート 0 割り込み入力(P00～P03, P04, P05)</li> <li>端子機能<br/>P06 : タイマ 0L 出力<br/>P07 : タイマ 0L 出力/UART0 クロック入力</li> </ul>                                                                                                                                                                                                                                         |

| ポート 1                                                                        | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能<br/>P10 : SI00 データ出力<br/>P11 : SI00 データ入力/バス入出力<br/>P12 : SI00 クロック入出力<br/>P13 : UART0 送信<br/>P14 : タイマ 3L 出力/UART0 受信<br/>P15 : タイマ 3H 出力<br/>P16 : UART2 受信<br/>P17 : UART2 送信</li> </ul>                                                                                                                                                                                            |

| ポート 2                                                                        | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能<br/>P20 : INT4 入力/HOLD 解除入力/タイマ 3 イベント入力/<br/>      タイマ 2L キャプチャ入力/タイマ 2H キャプチャ入力/<br/>P21 : INT5 入力/HOLD 解除入力/タイマ 3 イベント入力/<br/>      タイマ 2L キャプチャ入力/タイマ 2H キャプチャ入力<br/>P22 : SMIIC0 クロック入出力<br/>P23 : SMIIC0 バス入出力/データ入力<br/>P24 : SMIIC0 データ出力 (3 線式 SI0 モード時使用)<br/>P25 : タイマ 4 出力<br/>P26 : タイマ 5 出力<br/>インターラプト受付形式<br/>INT4, INT5 : H レベル, L レベル, H エッジ, L エッジ, 両エッジ</li> </ul> |

| P20～P27                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

次ページへ続く。

## LC88FC2H0A

前ページより続く。

| 端子名              | I/O | 機能説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ポート 3<br>P30～P37 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>P30 : INT0 入力/HOLD 解除/タイマ 2L キャプチャ入力<br/>     P31 : INT1 入力/HOLD 解除/タイマ 2H キャプチャ入力<br/>     P32 : INT2 入力/HOLD 解除/タイマ 2 イベント入力/タイマ 2L キャプチャ入力<br/>         /赤外線リモコン受信入力<br/>     P33 : INT3 入力/HOLD 解除/タイマ 2 イベント入力/タイマ 2H キャプチャ入力<br/>     P34 : UART3 受信<br/>     P35 : UART3 送信<br/>     P36 : タイマ 6 出力<br/>     P37 : タイマ 7 出力<br/>     インタラプト受付形式<br/>     INT0～INT3 : H レベル, L レベル, H エッジ, L エッジ, 両エッジ</p> |

| ポート 4<br>P40～P47 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>P40 : INT6 入力/HOLD 解除入力<br/>     P41 : INT7 入力/HOLD 解除入力<br/>     P43 : SI01 データ出力<br/>     P44 : SI01 データ入力/バス入出力<br/>     P45 : SI01 クロック入出力<br/>     P46 : PWM0A 出力<br/>     P47 : PWM0B 出力<br/>     インタラプト受付形式<br/>     INT6, INT7 : H レベル, L レベル, H エッジ, L エッジ, 両エッジ</p>                                                                                                                                    |

| ポート 5<br>P50～P57 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>ポート 5 割り込み機能</li> <li>HOLD 解除入力</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

| ポート 6<br>P60～P67 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>AN0 (P60)～AN7 (P67) : AD 変換入力ポート</p>                                                                                                                                                                                                                                                                                                                                                                             |

| ポート 7<br>P70～P77 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>AN8 (P70)～AN15 (P77) : AD 変換入力ポート</p>                                                                                                                                                                                                                                                                                                                                                                            |

次ページへ続く。

## LC88FC2H0A

前ページより続く。

| 端子名              | I/O | 機能説明                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ポート A<br>PA0～PA7 | I/O | <ul style="list-style-type: none"> <li>8 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>PA0 : SI04 データ出力<br/>     PA1 : SI04 データ入力/バス入出力<br/>     PA2 : SI04 クロック入出力<br/>     PA3 : SI04 チップセレクト入力<br/>     PA4 : SLIICO クロック入力<br/>     PA5 : SLIICO バス入出力/データ入力<br/>     PA6 : SLIICO データ出力 (3 線式 SI0 モード時使用)</p> |

| ポート B<br>PB0～PB6 | I/O | <ul style="list-style-type: none"> <li>7 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位のプルアップ抵抗 ON/OFF 可能</li> <li>端子機能</li> </ul> <p>PB4 : SMIIC1 クロック入出力<br/>     PB5 : SMIIC1 バス入出力/データ入力<br/>     PB6 : SMIIC1 データ出力 (3 線式 SI0 モード時使用)</p>                                                                                                                    |

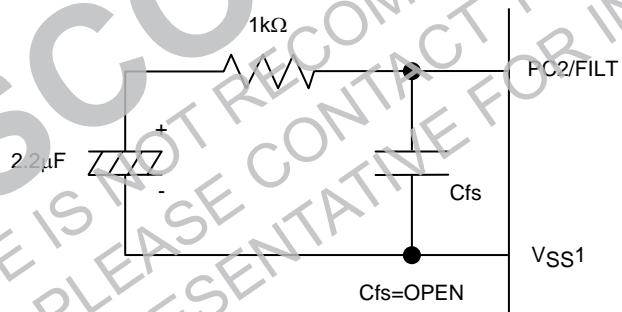

| ポート C<br>PC0～PC4 | I/O | <ul style="list-style-type: none"> <li>5 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位プルアップ抵抗 ON/OFF 可能 (PC2)</li> <li>端子機能</li> </ul> <p>PC0 : 32.768kHz 水晶発振子入力<br/>     PC1 : 32.768kHz 水晶発振子出力<br/>     PC2 : VCO 用 FILTER 接続<br/>     PC3 : セラミック発振子入力<br/>     PC4 : セラミック発振子出力</p>                                                                        |

| ポート D<br>PD0～PD5 | I/O | <ul style="list-style-type: none"> <li>6 ビットの入出力ポート</li> <li>1 ビット単位の入出力指定可能</li> <li>1 ビット単位プルアップ抵抗 ON/OFF 可能</li> </ul>                                                                                                                                                                                                                                               |

| TEST             | I/O | <ul style="list-style-type: none"> <li>TEST 端子</li> <li>オンチップデバッグ通信端子</li> </ul> <p>100kΩ のプルダウン抵抗を外部に接続してください。</p>                                                                                                                                                                                                                                                     |

| RESET            | I/O | リセット端子                                                                                                                                                                                                                                                                                                                                                                  |

## LC88FC2H0A

### ポート出力形態

ポート出力形態とプルアップ抵抗の有無を以下に示す。

なお、入力ポートでのデータの読み込みは、ポートが出力モード時でも可能である。

| ポート名    | 出力切換え<br>単位 | 出力形式                                                | プルアップ抵抗 |

|---------|-------------|-----------------------------------------------------|---------|

| P00～P07 | 1 ビット単位     | CMOS                                                | プログラマブル |

| P10～P17 |             | 兼用機能の出力形式は CMOS 出力 / Nch-オープンドレイン出力の設定をプログラマブルに制御可能 |         |

| P20～P27 |             |                                                     |         |

| P30～P37 |             |                                                     |         |

| P40～P47 |             |                                                     |         |

| PA0～PA7 |             |                                                     |         |

| PB0～PB6 |             |                                                     |         |

| P60～P67 |             | CMOS                                                |         |

| P70～P77 |             |                                                     |         |

| PD0～PD5 |             |                                                     |         |

| PC2     |             |                                                     |         |

| PC0     |             | CMOS<br>(32.768kHz 水晶発振子用入力)                        | なし      |

| PC1     |             | CMOS<br>(32.768kHz 水晶発振子用出力)                        | なし      |

| PC3     |             | CMOS<br>(セラミック発振子用入力)                               | なし      |

| PC4     |             | CMOS<br>(セラミック発振子用出力)                               | なし      |

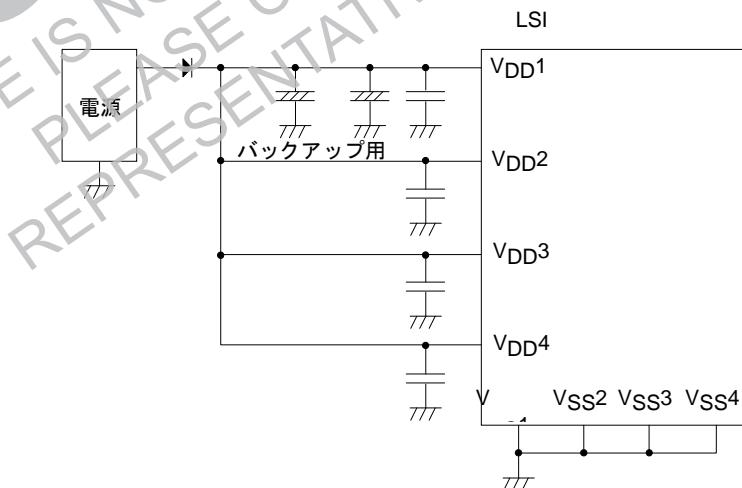

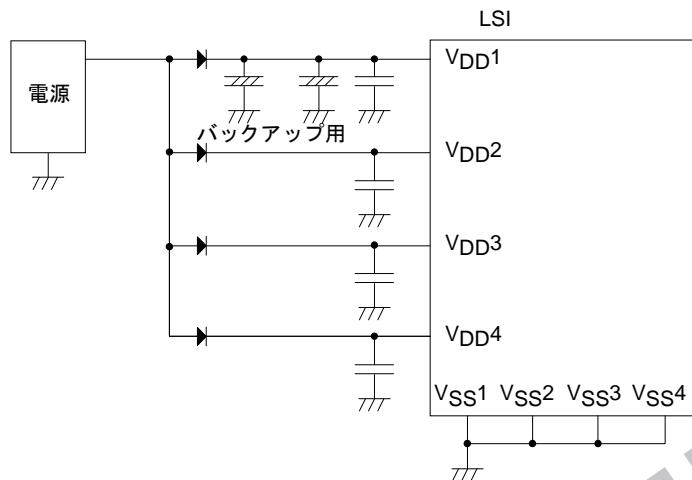

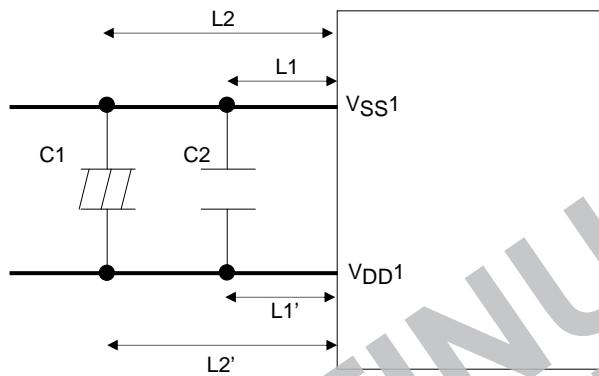

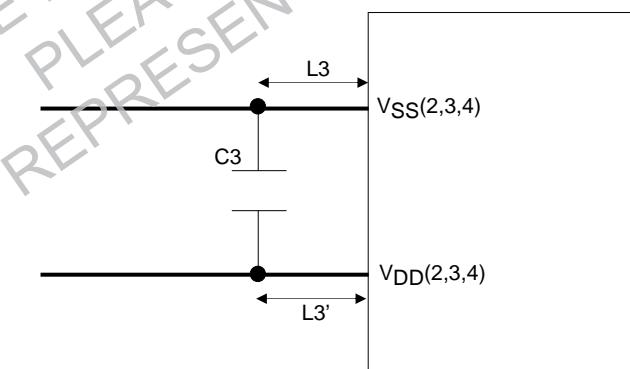

V<sub>DD1</sub> 端子に入るノイズを小さくし、バックアップ時間を作るために次のように接続すること。

V<sub>SS1</sub> 端子と V<sub>SS2</sub> 端子と V<sub>SS3</sub> 端子と V<sub>SS4</sub> 端子は必ず電気的にショートすること。

(例 1) HOLD キードでバックアップ時、ポート出力の「H」レベルはバックアップ用コンデンサより供給される。

## LC88FC2H0A

(例 2) HOLD モードバックアップ時、ポートの「H」レベル出力は保持されず不定となる。

DISCONTINUED

THIS DEVICE IS NOT RECOMMENDED FOR NEW DESIGN

PLEASE CONTACT YOUR onsemi

REPRESENTATIVE FOR INFORMATION

# LC88FC2H0A

絶対最大定格 / Ta = 25°C, V<sub>SS1</sub> = V<sub>SS2</sub> = V<sub>SS3</sub> = V<sub>SS4</sub> = 0 V

| 項目                | 記号                  | 適用端子・備考                                                                   | 条件                                                                     | 規格                  |       |     |                         |

|-------------------|---------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|-------|-----|-------------------------|

|                   |                     |                                                                           |                                                                        | V <sub>DD</sub> [V] | min   | typ | max                     |

| 最大電源電圧            | V <sub>DD</sub> max | V <sub>DD1</sub> , V <sub>DD2</sub> , V <sub>DD3</sub> , V <sub>DD4</sub> | V <sub>DD1</sub> =V <sub>DD2</sub> =V <sub>DD3</sub> =V <sub>DD4</sub> |                     | -0.3  |     | +4.6                    |

| 入力電圧              | V <sub>I</sub> (1)  | RESB                                                                      |                                                                        |                     | -0.3  |     | V <sub>DD</sub><br>+0.3 |

| 入出力電圧             | V <sub>I0</sub> (1) | ポート 0, 1, 2<br>ポート 3, 4, 5<br>ポート 6, 7<br>ポート A, B, C, D                  |                                                                        |                     | -0.3  |     | V <sub>DD</sub><br>+0.3 |

| 高レベル出力電流          | IOPH(1)             | ポート 0, 1, 2, 3<br>P40～P45<br>ポート 7, A, D<br>PB2～PB6                       | CMOS 出力選択<br>適用 1 端子当り                                                 |                     | -7.5  |     |                         |

|                   | IOPH(2)             | P46, P47<br>PB0, PB1                                                      | 適用 1 端子当り                                                              |                     | -12.5 |     |                         |

|                   | IOPH(3)             | ポート 5, 6<br>PC2                                                           | 適用 1 端子当り                                                              |                     | -4.5  |     |                         |

| 平均出力電流<br>(注 1-1) | IOMH(1)             | ポート 0, 1, 2, 3<br>P40～P45<br>ポート 5, 6, 7, A<br>PB2～PB6<br>ポート D           | CMOS 出力選択<br>適用 1 端子当り                                                 |                     | -     |     |                         |

|                   | IOMH(2)             | P46, P47<br>PB0, PB1                                                      | 適用 1 端子当り                                                              |                     | -10   |     |                         |

|                   | IOMH(3)             | ポート 5, 6<br>PC0～PC4                                                       | 適用 1 端子当り                                                              |                     | -3    |     |                         |

| 合計出力電流            | ΣI0AH(1)            | ポート 5,<br>PC0～PC4                                                         | 適用全端子合計                                                                |                     | -10   |     |                         |

|                   | ΣI0AH(2)            | ポート 6                                                                     | 適用全端子合計                                                                |                     | -10   |     |                         |

|                   | ΣI0AH(3)            | ポート 5, 6,<br>PC0～PC4                                                      | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(4)            | ポート 1, D<br>P20, P21                                                      | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(5)            | P22～P27                                                                   | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(6)            | ポート 1, 2, D                                                               | 適用全端子合計                                                                |                     | -40   |     |                         |

|                   | ΣI0AH(7)            | ポート 4                                                                     | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(8)            | ポート 0, 3                                                                  | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(9)            | ポート 0, 3, 4                                                               | 適用全端子合計                                                                |                     | -40   |     |                         |

|                   | ΣI0AH(10)           | ポート B, 7                                                                  | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(11)           | ポート A                                                                     | 適用全端子合計                                                                |                     | -20   |     |                         |

|                   | ΣI0AH(12)           | ポート 7, A, B                                                               | 適用全端子合計                                                                |                     | -40   |     |                         |

注1-1 : 平均出力電流は100ms期間の平均値を示す。

次ページへ続く。

# LC88FC2H0A

前ページより続く。

| 項目                                   | 記号        | 適用端子・備考                                                                              | 条件                                     | 規格                  |     |     |      |

|--------------------------------------|-----------|--------------------------------------------------------------------------------------|----------------------------------------|---------------------|-----|-----|------|

|                                      |           |                                                                                      |                                        | V <sub>DD</sub> [V] | min | typ | max  |

| 低<br>レ<br>ベ<br>ル<br>出<br>力<br>電<br>流 | IOPL(1)   | ポート 0, 1, 3, 4<br>ポート 7, D<br>P20, P21, P24～P27<br>PA0～PA3, PA6, PA7<br>PB0～PB3, PB6 | 適用 1 端子当り                              |                     |     |     | 15   |

|                                      |           |                                                                                      |                                        |                     |     |     | 20   |

|                                      |           |                                                                                      |                                        |                     |     |     | 7.5  |

| 平均出力<br>電流<br>(注 1-1)                | IOML(1)   | ポート 0, 1, 3, 4<br>ポート 7, D<br>P20, P21, P24～P27<br>PA0～PA3, PA6, PA7<br>PB0～PB3, PB6 | 適用 1 端子当り                              |                     |     |     | 12.5 |

|                                      |           |                                                                                      |                                        |                     |     |     | 15   |

|                                      |           |                                                                                      |                                        |                     |     |     | 5    |

| 合計出力<br>電流                           | ΣI0AL(1)  | ポート 5<br>PC0～PC2                                                                     | 適用全端子合計                                |                     |     |     | 10   |

|                                      | ΣI0AL(2)  | ポート 6<br>PC3～PC4                                                                     | 適用全端子合計                                |                     |     |     | 10   |

|                                      | ΣI0AL(3)  | ポート 5, 6<br>PC0～PC4                                                                  | 適用全端子合計                                |                     |     |     | 20   |

|                                      | ΣI0AL(4)  | ポート 1, D<br>P20, 21                                                                  | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(5)  | P22～P27                                                                              | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(6)  | ポート 1, 2, D                                                                          | 適用全端子合計                                |                     |     |     | 70   |

|                                      | ΣI0AL(7)  | ポート 4                                                                                | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(8)  | ポート 0, 3                                                                             | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(9)  | ポート 0, 3, 4                                                                          | 適用全端子合計                                |                     |     |     | 70   |

|                                      | ΣI0AL(10) | ポート 7, B                                                                             | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(11) | ポート A                                                                                | 適用全端子合計                                |                     |     |     | 35   |

|                                      | ΣI0AL(12) | ポート 7, A, B                                                                          | 適用全端子合計                                |                     |     |     | 70   |

| 許容消費電力                               | Pd max    | TQFP100                                                                              | Ta=−40～+85°C<br>熱抵抗評価基板に<br>実装 (注 1-2) |                     |     | 460 | mW   |

| 動作周囲温度                               | Topr      |                                                                                      |                                        |                     |     | +85 | °C   |

| 保存周囲温度                               | Tstg      |                                                                                      |                                        |                     |     | −55 |      |

注1-1：平均出力電流は100ms期間の平均値を示す。

注1-2：熱抵抗評価基板はSEMI準拠（サイズ：76.1×114.3×1.6 mm, ガラエボ）を使用。

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。これらの定格値を超えた場合は、デバイスの機能性を損ない、ダメージが生じ、信頼性に影響を及ぼす危険性があります。

# LC88FC2H0A

許容動作条件 /  $T_a = -40\sim+85^\circ\text{C}$ ,  $V_{SS1} = V_{SS2} = V_{SS3} = V_{SS4} = 0 \text{ V}$

| 項目                       | 記号          | 適用端子・備考                                                               | 条件                        | 規格                  |                      |     |               |

|--------------------------|-------------|-----------------------------------------------------------------------|---------------------------|---------------------|----------------------|-----|---------------|

|                          |             |                                                                       |                           | $V_{DD} [\text{V}]$ | min                  | typ | max           |

| 動作電源電圧<br>(注 2-1)        | $V_{DD(1)}$ | $V_{DD1}=V_{DD2}=V_{DD3}=V_{DD4}$                                     | 0.081μs ≤ tCYC ≤ 66μs     |                     | 3.0                  |     | 3.6           |

|                          |             |                                                                       | 0.098μs ≤ tCYC ≤ 66μs     |                     | 2.7                  |     | 3.6           |

| メモリ保持<br>電源電圧            | $V_{HD}$    | $V_{DD1}=V_{DD2}=V_{DD3}=V_{DD4}$                                     | HOLD モード時<br>RAM, レジスタ保持  |                     | 2.0                  |     | 3.6           |

| 高レベル<br>入力電圧             | $V_{IH(1)}$ | ポート 0, 1, 2, 3, 4<br>ポート 5, A, B                                      |                           | 2.7~3.6             | 0.3 $V_{DD}$<br>+0.7 |     | $V_{DD}$      |

|                          | $V_{IH(2)}$ | ポート 6, 7, D, PC2                                                      |                           | 2.7~3.6             | 0.3 $V_{DD}$<br>+0.7 |     | $V_{DD}$      |

|                          | $V_{IH(3)}$ | RESB<br>PC0, PC1, PC3, PC4                                            |                           | 2.7~3.6             | 0.75 $V_{DD}$        |     | $V_{DD}$      |

|                          | $V_{IH(4)}$ | P22, P23, PA4, PA5,<br>PB4, PB5 の I <sup>2</sup> C 側                  |                           | 2.7~3.6             | 0.7 $V_{DD}$         |     | $V_{DD}$      |

| 低レベル<br>入力電圧             | $V_{IL(1)}$ | ポート 1, 2, 3, 4<br>ポート 5, A, B<br>の PnFSAn=0 の時<br>ポート 0, 6, 7, D, PC2 |                           | 2.7~3.6             | $V_{SS}$             |     | 0.2 $V_{DD}$  |

|                          | $V_{IL(2)}$ | ポート 1, 2, 3, 4<br>ポート 5, A, B<br>の PnFSAn=1 の時                        |                           | 2.7~3.6             | $V_{SS}$             |     | 0.2 $V_{DD}$  |

|                          | $V_{IL(3)}$ | RESB<br>PC0, PC1, PC3, PC4                                            |                           | 2.7~3.6             | $V_{SS}$             |     | 0.25 $V_{DD}$ |

|                          | $V_{IL(4)}$ | P22, P23, PA4, PA5,<br>PB4, PB5 の I <sup>2</sup> C 側                  |                           | 2.7~3.6             | $V_{SS}$             |     | 0.3 $V_{DD}$  |

| 命令サイクル<br>タイム<br>(注 2-2) | tCYC        |                                                                       |                           | 3.0~3.6             | 0.081                |     | 66            |

|                          |             |                                                                       |                           | 2.7~3.6             | 0.098                |     | 66            |

| 外部システム<br>クロック周波数        | FFXCF(1)    | PC3(CF1)                                                              | CF2 端子オープン                | 3.0~3.6             | 0.1                  |     | 12            |

|                          |             |                                                                       | システムクロック分周<br>1/1         | 2.7~3.6             | 0.1                  |     | 10            |

|                          |             |                                                                       | 外部システムクロック<br>の DUTY50±5% | 3.0~3.6             | 0.2                  |     | 24            |

|                          |             |                                                                       | CF2 端子オープン                | 2.7~3.6             | 0.2                  |     | 20            |

|                          |             |                                                                       | システムクロック分周<br>1/2         |                     |                      |     |               |

注 2-1 : tCYC と発振周波数の関係式は、1/1 分周時 : 1/FmCF、1/2 分周時 : 2/FmCF。

次ページへ続く。

# LC88FC2H0A

前ページより続く。

| 項目                 | 記号       | 適用端子・備考               | 条件                              | 規格                  |     |        |     |

|--------------------|----------|-----------------------|---------------------------------|---------------------|-----|--------|-----|

|                    |          |                       |                                 | V <sub>DD</sub> [V] | min | typ    | max |

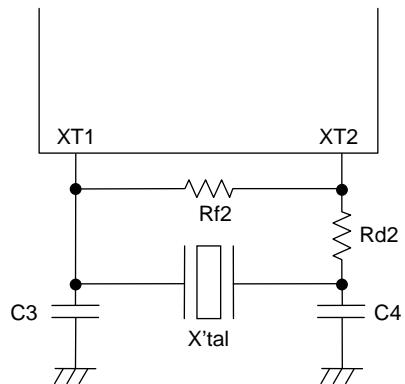

| 発振周波数範囲<br>(注 2-3) | FmCF(1)  | PC3(CF1),<br>PC4(CF2) | 12MHz セラミック発振時<br>図 1 参照        | 3.0~3.6             |     | 12     |     |

|                    | FmCF(2)  | PC3(CF1),<br>PC4(CF2) | 10MHz セラミック発振時<br>図 1 参照        | 2.7~3.6             |     | 10     |     |

|                    | FmRC     |                       | 内蔵 RC 発振                        | 2.7~3.6             | 0.5 | 1.0    | 2.0 |

|                    | FmSLRC   |                       | 内蔵低速 RC 発振                      | 2.7~3.6             | 18  | 30     | 45  |

|                    | FsX'tal  | PC0(XT1),<br>PC1(XT2) | 32.768kHz 水晶発振時<br>図 2 参照       | 2.7~3.6             |     | 32.768 |     |

|                    | FmVCO(1) |                       | VCO 発振<br>FRQSEL=0 の時<br>図 9 参照 | 2.7~3.6             | 12  |        | 28  |

|                    | FmVCO(2) |                       | VCO 発振<br>FRQSEL=1 の時<br>図 9 参照 | 2.7~3.6             | 38  |        | 70  |

|                    | FmVCO(3) |                       | VCO 発振                          | 2.7~3.6             |     | 注 2-2  |     |

注2-2：発振定数は表1,2参照のこと。

注2-3：VCO発振周波数=CF発振周波数×SELREF設定値

推奨動作範囲を超えるストレスでは推奨動作機能を得られません。推奨動作範囲を超えるストレスの印加は、デバイスの信頼性に影響を与える危険性があります。

# LC88FC2H0A

電気的特性 /  $T_a = -40\sim+85^\circ\text{C}$ ,  $V_{SS1} = V_{SS2} = V_{SS3} = V_{SS4} = 0 \text{ V}$

| 項目       | 記号          | 適用端子・備考                                                           | 条件                                                                     | $V_{DD} [\text{V}]$ | 規格           |             |     |                  |

|----------|-------------|-------------------------------------------------------------------|------------------------------------------------------------------------|---------------------|--------------|-------------|-----|------------------|

|          |             |                                                                   |                                                                        |                     | min          | typ         | max | unit             |

| 高レベル入力電流 | $I_{IH}(1)$ | ポート 0, 1, 2<br>ポート 3, 4, 5<br>ポート 6, 7<br>ポート A, B, C, D<br>RESB  | 出力ディイセーブル<br>プルアップ抵抗オフ<br>$V_{IN}=V_{DD}$<br>(出力 Tr. のオフリーク電流を含む)      | 2.7~3.6             |              |             | 1   |                  |

| 低レベル入力電流 | $I_{IL}(1)$ | ポート 0, 1, 2<br>ポート 3, 4, 5<br>ポート 6, 7<br>ポート A, B, C, D<br>RESB  | 出力ディイセーブル<br>プルアップ抵抗オフ<br>$V_{IN}=V_{SS}$<br>(出力 Tr. のオフリーク電流を含む)      | 2.7~3.6             | -1           |             |     |                  |

| 高レベル出力電圧 | $V_{OH}(1)$ | ポート 0, 1, 2, 3<br>ポート 5, 6<br>ポート A, D, PC2                       | $I_{OH}=-0.4\text{mA}$                                                 | 3.0~3.6             | $V_{DD}-0.4$ |             |     |                  |

|          | $V_{OH}(2)$ | P40~P45<br>PB2~PB6                                                | $I_{OH}=-0.2\text{mA}$                                                 | 2.7~3.6             | $V_{DD}-0.4$ |             |     |                  |

|          | $V_{OH}(3)$ | P46, P47<br>PB0, PB1                                              | $I_{OH}=-1.6\text{mA}$                                                 | 3.0~3.6             | $V_{DD}-0.4$ |             |     |                  |

|          | $V_{OH}(4)$ |                                                                   | $I_{OH}=-1.0\text{mA}$                                                 | 2.7~3.6             | $V_{DD}-0.4$ |             |     |                  |

|          | $V_{OH}(5)$ | PC0~PC1,<br>PC3~PC4                                               | $I_{OH}=-1.0\text{mA}$                                                 | 3.0~3.6             | $V_{DD}-0.4$ |             |     |                  |

|          | $V_{OH}(6)$ |                                                                   | $I_{OH}=-0.4\text{mA}$                                                 | 2.7~3.6             | $V_{DD}-0.4$ |             |     |                  |

| 低レベル出力電圧 | $V_{OL}(1)$ | ポート 0, 1, 3, 4<br>ポート 5, 6, 7, D                                  | $I_{OL}=1.6\text{mA}$                                                  | 3.0~3.6             |              |             | 0.4 |                  |

|          | $V_{OL}(2)$ | PC2<br>P20~P21,<br>P24~P27<br>PA0~PA3,<br>PA6~PA7<br>PB0~PB3, PB6 | $I_{OL}=1.0\text{mA}$                                                  | 2.7~3.6             |              |             | 0.4 |                  |

|          | $V_{OL}(3)$ | P22, P23<br>PA4, PA5                                              | $I_{OL}=3.0\text{mA}$                                                  | 3.0~3.6             |              |             | 0.4 |                  |

|          | $V_{OL}(4)$ | PA4, PA5<br>PB4, PB5                                              | $I_{OL}=1.3\text{mA}$                                                  | 2.7~3.6             |              |             | 0.4 |                  |

|          | $V_{OL}(5)$ | PC0~PC1,<br>PC3~PC4                                               | $I_{OL}=1.0\text{mA}$                                                  | 3.0~3.6             |              |             | 0.4 |                  |

|          | $V_{OL}(6)$ |                                                                   | $I_{OL}=0.4\text{mA}$                                                  | 2.7~3.6             |              |             | 0.4 |                  |

| プルアップ抵抗  | $R_{pu}(1)$ | ポート 0, 1, 2, 3<br>ポート 4, 5, 6, 7<br>ポート A, B, D, PC2              | $V_{OH}=0.9V_{DD}$                                                     | 3.0~3.6             | 15           | 35          | 80  |                  |

|          | $R_{pu}(2)$ |                                                                   |                                                                        | 2.7~3.6             | 15           | 35          | 100 | $\text{k}\Omega$ |

| ヒステリシス電圧 | VHYS        | RESB<br>ポート 1, 2, 3, 4<br>ポート A, B<br>の $PnFSAn=1$ の時             |                                                                        | 2.7~3.6             |              | $0.1V_{DD}$ |     | V                |

| 端子容量     | CP          | 全端子                                                               | 被測定端子以外<br>$V_{IN}=V_{SS}$<br>$f=1\text{MHz}$<br>$Ta=25^\circ\text{C}$ | 2.7~3.6             |              | 10          |     | pF               |

製品パラメータは、特別な記述が無い限り、記載されたテスト条件に対する電気的特性で示しています。異なる条件下で製品動作を行った時には、電気的特性で示している特性を得られない場合があります。

# LC88FC2H0A

シリアル入出力特性 /  $T_a = -40\sim+85^\circ C$ ,  $V_{SS1} = V_{SS2} = V_{SS3} = V_{SS4} = 0 V$

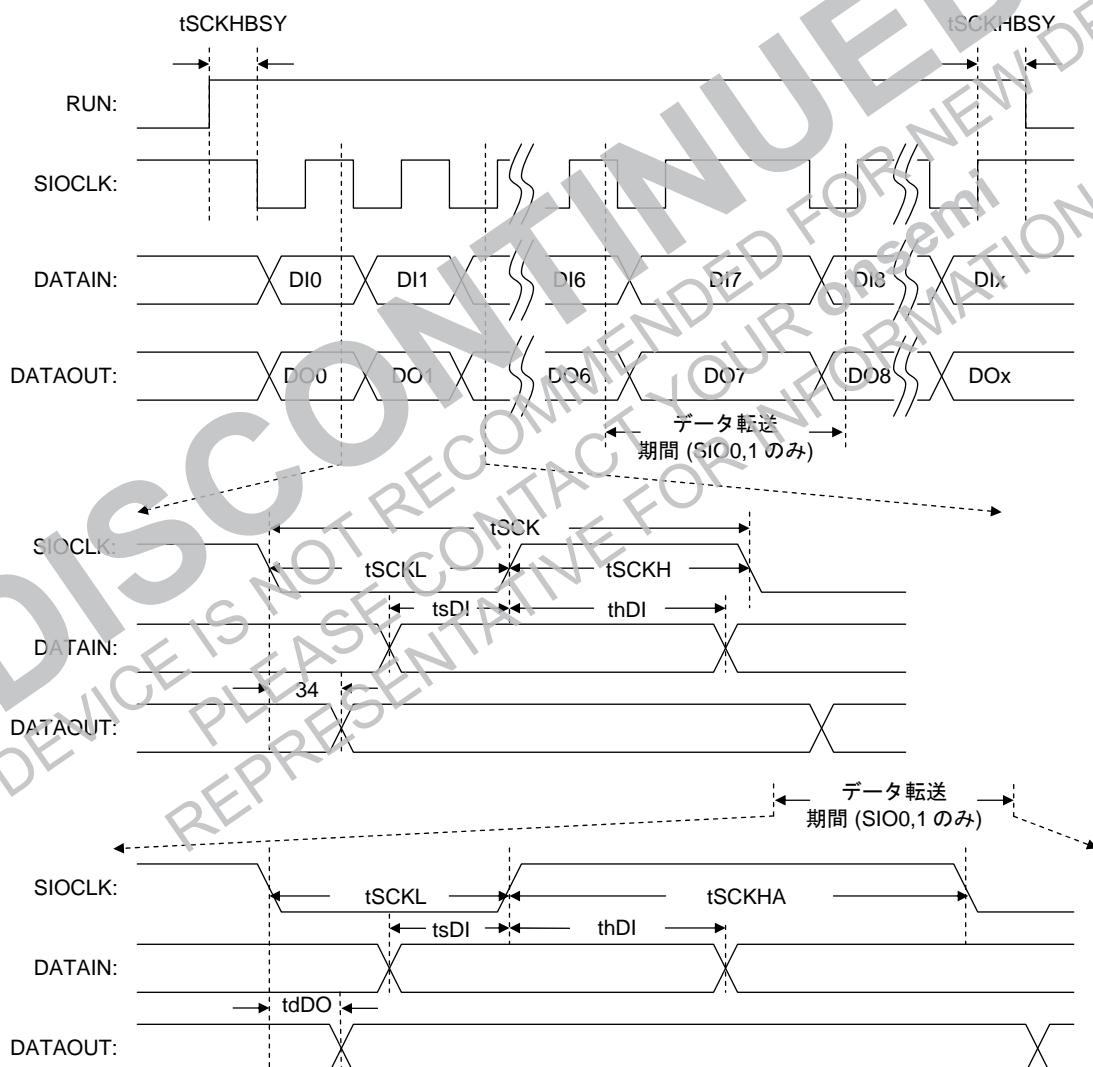

1-1. SI00 シリアル入出力特性（ウェークアップ機能不使用時）(注 4-1-1)

| 項目       |        | 記号          | 適用端子<br>・備考  | 条件                                                                                                                                       | $V_{DD}$ [V]                         | 規格   |     |     |                |

|----------|--------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|-----|-----|----------------|

|          |        |             |              |                                                                                                                                          |                                      | min  | typ | max | unit           |

| シリアルクロック | 入力クロック | 周期          | tSCK(1)      | SCK0(P12)<br>•図 6 参照<br>•自動通信モード<br>•図 6 参照<br>•自動通信モード<br>•図 6 参照<br>•自動通信モード以外<br>•図 6 参照                                              | 2.7~3.6                              | 4    |     |     | tCYC           |

|          |        | 低レベルパルス幅    | tSCKL(1)     |                                                                                                                                          |                                      | 2    |     |     |                |

|          |        | 高レベルパルス幅    | tSCKH(1)     |                                                                                                                                          |                                      | 2    |     |     |                |

|          |        |             | tSCKHA(1)    |                                                                                                                                          |                                      | 6    |     |     |                |

|          |        |             | tSCKHBSY(1a) |                                                                                                                                          |                                      | 23   |     |     |                |

|          |        |             | tSCKHBSY(1b) |                                                                                                                                          |                                      | 4    |     |     |                |

|          |        | 周期          | tSCK(2)      |                                                                                                                                          |                                      | 4    |     |     |                |

| シリアル入力   | 出力クロック | 低レベルパルス幅    | tSCKL(2)     | SCK0(P12)<br>•CMOS 出力選択時<br>•図 6 参照<br>•自動通信モード<br>•CMOS 出力選択時<br>•図 6 参照<br>•自動通信モード<br>•CMOS 出力選択時<br>•図 6 参照<br>•自動通信モード以外<br>•図 6 参照 | 2.7~3.6                              | 1/2  |     |     | tCK            |

|          |        | 高レベルパルス幅    | tSCKH(2)     |                                                                                                                                          |                                      | 1/2  |     |     |                |

|          |        |             | tSCKHA(2)    |                                                                                                                                          |                                      | 6    |     |     |                |

|          |        |             | tSCKHBSY(2a) |                                                                                                                                          |                                      | 4    |     | 23  |                |

|          |        |             | tSCKHBSY(2b) |                                                                                                                                          |                                      | 4    |     |     |                |

|          |        | データセットアップ時間 | tsDI(1)      | SI0(P11),<br>SB0(P11)                                                                                                                    | SI0CLK の立ち上がり<br>に対して規定する<br>•図 6 参照 | 0.03 |     |     | $\mu s$        |

|          |        | データホールド時間   | thDI(1)      |                                                                                                                                          |                                      | 0.03 |     |     |                |

| シリアル出力   | 入力クロック | 出力遅延時間      | tdD0(1)      | S00(P10),<br>SB0(P11)                                                                                                                    | •(注 4-1-2)<br>•(注 4-1-2)             |      |     |     | 1tCYC<br>+0.05 |

|          |        |             | tdD0(2)      |                                                                                                                                          |                                      |      |     |     |                |

注 4-1-1 : 本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-1-2 : SI0CLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

# LC88FC2H0A

## 1-2. SI00 シリアル入出力特性（ウェークリップ機能使用時）(注 4-2-1)

| 項目       |        | 記号              | 適用端子<br>・備考     | 条件                                     | 規格                                                   |         |     |     |                      |      |

|----------|--------|-----------------|-----------------|----------------------------------------|------------------------------------------------------|---------|-----|-----|----------------------|------|

|          |        |                 |                 |                                        | V <sub>DD</sub> [V]                                  | min     | typ | max | unit                 |      |

| シリアルクロック | 入力クロック | 周期              | tSCK(3)         | SCK0(P12)<br><br>SI0(P11),<br>SB0(P11) | ・図 6 参照<br><br>・SIOCLK の立ち上がり<br>に対して規定する<br>・図 6 参照 | 2.7～3.6 | 2   |     |                      | tCYC |

|          |        | 低レベル<br>パルス幅    | tSCKL(3)        |                                        |                                                      | 1       |     |     |                      |      |

|          |        | 高レベル<br>パルス幅    | tSCKH(3)        |                                        |                                                      | 1       |     |     |                      |      |

|          |        |                 | tSCKHBSY<br>(3) |                                        |                                                      | 2       |     |     |                      |      |

| シリアル入力   |        | データセット<br>アップ時間 | tsDI(2)         |                                        | 2.7～3.6                                              | 0.03    |     |     |                      |      |

|          |        | データホールド<br>時間   | thDI(2)         |                                        |                                                      | 0.03    |     |     |                      |      |

| シリアル出力   | 入力クロック | 出力遅延<br>時間      | tdD0(3)         | S00(P10),<br>SB0(P11)                  | ・(注 4-2-2)                                           | 2.7～3.6 |     |     | μs<br>1tCYC<br>+0.05 |      |

注 4-2-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-2-2：SIOCLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

# LC88FC2H0A

## 2-1. SI01 シリアル入出力特性（ウェークリップ機能不使用時）(注 4-3-1)

| 項目       |                 | 記号           | 適用端子<br>・備考           | 条件                                      | 規格                  |         |     |     |                |

|----------|-----------------|--------------|-----------------------|-----------------------------------------|---------------------|---------|-----|-----|----------------|

|          |                 |              |                       |                                         | V <sub>DD</sub> [V] | min     | typ | max | unit           |

| シリアルクロック | 入力クロック          | 周期           | tSCK(4)               | SCK1(P45)<br><br>・図 6 参照                | 2.7～3.6             | 4       |     |     | tCYC           |

|          |                 | 低レベル<br>パルス幅 | tSCKL(4)              |                                         |                     | 2       |     |     |                |

|          |                 | 高レベル<br>パルス幅 | tSCKH(4)              |                                         |                     | 2       |     |     |                |

|          |                 |              | tSCKHA(4)             |                                         |                     | 6       |     |     |                |

|          |                 |              | tSCKHBSY<br>(4a)      |                                         |                     | 23      |     |     |                |

|          | 出力クロック          | 周期           | tSCK(5)               | SCK1(P45)<br><br>・CMOS 出力選択時<br>・図 6 参照 | 2.7～3.6             | 4       |     |     | tSCK           |

|          |                 | 低レベル<br>パルス幅 | tSCKL(5)              |                                         |                     | 1/2     |     |     |                |

|          |                 | 高レベル<br>パルス幅 | tSCKH(5)              |                                         |                     | 1/2     |     |     |                |

|          |                 |              | tSCKHA(5)             |                                         |                     | 6       |     |     |                |

|          |                 |              | tSCKHBSY<br>(5a)      |                                         |                     | 4       |     | 23  |                |

| シリアルデータ  | データセット<br>アップ時間 | tsDI(3)      | S11(P44),<br>SR1(P44) | ・SI0CLK の立ち上がり<br>に対して規定する<br>図 6 参照    | 2.7～3.6             | 0.03    |     |     | μs             |

|          |                 | tnDI(3)      |                       |                                         |                     | 0.03    |     |     |                |

|          | データホールド<br>時間   |              |                       |                                         |                     |         |     |     |                |

| シリアル出力   | 入力クロック          | 出力遅延<br>時間   | tdD0(4)               | S01(P43),<br>SB1(P44)                   | ・(注 4-3-2)          | 2.7～3.6 |     |     | 1tCYC<br>+0.05 |

|          |                 |              | tdD0(5)               |                                         |                     |         |     |     | 1tCYC<br>+0.05 |

注 4-3-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-3-2：SI0CLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

## LC88FC2H0A

### 2-2. SI01 シリアル入出力特性（ウェークリップ機能使用時）(注 4-4-1)

| 項目       |             |          | 記号          | 適用端子<br>・備考           | 条件                                    | 規格      |      |     |      |

|----------|-------------|----------|-------------|-----------------------|---------------------------------------|---------|------|-----|------|

|          |             |          |             |                       |                                       | min     | typ  | max | unit |

| シリアルクロック | 入力クロック      | 周期       | tSCK(6)     | SCK1(P45)             | ・図 6 参照                               | 2.7～3.6 | 2    |     |      |

|          |             | 低レベルパルス幅 | tSCKL(6)    |                       |                                       |         | 1    |     |      |

|          |             | 高レベルパルス幅 | tSCKH(6)    |                       |                                       |         | 1    |     |      |

|          |             |          | tSCKHBSY(6) |                       |                                       |         | 2    |     |      |

| シリアル入力   | データセットアップ時間 |          | tsDI(4)     | SI1(P44),<br>SB1(P44) | ・SIOCLK の立ち上がり<br>に対して規定する<br>・図 6 参照 | 2.7～3.6 | 0.03 |     |      |

|          | データホールド時間   |          | thDI(4)     |                       |                                       |         | 0.03 |     |      |

| シリアル出力   | 入力クロック      | 出力遅延時間   | tdD0(6)     | S01(P43),<br>SB1(P44) | ・(注 4-4-2)                            | 2.7～3.6 |      |     | μs   |

注 4-4-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-4-2：SIOCLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

# LC88FC2H0A

## 3-1. SI04 シリアル入出力特性（ウェークリップ機能不使用時）(注 4-5-1)

| 項目       |             | 記号       | 適用端子<br>・備考           | 条件                                      | 規格                  |      |     |     |                |

|----------|-------------|----------|-----------------------|-----------------------------------------|---------------------|------|-----|-----|----------------|

|          |             |          |                       |                                         | V <sub>DD</sub> [V] | min  | typ | max | unit           |

| シリアルクロック | 入力クロック      | 周期       | tSCK(7)               | SCK4(PA2)<br><br>・図 6 参照                | 2.7～3.6             | 4    |     |     | tCYC           |

|          |             | 低レベルパルス幅 | tSCKL(7)              |                                         |                     | 2    |     |     |                |

|          |             | 高レベルパルス幅 | tSCKH(7)              |                                         |                     | 2    |     |     |                |

|          |             |          | tSCKHA(7)             |                                         |                     | 6    |     |     |                |

|          |             |          | tSCKHBSY(7a)          |                                         |                     | 23   |     |     |                |

|          | 出力クロック      | 周期       | tSCK(8)               | SCK4(PA2)<br><br>・CMOS 出力選択時<br>・図 6 参照 | 2.7～3.6             | 4    |     |     | tSCK           |

|          |             | 低レベルパルス幅 | tSCKL(8)              |                                         |                     | 1/2  |     |     |                |

|          |             | 高レベルパルス幅 | tSCKH(8)              |                                         |                     | 1/2  |     |     |                |

|          |             |          | tSCKHA(8)             |                                         |                     | 6    |     |     |                |

|          |             |          | tSCKHBSY(8a)          |                                         |                     | 4    |     | 23  |                |

| シリアルデータ  | データセットアップ時間 | tsDI(5)  | SI4(PA1),<br>SR4(PA1) | SI0CLK の立ち上がり<br>に対して規定する<br>図 6 参照     | 2.7～3.6             | 0.03 |     |     | μs             |

|          |             | tnDI(5)  |                       |                                         |                     | 0.03 |     |     |                |

|          | データホールド時間   |          |                       |                                         |                     |      |     |     |                |

| シリアル出力   | 入力クロック      | 出力遅延時間   | tdD0(7)               | S04(PA0),<br>SB4(PA1)<br><br>・(注 4-5-2) | 2.7～3.6             |      |     |     | 1tCYC<br>+0.05 |

|          |             |          | tdD0(8)               |                                         |                     |      |     |     | 1tCYC<br>+0.05 |

注 4-5-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-5-2：SI0CLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

## LC88FC2H0A

### 3-2. SI04 シリアル入出力特性（ウェークリップ機能使用時）(注 4-6-1)

| 項目       |             |          | 記号          | 適用端子<br>・備考           | 条件                                    | 規格      |      |                |      |

|----------|-------------|----------|-------------|-----------------------|---------------------------------------|---------|------|----------------|------|

|          |             |          |             |                       |                                       | min     | typ  | max            | unit |

| シリアルクロック | 入力クロック      | 周期       | tSCK(9)     | SCK4(PA2)             | ・図 6 参照<br>2.7～3.6                    | 2       |      |                | tCYC |

|          |             | 低レベルパルス幅 | tSCKL(9)    |                       |                                       | 1       |      |                |      |

|          |             | 高レベルパルス幅 | tSCKH(9)    |                       |                                       | 1       |      |                |      |

|          |             |          | tSCKHBSY(9) |                       |                                       | 2       |      |                |      |

| シリアル入力   | データセットアップ時間 |          | tsDI(6)     | SI4(PA1),<br>SB4(PA1) | ・SIOCLK の立ち上がり<br>に対して規定する<br>・図 6 参照 | 0.03    |      |                |      |

|          | データホールド時間   |          | thDI(6)     |                       |                                       | 2.7～3.6 | 0.03 |                |      |

| シリアル出力   | 入力クロック      | 出力遅延時間   | tdD0(9)     | SO4(PA0),<br>SB4(PA1) | ・(注 4-4-2)<br>2.7～3.6                 |         |      | 1tCYC<br>+0.05 | μs   |

注 4-6-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-6-2：SIOCLK の立ち下がりに対して規定する。オープンドレイン出力時は出力変化開始までの時間として規定する。図 6 参照。

# LC88FC2H0A

## 4-1. SMIICO 単純 SI0 モード時入出力特性

| 項目       |             | 記号       | 適用端子<br>・備考                       | 条件                                                            | 規格                     |         |     |                |      |

|----------|-------------|----------|-----------------------------------|---------------------------------------------------------------|------------------------|---------|-----|----------------|------|

|          |             |          |                                   | V <sub>DD</sub> [V]                                           | min                    | typ     | max | unit           |      |

| シリアルクロック | 入力クロック      | 周期       | tSCK(10)                          | SMOCK<br>(P22)                                                | 図 6 参照                 | 2.7~3.6 | 4   |                | tCYC |

|          |             | 低レベルパルス幅 | tSCKL(10)                         |                                                               |                        |         | 2   |                |      |

|          |             | 高レベルパルス幅 | tSCKH(10)                         |                                                               |                        |         | 2   |                |      |

|          | 出力クロック      | 周期       | tSCK(11)                          | SMOCK<br>(P22)                                                | ・CMOS 出力選択時<br>・図 6 参照 | 2.7~3.6 | 4   |                | tSCK |

|          |             | 低レベルパルス幅 | tSCKL(11)                         |                                                               |                        |         | 1/2 |                |      |

|          |             | 高レベルパルス幅 | tSCKH(11)                         |                                                               |                        |         | 1/2 |                |      |

| シリアル入力   | データセットアップ時間 | tsDI(7)  | SMODA<br>(P23),                   | ・SI0CLK の立ち上がり<br>に対して規定する<br>・図 6 参照                         | 2.7~3.6                | 0.03    |     |                | μs   |

|          | データホールド時間   | thDI(7)  |                                   |                                                               |                        | 0.03    |     |                |      |

| シリアル出力   | 出力遅延時間      | tdD0(10) | SMODO<br>(P24),<br>SMODA<br>(P23) | ・SI0CLK の立ち下がり<br>に対して規定する<br>・出力変化開始までの時間として規定する。<br>・図 6 参照 | 2.7~3.6                |         |     | 1tCYC<br>+0.05 |      |

注 4-7-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

# LC88FC2H0A

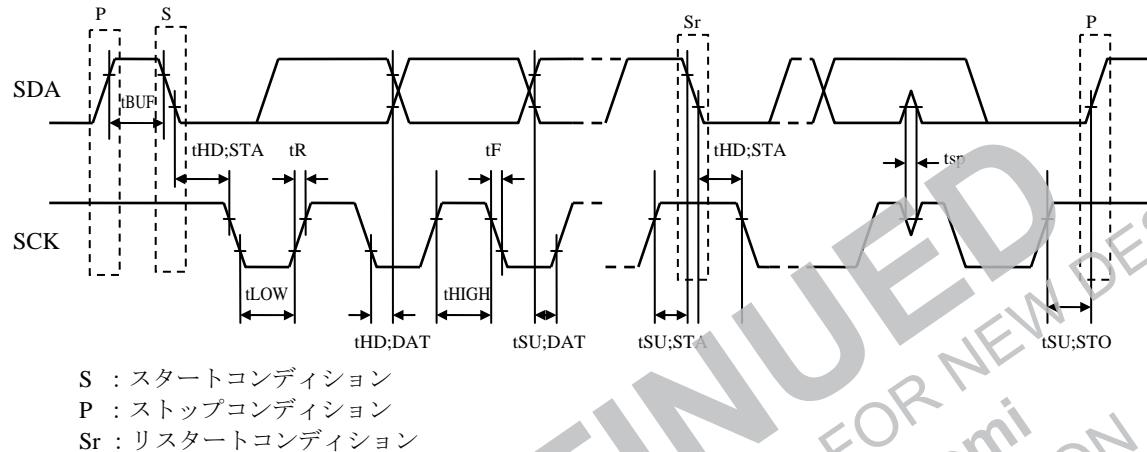

## 4-2. SMIICO I<sup>2</sup>C モード時入出力特性

| 項目                                  |        |              | 記号                         | 適用端子<br>・備考                                  | 条件                       | 規格      |     |  |   |         |  |

|-------------------------------------|--------|--------------|----------------------------|----------------------------------------------|--------------------------|---------|-----|--|---|---------|--|

| クロック                                | 入力クロック | 周期           | tSCL                       | SMOCK<br>(P22)                               | ・図 8 参照                  | 2.7~3.6 | 5   |  |   | Tfilt   |  |

|                                     |        | 低レベル<br>パルス幅 | tSCLL                      |                                              |                          |         | 2.5 |  |   |         |  |

|                                     |        | 高レベル<br>パルス幅 | tSCLH                      |                                              |                          |         | 2   |  |   |         |  |

| 出力クロック                              | 出力クロック | 周期           | tSCLx                      | SMOCK<br>(P22)                               | ・出力変化開始までの時<br>間として規定する。 | 2.7~3.6 | 10  |  |   | tSCL    |  |

|                                     |        | 低レベル<br>パルス幅 | tSCLLx                     |                                              |                          |         | 1/2 |  |   |         |  |

|                                     |        | 高レベル<br>パルス幅 | tSCLHx                     |                                              |                          |         | 1/2 |  |   |         |  |

| SMOC, SMODA 端子入<br>力スパイク抑圧時間        |        |              | tsp                        | SMOCK (P22)<br>SMODA (P23)                   | ・図 8 参照                  | 2.7~3.6 |     |  | 1 | Tfilt   |  |

| スタート、ス<br>トップ間のバス<br>開放時間           | 入<br>力 | tBUF         | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                      |                          | 2.7~3.6 | 2.5 |  |   | Tfilt   |  |

|                                     |        | tBUFx        | SMOCK (P22)<br>SMODA (P23) | ・標準クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          |         | 5.5 |  |   | $\mu$ s |  |

|                                     |        |              |                            | ・高速クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          |         | 1.6 |  |   |         |  |

| スタートリス<br>タートコンディ<br>ションのホール<br>ド時間 | 入<br>力 | tHD;STA      | SMOCK (P22)<br>SMODA (P23) | ・SMIIC レジスタ制御ビット<br>I2CSHDS=0 のとき<br>・図 8 参照 |                          | 2.7~3.6 | 2.0 |  |   | Tfilt   |  |

|                                     |        |              |                            | ・SMIIC レジスタ制御ビット<br>I2CSHDS=1 のとき<br>・図 8 参照 |                          |         | 2.5 |  |   | $\mu$ s |  |

|                                     |        | tHD;STAx     | SMOCK (P22)<br>SMODA (P23) | ・標準クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          |         | 4.1 |  |   |         |  |

| リストアコン<br>ディジョンの<br>セットアップ時<br>間    | 出<br>力 |              |                            | ・高速クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          | 2.7~3.6 | 1.0 |  |   | $\mu$ s |  |

|                                     |        | tSU;STA      | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                      |                          |         | 1.0 |  |   | Tfilt   |  |

|                                     |        | tSU;STAx     | SMOCK (P22)<br>SMODA (P23) | ・標準クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          |         | 5.5 |  |   |         |  |

|                                     |        |              |                            | ・高速クロックモード時<br>・出力変化開始までの時<br>間として規定する。      |                          |         | 1.6 |  |   |         |  |

# LC88FC2H0A

| 項目                    |    | 記号       | 適用端子<br>・備考                | 条件                                                                                   | V <sub>DD</sub> [V] | 規格                | 規格  |       |

|-----------------------|----|----------|----------------------------|--------------------------------------------------------------------------------------|---------------------|-------------------|-----|-------|

|                       |    |          |                            |                                                                                      | min                 | typ               | max | unit  |

| ストップコンディションのセットアップ時間  | 入力 | tSU;ST0  | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                                                              | 2.7~3.6             | 1.0               |     | Tfilt |

|                       | 出力 | tSU;ST0x | SMOCK (P22)<br>SMODA (P23) | ・標準クロックモード時<br>・出力変化開始までの時間として規定する。<br>・高速クロックモード時<br>・出力変化開始までの時間として規定する。           |                     | 4.9               |     | μs    |

|                       |    |          |                            |                                                                                      |                     | 1.1               |     |       |

| データホールド時間             | 入力 | tHD;DAT  | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                                                              | 2.7~3.6             | 0                 |     | Tfilt |

|                       | 出力 | tHD;DATx | SMOCK (P22)<br>SMODA (P23) | ・出力変化開始までの時間として規定する。                                                                 |                     | 1                 | 1.5 |       |

| データセットアップ時間           | 入力 | tSU;DAT  | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                                                              | 2.7~3.6             | 1                 |     | Tfilt |

|                       | 出力 | tSU;DATx | SMOCK (P22)<br>SMODA (P23) | ・出力変化開始までの時間として規定する。                                                                 |                     | 1tSCL-<br>1.5Tf11 |     |       |

| SMOCK, SMODA 端子の立下り時間 | 入力 | tF       | SMOCK (P22)<br>SMODA (P23) | ・図 8 参照                                                                              | 2.7~3.6             |                   | 300 | ns    |

|                       | 出力 | tF       | SMOCK (P22)<br>SMODA (P23) | ・SMIIC リスク制御ビット<br>PSLW=1, PHV=1 のとき<br>・SMOCK, SMODA ポート出力 FAST モード設定時<br>・Cb≤400pF |                     | 3<br>20+0.1Cb     |     |       |

|                       |    |          |                            |                                                                                      |                     |                   | 250 |       |

|                       |    |          |                            |                                                                                      |                     |                   | 100 |       |

注 4-8-1：本規格値は理論値である。使用の状態に合わせて必ずマージンを確保すること。

注 4-8-2 : Tfilt は、レジスタ SMICOBRG の bit7, 6(BRP1, BRP0) の設定値と、システムクロック周波数により決定される値

| BRP1 | BRP0 | Tfilt  |

|------|------|--------|

| 0    | 0    | tCYC×1 |

| 0    | 1    | tCYC×2 |

| 1    | 0    | tCYC×3 |

| 1    | 1    | tCYC×4 |

Tfilt は以下の範囲になるように、(BPR1, BPR0) を設定してください。

$$250 \text{ ns} \geq \text{Tfilt} > 140 \text{ ns}$$

注 4-8-3 : Cb は各バスに接続された負荷のトータル(単位 : pF) Cb≤400pF

注 4-8-4 : 標準クロックモードは SMICOBRG の設定を、以下の条件の範囲内とした場合

$$250 \text{ ns} \geq \text{Tfilt} > 140 \text{ ns}$$

$$\text{BRDQ(bit5)} = 1$$

$$\text{SCL 周波数設定} \leq 100 \text{ kHz}$$

高速クロックモードは SMICOBRG の設定を、以下の条件の範囲内とした場合

$$250 \text{ ns} \geq \text{Tfilt} > 140 \text{ ns}$$

$$\text{BRDQ(bit5)} = 0$$

$$\text{SCL 周波数設定} \leq 400 \text{ kHz}$$

## 5-1. SMIIC1 単純 SIO モード時入出力特性

| 項目       |                 | 記号           | 適用端子<br>・備考                       | 条件                                                                               | $V_{DD}$ [V]                          | 規格  |     |                |         |

|----------|-----------------|--------------|-----------------------------------|----------------------------------------------------------------------------------|---------------------------------------|-----|-----|----------------|---------|

|          |                 |              |                                   |                                                                                  |                                       | min | typ | max            | unit    |