# **Direct AC Drive LED Driver** for Power Factor Correction and Precise Constant Current Regulation

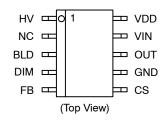

The NCL30170 is a linear regulating constant current LED controller in smart lighting and phase-cut dimming application. The controller manages multiple series LED current in ON Semiconductor's proprietary auto-commutation topology with high CC regulation accuracy and superior performance in PF and THD.

The device provides wide analog dimming range with linear dimming curve and low current consumption in the standby mode. In phase-cut dimming application, input current shape modulation provides both good PF and excellent dimmer compatibility. Self-biasing high-voltage regulator supplies stable IC bias voltage with fast startup time. The NCL30170 has several protections such as thermal shutdown, input over voltage protection, sensing resistor short protection and LED over current limit for high system reliability.

# Features

- Accurate CC Regulation by Closed Loop Control

- High PF and Low THD: 0.99 PF and less than 10% THD

- Wide Analog Dimming down to 5%

- Input Voltage and Current Modulation for High Phase-cut Dimmer Compatibility

- Low System BOM

- High Voltage Startup

- Flexible Selection of the Number of LED Channels

- Wide Range Power Design in 5 ~ 300 W with Single Controller

- Robust Protection Features

- Input Over Voltage Protection

- Sensing Resistor Short Protection

- Thermal Shutdown

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

• LED Lighting System

# **ON Semiconductor®**

www.onsemi.com

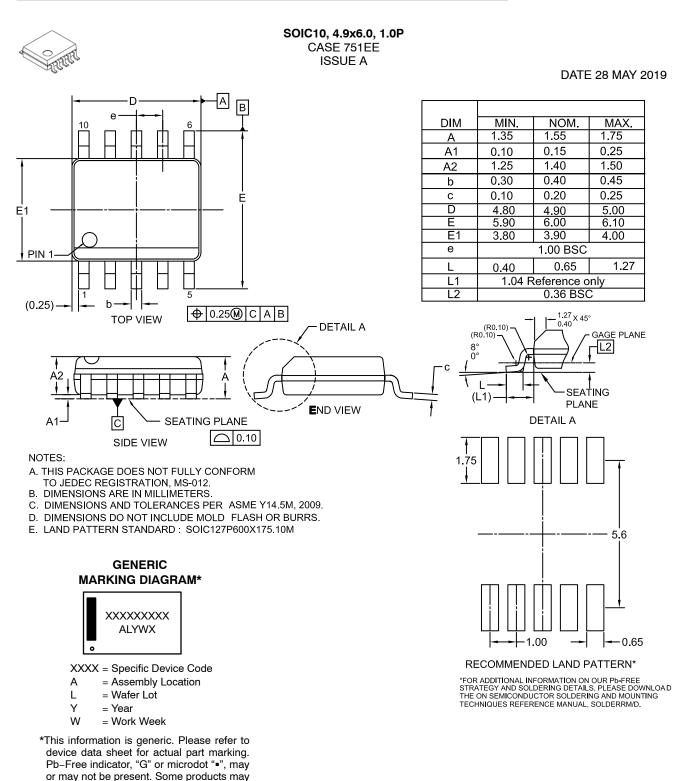

SOIC10 R2 SUFFIX CASE 751EE

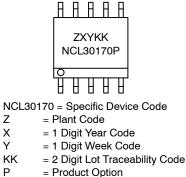

# MARKING DIAGRAM

#### **ORDERING INFORMATION**

See detailed ordering, marking and shipping information on page 12 of this data sheet.

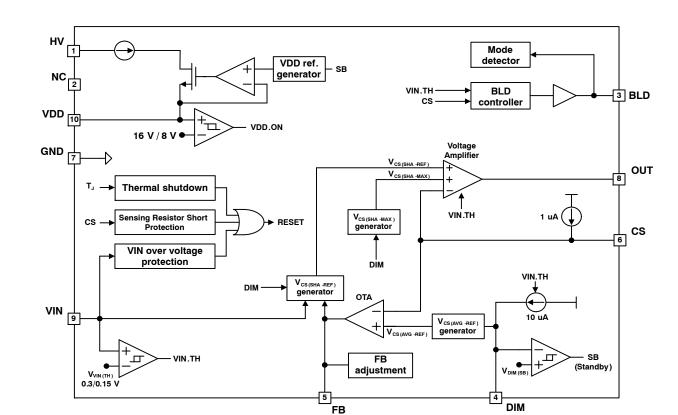

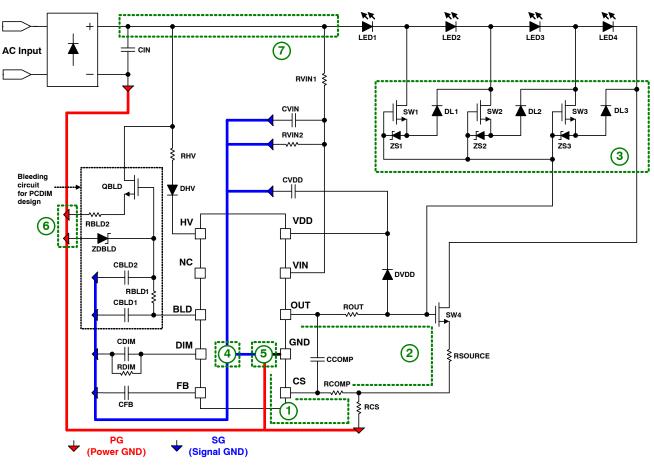

Figure 2. Simplified Block Diagram

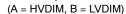

## **Table 1. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name | Function                | Description                                                                                                                                                             |

|---------|----------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | HV       | High Voltage Startup    | This pin is connected to the rectified input voltage for fast startup and self biasing.                                                                                 |

| 2       | NC       | No Connection           |                                                                                                                                                                         |

| 3       | BLD      | Bleeding Control        | This pin controls the external bleeding MOSFET for phase-cut dimming.                                                                                                   |

| 4       | DIM      | Dimming Input           | Analog dimming signal is provided to this pin. In phase-cut dimming, this pin is connected to a resistor and a capacitor in parallel to obtain phase angle information. |

| 5       | FB       | Feedback                | This pin is connected to the compensation network.                                                                                                                      |

| 6       | CS       | Current Sense           | This pin monitors LED current.                                                                                                                                          |

| 7       | GND      | Ground.                 | The controller ground.                                                                                                                                                  |

| 8       | OUT      | Output Drive            | This pin is connected to drive external regulator switch.                                                                                                               |

| 9       | VIN      | Input Voltage Detection | This pin is connected to the resistive divider to detect input voltage.                                                                                                 |

| 10      | VDD      | Power Supply            | This pin voltage is regulated by internal self biasing HV supply.                                                                                                       |

# Table 2. NCL30170 VERSION

| Part Number   | Description                                                          |

|---------------|----------------------------------------------------------------------|

| NCL30170ADR2G | Option A: HVDIM version has analog DIM voltage control in 0 ~ 3 V.   |

| NCL30170BDR2G | Option B: LVDIM version has analog DIM voltage control in 0 ~ 1.5 V. |

## **Table 3. MAXIMUM RATINGS**

| Rating                                                                        | Symbol                 | Value      | Unit |

|-------------------------------------------------------------------------------|------------------------|------------|------|

| HV Pin Voltage Range                                                          | V <sub>HV(MAX)</sub>   | 560        | V    |

| VDD, BLD, OUT, VIN Pin Voltage Range                                          | V <sub>MV(MAX)</sub>   | -0.3 to 26 | V    |

| FB, DIM, CS Pin Voltage Range                                                 | V <sub>LV(MAX)</sub>   | –0.3 to 6  | V    |

| CS Pin Negative Pulse Voltage at $I_{LV}$ < 0.2 A and $t_{PULSE}$ < 5 $\mu s$ | V <sub>LV(PULSE)</sub> | -1.5       | V    |

| Maximum Power Dissipation ( $T_A < 50^{\circ}C$ )                             | P <sub>D(MAX)</sub>    | 663        | mW   |

| Maximum Junction Temperature                                                  | T <sub>J(max)</sub>    | 150        | °C   |

| Storage Temperature Range                                                     | T <sub>STG</sub>       | –55 to 150 | °C   |

| Junction-to-Ambient Thermal Impedance                                         | R <sub>0JA</sub>       | 158        | °C/W |

| Junction-to-Case Thermal Impedance                                            | R <sub>θJC</sub>       | 39         | °C/W |

| ESD Capability, Human Body Model (Note 1)                                     | ESDHBM                 | 1.5        | kV   |

| ESD Capability, Charged Device Model (Note 1)                                 | ESDCDM                 | 1.0        | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

## **Table 4. RECOMMENDED OPERATING RANGES**

| Rating               | Symbol | Min | Max | Unit |  |

|----------------------|--------|-----|-----|------|--|

| Junction Temperature | TJ     | -40 | 125 | °C   |  |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

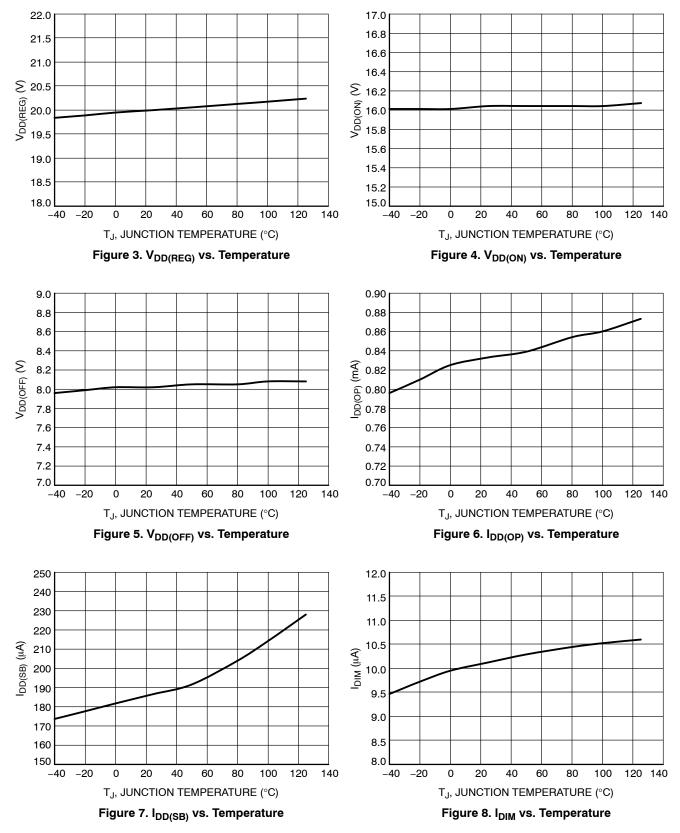

# Table 5. ELECTRICAL CHARACTERISTICS V\_{DD} = 20 V and T\_J = -40 $\sim$ 125°C unless otherwise specified

| Parameter                                                                                                               | Test Conditions                                                                                                                                                                                                                 | Symbol                       | Min                                                | Тур                                                | Max                                                | Unit  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|-------|

| VDD SECTION                                                                                                             | L                                                                                                                                                                                                                               |                              |                                                    |                                                    |                                                    |       |

| VDD Regulation Voltage                                                                                                  | V <sub>HV</sub> = 80 V                                                                                                                                                                                                          | V <sub>DD(REG)</sub>         | 19.5                                               | 20                                                 | 20.5                                               | V     |

| VDD Regulation High Voltage at Standby                                                                                  | V <sub>HV</sub> = 80 V , V <sub>DIM</sub> = 0 V                                                                                                                                                                                 | V <sub>DD(SB-H)</sub>        | 9.5                                                | 10                                                 | 10.5                                               | V     |

| VDD Regulation Low Voltage at Standby                                                                                   | V <sub>HV</sub> = 80 V , V <sub>DIM</sub> = 0 V                                                                                                                                                                                 | V <sub>DD(SB-L)</sub>        | 9.0                                                | 9.5                                                | 10.0                                               | V     |

| IC Turn-On Threshold Voltage                                                                                            |                                                                                                                                                                                                                                 | V <sub>DD(ON)</sub>          | 15                                                 | 16                                                 | 17                                                 | V     |

| IC Turn-Off Threshold Voltage                                                                                           |                                                                                                                                                                                                                                 | V <sub>DD(OFF)</sub>         | 7                                                  | 8                                                  | 9                                                  | V     |

| Startup HV Current                                                                                                      | V <sub>HV</sub> = 80 V, V <sub>DD</sub> = V <sub>DD(ON)</sub> – 1.6 V                                                                                                                                                           | I <sub>DD(ST-HV)</sub>       | 1.35                                               |                                                    |                                                    | mA    |

| Startup Current                                                                                                         | V <sub>HV</sub> = 80 V, V <sub>DD</sub> = V <sub>DD(ON)</sub> – 1.6 V                                                                                                                                                           | I <sub>DD(ST)</sub>          |                                                    | 90                                                 | 200                                                | μΑ    |

| Operating Current                                                                                                       | V <sub>HV</sub> = 80 V                                                                                                                                                                                                          | I <sub>DD(OP)</sub>          |                                                    | 0.8                                                | 1.2                                                | mA    |

| Standby Current                                                                                                         | V <sub>HV</sub> = 80 V, T <sub>J</sub> = 25°C                                                                                                                                                                                   | I <sub>DD(SB)</sub>          |                                                    |                                                    | 250                                                | μA    |

| DIM SECTION                                                                                                             | L                                                                                                                                                                                                                               |                              |                                                    |                                                    |                                                    |       |

| DIM Sourcing Current                                                                                                    | V <sub>DIM</sub> = 3.5 V                                                                                                                                                                                                        | I <sub>DIM</sub>             | 9                                                  | 10                                                 | 11                                                 | μA    |

| DIM Voltage for 99% V <sub>CS(AVG-REF)</sub> at<br>HVDIM                                                                | A version                                                                                                                                                                                                                       | V <sub>DIM(MAX-EFF-HV)</sub> | 2.91                                               | 2.97                                               | 3.03                                               | V     |

| DIM Voltage for 99% V <sub>CS(AVG-REF)</sub> at LVDIM                                                                   | B version                                                                                                                                                                                                                       | VDIM(MAX-EFF-LV)             | 1.428                                              | 1.488                                              | 1.548                                              | V     |

| Standby Enabling DIM Voltage at HVDIM                                                                                   | A version                                                                                                                                                                                                                       | V <sub>DIM(SB-ENA-HV)</sub>  | 0.15                                               | 0.2                                                | 0.25                                               | V     |

| Standby Disabling DIM Voltage at HVDIM                                                                                  | A version                                                                                                                                                                                                                       | V <sub>DIM(SB-DIS-HV)</sub>  | 0.25                                               | 0.3                                                | 0.35                                               | V     |

| Standby Enabling DIM Voltage at LVDIM                                                                                   | B version                                                                                                                                                                                                                       | V <sub>DIM(SB-ENA-LV)</sub>  | 0.05                                               | 0.1                                                | 0.15                                               | V     |

| Standby Disabling DIM Voltage at LVDIM                                                                                  | B version                                                                                                                                                                                                                       | V <sub>DIM(SB-DIS-LV)</sub>  | 0.15                                               | 0.2                                                | 0.25                                               | V     |

| Standby Delay Time                                                                                                      |                                                                                                                                                                                                                                 | t <sub>SB(DELAY)</sub>       |                                                    | 10                                                 |                                                    | ms    |

| CS SECTION                                                                                                              |                                                                                                                                                                                                                                 |                              |                                                    | 1                                                  |                                                    |       |

| CS Average Regulation Voltage at HVDIM<br>(Test in closed loop CC regulation)<br>CS Average Regulation Voltage at LVDIM | A version<br>$V_{DIM} = 3.1 V$<br>$V_{DIM} = 3.1 V$ (Note 2)<br>$V_{DIM} = 1.0 V$<br>$V_{DIM} = 1.0 V$ (Note 2)<br>$V_{DIM} = 0.3 V$ (T <sub>J</sub> = 25°C)<br>$V_{DIM} = 0.3 V$ (T <sub>J</sub> = 25°C) (Note 2)<br>B version | V <sub>CS</sub> (AVG-REG-HV) | 1.432<br>1.455<br>0.253<br>0.265<br>0.025<br>0.043 | 1.500<br>1.500<br>0.300<br>0.300<br>0.050<br>0.050 | 1.568<br>1.545<br>0.347<br>0.335<br>0.075<br>0.057 | V     |

| (Test in closed loop CC regulation)                                                                                     | $V_{DIM} = 1.6 V$ $V_{DIM} = 1.6 V (Note 2)$ $V_{DIM} = 1.0 V$ $V_{DIM} = 1.0 V (Note 2)$ $V_{DIM} = 0.2 V (Note 2)$ $V_{DIM} = 0.2 V (T_{J} = 25^{\circ}C) (Note 2)$                                                           | Vcs(avg-reg-lv)              | 1.432<br>1.455<br>0.805<br>0.825<br>0.025<br>0.043 | 1.500<br>1.500<br>0.875<br>0.875<br>0.050<br>0.050 | 1.568<br>1.545<br>0.945<br>0.925<br>0.075<br>0.057 |       |

| Temperature Coefficient of CS Regulation                                                                                | $V_{DIM}$ = 0.3 V A Ver. Design guaranteed                                                                                                                                                                                      | TC <sub>VCS(AVG-REG)</sub>   | -180                                               |                                                    | +180                                               | μV/°C |

| CS Source Current                                                                                                       |                                                                                                                                                                                                                                 | I <sub>CS(SOURCE)</sub>      | 0.7                                                | 1.0                                                | 1.3                                                | μA    |

| FB SECTION                                                                                                              |                                                                                                                                                                                                                                 |                              |                                                    |                                                    |                                                    |       |

| FB OTA Sink Current                                                                                                     | V <sub>CS</sub> = 2.5 V                                                                                                                                                                                                         | I <sub>FB(SINK)</sub>        | 26                                                 | 34                                                 | 47                                                 | μΑ    |

| FB OTA Source Current                                                                                                   | V <sub>CS</sub> = 0.5 V                                                                                                                                                                                                         | I <sub>FB(SOURCE)</sub>      | 26                                                 | 34                                                 | 47                                                 | μA    |

| FB OTA Sink Current     | V <sub>CS</sub> = 2.5 V                           | I <sub>FB(SINK)</sub>   | 26  | 34 | 47 | μΑ   |

|-------------------------|---------------------------------------------------|-------------------------|-----|----|----|------|

| FB OTA Source Current   | V <sub>CS</sub> = 0.5 V                           | I <sub>FB(SOURCE)</sub> | 26  | 34 | 47 | μΑ   |

| FB OTA Transconductance |                                                   | 9м(FB)                  | 26  | 34 | 47 | μmho |

| FB OTA High Voltage     | $V_{\mbox{DIM}}$ = 3.3 V, $V_{\mbox{CS}}$ = 0.5 V | V <sub>FB(HIGH)</sub>   | 4.7 |    |    | V    |

Drift after IC reliability test (HTOL, HOSL, TMCL, HAST) is not included.

If over-temperature protection is activated, the power system enters Protection Mode and output is disabled. Device operation above the maximum junction temperature is not guaranteed.

| Parameter                               | Test Conditions                     | Symbol                   | Min  | Тур  | Max  | Unit |

|-----------------------------------------|-------------------------------------|--------------------------|------|------|------|------|

| FB SECTION                              |                                     |                          |      |      | •    | •    |

| FB OTA Low Voltage                      | $V_{DIM}$ = 3.3 V, $V_{CS}$ = 2.5 V | V <sub>FB(LOW)</sub>     |      |      | 0.1  | V    |

| FB Clamping Voltage at PCDIM            |                                     | V <sub>FB(CLP-PC)</sub>  | 1.7  | 1.8  | 1.9  | V    |

| VIN SECTION                             | ·                                   |                          |      |      | -    |      |

| VIN-TH High Threshold                   |                                     | V <sub>VIN(TH-H)</sub>   | 0.25 | 0.30 | 0.35 | V    |

| VIN-TH Low Threshold                    |                                     | V <sub>VIN(TH-L)</sub>   | 0.10 | 0.15 | 0.20 | V    |

| OUT SECTION                             |                                     |                          |      |      |      |      |

| OUT Voltage High                        |                                     | V <sub>OUT(H)</sub>      | 19   |      |      | V    |

| OUT Voltage Low                         |                                     | V <sub>OUT(L)</sub>      |      |      | 1    | V    |

| Voltage Amplifier Input Offset          |                                     | V <sub>OUT(OFFSET)</sub> |      |      | 10   | mV   |

| Voltage Amplifier Open Loop Gain        | Design guaranteed                   | A <sub>VA(OPEN)</sub>    |      | 100  |      | dB   |

| Voltage Amplifier Bandwidth             | Design guaranteed                   | f <sub>VA(BW)</sub>      |      | 190  |      | kHz  |

| BLD SECTION                             |                                     |                          |      |      |      |      |

| BLD Reset Time                          |                                     | t <sub>BLD(RST)</sub>    | 56   | 80   | 104  | μs   |

| Phase Cut DIM Mode Monitoring Time      |                                     | t <sub>BLD</sub> (PCDIM) | 3.5  | 5.0  | 6.8  | μs   |

| Phase Cut DIM Mode Monitoring Voltage   |                                     | V <sub>BLD(PCDIM)</sub>  | 2.75 | 3.25 | 3.75 | V    |

| Internal BLD Resistance                 |                                     | R <sub>BLD</sub>         | 85   | 110  | 135  | kΩ   |

| BLD Enabling CS Voltage                 |                                     | V <sub>CS(BLD)</sub>     | 150  | 200  | 250  | mV   |

| PROTECTION SECTION                      |                                     |                          |      |      |      |      |

| Thermal Shut Down Temperature           | Design guaranteed (Note 3)          | T <sub>SD</sub>          | 145  | 160  | 175  | °C   |

| Thermal Shut Down Hysteresis            | Design guaranteed                   | T <sub>SD(HYS)</sub>     |      | 30   |      | °C   |

| Input Over Voltage Protection Threshold |                                     | V <sub>VIN(OVP)</sub>    | 3.5  | 4.0  | 4.5  | V    |

| Sensing Resistor Short Current          |                                     | I <sub>SRSP</sub>        | 30   |      | 90   | mA   |

| Sensing Resistor Short Voltage          |                                     | V <sub>SRSP</sub>        | 60   | 100  | 140  | mV   |

Drift after IC reliability test (HTOL, HOSL, TMCL, HAST) is not included.

If over-temperature protection is activated, the power system enters Protection Mode and output is disabled. Device operation above the maximum junction temperature is not guaranteed.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# **APPLICATION INFORMATION**

## General

NCL30170 provides accurate LED current regulation with good PF and THD in ON Semiconductor's proprietary auto-commutation topology. The number of LED current regulation channels is flexibly selected with single controller. By selecting different values of external resistor and capacitor at DIM pin, either analog dimming or phase-cut dimming is easily implemented. Self-biasing HV supply shortens startup time with no external components and standby power consumption is minimized by reducing the operating current.

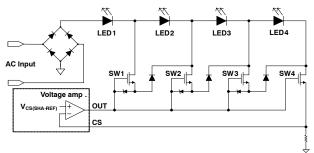

## **ON Semiconductor's Auto Commutation Topology**

By adding cost effective HV diode between series switch connection, auto commutation in each LED channels is easily implemented in ON Semiconductor's proprietary topology. User can choose the number of LED channels based on the trade–off of system BOM and efficiency.

## **Power Factor Correction**

Different from stepped input current in conventional parallel topology, NCL30170 in new parallel topology provides excellent sinusoidal input current shape with 0.99 PF and less than 10% THD.

## **Constant Current Regulation**

Averaged input current is precisely regulated by closed loop control which minimizes CC tolerance in mains line variation.

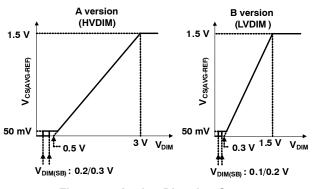

# **Analog Dimming**

NCL30170 features wide analog dimming down to 5%. The dimming curve is linear and IC to IC tolerance is small by high resolution trimming in max and min VDIM conditions.

# Low Standby Power

When DIM pin voltage is close to 0 V, standby mode is entered and most of the internal biasing blocks are turned off to minimize standby power. Also, VDD regulation voltage is dropped from 20 V to 10 V and internal HV supply headroom loss will be almost zero if there is external supply voltage (around 15 V) connection through diode to VDD pin.

## Phase-cut Dimming

As phase angle is reduced, input current is smoothly changed to flat shape from sinusoidal shape. In the low phase angle range, the flattened input current is maintained higher than TRIAC holding current. When input voltage is less than first LED channel voltage and CS voltage is close to 0 V, BLD pin controls external bleeding MOSFET so that input voltage softly reaches to 0 V and maintains close to 0 V during phase–cut condition. The input current shape and bleeding current control performs high dimmer compatibility.

# **High Voltage Startup**

Internal HV startup fastens startup time less than 0.2 sec with no external components.

## Input Over Voltage Protection

When VIN pin voltage is higher than 4 V, OUT pin voltage is pulled down and external linear regulator switches are protected from thermal stress by large headroom loss.

## Thermal Shut Down

Protection is triggered when the internal junction temperature reaches to  $150^{\circ}$ C and normal startup begins once the temperature comes down to  $120^{\circ}$ C.

#### **Sensing Resistor Short Protection**

Short circuit of a sensing resistor makes severe over current at LED loads by losing close loop regulation. At startup, CS pin short is monitored by sourcing large current into external sensing resistor and protection is triggered if CS pin voltage is lower than SRSP threshold voltage.

## **Direct AC Driver Topology**

NCL30170 controls multiple LED channels in new Direct AC Drive parallel topology. In the configuration, HV blocking diodes are connected between SW(n) source and SW(n+1) drain. As input voltage increases, the HV diodes are turned off one by one in auto commutation of the ambient switches. Therefore, one main amplifier controls all the channel current with one reference. The amplifier CS shaping reference,  $V_{CS(SHA-REF)}$ , is sinusoidal so that the input current is optimally sinusoidal with 0.99 PF and less than 10% THD compared to the conventional parallel topology which hardly meets THD in class C due to the stepped input current. 24 V zener diodes are added at gate to source node of each switch except for the last channel switch so that gate to source voltage is maintained under maximum voltage rating specified in the external switch datasheet.

Figure 9. ON Semiconductor's Proprietary DACD Topology

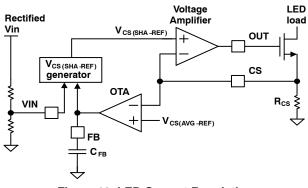

#### **Current Regulation and Power Factor Correction**

An LED current is constantly regulated in the closed feedback loop. The LED current is detected through CS pin and CS voltage is compared with  $V_{CS(AVG-REF)}$  reference by internal OTA which generates FB voltage in a narrow bandwidth due to an external large compensation capacitor,  $C_{FB}$ . In the closed loop, averaged CS voltage is accurately regulated same as  $V_{CS(AVG-REF)}$  thanks to a minimized input voltage offset of OTA which is obtained by high resolution trimming done in mass production.

Figure 10. LED Current Regulation

An input current in the driver flows through CS sensing resistor,  $R_{CS}$ . Therefore, sinusoidal CS voltage shape in a half line period makes sinusoidal input current with ideal power factor correction. In order to obtain the excellent PF

and THD, CS voltage shape is controlled by a voltage amplifier and the voltage amplifier reference,  $V_{CS(SHA-REF)}$ , is set by VIN and FB signals. VIN voltage comes from a resistive divider detecting a rectified Vin.  $V_{CS(SHA-REF)}$  generator outputs  $V_{CS(SHA-REF)}$  which is a sum of VIN voltage and a voltage offset controlled by the FB voltage. As line voltage increases, FB voltage is reduced to keep the same CS average voltage by OTA and  $V_{CS(SHA-REF)}$  voltage offset is reduced accordingly.

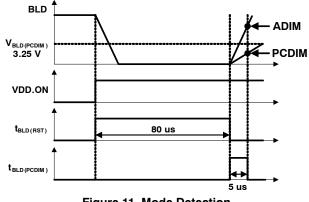

#### **Mode Detection**

NCL30170 provides two dimming modes, ADIM (Analog Dimming Mode) and PCDIM (Phase-Cut Dimming Mode). The dimming mode is set before current regulation starts and NCL30170 operates differently in each dimming mode for the optimized dimming control.

BLD voltage is pulled up to VDD during UVLO state and pulled down for 80 us once VDD is higher than VDD.ON threshold. After 80 us  $t_{BLD(RST)}$ , BLD pin is pulled up by internal 110 k $\Omega$  R<sub>BLD</sub> for 5 us  $t_{BLD(PCDIM)}$ . If BLD voltage is less than 3.25 V V<sub>BLD(PCDIM</sub>) threshold in the end of  $t_{BLD(PCDIM)}$  by a large capacitor over 500 pF in an external bleeding circuit for PCDIM, dimming mode is set by PCDIM. If not, operation begins in ADIM mode. In order to set ADIM mode, BLD pin is open or connected to a filtering capacitor less than 50 pF.

Figure 11. Mode Detection

#### **Analog Dimming**

Analog dimming is controlled by DC DIM voltage supplied from external dimming control signal. For a resistor controlled analog dimming, a variable resistor is connected to DIM pin in which 10 uA DIM internal current source and the variable resistor sets the DIM voltage.

As DIM voltage is reduced,  $V_{CS(AVG-REF)}$  is reduced accordingly. As  $V_{CS(AVG-REF)}$  decreases, FB voltage is also reduced and  $V_{CS(SHA-REF)}$  has more negative offset voltage from VIN pin voltage.

When dimming signal is generated by an MCU, maximum dimming voltage is dependent on Vcc (3.3 V or 1.6 V) of the selected MCU. Therefore, two versions of NCL30170 are provided as shown in Figure 12. In A version, DIM range is up to 3 V and standby is enabled when DIM voltage is lower than 0.2/0.3 V. B version provides dimming range in 0 ~ 1.5 V DIM voltage with 0.1/0.2 V standby threshold voltage,  $V_{\text{DIM(SB)}}$ . In both options,  $V_{\text{CS(AVG-REF)}}$  is in between 50 mV and 1.5 V so that min LED brightness is less than 5% of maximum light output.

When DIM voltage is lower than  $V_{DIM(SB)}$  for 10 ms  $t_{SB(DELAY)}$ , standby mode is entered and IC operating current drops less than 300  $\mu$ A.

Figure 12. Analog Dimming Curve

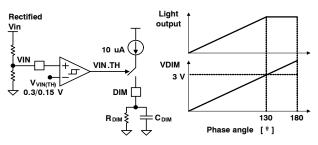

#### **Phase-Cut Dimming**

In PCDIM mode, DIM current source is enabled and disabled by VIN.TH signal which is set by hysteretic comparator detecting VIN pin voltage. A time constant of external  $R_{DIM}$  and  $C_{DIM}$  is around 100 ms so that DIM voltage is almost constant over a half line period. Therefore, DIM voltage level is proportional to the phase angle set by the phase–cut dimmer.

When VDIM is higher than 3 V,  $V_{CS(AVG-REF)}$  is constantly set to 1.5 V and constant light output is obtained in the VDIM range. Also,  $V_{CS(SHA-REF)}$  is set to sinusoidal shape dominantly determined by VIN voltage for high PF. As VDIM decreases lower than 3 V, light output is reduced and  $V_{CS(SHA-REF)}$  gradually changes from sinusoidal shape to flat shape to perform wide phase–cut dimming range and maintain TRIAC holding current by ON Semiconductor's proprietary active PCDIM control.

Figure 13. PCDIM Operation

BLD pin drives external bleeding MOSFET to stabilize phase-cut dimmer during TRIAC turn-off time. At input voltage leading edge, inrush current could come through LED current regulation path and damage LED loads and external regulation switches. Therefore, voltage amplifier output is pulled down during the leading edge and softly rises after several tens of usec to normally regulate LED current.

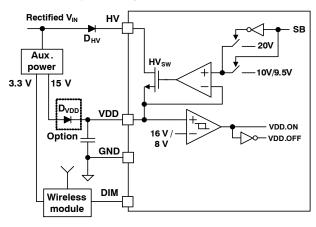

#### VDD Supply

NCL30170 has internal HV JFET switch to supply VDD current for fast startup and self biasing with no external VDD supply circuitry. Once VDD reaches to 16 V, VDD.ON flag is high and internal operation begins and VDD is regulated at 20 V. After VDD drops lower than 8 V, all operating blocks are shutdown. Blocking diode,  $D_{HV}$ , is connected to HV pin to protect reverse current when HV voltage is lower than VDD voltage.

Once SB (Stand By) flag signal is high as DIM pin voltage is lower than  $V_{DIM(SB)}$ , IC minimizes operating current less than 300  $\mu$ A by disabling most of the functional blocks.

Figure 14. VDD Supply

In standby mode, VDD regulation voltage drops from 20 V down to 10 V/9.5 V by a hysteretic regulation. In wireless smart dimming application, auxiliary power supply is generally added to provide wireless module operating current. If aux. power could provide another output voltage around 15 V, this voltage can be utilized to supply NCL30170 VDD current through a diode ( $D_{VDD}$  in Figure 14) during standby condition in which 300  $\mu$ A IC standby current is provided from efficient aux. power output, not internal HV regulator.

#### Protection

NCL30170 provides robust protections such as input over voltage, sensing resistor short and over temperature protections for system reliability.

When input voltage increases out of system input spec, external regulation switches take large amount of headroom loss and those switches can end up with severe damage. In order to protect the input over voltage condition, OUT and FB are pulled down when VIN voltage is higher than 4 V  $V_{VIN(OVP)}$ . This protection is disabled at PCDIM mode to prevent abnormal triggering caused by a leading edge input voltage spike.

When sensing resistor is short circuited, voltage amplifier is out of regulation and OUT pin voltage is pulled up with high power consumption in the external regulation switches. So, at the beginning of  $t_{BLD(RST)}$ , 30 mA I<sub>SRSP</sub> flows into the external CS sensing resistor and SRSP protection is triggered if CS voltage is not higher than 60 mV V<sub>SRSP</sub> for 5  $\mu$ s. Once sensing resistor short protection is triggered, internal timer counts 40 ms and detects CS voltage again with I<sub>SRSP</sub> and startup begins if CS voltage is higher than V<sub>SRSP</sub> threshold.

NCL30170 has thermal shutdown protection by detecting internal junction temperature. When the temperature is over

160°C, protection is triggered and VDD is regulated at 20 V. If the junction temperature drops lower than 130°C, startup sequence with mode detection normally begins.

# **DESIGN GUIDANCE**

Figure 15. System Layout

# Noise Immune Layout Guidance

- 1. CS RCS GND distance should be short.

- 2. OUT SW4 (Switch in the last channel) CS distance should be short.

- 3. It would be better to have SW1 ~ 3 and DL1 ~ 3 close to SW4. But, those switches shouldn't be very close due to thermal dissipation.

- 4. GND of control circuit (CBLD, CDIM, RDIM, CFB, CVIN, RVIN and CVDD) is closely connected near IC GND pin.

- 5. SG and PG are connected near IC GND pin.

- 6. RBLD2 and ZDBLD are connected to PG.

- 7. RVIN1 is connected to rectified input voltage node behind CIN, not between the bridge diode and CIN.

#### EMI Improvement

- 1. RCOMP and CCOMP can be optionally added to reduce regulation loop speed.

- 2. RSOURCE between SW4 and RCS can be optionally added to reduce input current glitch near input voltage zero cross.

# **ORDERING INFORMATION**

| Device        | Package                                     | Shipping      |

|---------------|---------------------------------------------|---------------|

| NCL30170ADR2G | 10 Lead SOIC, JDEC MS-012, 150" Narrow Body | Tape and Reel |

| NCL30170BDR2G | 10 Lead SOIC, JDEC MS-012, 150" Narrow Body | Tape and Reel |

DOCUMENT NUMBER:

98AON13738G

Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.

DESCRIPTION:

SOIC10, 4.9x6.0, 1.0P

PAGE 1 OF 1

ON Semiconductor and use trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

not follow the Generic Marking.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>