# Onsemi

## **Precise CC/CV/CP Secondary-side Controller Compatible with Analog** and PWM Dimming Signal

## NCL38046

## Features

- Precise CC Regulation with +/- 0.5 mV Tolerance

- Compatible with Multiple Dimming Input Signals

- ADIM Pin Receives Analog Voltage Dimming Input

- PWM Pin Receives PWM Duty Dimming Input

- Constant Power Regulation

- Dimming Curve Modulation

- Maximum and Minimum Dimming Input Limit

- Minimum Dimming Output Level Limit

- Linear or Logarithmic Dimming Curve Externally Selectable

- Standby Mode

- 3.3 V Reference Voltage Output

- This is a Pb–Free Device

## **Typical Applications**

- Power Conversion

- Lighting Ballast

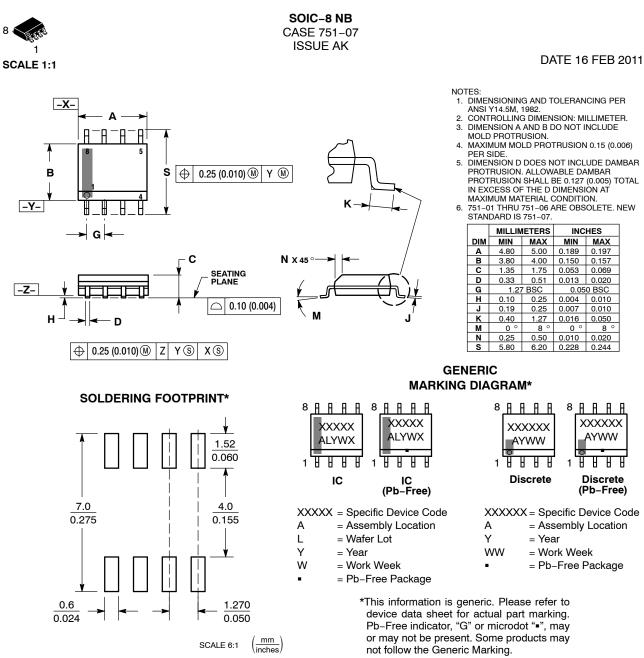

**D SUFFIX** CASE 751-07

= Work Week Number

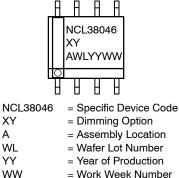

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Device                                                                                                   | Package | Shipping              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|---------|-----------------------|--|--|--|--|

| NCL38046PADR2G                                                                                           | SOIC-8  | 2500 /<br>Tape & Reel |  |  |  |  |

| NCL38046AADR2G                                                                                           | SOIC-8  | 2500 /<br>Tape & Reel |  |  |  |  |

| Letter Coding<br>L1 : P (PDIM modulation), A (ADIM modulation)<br>L2 : Sequentially assigned from A to Z |         |                       |  |  |  |  |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

www.onsemi.com

DATA SHEET

#### **PIN DESCRIPTION**

| Pin N° | Pin Name | Pin Description                                                                                                                                                                                |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | FB       | Output of the feedback OTA.                                                                                                                                                                    |

| 2      | VDD      | IC operating current is supplied to this pin                                                                                                                                                   |

| 3      | SET/REF  | At startup, external SET resistor and capacitor are detected to adjust the internal DIM modulator parameters. Then, 3.3 V output is provided for an external use such as setting ADIM voltage. |

| 4      | ADIM     | ADIM detects an analog voltage signal.                                                                                                                                                         |

| 5      | PDIM     | PDIM detects a PWM duty current signal.                                                                                                                                                        |

| 6      | GND      | The controller ground.                                                                                                                                                                         |

| 7      | CS       | This pin is connected to sense the output current.                                                                                                                                             |

| 8      | VS       | This pin is connected to sense the output voltage.                                                                                                                                             |

#### MAXIMUM RATINGS TABLE

| Rating                                                                             | Symbol               | Value       | Unit |

|------------------------------------------------------------------------------------|----------------------|-------------|------|

| VDD Pin Voltage Range                                                              | V <sub>MV(MAX)</sub> | -0.3 to 30  | V    |

| FB Pin Voltage Range                                                               | V <sub>FB(MAX)</sub> | –0.3 to VDD | V    |

| CS, VS, ADIM, PDIM, SET/REF Pin Voltage Range                                      | V <sub>LV(MAX)</sub> | –0.3 to 6   | V    |

| Maximum Junction Temperature                                                       | T <sub>J(MAX)</sub>  | 150         | °C   |

| Storage Temperature Range                                                          | Т                    | -60 to 150  | °C   |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb – Free Versions (Note1) | T <sub>SLD</sub>     | 260         | °C   |

| ESD Capability, Human Body Model (Note 2)                                          | ESD <sub>HBM</sub>   | 1.5         | kV   |

| ESD Capability, Charged Device Model (Note 2)                                      | ESD <sub>CDM</sub>   | 1           | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC–Q100–003 (EIA/JESD22–A115) Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

### THERMAL CHARACTERISTICS (Note 3)

| Rating                                                                 | Symbol         | Value | Unit |

|------------------------------------------------------------------------|----------------|-------|------|

| Thermal Characteristics, SOIC-8<br>Thermal Resistance, Junction-to-Air | $R_{\ThetaJA}$ | 153   | °C/W |

3. Mounted on a JEDEC standard 51-3 (1s0p) test board, 100 mm<sup>2</sup> copper area, 1 oz copper thickness

#### **RECOMMENDED OPERATING RANGES**

| Rating                               | Symbol | Min | Max | Unit |

|--------------------------------------|--------|-----|-----|------|

| Operating Junction Temperature Range | TJ     | -40 | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## **ELECTRICAL CHARACTERISTICS** (V<sub>DD</sub> = 12 V and T<sub>J</sub> = $-40^{\circ}$ C to 125°C, unless otherwise noted)

| Parameter                             | Test Condition                                                                                                                      | Symbol                   | Min    | Тур   | Max   | Unit |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|-------|-------|------|

| VDD SECTION                           |                                                                                                                                     |                          |        |       |       |      |

| IC Turn-On Threshold Voltage          |                                                                                                                                     | V <sub>DD(ON)</sub>      | 8.0    | 8.5   | 9.0   | V    |

| IC Turn-Off Threshold Voltage         |                                                                                                                                     | V <sub>DD(OFF)</sub>     | 7.0    | 7.5   | 8.0   | V    |

| Startup Current                       | V <sub>DD</sub> = 7 V                                                                                                               | I <sub>DD(ST)</sub>      | -      | -     | 210   | μΑ   |

| Operating Current                     | $I_{PDIM} = 0 \ \mu A, \ R_{SET} = 9.09 \ k\Omega$ (Note 4)                                                                         | I <sub>DD(OP–L)</sub>    | -      | 0.8   | 1.0   | mA   |

|                                       | $I_{PDIM} = 500 \ \mu A, R_{SET} = 9.09 \ (Note 4)$                                                                                 | I <sub>DD(OP-H)</sub>    | -      | 1.3   | 1.5   | mA   |

| Standby Current                       | PDIM = 2% in1 kHz, No R <sub>SET</sub>                                                                                              | I <sub>DD(SB)</sub>      | 400    | -     | 600   | μΑ   |

| SET/REF SECTION                       |                                                                                                                                     |                          |        |       |       |      |

| SET Current                           |                                                                                                                                     | I <sub>SET</sub>         | 47.5   | 50.0  | 52.5  | μA   |

| SET Reference Voltage                 | When $R_{SET} = 9.1 \text{ k}\Omega$ ,<br>$V_{SET(0)} < V_{SET} < V_{SET(1)}$                                                       | V <sub>SET(0)</sub>      | 281    | 300   | 319   | mV   |

|                                       | When $R_{SET}$ = 13 k $\Omega$ , $V_{SET(1)} < V_{SET} < V_{SET(2)}$                                                                | V <sub>SET(1)</sub>      | 519    | 545   | 571   | mV   |

|                                       | When $R_{SET}$ = 18 k $\Omega$ , $V_{SET(2)} < V_{SET} < V_{SET(3)}$                                                                | V <sub>SET(2)</sub>      | 732    | 765   | 798   | mV   |

|                                       | When $R_{SET} = 24 \text{ k}\Omega$ , $V_{SET(3)} < V_{SET} < V_{SET(4)}$                                                           | V <sub>SET(3)</sub>      | 999    | 1040  | 1081  | mV   |

|                                       | When $R_{SET}$ = 33 k $\Omega$ , $V_{SET(4)}$ < $V_{SET}$ < $V_{SET(5)}$                                                            | V <sub>SET(4)</sub>      | 1348   | 1400  | 1452  | mV   |

|                                       | When $R_{SET}$ = 43 k $\Omega$ , $V_{SET(5)}$ < $V_{SET}$ < $V_{SET(6)}$                                                            | V <sub>SET(5)</sub>      | 1814   | 1880  | 1946  | mV   |

|                                       | When $R_{SET}$ = 56 k $\Omega$ , $V_{SET(6)}$ < $V_{SET}$ < $V_{SET(7)}$                                                            | V <sub>SET(6)</sub>      | 2367   | 2450  | 2534  | mV   |

|                                       | When $R_{SET}$ = open, $V_{SET(7)} < V_{SET}$                                                                                       | V <sub>SET(7)</sub>      | 3288   | 3400  | 3512  | mV   |

| SET Capacitor Detection Delay<br>Time | Design guaranteed                                                                                                                   | t <sub>SET(CAP)</sub>    | 4.76   | 5     | 5.26  | μs   |

| SET Resistor Detection Delay Time     | Design guaranteed                                                                                                                   | t <sub>SET(RES)</sub>    | 487    | 512   | 538   | μs   |

| REF Regulation Voltage                |                                                                                                                                     | V <sub>REF</sub>         | 3.26   | 3.30  | 3.34  | V    |

| PDIM and ADIM SECTION                 |                                                                                                                                     |                          |        |       |       |      |

| PDIM High Threshold Current           | Increasing I <sub>PDIM</sub>                                                                                                        | I <sub>PDIM(TH-H)</sub>  | 125    | 153   | 170   | μA   |

| PDIM Low Threshold Current            | Decreasing I <sub>PDIM</sub>                                                                                                        | I <sub>PDIM(TH-L)</sub>  | 55     | 70    | 80    | μA   |

| PDIM Maximum Current Limit            | V <sub>PDIM</sub> = 0 V                                                                                                             | I <sub>PDIM(MAX)</sub>   | 0.8    | 1     | 1.2   | mA   |

| PDIM Regulation Voltage               | I <sub>PDIM</sub> = 250 μA                                                                                                          | V <sub>PDIM</sub>        | 2.9    | 3.0   | 3.1   | V    |

| PDIM Minimum Frequency Limit          | Design Guaranteed                                                                                                                   | f <sub>PDIM(MIN)</sub>   | 65     | -     | -     | Hz   |

| ADIM Maximum Voltage                  |                                                                                                                                     | V <sub>ADIM(MAX)</sub>   | 2.47   | 2.50  | 2.53  | V    |

| VS SECTION                            |                                                                                                                                     |                          |        |       |       |      |

| VS OTA Input Offset                   |                                                                                                                                     | V <sub>VS(OTA-IO)</sub>  | -25    | 0     | +25   | mV   |

| VS Maximum Regulation Voltage         |                                                                                                                                     | V <sub>VS(REG-MAX)</sub> | 2.425  | 2.500 | 2.575 | V    |

| VS Standby Regulation Voltage         | $\begin{array}{l} D_{PDIM} < D_{PDIM(SB-EN)} \text{ in PA version} \\ V_{ADIM} < V_{ADIM(SB-EN)} \text{ in AA version} \end{array}$ | V <sub>VS(REG-SB)</sub>  | 0.475  | 0.500 | 0.525 | V    |

| CS SECTION                            |                                                                                                                                     |                          |        |       |       |      |

| CS OTA Input Offset                   | Temp range: $-40^{\circ}C \approx 125^{\circ}C$                                                                                     | V <sub>CS(OTA-IO)</sub>  | -0.8   | 0     | 0.8   | mV   |

|                                       | Temp range: $-40^{\circ}C \approx 85^{\circ}C$                                                                                      |                          | -0.45  | 0     | 0.45  | mV   |

|                                       | Only 25°C                                                                                                                           |                          | -0.175 | 0     | 0.175 | mV   |

| CS Maximum Regulation Voltage         | $I_{FB}$ = 0.5 mA in a closed loop regulation<br>Temp range: -40°C ~ 125°C                                                          | V <sub>CS(REG-MAX)</sub> | 98     | 100   | 102   | mV   |

|                                       | $I_{FB}$ = 0.5 mA in a closed loop regulation<br>Temp range: 25°C ~ 85°C                                                            |                          | 99     | 100   | 101   | mV   |

| Parameter                                                                                                                   | Test Condition                                                                                              | Symbol                   | Min | Тур  | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------|-----|------|------|------|

| CS Half Regulation Voltage                                                                                                  | Voltage $I_{FB} = 0.5$ mA in a closed loop regulation $V_{CS(REG-H)}$<br>Temp range: -40°C ~ 125°C (Note 5) |                          |     |      | 51.5 | mV   |

|                                                                                                                             | $I_{FB} = 0.5$ mA in a closed loop regulation<br>Temp range: 25°C ~ 85°C (Note 5)                           |                          | 50  | 50.5 | 51   | mV   |

| CS Minimum Regulation Voltage $I_{FB} = 0.5$ mA in a closed loop regulation Temp range: $-40^{\circ}C \approx 125^{\circ}C$ |                                                                                                             | V <sub>CS(REG-MIN)</sub> | 0.3 | 1    | 1.7  | mV   |

|                                                                                                                             | $I_{FB}$ = 0.5 mA in a closed loop regulation<br>Temp range: 25°C ~ 85°C                                    |                          | 0.6 | 1    | 1.4  | mV   |

| CS Fault Current                                                                                                            |                                                                                                             | I <sub>CS(FAULT)</sub>   | -28 | -24  | -19  | μA   |

#### **FB SECTION**

| FB Maximum Sink Current of CS OTA | V <sub>CS</sub> = 1 V | I <sub>FB(SINK-CS-MAX)</sub> | 2.5 | _ | _ | mA  |

|-----------------------------------|-----------------------|------------------------------|-----|---|---|-----|

| FB Maximum Sink Current of VS OTA | V <sub>VS</sub> = 3 V | I <sub>FB(SINK-VS-MAX)</sub> | 2.5 | - | - | mA  |

| Transconductance of CS OTA        |                       | Ям(CS)                       | -   | 7 | - | mho |

| Transconductance of VS OTA        |                       | Ям(VS)                       | -   | 3 | - | mho |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

4. I<sub>DD</sub> is affected to R<sub>SET</sub> value. If you want to know I<sub>DD</sub> with other R<sub>SET</sub>,  $I_{DD(RSET changed)} = I_{DD} - 3.3 V \cdot \left(\frac{1}{9.09k} + \frac{1}{RSET}\right)$ 5. The value has an offset due to MOD<sub>OUT(MIN)</sub> to modulate a dimming curve. V<sub>CS(REG)</sub> is calculated as shown below.  $V_{CS(REG)} = Dim[\%] \cdot slope + offset$ , where  $slope = \frac{MOD_{OUT(MAX)} - MOD_{OUT(MIN)}}{MOD_{IN(MAX)} - MOD_{IN(MIN)}}$ , off set =  $MOD_{OUT(MAX)} - slope \cdot MOD_{IN(MAX)}$

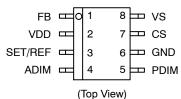

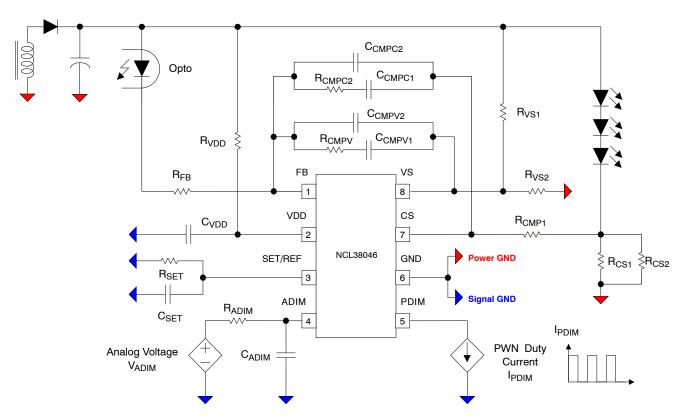

#### **APPLICATION INFORMATION**

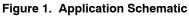

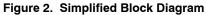

NCL38046 performs precise CC regulation in the wide dimming range controlled by both PWM duty and analog voltage signal. Dimming curve is internally modulated by an effective dimming input range (e.g.,  $10\% \sim 90\%$ ) and the minimum dimming output level (e.g., 1%). Also, either linear or logarithmic dimming curve is externally selected by a SET capacitor. Constant power regulation is implemented by CV regulation reference defined inversely proportional to the dimming level where the CP level is flexibly set by an external SET resistor.

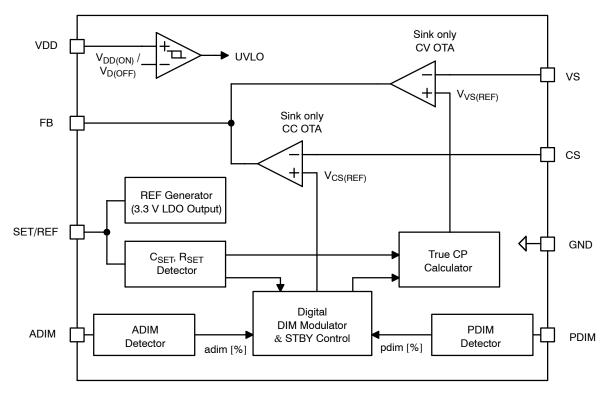

#### CC/ CV Regulation

For high CC accuracy, an input voltage offset of the CC regulation OTA is significantly reduced by a novel amplifier design with high resolution trimming so that the input voltage at room temperature is less than +/– 0.1 mV. When a LED load is connected, CS pin voltage ( $V_{CS}$ ) is regulated to  $V_{CS(REF)}$ , an internally generated CS reference voltage controlled by PDIM and ADIM inputs. When the LED load is open,  $V_{CS}$  drops to 0 V and CC OTA does not sink FB current and  $V_{VS}$  is regulated to  $V_{VS(REF)}$ .

Figure 3. CC/CV Regulation Block

#### CC/ CV Regulation

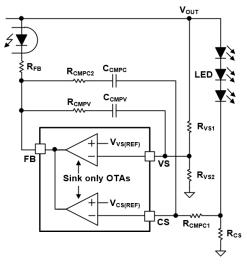

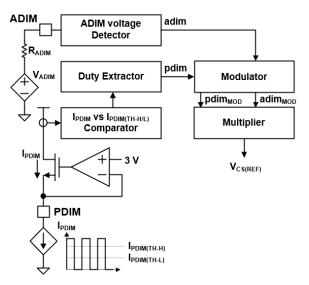

#### PDIM and ADIM Detection

As shown in Figure 4, PDIM pin voltage is regulated to 3 V by the pull-up buffer. PDIM current,  $I_{PDIM}$ , is compared with  $I_{PDIM(TH-H/L)}$  hysteretic current thresholds and the comparison output signal is converted to pdim signal (0% ~ 100%) by the duty extractor. When  $I_{PDIM}$  is higher than the current threshold, it is considered as the on state in the PWM duty. The recommended  $I_{PDIM}$  on-state level is 300 ~ 600  $\mu$ A and PDIM pin is pulled down to 0 V when  $I_{PDIM}$  is higher than 1 mA in order to limit the VDD operating current. 200 Hz PWM frequency is recommended to perform high resolution dimming.

ADIM signal is detected by the ADIM voltage detector and ADIM voltage input range is 0 ~ 2.5 V. The detected ADIM voltage is converted to adim signal (0% ~ 100%). At startup, ADIM pin is buffered by SET/REF pin voltage as described in Section. *REF Function*. So, 10 k $\Omega$  R<sub>ADIM</sub> in Figure 4 is recommended when V<sub>ADIM</sub> is set by the external voltage source not to conflict with an internal buffer (SET/ref to ADIM) output.

Figure 4. CC Reference Generation Block

#### **Dimming Signal Modulation**

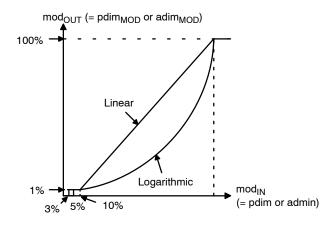

In general, an external dimming signal generator such as 0 - 10 V dimmer doesn't provide the full range of the dimming signal. In such case, NCL38046 can scale either pdim or adim signal by the internal modulator. As shown in Figure 5, the modulator input signal, mod<sub>IN</sub>, has an effective input range between 10% and 90%. In other words, when mod<sub>IN</sub> is 10%, mod<sub>OUT</sub> becomes the min value and mod<sub>OUT</sub> doesn't decrease although mod<sub>IN</sub> goes below 10% because mod<sub>OUT</sub> is clamped to 1% by mod<sub>OUT(MIN)</sub>. When mod<sub>IN</sub> is lower than 3%, NCL38046 enters STBY. In order to exist STBY, mod<sub>IN</sub> should be higher than 5% because of STBY threshold hysteresis.

Figure 5. Dimming Signal Modulation

When  $mod_{IN}$  is 90%,  $mod_{OUT}$  becomes the max value and  $mod_{OUT}$  doesn't increase even though  $mod_{IN}$  rises above 90% by  $mod_{IN(MAX)}$ .

There're also two types of dimming curves (Linear and Logarithmic).

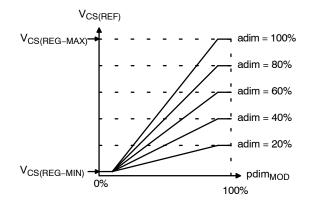

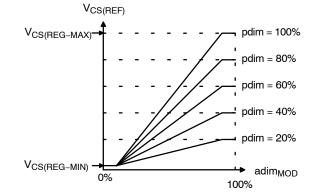

#### Multiplier

Recently, LED drivers generally control the output current by the dual dimming signals to set the maximum output current and to implement the dimming function. In order to perform the multiple dimming in NCL38046, adim (0 ~ 100%) and pdim (0 ~ 100%) signals are multiplied and scaled to V<sub>CS(REF-MAX)</sub> to provide V<sub>CS(REF)</sub> as shown in Figure 6 and Figure 7. The dimming signal input is usually modulated, and the maximum output current setting signal is not modulated just to set the coefficient in the dimming curve.

When analog voltage signal at ADIM is used for the maximum output current setting and PWM duty signal at PDIM is used for dimming, PA version should be used.  $V_{CS(REF)}$  is determined by (eq. 1) which corresponds to Figure 6.

$$V_{CS(REF)}[V] = V_{CS(REF-MAX)}[V] \cdot adim[\%] \cdot pdim_{MOD}[\%]$$

(eq. 1)

When adim is used for dimming and pdim is to set the maximum output current, AA version should be used.  $V_{CS(REF)}$  is set by (eq. 2) corresponding to Figure 7.

$$V_{CS(REF)}[V] = V_{CS(REF-MAX)}[V] \cdot pdim[\%] \cdot adim_{MOD}[\%]$$

(eq. 2)

$V_{CS(\text{REF})}$  dimming voltage range is limited by  $V_{CS(\text{REF-MAX})}$  and  $V_{CS(\text{REF-MIN})}.$

Figure 6. Dimming Curve in PA Version

Figure 7. Dimming Curve in AA Version

#### **CV Reference**

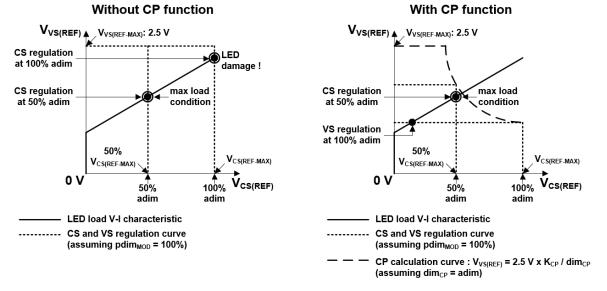

Constant voltage reference is determined by constant power regulation block to protect the LED load and limit the LED driver power when maximum output current is incorrectly set. CV reference,  $V_{VS(REF)}$ , is determined by:

$$V_{VS(REF)}[V] = 2.5 V \cdot K_{CP}[\%] / dim_{CP}[\%]$$

(eq. 3)

where  $K_{CP}[\%]$  is a constant power coefficient and dim<sub>CP</sub>[%] is CP dim input which is adim in PA version or pdim in AA version. K<sub>CP</sub> is set by R<sub>SET</sub> value as described in Section. SET/REF Function. Also, V<sub>VS(REF-MAX)</sub> is clamped to 2.5 V.

Figure 8 shows an example of the load operating point assuming that the maximum current spec of an LED load is at 50% V<sub>CS(REF-MAX)</sub> by setting adim at 50%  $(V_{ADIM} = 1.25 \text{ V})$  and the output current dimming is controlled by pdim<sub>MOD</sub>.

Without CP function, the LED current will be twice than its maximum current rating with the LED damage if adim is mistakenly set to 100% (V<sub>ADIM</sub> = 2.5 V).

With CP function in Figure 8,  $V_{VS(REF)}$  is set by (eq. 3) and the LED load is safe even though adim is wrongly set to 100% because V<sub>VS(REF)</sub>, inversely proportional to adim, is set lower than the max load operating point. If adim is correctly set back to 50%, V<sub>VS(REF)</sub> is set higher than the max load condition and the LED load current is regulated to the right max load condition by CS regulation.

When the LED load is open, the output voltage is regulated little higher than the LED load forward voltage so that there won't be a large inrush current from the output capacitor to the LED load when the LED load is connected again. In the conventional LED driver with CP function, CV regulation level is determined by total LED current level so that the output voltage is regulated to the maximum output level at LED open condition. In such condition, the LED load can be damaged when the LED load is connected because the output regulation level is much higher than the LED load forward voltage.

Figure 8. Operating Point by the Maximum Output Current Set Level

#### Standby Mode

When either adim or pdim is lower than a standby threshold level which is PDIM = 3% in PA version or  $V_{ADIM}$  = 75 mV in AA version, the CC OTA is disabled to terminate the output current regulation and CV OTA reference, V<sub>VS(REF)</sub>, is changed to V<sub>VS(REG-SB</sub>) to turn off the LED load during standby mode.

#### **SET/REF Function**

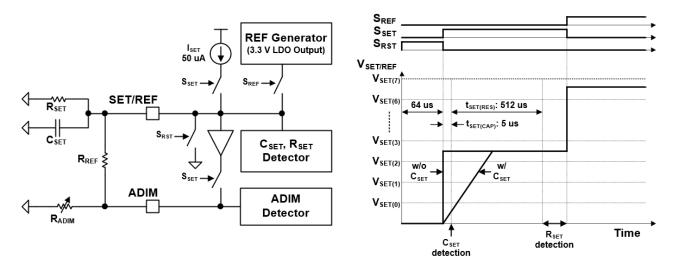

#### SET and REF Sequence

NCL38046 has a multi-functional pin, VSET/REF, for setting internal parameters and providing 3.3 V reference output for the external use.

As shown in Figure 9, V<sub>SET/REF</sub> is pulled down to 0 V for 64 µs once V<sub>DD</sub> is higher than V<sub>DD(ON)</sub>. Then, SET/REF pin is pulled up by 50  $\mu$ A I<sub>SET</sub>. If V<sub>SET/REF</sub> is lower than V<sub>SET(0)</sub> due to CSET after 5 µs tSET(CAP) delay, CSET connection is detected. If V<sub>SET/REF</sub> is higher than V<sub>SET(0)</sub>, NCL38046 decides that CSET is not connected. For CSET detection, 1.2 nF is used.

After C<sub>SET</sub> detection, NCL38046 waits for R<sub>SET</sub> detection for 512 µs tSET(RES) delay until VSET/REF level is settled to  $R_{SET} \times I_{SET}$ , then  $V_{SET/REF}$  is compared with internal references,  $V_{SET(n)}$  (n = 0 ~ 7). For R<sub>SET</sub> detection, 9.1/13/18/24/33/43/56 k $\Omega$  is used as shown in Table 1.

If SET/REF pin is open or short circuited,  $V_{SET/REF}$  will be higher than  $V_{SET(7)}$  or lower than  $V_{SET(0)}$ . In such case,  $V_{SET/REF}$  reset (S<sub>RST</sub> high period) and I<sub>SET</sub> enabling time (S<sub>SET</sub> high period) in Figure 9 are repeated and FB pin voltage is slowly pulled down to reduce the power delivery to the load until R<sub>SET</sub> is normally detected. Once  $C_{SET}$  and  $R_{SET}$  detections are completed,  $V_{SET/REF}$  is regulated to 3.3 V by internal LDO, and the 3.3 V reference voltage can be utilized for various purpose in the external circuit.

Figure 9. SET/REF Functional Block and Sequence

| R <sub>SET</sub> | K <sub>CP</sub> |

|------------------|-----------------|

| 9.1 kΩ           | 40%             |

| 13 kΩ            | 50%             |

| 18 kΩ            | 60%             |

| 24 kΩ            | 70%             |

| <b>33</b> kΩ     | 80%             |

| 43 kΩ            | 90%             |

| 56 kΩ            | 100%            |

| C <sub>SET</sub> | Dimming curve   |

| 0 nF             | Linear          |

| 1.2 nF           | Logarithmic     |

#### **REF Function**

After  $C_{SET}$  and  $R_{SET}$  detection, SET/REF pin voltage is regulated to 3.3 V. The reference voltage can be utilized to set ADIM voltage by adding  $R_{REF}$  resistor between SET/REF and ADIM pin so that ADIM voltage,  $V_{ADIM}$ , is determined by:

$$V_{ADIM}[V] = 3.3 V \cdot R_{ADIM} / (R_{REF} + R_{ADIM})$$

(eq. 4)

Variable resistor can be used for  $R_{ADIM}$  to externally adjust the maximum output current level by ADIM.

During  $I_{SET}$  enabling time (S<sub>SET</sub> high period), R<sub>REF</sub> network can affect R<sub>SET</sub> detection level. In order to monitor only R<sub>SET</sub> impedance through SET/REF pin, ADIM pin voltage is buffered same as SET/REF pin voltage and R<sub>REF</sub> impedance from SET/REF pin becomes infinite with no effect on the SET/REF voltage.

## Table 2. NCL38046 OPTION TABBLE

| P/N      | 1 <sup>st</sup><br>Letter | 2 <sup>nd</sup><br>Letter | MOD<br>Input | STBY<br>Trigger | V <sub>CS(REF-MAX)</sub> | V <sub>CS(REF-MIN)</sub> | V <sub>VS(REF-SB)</sub> | R <sub>SET</sub> func. | K <sub>CP</sub> |

|----------|---------------------------|---------------------------|--------------|-----------------|--------------------------|--------------------------|-------------------------|------------------------|-----------------|

| NCL38046 | Р                         | А                         | a1           | b1              | c2                       | d3                       | e2                      | f1                     | g22 (69%)       |

|          | А                         | А                         | a2           | b2              | c2                       | d3                       | e2                      | f1                     | g22 (69%)       |

| P/N      | 1 <sup>st</sup><br>Letter | 2 <sup>nd</sup><br>Letter | CP_sel | MOD <sub>IN(MIN)</sub> | STBY<br>Threshold | MOD <sub>IN(MAX)</sub> | MOD <sub>OUT(MIN)</sub> | Log. Curve Eq. |

|----------|---------------------------|---------------------------|--------|------------------------|-------------------|------------------------|-------------------------|----------------|

| NCL38046 | Р                         | А                         | h1     | i2                     | j2                | k2                     | 15                      | m1             |

|          | А                         | А                         | h2     | i2                     | j2                | k2                     | 15                      | m1             |

## MOD Input

| a1 | pdim |

|----|------|

| a2 | adim |

## STBY Trigger

| b1 | pdim |

|----|------|

| b2 | adim |

## V<sub>CS(REF-MAX)</sub>

| c1 | 50 mV  |

|----|--------|

| c2 | 100 mV |

| c3 | 200 mV |

| c4 | 500 mV |

## V<sub>CS(REF-MIN)</sub>

| d1 | 0%   |

|----|------|

| d2 | 0.4% |

| d3 | 1%   |

| d4 | 2%   |

## V<sub>VS(REF-SB)</sub>

| e1 | 0 V   |

|----|-------|

| e2 | 0.5 V |

| e3 | 1 V   |

| e4 | 1.5 V |

## **R<sub>SET</sub> Function**

| f1 | K <sub>CP</sub> set         |

|----|-----------------------------|

| f2 | MOD <sub>OUT(MIN)</sub> set |

## K<sub>CP</sub>

| g1 ~ g32 | 100% ~ 3% (3% step) |

|----------|---------------------|

|          |                     |

## CP dim input (dim<sub>CP</sub>)

| h1 | adim |

|----|------|

| h2 | pdim |

## MOD<sub>IN(MIN)</sub>

| 114(141114) |     |

|-------------|-----|

| i1          | 0%  |

| i2          | 10% |

#### STBY threshold

| j1 | 6% / 8%  |

|----|----------|

| j2 | 3% / 5%  |

| j3 | 2% / 3%  |

| j4 | Disabled |

## MOD<sub>IN(MAX)</sub>

| 114(111-04) |      |

|-------------|------|

| k1          | 100% |

| k2          | 90%  |

| k3          | 85%  |

| k4          | 80%  |

## MOD<sub>OUT(MIN)</sub>

| 11 | 10%  |

|----|------|

| 12 | 7.5% |

| 13 | 5%   |

| 14 | 2%   |

| 15 | 1%   |

## Logarithmic Curve Equation

| m1 | modout = modin^2 |

|----|------------------|

| m2 | modout = modin^3 |

## PCB LAYOUT GUIDANCE

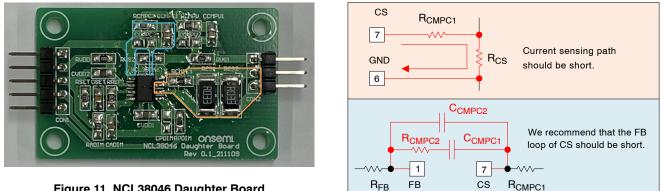

Figure 11. NCL38046 Daughter Board

Figure 12. NCL38046 Layout Guidance

# onsemi

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |  |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves<br>the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular<br>purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation<br>special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |  |  |

#### SOIC-8 NB CASE 751-07 ISSUE AK

STYLE 1: PIN 1. EMITTER COLLECTOR 2. COLLECTOR 3. 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN З. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT 6. IOUT IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. 8. CATHODE STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4. SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5. 6.

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. **MIRROR 1** STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT 2 OVI 0 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 BASE #2 З. COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE

6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK

7. VOULK 8. VIN

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 2 OF 2 |

|                  |             |                                                                                                                                                                                     |             |

SOURCE 1/DRAIN 2

7.

8. GATE 1

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights or others.

7.

8

COLLECTOR, #1

COLLECTOR, #1

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>