# onsemi

## **CrM Totem Pole PFC IC**

### Totem Pole CrM Power Factor Correction Controller

## NCP1680

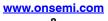

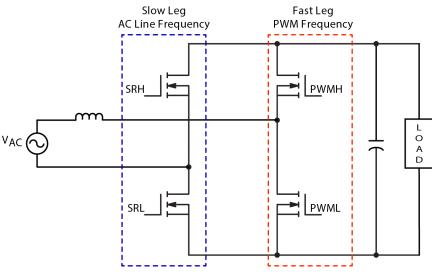

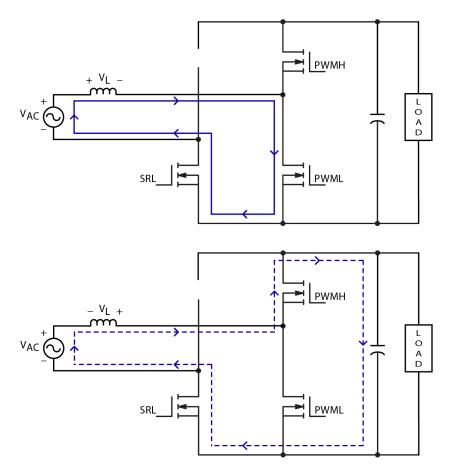

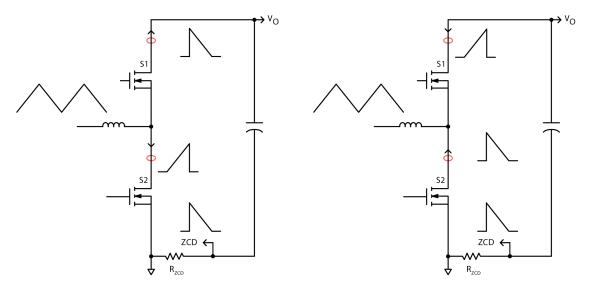

The NCP1680 is a Critical Conduction Mode (CrM) Power Factor Correction (PFC) controller IC designed to drive the bridgeless totem pole PFC topology. The bridgeless totem pole PFC consists of two totem pole legs: a fast switching leg driven at the PWM switching frequency and a second leg that operates at the AC line frequency. This topology eliminates the diode bridge present at the input of a conventional PFC circuit, allowing significant improvement in efficiency and power density.

#### Features

- Totem Pole PFC Topology Eliminates Input Diode Bridge Enabling Very High Efficiency & Compact Design

- AC Line Monitoring Circuit & AC Phase Detection

- Brownout Detection

- Critical Conduction Mode (CrM) Operation

- Discontinuous Conduction Mode (DCM) with Valley Turn On under Light Load Conditions

- Frequency Foldback in DCM with 25 kHz Minimum Frequency

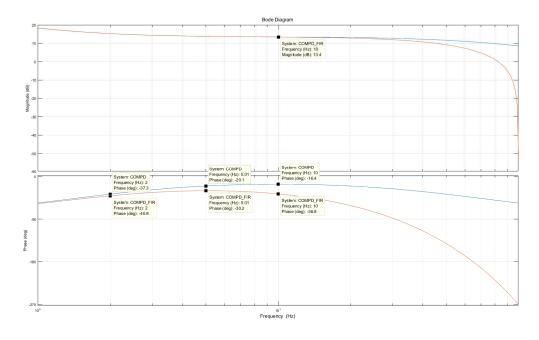

- Digital Loop Compensation

- Simplified Valley Sensing

- Novel Current Limit Scheme Eliminates the Needs for Hall Effect Sensors

- Soft Skip Mode with a Skip Flag for Optimizing Light Load Performance

- Near Unity Power Factor in All Operating Modes

- PFCOK Indicator

#### Safety Features

- Soft and Fast Overvoltage Protection

- 2-Level Latch Input for OVP & OTP

- Bulk Undervoltage Protection

- Internal Thermal Shutdown

- Cycle-by-Cycle Current Limit

#### Applications

- 5 G/Telecom Power Supplies

- Industrial Power Supplies

- Gaming Console Power Supplies

- Ultra High Density (UHD) Power Supplies

- Merchant Power

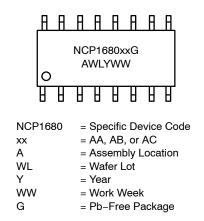

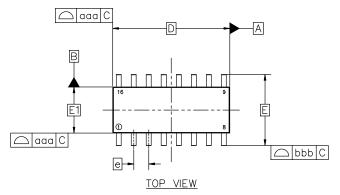

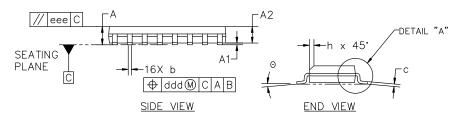

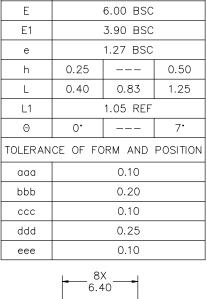

SOIC-16 CASE 751B-05

#### MARKING DIAGRAM

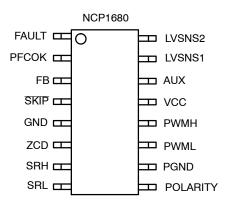

#### **PIN CONNECTIONS**

|         | NCP1680 |          |

|---------|---------|----------|

| FAULT 🚥 | 0       | LVSNS2   |

| PFCOK 📼 |         | LVSNS1   |

| FBŒ     |         | III AUX  |

| SKIP    |         |          |

| GND 🚥   |         | D PWMH   |

| ZCD 🚥   |         | PWML     |

| SRH     |         | 🞞 PGND   |

| SRL 🚥   |         | POLARITY |

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 36 of this data sheet.

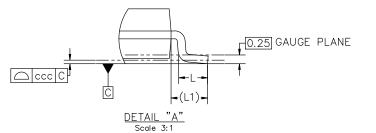

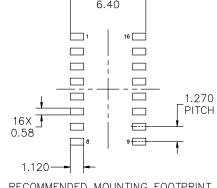

#### **DRAWING / PINOUT**

Figure 1. NCP1680 Controller Pinout

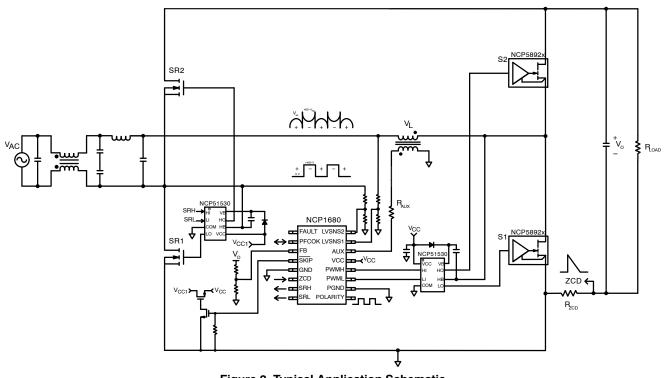

#### **TYPICAL APPLICATION SCHEMATIC**

Figure 2. Typical Application Schematic

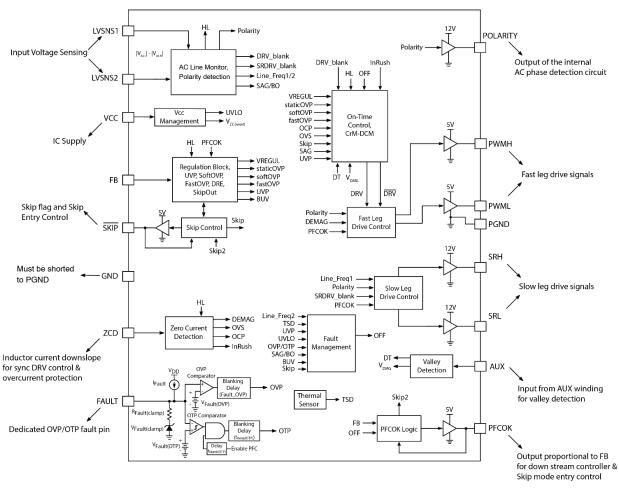

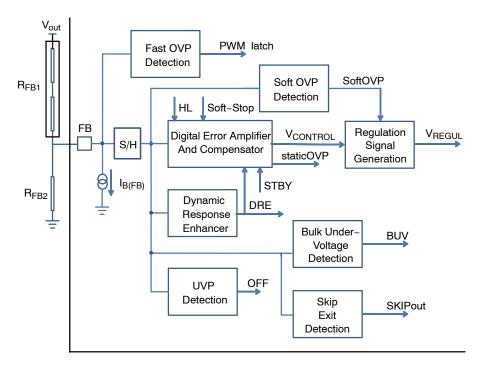

#### FUNCTIONAL BLOCK DIAGRAM

#### **PIN DESCRIPTION**

#### Table 1. PIN DESCRIPTIONS

| Pin Number | Pin Name | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

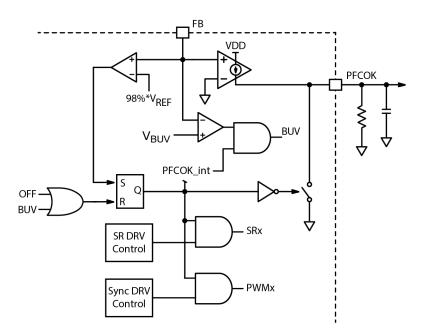

| 1          | FAULT    | Combined OVP/OTP fault pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

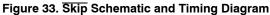

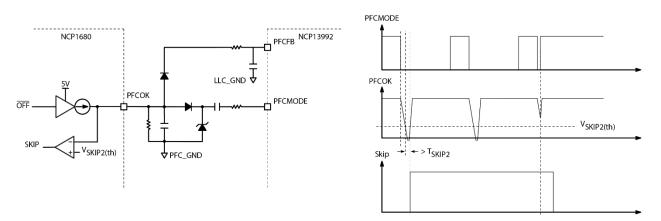

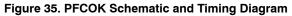

| 2          | PFCOK    | The PFCOK pin is held low when the PFC output voltage is out of regulation and during fault conditions. The pin becomes active when the PFC output achieves regulation in nominal operation, sourcing a current proportional to the feedback voltage, $V_{FB}$ . The PFCOK pin is bidirectional; it can be used to enable a downstream converter and can be used by the downstream converter to force the NCP1680 into Soft Skip Mode operation.                                       |

| 3          | FB       | This pin senses the PFC output voltage for loop regulation.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4          | Skip     | The $\overline{\text{Skip}}$ pin is a 5 V signal that goes high when the device enables PWML/H pulses. When the device enters Soft Skip Mode or is in Fault Mode, the pin will pull to GND.<br>The $\overline{\text{Skip}}$ pin is bidirectional; it can be used to enable/disable peripheral circuitry, reducing I <sub>CC</sub> consumption in Soft Skip Mode. The pin can also be used to force the NCP1680 into skip mode by externally grounding the pin for at least 56 $\mu$ s. |

| 5          | GND      | GND pin should be shorted to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6          | ZCD      | The pin senses the inductor current downslope. It is used to detect demagnetization and turn-off the (1–D) switch. Current limit is also based on the signal on this pin. Use of a low inductance current sensing resistor is recommended.                                                                                                                                                                                                                                             |

| 7          | SRH      | Control signal for high side slow leg device.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 1. PIN DESCRIPTIONS (continued)

| Pin Number | Pin Name | Function                                                                                                                                             |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8          | SRL      | Control signal for low side slow leg device.                                                                                                         |

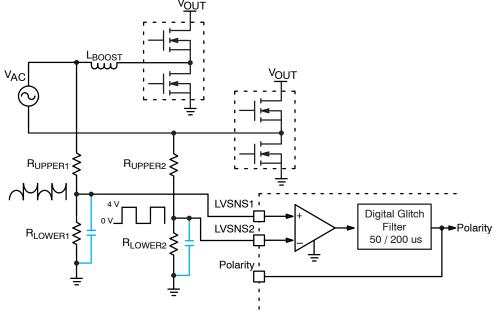

| 9          | POLARITY | Output of the internal AC polarity detection circuit.                                                                                                |

| 10         | PGND     | Power ground reference.                                                                                                                              |

| 11         | PWML     | PWM logic level output for control of low side fast leg switch.                                                                                      |

| 12         | PWMH     | PWM logic level output for control of high side fast leg switch.                                                                                     |

| 13         | VCC      | IC supply pin.                                                                                                                                       |

| 14         | AUX      | The pin is used to monitor the switch node resonance on the auxiliary winding and enable valley turn-on during CrM and frequency foldback operation. |

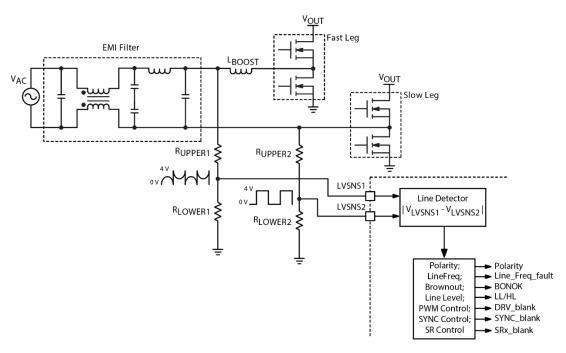

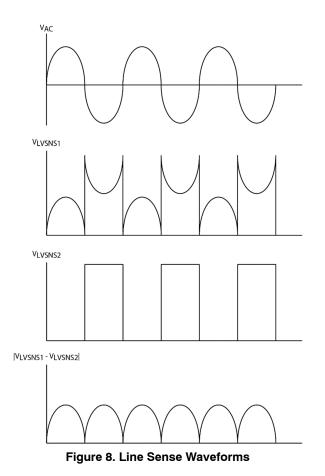

| 15         | LVSNS1   | Low voltage input for AC line voltage monitoring. LVSNS1 resistor divider should be connected to AC line side of the boost inductor.                 |

| 16         | LVSNS2   | Low voltage input for AC line voltage monitoring. LVSNS2 resistor divider should be connected to the neutral of the AC line voltage.                 |

#### Table 2. MAXIMUM RATINGS

| Rating                                                                                                                                                                                            | Pin                                      | Symbol                                                     | Value                | Unit       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------|----------------------|------------|

| Supply Input Voltage, V <sub>CC</sub> Pin                                                                                                                                                         | VCC                                      | V <sub>CC(MAX)</sub>                                       | –0.3 to 30           | V          |

| PWML Pin Maximum Voltage                                                                                                                                                                          | PWML                                     | V <sub>PWML(MAX)</sub>                                     | -0.3 to 5.5          | V          |

| PWML Pin Maximum Current                                                                                                                                                                          | PWML                                     | I <sub>PWML(SRC_MAX)</sub><br>I <sub>PWML(SNK_MAX)</sub>   | -100<br>+160         | mA         |

| PWMH Pin Maximum Voltage                                                                                                                                                                          | PWMH                                     | V <sub>PWMH(MAX)</sub>                                     | –0.3 to 5.5          | V          |

| PWMH Pin Maximum Current                                                                                                                                                                          | PWMH                                     | I <sub>PWMH</sub> (SRC_MAX)<br>I <sub>PWMH</sub> (SNK_MAX) | -100<br>+160         | mA         |

| SRx, Polarity Pin Maximum Voltage                                                                                                                                                                 | SRL, SRH,<br>Polarity                    | V <sub>SRx(MAX)</sub>                                      | –0.3 to 14           | V          |

| SRx, Polarity Pin Maximum Current                                                                                                                                                                 | SRL, SRH,<br>Polarity                    | I <sub>SRx(SRC_MAX)</sub><br>I <sub>SRx(SNK_MAX)</sub>     | -100<br>+160         | mA         |

| AUX Pin Input Voltage                                                                                                                                                                             | AUX                                      | V <sub>AUX</sub>                                           | -0.3 to 5.5 (Note 1) | V          |

| AUX Pin Input Current                                                                                                                                                                             | AUX                                      | I <sub>AUX</sub>                                           | -2 / +5              | mA         |

| ZCD Pin Input Voltage Range                                                                                                                                                                       | ZCD                                      | V <sub>ZCD</sub>                                           | -0.3 to 5.5 (Note 1) | V          |

| ZCD Pin Maximum Current                                                                                                                                                                           | ZCD                                      | I <sub>ZCD(MAX)</sub>                                      | -2 / +5              | mA         |

| Maximum Input Voltage Other Pins                                                                                                                                                                  | LVSNS1,<br>LVSNS2,<br>Skip, FB,<br>FAULT | V <sub>MAX</sub>                                           | -0.3 to 5.5 (Note 1) | V          |

| Maximum Current Other Pins                                                                                                                                                                        | LVSNS1,<br>LVSNS2,<br>Skip, FB,<br>FAULT | I <sub>MAX</sub>                                           | -2 to +5             | mA         |

| Power Dissipation and Thermal Characteristics<br>Maximum Power Dissipation at T <sub>A</sub> = 70°C<br>Thermal Resistance Junction-to-Air<br>(1 Oz Cu, 0.155 Sq Inch Printed Circuit Copper Clad) |                                          | P <sub>D</sub><br>R <sub>θJA</sub>                         | 550<br>145           | mW<br>°C/W |

| Maximum Junction Temperature                                                                                                                                                                      |                                          | T <sub>J(MAX)</sub>                                        | 150                  | °C         |

| Operating Temperature Range                                                                                                                                                                       |                                          | · · ·                                                      | -40 to +125          | °C         |

| Storage Temperature Range                                                                                                                                                                         |                                          |                                                            | -60 to +150          | °C         |

#### Table 2. MAXIMUM RATINGS (continued)

| Rating                             | Pin | Symbol | Value | Unit |

|------------------------------------|-----|--------|-------|------|

| ESD Capability, HBM Model (Note 2) |     |        | 3.5   | kV   |

| ESD Capability, CDM Model (Note 2) |     |        | 1.25  | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. This level is low enough to guarantee not to exceed the internal ESD diode and 5.5 V ZENER diode. More positive and negative voltages can be applied if the pin current stays within the -2 mA / +5 mA range.

2. This device contains ESD protection and exceeds the following tests: Human Body Model 3500 V per JEDEC Standard JESD22–A114E, Charged Device Model 1250 V per JEDEC Standard JESD22–C101E.

3. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

#### Table 3. ELECTRICAL CHARACTERISTICS

$(V_{CC} = 12 \text{ V}, V_{LVSNS1} = 1.2 \text{ V}, V_{LVSNS2} = 0 \text{ V}, V_{FB} = 2.4 \text{ V}, V_{FAULT} = \text{open}, C_{POLARITY} = 100 \text{ pF}, V_{AUX} = 0 \text{ V}, V_{ZCD} = 0 \text{ V}, C_{VCC} = 100 \text{ nF}, C_{SRL} = C_{SRH} = 100 \text{ pF}, C_{PWML} = C_{PWMH} = 100 \text{ pF}, \text{ for typical values } T_J = 25^{\circ}\text{C}, \text{ for min/max values, } T_J \text{ is } -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted})$

| Characteristics                                                          | Conditions                 | Symbol                 | Min  | Тур  | Max   | Unit |

|--------------------------------------------------------------------------|----------------------------|------------------------|------|------|-------|------|

| START-UP & SUPPLY CIRCUITS                                               |                            | -                      |      |      |       |      |

| Supply Voltage                                                           |                            |                        |      |      |       | V    |

| Startup Threshold                                                        | V <sub>CC</sub> increasing | V <sub>CC(on)</sub>    | 9.75 | 10.5 | 11.25 |      |

| Minimum Operating Voltage                                                | V <sub>CC</sub> decreasing | V <sub>CC(off)</sub>   | 8.2  | 8.8  | 9.4   |      |

| V <sub>CC</sub> Hysteresis (V <sub>CC(on)</sub> – V <sub>CC(off)</sub> ) | V <sub>CC</sub> decreasing | V <sub>CC(HYS)</sub>   | 1.2  | 1.7  | -     |      |

| Internal Latch / Logic Reset Level                                       | V <sub>CC</sub> decreasing | V <sub>CC(reset)</sub> | 2.5  | 4    | 6     |      |

| Supply Voltage                                                           |                            |                        |      |      |       | mA   |

| Before Startup                                                           | $V_{CC} = 9.5 V$           | I <sub>CC1</sub>       | -    | 1.8  | 2.2   |      |

| Fault or Latch                                                           | V <sub>FLT</sub> = 0 V     | I <sub>CC2</sub>       | -    | 1.8  | 2.2   |      |

| Operational, Switching at 100 kHz                                        | All DRVs Open              | I <sub>CC3</sub>       | -    | 3.3  | 4     |      |

| Operational, Skipping                                                    | V <sub>PFCOK</sub> = 0 V   | I <sub>CC4</sub>       | -    | 0.54 | 0.9   |      |

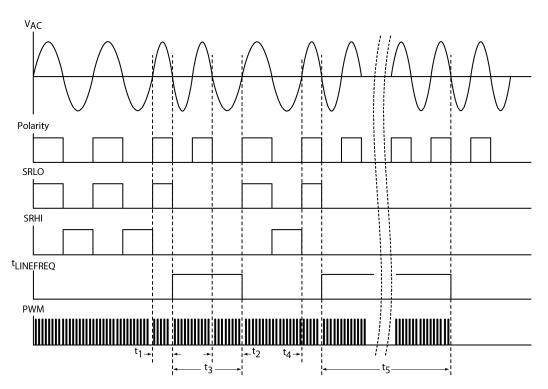

#### AC ZERO CROSSING MANAGEMENT

| Recommended External Divider<br>Ratio                                       |                                                                                                                                                                                                           | K <sub>L_DIV</sub>                                           | -          | 100                                | -        |    |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------|------------------------------------|----------|----|

| Main PWM Drive Control                                                      |                                                                                                                                                                                                           | 4                                                            |            |                                    |          |    |

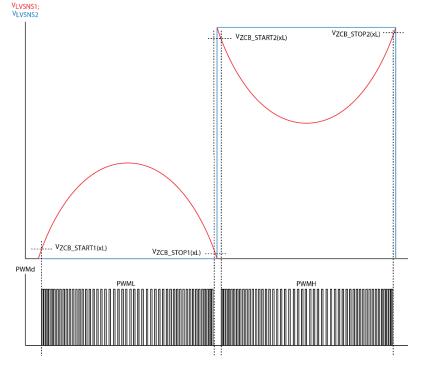

| PWM Zero Crossing Blanking<br>Thresholds<br>Threshold to Stop PWML/H Pulses | V <sub>ZCB_STOP</sub> =  V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>  <br>V <sub>LVSNS1</sub> Decreasing, V <sub>LVSNS2</sub> = 0 V<br>V <sub>LVSNS1</sub> Increasing, V <sub>LVSNS2</sub> = 4 V            | Vzcb_stop1(LL)<br>Vzcb_stop2(LL)                             |            | 100                                |          | mV |

| Threshold to Start PWML/H Pulses                                            | V <sub>ZCB_START</sub> =  V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>  <br>V <sub>LVSNS1</sub> Increasing, V <sub>LVSNS2</sub> = 0 V<br>V <sub>LVSNS1</sub> Decreasing, V <sub>LVSNS2</sub> = 4 V           | V <sub>ZCB_</sub> START1(LL)<br>V <sub>ZCB_</sub> START2(LL) |            | V <sub>ZCB_STOPx(LL)</sub> +<br>20 |          |    |

| Zero Crossing Blanking Filter<br>NCP1680AA, AB:<br>NCP1680AC:               |                                                                                                                                                                                                           | <sup>†</sup> FILT(ZCB)                                       | -          | 20<br>Disabled                     | 25       | μs |

| Polarity Detection Control                                                  |                                                                                                                                                                                                           |                                                              |            |                                    |          |    |

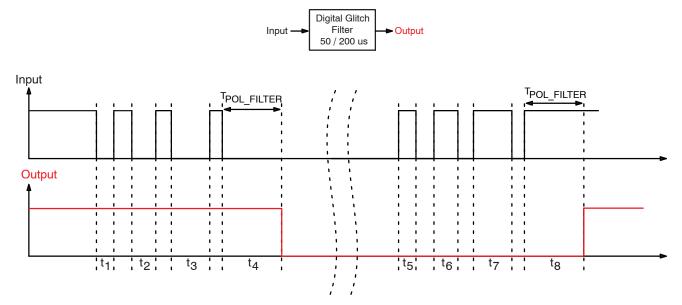

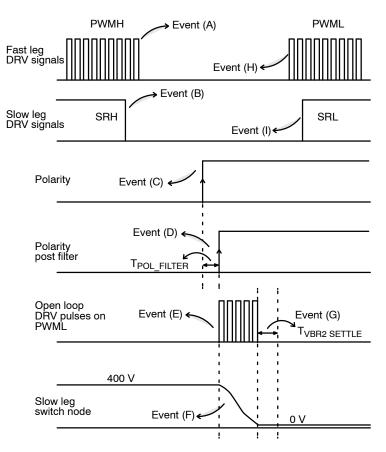

| Polarity Detection Filter<br>NCP1680AA, AB:<br>NCP1680AC:                   |                                                                                                                                                                                                           | <sup>t</sup> POL_FILTER                                      | _          | 200<br>50                          |          | μs |

| Polarity Detection Threshold                                                | $\label{eq:VPOL_DETx} \begin{array}{l} V_{POL\_DETx} = V_{LVSNS1} - V_{LVSNS2} \\ V_{LVSNS1} \mbox{ Decreasing}, \ V_{LVSNS2} = 0 \ V \\ V_{LVSNS1} \mbox{ Increasing}, \ V_{LVSNS2} = 4 \ V \end{array}$ | V <sub>POL_DET1</sub><br>V <sub>POL_DET2</sub>               | -55<br>-20 | -15<br>15                          | 20<br>55 | mV |

Table 3. ELECTRICAL CHARACTERISTICS (continued) ( $V_{CC} = 12 V$ ,  $V_{LVSNS1} = 1.2 V$ ,  $V_{LVSNS2} = 0 V$ ,  $V_{FB} = 2.4 V$ ,  $V_{FAULT} = 0$  pen,  $C_{POLARITY} = 100 pF$ ,  $V_{AUX} = 0 V$ ,  $V_{ZCD} = 0 V$ ,  $C_{VCC} = 100 nF$ ,  $C_{SRL} = C_{SRH} = 100 pF$ ,  $C_{PWML} = C_{PWMH} = 100 pF$ , for typical values  $T_J = 25^{\circ}C$ , for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                       | Conditions                                                                                                                                                                                           | Symbol                                                       | Min  | Тур                               | Max  | Uni |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----------------------------------|------|-----|

| AC ZERO CROSSING MANAGEME                             | NT                                                                                                                                                                                                   |                                                              |      |                                   |      |     |

| Slow Leg (SR) Drive Control                           |                                                                                                                                                                                                      |                                                              |      |                                   |      |     |

| Slow Leg Zero Crossing Blanking<br>Thresholds         |                                                                                                                                                                                                      |                                                              |      |                                   |      | mV  |

| Threshold to Stop SRx Pulses                          | $ \begin{array}{l} V_{SR\_STOP} =  V_{LVSNS1} - V_{LVSNS2}  \\ V_{LVSNS1} \mbox{ Decreasing}, V_{LVSNS2} = 0 \ V \\ V_{LVSNS1} \mbox{ Increasing}, V_{LVSNS2} = 4 \ V \end{array} $                  | Vsr_stop1(LL)<br>Vsr_stop2(LL)                               |      | 180                               |      |     |

| Threshold to Start SRx Pulses                         | V <sub>SR_START</sub> =  V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>  <br>V <sub>LVSNS1</sub> Increasing, V <sub>LVSNS2</sub> = 0 V<br>V <sub>LVSNS1</sub> Decreasing, V <sub>LVSNS2</sub> = 4 V       | V <sub>SR_START1(LL)</sub><br>V <sub>SR_START2(LL)</sub>     |      | V <sub>SR_STOPx(LL)</sub> +<br>20 |      |     |

| Synchronous (1 – d) Drive<br>Control                  |                                                                                                                                                                                                      |                                                              |      |                                   |      |     |

| Sync Zero Crossing Blanking<br>Thresholds             |                                                                                                                                                                                                      |                                                              |      |                                   |      | mV  |

| Threshold to Stop Sync Pulses                         | $ \begin{array}{l} V_{SYNC\_STOP} = \left  V_{LVSNS1} - V_{LVSNS2} \right  \\ V_{LVSNS1} \mbox{ Decreasing, } V_{LVSNS2} = 0 \ V \\ V_{LVSNS1} \mbox{ Increasing, } V_{LVSNS2} = 4 \ V \end{array} $ | VSYNC_STOP1(LL)<br>VSYNC_STOP2(LL)                           |      | 200                               |      |     |

| Threshold to Start Sync Pulses                        | $ \begin{array}{l} V_{SYNC\_START} =  V_{LVSNS1} - V_{LVSNS2}  \\ V_{LVSNS1} \text{ Increasing}, V_{LVSNS2} = 0 \ V \\ V_{LVSNS1} \text{ Decreasing}, V_{LVSNS2} = 4 \ V \end{array} $               | V <sub>SYNC_START1(LL)</sub><br>V <sub>SYNC_START2(LL)</sub> |      | V <sub>SYNC_STOPx(LL)</sub> + 20  |      |     |

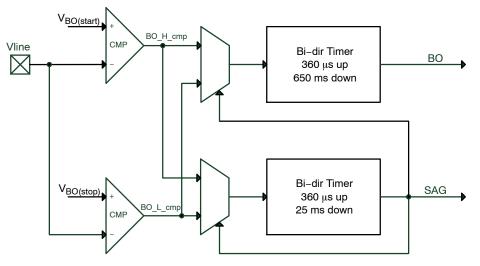

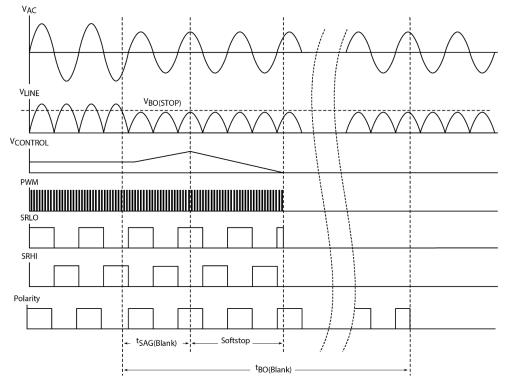

| BROWN-OUT, LINE SAG AND LINE                          | E RANGE DETECTION                                                                                                                                                                                    |                                                              |      |                                   |      |     |

| Line Sag and Brown–Out Detection<br>Upper Threshold   | $ V_{LVSNS1} - V_{LVSNS2} $ Increasing                                                                                                                                                               | V <sub>BO(START)</sub>                                       | 1.02 | 1.10                              | 1.18 | V   |

| Line Sag and Brown–Out Detection<br>Lower Threshold   | V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>   Decreasing                                                                                                                                               | V <sub>BO(STOP)</sub>                                        | 0.92 | 1.00                              | 1.08 | V   |

| Brown–Out Detection Hysteresis                        | V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>   Increasing                                                                                                                                               | V <sub>BO(HYS)</sub>                                         | 60   | 100                               |      | m۷  |

| Line Sag Detection Blanking Timer                     | V <sub>LVSNS1</sub> − V <sub>LVSNS2</sub>   < V <sub>BO(STOP),</sub><br>Delay to Soft Stop Enable                                                                                                    | t <sub>SAG(blank)</sub>                                      | 20   | 25                                | 30   | ms  |

| Brown–Out Detection Blanking<br>Timer                 | ∣V <sub>LVSNS1</sub> – V <sub>LVSNS2</sub> ∣ Decreasing,<br>Delay to Polarity Disable                                                                                                                | t <sub>BO(blank)</sub>                                       | 520  | 650                               | 780  | ms  |

| High–Line Level Detection<br>Threshold                | $ V_{LVSNS1} - V_{LVSNS2} $ Increasing                                                                                                                                                               | V <sub>HL</sub>                                              | 2.20 | 2.36                              | 2.52 | V   |

| Low–Line Level Detection<br>Threshold                 | V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>   Decreasing                                                                                                                                               | V <sub>LL</sub>                                              | 2.07 | 2.22                              | 2.37 | V   |

| Line Range Select Hysteresis                          | V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>   Increasing                                                                                                                                               | V <sub>LR(HYS)</sub>                                         | 100  | 140                               |      | m۷  |

| High to Low Line Mode Selector<br>Timer               | $ V_{LVSNS1} - V_{LVSNS2}  < V_{LL}$                                                                                                                                                                 | t <sub>blank</sub> (LL)                                      | 20   | 25                                | 30   | ms  |

| Low to High Line Mode Selector<br>Timer Filter        | V <sub>LVSNS1</sub> - V <sub>LVSNS2</sub>   > V <sub>HL</sub>                                                                                                                                        | <sup>t</sup> filter(HV)                                      | 200  | 300                               | 400  | μs  |

| Lockout Timer for Low to High Line<br>Mode Transition | Low Line Mode,<br> V <sub>LVSNS1</sub> – V <sub>LVSNS2</sub>   > V <sub>HL</sub>                                                                                                                     | t <sub>line(lockout)</sub>                                   | 400  | 500                               | 600  | ms  |

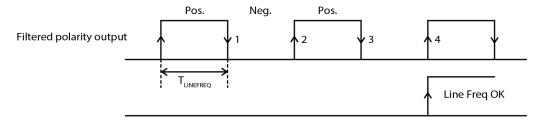

| AC LINE FREQUENCY MONITORIN                           | G                                                                                                                                                                                                    | •                                                            |      | •                                 |      | •   |

| Line Frequency Upper Threshold                        |                                                                                                                                                                                                      | t <sub>LINE(65)</sub>                                        | 66   | 72                                | 78   | Hz  |

| Line Frequency Lower Threshold                        |                                                                                                                                                                                                      | tune(45)                                                     | 37   | 41                                | 45   | Hz  |

Line Frequency Lower Threshold 37 41 45 Ηz t<sub>LINE(45)</sub> **Device Enable Counter** 4 N<sub>DRV\_EN</sub> 1 Slow Leg Disable Counter N<sub>SR</sub> DIS

Table 3. ELECTRICAL CHARACTERISTICS (continued) ( $V_{CC} = 12 \text{ V}, V_{LVSNS1} = 1.2 \text{ V}, V_{LVSNS2} = 0 \text{ V}, V_{FB} = 2.4 \text{ V}, V_{FAULT} = \text{open}, C_{POLARITY} = 100 \text{ pF}, V_{AUX} = 0 \text{ V}, V_{ZCD} = 0 \text{ V}, C_{VCC} = 100 \text{ nF}, C_{SRL} = C_{SRH} = 100 \text{ pF}, C_{PWML} = C_{PWMH} = 100 \text{ pF}, \text{ for typical values } T_J = 25^{\circ}\text{C}, \text{ for min/max values}, T_J \text{ is } -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted}$

| Characteristics                                                               | Conditions                                                                                                                     | Symbol                                                        | Min       | Тур        | Мах        | Unit |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|------------|------------|------|

| AC LINE FREQUENCY MONITORIN                                                   | G                                                                                                                              |                                                               |           |            |            |      |

| Line Frequency2 Timer                                                         | Delay to PWM Disable                                                                                                           | t <sub>LINEFREQ(DLY)</sub>                                    | 60        | 100        | 165        | ms   |

| VALLEY DETECTION CIRCUIT                                                      | •                                                                                                                              |                                                               |           |            | •          |      |

| Valley Detection Thresholds in<br>Positive Half Line Cycle                    | V <sub>LVSNS1</sub> = 1.2 V, V <sub>LVSNS2</sub> = 0 V,<br>V <sub>AUX</sub> Rising (Arm)<br>V <sub>AUX</sub> Falling (Trigger) | VVD1_TH(rising)<br>VVD1_TH(falling)                           | 150<br>50 | 200<br>100 | 250<br>150 | mV   |

| Valley Detection Hysteresis in<br>Positive Half Line Cycle                    |                                                                                                                                | V <sub>VD1(HYS)</sub>                                         | 50        | 100        |            | mV   |

| Propagation Delay of Valley<br>Detection in Positive Half Line<br>Cycle       | Step V <sub>AUX</sub> 1.5 V to -0.2 V,<br>Time to PWML = 2.5 V                                                                 | T <sub>VD1</sub>                                              |           | 50         | 80         | ns   |

| Valley Detection Thresholds in<br>Negative Half Line Cycle                    | V <sub>LVSNS1</sub> = 0 V, V <sub>LVSNS2</sub> = 1.2 V,<br>V <sub>AUX</sub> Falling (Arm)<br>V <sub>AUX</sub> Rising (Trigger) | V <sub>VD2_</sub> TH(falling)<br>V <sub>VD2_</sub> TH(rising) | 50<br>150 | 100<br>200 | 150<br>250 | mV   |

| Valley Detection Hysteresis in<br>Negative Half Line Cycle                    |                                                                                                                                | V <sub>VD2(HYS)</sub>                                         | 50        | 100        |            | mV   |

| Propagation Delay of Valley<br>Detection in Negative Half Line<br>Cycle       | Step V <sub>AUX</sub> 0 V to 1.5 V,<br>Time to PWMH = 2.5 V                                                                    | T <sub>VD2</sub>                                              |           | 45         | 75         | ns   |

| Minimum AUX Pulse Width                                                       |                                                                                                                                | T <sub>SYNC</sub>                                             |           | 95         | 155        | ns   |

| AUX Pin Bias Current,<br>V <sub>AUX</sub> = V <sub>VD1_TH(rising)</sub>       |                                                                                                                                | I <sub>AUX(bias1)</sub>                                       | 0.5       | 1          | 2          | μΑ   |

| AUX Pin Bias Current,<br>V <sub>AUX</sub> = V <sub>VD1_TH(falling)</sub>      |                                                                                                                                | I <sub>AUX(bias2)</sub>                                       | 0.5       | 1          | 2          | μA   |

| FAST LEG DRIVE SIGNALS (PWML                                                  | . & PWMH)                                                                                                                      | •                                                             |           |            |            |      |

| PWMx Rise Time,<br>x = L, H                                                   | $V_{PWMx}$ = 10% to 90% of 5 V,<br>$C_{PWMx}$ = 1 nF                                                                           | T <sub>PWMx(rise)</sub>                                       |           | 95         |            | ns   |

| PWMx Fall Time                                                                | $V_{PWMx}$ = 90% to 10% of 5 V,<br>$C_{PWMx}$ = 1 nF                                                                           | T <sub>PWMx(fall)</sub>                                       |           | 30         |            | ns   |

| Source Resistance                                                             |                                                                                                                                | ROH                                                           | -         | 15         | 25         | Ω    |

| Sink Resistance                                                               |                                                                                                                                | ROL                                                           | -         | 5          | 10         | Ω    |

| Peak Source Current<br>(Guaranteed by Design)                                 | V <sub>PWMx</sub> = 0 V                                                                                                        | I <sub>PWMx(SRC)</sub>                                        |           | 100        |            | mA   |

| Peak Sink Current<br>(Guaranteed by Design)                                   | V <sub>PWMx</sub> = 5 V                                                                                                        | I <sub>PWMx(SNK)</sub>                                        |           | 160        |            | mA   |

| PWMx Clamp Voltage                                                            | R <sub>PWMx</sub> = 10 kΩ                                                                                                      | V <sub>PWMx(high)</sub>                                       | 4.5       | 5          | 5.5        | V    |

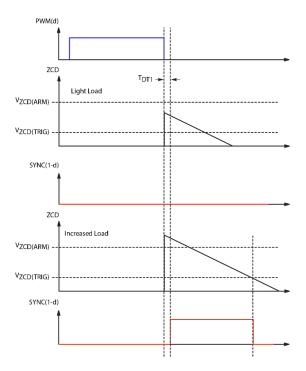

| Non-overlap Time between Falling<br>Edge of PWMd & Rising Edge of<br>PWM(1-d) | V <sub>ZCD</sub> = 0.5 V                                                                                                       | T <sub>DT1</sub>                                              | 90        | 130        | 170        | ns   |

| SLOW LEG DRIVE SIGNALS (SRL                                                   | & SRH)                                                                                                                         | -                                                             | - I       |            | •          | -    |

| SRx Rise Time<br>x = L, H                                                     | $V_{PWMSRx}$ = 10% to 90% of 12 V<br>$C_{PWMSRx}$ = 1 nF                                                                       | T <sub>PWMSRx(rise)</sub>                                     |           | 185        |            | ns   |

| SRx Fall Time                                                                 | V <sub>PWMSRx</sub> = 90% to 10% of 12 V<br>C <sub>PWMSRx</sub> = 1 nF                                                         | T <sub>PWMSRx(fall)</sub>                                     |           | 125        |            | ns   |

| Course Desistance                                                             |                                                                                                                                | ROH2                                                          | _         | 45         | 85         | Ω    |

| Source Resistance                                                             |                                                                                                                                |                                                               |           |            | 00         |      |

Table 3. ELECTRICAL CHARACTERISTICS (continued) ( $V_{CC} = 12 V$ ,  $V_{LVSNS1} = 1.2 V$ ,  $V_{LVSNS2} = 0 V$ ,  $V_{FB} = 2.4 V$ ,  $V_{FAULT} = 0$  pen,  $C_{POLARITY} = 100 pF$ ,  $V_{AUX} = 0 V$ ,  $V_{ZCD} = 0 V$ ,  $C_{VCC} = 100 nF$ ,  $C_{SRL} = C_{SRH} = 100 pF$ ,  $C_{PWML} = C_{PWMH} = 100 pF$ , for typical values  $T_J = 25^{\circ}C$ , for min/max values,  $T_J$  is -40°C to 125°C, unless otherwise noted)

| Characteristics                                   | Conditions                                                                                                 | Symbol                       | Min | Тур | Max | Unit |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------|-----|-----|-----|------|

| SLOW LEG DRIVE SIGNALS (SRL                       | & SRH)                                                                                                     | •                            |     |     |     |      |

| SRx Peak Source Current<br>(Guaranteed by Design) | V <sub>PWMSRx</sub> = 0 V                                                                                  | I <sub>PWMSRx(SRC)</sub>     |     | 100 |     | mA   |

| SRx Peak Sink Current<br>(Guaranteed by Design)   | V <sub>PWMSRx</sub> = 12 V                                                                                 | I <sub>PWMSRx</sub> (SNK)    |     | 160 |     | mA   |

| SRx Clamp Voltage                                 | $R_{PWMSRx}$ = 10 k $\Omega$ , $V_{CC}$ = 30 V                                                             | V <sub>PWMSRx(high)</sub>    | 10  | 12  | 14  | V    |

| SRx Minimum Drive Voltage                         | $\begin{array}{l} R_{PWMSRx} = 10 \ \text{k}\Omega, \\ V_{CC} = V_{CC(off)} + 100 \ \text{mV} \end{array}$ | V <sub>PWMSRx(MIN)</sub>     | 7.8 | 9   |     | V    |

| POLARITY OUTPUT                                   |                                                                                                            |                              |     |     |     |      |

| POLARITY Rise Time                                | $V_{POLARITY}$ = 10% to 90% of 12 V,<br>$C_{POLARITY}$ = 1 nF                                              | T <sub>POLARITY</sub> (rise) |     | 185 |     | ns   |

| POLARITY Fall Time                                | V <sub>POLARITY</sub> = 10% to 90% of 12 V,<br>C <sub>POLARITY</sub> = 1 nF                                | T <sub>POLARITY(fall)</sub>  |     | 125 |     | ns   |

| Source Resistance                                 |                                                                                                            | ROH3                         | -   | 45  | 85  | Ω    |

| Sink Resistance                                   |                                                                                                            | ROL3                         | -   | 30  | 60  | Ω    |

| POLARITY Peak Source Current                      | VPOLADITY = 0 V                                                                                            |                              |     | 100 |     | mA   |

| POLARITY Rise Time                                     | V <sub>POLARITY</sub> = 10% to 90% of 12 V,<br>C <sub>POLARITY</sub> = 1 nF                                                    | T <sub>POLARITY(rise)</sub> |     | 185 |    | ns |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|----|----|

| POLARITY Fall Time                                     | V <sub>POLARITY</sub> = 10% to 90% of 12 V,<br>C <sub>POLARITY</sub> = 1 nF                                                    | T <sub>POLARITY(fall)</sub> |     | 125 |    | ns |

| Source Resistance                                      |                                                                                                                                | ROH3                        | -   | 45  | 85 | Ω  |

| Sink Resistance                                        |                                                                                                                                | ROL3                        | -   | 30  | 60 | Ω  |

| POLARITY Peak Source Current<br>(Guaranteed by Design) | V <sub>POLARITY</sub> = 0 V                                                                                                    | I <sub>POLARITY</sub> (SRC) |     | 100 |    | mA |

| POLARITY Peak Sink Current<br>(Guaranteed by Design)   | V <sub>POLARITY</sub> = 12 V                                                                                                   | I <sub>POLARITY</sub> (SNK) |     | 160 |    | mA |

| POLARITY Clamp Voltage                                 | R <sub>POLARITY</sub> = 10 kΩ<br>V <sub>CC</sub> = 30 V                                                                        | VPOLARITY(high)             | 10  | 12  | 14 | V  |

| POLARITY Minimum Drive Voltage                         | $\begin{array}{l} R_{\text{POLARITY}} = 10 \text{ k}\Omega \\ V_{\text{CC}} = V_{\text{CC(off)}} + 100 \text{ mV} \end{array}$ | Vpolarity(MIN)              | 7.8 | 9   |    | V  |

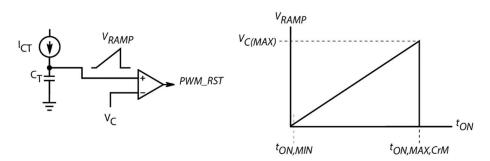

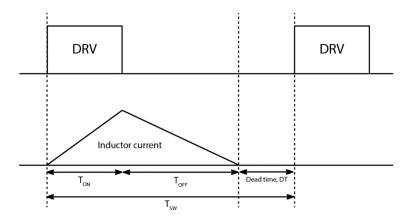

#### **ON TIME MODULATION CIRCUIT**

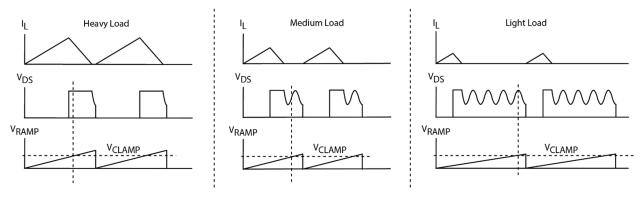

| V <sub>FB</sub> < V <sub>REF,</sub><br>V <sub>LVSNS1</sub> = 1.20 V, V <sub>LVSNS2</sub> = 0 V | T <sub>on, max, Cr</sub> M                                                                                | 15.5<br>9                                                                                                                                                                           | 17.2<br>10.2                                                                                                                                                                                                                                                                          | 18.9<br>11.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                | F <sub>clamp1</sub>                                                                                       |                                                                                                                                                                                     | 130<br>275                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Low Line<br>High Line<br>Low Line<br>High Line                                                 | ( <sup>t</sup> on_ff)ll<br>( <sup>t</sup> on_ff)hl                                                        |                                                                                                                                                                                     | 3.84<br>1.92<br>1.82<br>0.91                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                | F <sub>MIN</sub>                                                                                          | 25                                                                                                                                                                                  | 30.5                                                                                                                                                                                                                                                                                  | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{FB} > V_{REF}, C_{PWMx} = Open$                                                            | T <sub>on, min</sub>                                                                                      | 200                                                                                                                                                                                 | 260                                                                                                                                                                                                                                                                                   | 320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                | T <sub>on, max, DCM</sub>                                                                                 |                                                                                                                                                                                     | 20<br>12.7                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                | V <sub>LVSNS1</sub> = 1.20 V, V <sub>LVSNS2</sub> = 0 V<br>Low Line<br>High Line<br>Low Line<br>High Line | VLVSNS1 = 1.20 V, VLVSNS2 = 0 V         Fclamp1         Fclamp1         Low Line         High Line         Low Line         High Line         FMIN         VFB > VREF, CPWMx = Open | $V_{LVSNS1} = 1.20 \text{ V}, V_{LVSNS2} = 0 \text{ V}$ 15.5<br>9 $F_{clamp1}$ $F_{clamp1}$ $Low Line$<br>High Line $\begin{pmatrix} (t_{ON}_{FF})LL \\ (t_{ON}_{FF})HL \end{pmatrix} \\ Low Line High LineLow LineHigh LineF_{MIN}25V_{FB} > V_{REF}, C_{PWMx} = OpenT_{on, min}200$ | $V_{LVSNS1} = 1.20 \text{ V}, V_{LVSNS2} = 0 \text{ V}$ 15.5       17.2 $P_{Clamp1}$ $P_{Clamp1}$ 130 $F_{clamp1}$ $P_{Clamp1}$ 130 $Low Line$ $(t_{ON_FF})LL$ $P_{Clamp1}$ $High Line$ $P_{Clamp1}$ $P_{Clamp1}$ $Low Line$ $P_{Clamp1}$ $P_{Clamp1}$ $High Line$ $P_{Clamp1}$ $P_{Clamp1}$ $Low Line$ $P_{Clamp1}$ $P_{Clamp1}$ $High Line$ $P_{Clamp1}$ $P_{Clamp1}$ $Low Line$ $P_{Clamp1}$ $P_{Clamp1}$ $High Line$ $P_{Clamp1}$ $P_{Clamp1}$ $V_{FB} > V_{REF, CPWMx} = Open$ $P_{On, min}$ $P_{Clamp1}$ $V_{FB} > V_{REF, CPWMx} = Open$ $P_{On, max, DCM}$ $P_{Clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ | $V_{LVSNS1} = 1.20 V, V_{LVSNS2} = 0 V$ 15.5       17.2       18.9 $P_{Clamp1}$ $P_{Clamp1}$ 10.2       11.4 $F_{clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ 130       11.4 $Low Line$ $P_{Clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ $P_{Clamp1}$ 130       11.4 $Low Line$ $P_{Clamp1}$ |

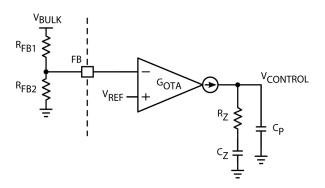

#### Feedback Voltage Reference: $V_{\mathsf{REF}}$ ٧ @ 25°C 2.475 2.50 2.525 Over the Temperature Range 2.44 2.50 2.56

Table 3. ELECTRICAL CHARACTERISTICS (continued) ( $V_{CC} = 12 \text{ V}, V_{LVSNS1} = 1.2 \text{ V}, V_{LVSNS2} = 0 \text{ V}, V_{FB} = 2.4 \text{ V}, V_{FAULT} = \text{open}, C_{POLARITY} = 100 \text{ pF}, V_{AUX} = 0 \text{ V}, V_{ZCD} = 0 \text{ V}, C_{VCC} = 100 \text{ nF}, C_{SRL} = C_{SRH} = 100 \text{ pF}, C_{PWML} = C_{PWMH} = 100 \text{ pF}, \text{ for typical values } T_J = 25^{\circ}\text{C}, \text{ for min/max values}, T_J \text{ is } -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted}$

| Characteristics                                                                                            | Conditions                                                                                                                                       | Symbol                                | Min  | Тур        | Мах  | Unit |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------|------------|------|------|

| REGULATION BLOCK                                                                                           |                                                                                                                                                  |                                       |      |            |      |      |

| Ratio (V <sub>OUT</sub> Low Detect Lower<br>Threshold / V <sub>REF</sub> )<br>(Guaranteed by Design)       | V <sub>FB</sub> Decreasing                                                                                                                       | V <sub>DRE</sub> L / V <sub>REF</sub> | 95.0 | 95.5       | 96.0 | %    |

| Ratio (V <sub>OUT</sub> Low Detect Higher<br>Threshold / V <sub>REF</sub><br>(Guaranteed by Design)        | V <sub>FB</sub> Increasing                                                                                                                       | V <sub>DRE</sub> H / V <sub>REF</sub> | 97.5 | 98.0       | 98.5 | %    |

| Ratio (V <sub>OUT</sub> Low Detect<br>Hysteresis / V <sub>REF</sub> )<br>(Guaranteed by Design)            | V <sub>FB</sub> Increasing                                                                                                                       | H <sub>DRE</sub> / V <sub>REF</sub>   | 2    | 2.5        | -    | %    |

| Loop Gain Increase due to Dynamic<br>Response Enhancer<br>NCP1680AA, AB<br>NCP1680AC                       | PFCOK = High                                                                                                                                     | K <sub>DRE1</sub>                     |      | 5x<br>10x  |      | _    |

| All Devices                                                                                                | PFCOK = Low                                                                                                                                      | K <sub>DRE0</sub>                     |      | 2.5x       |      |      |

| STATIC OVP                                                                                                 |                                                                                                                                                  |                                       |      |            |      |      |

| Duty Ratio                                                                                                 | V <sub>FB</sub> = 3 V                                                                                                                            | D <sub>MIN</sub>                      | -    | -          | 0    | %    |

| SOFT SKIP CIRCUIT                                                                                          |                                                                                                                                                  | -                                     |      |            |      | -    |

| SKIP Voltage in CrM/DCM                                                                                    |                                                                                                                                                  | VSKIP                                 | 4.5  | 5          | 5.5  | V    |

| SKIP Current Capability                                                                                    |                                                                                                                                                  | ISKIP                                 | 450  | 700        | -    | μΑ   |

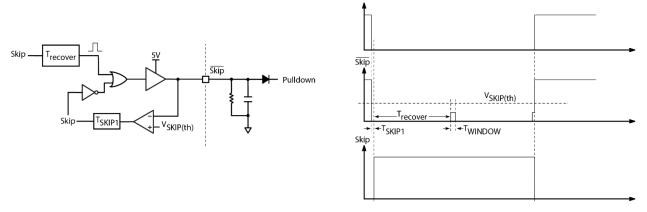

| SKIP Threshold Voltage to Enter<br>Skip Mode                                                               |                                                                                                                                                  | V <sub>SKIP(th)</sub>                 | 1.2  | 1.5        | 1.8  | V    |

| SKIP Minimum Pulse Duration for<br>SKIP Detection                                                          | $V_{\overline{SKIP}} < V_{SKIP(th)}$                                                                                                             | T <sub>SKIP1</sub>                    | 56   |            |      | μs   |

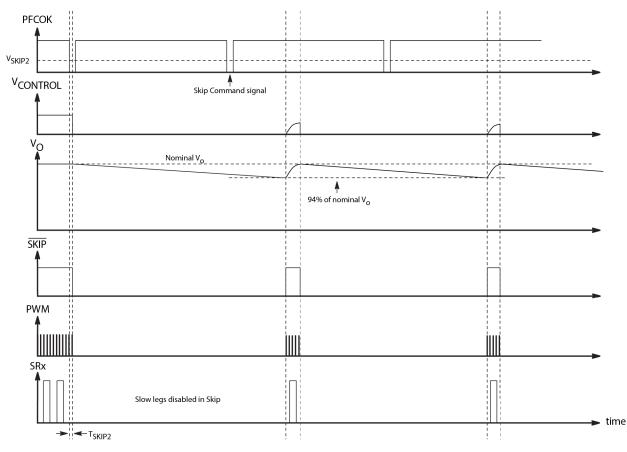

| PFCOK SKIP Threshold                                                                                       |                                                                                                                                                  | V <sub>SKIP2</sub>                    | 0.4  | 0.5        | 0.6  | V    |

| Minimum PFCOK Negative Pulse<br>Duration for SKIP Detection                                                |                                                                                                                                                  | T <sub>SKIP2</sub>                    | 10   | 30         | 50   | μs   |

| $V_{\text{FB}}$ Lower Value at the End of a Soft Skip Cycle Burst Defined as a $V_{\text{REF}}$ Percentage |                                                                                                                                                  | (R <sub>FB</sub> ) <sub>recover</sub> | 92.5 | 94         | 95.5 | %    |

| V <sub>FB</sub> Restart Level in Skip Cycle                                                                |                                                                                                                                                  | V <sub>RESTART</sub>                  |      | 2.35       |      | V    |

| Blanking Time for Operation<br>Recovery                                                                    |                                                                                                                                                  | T <sub>recover</sub>                  | 400  | 500        | 600  | ms   |

| SKIP Confirmation Window                                                                                   |                                                                                                                                                  | T <sub>WINDOW</sub>                   |      | 400        |      | μs   |

| ZCD PIN                                                                                                    |                                                                                                                                                  | •                                     |      |            |      |      |

| ZCD Arming Threshold<br>NCP1680AA<br>NCP1680AB, AC                                                         | V <sub>ZCD</sub> Increasing                                                                                                                      | V <sub>ZCD(ARM)</sub>                 |      | 300<br>100 |      | mV   |

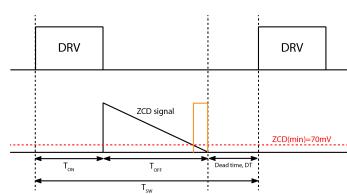

| ZCD Trigger Threshold                                                                                      | V <sub>ZCD</sub> Decreasing                                                                                                                      | V <sub>ZCD(TRG)</sub>                 |      | 50         |      | mV   |

| Threshold for Inrush Current<br>Protection                                                                 |                                                                                                                                                  | V <sub>ZCD</sub> (INRUSH)             |      | 50         |      | mV   |

| Propagation Delay to (1–D) Drive<br>Pulse                                                                  | $\begin{array}{l} \text{Step V}_{ZCD} \text{ 0 V to} \\ \text{V}_{ZCD(ARM)} + 250 \text{ mV} \\ \text{Time to PWMx} = 2.5 \text{ V} \end{array}$ | T <sub>ZCD(ARM)</sub>                 | -    | 45         | 75   | ns   |

| Propagation Delay (1–D) Drive<br>Termination                                                               | Step $V_{ZCD}$ 1 V to<br>$V_{ZCD(TRIG)}$ – 250 mV;<br>Time to PWMx = 2.5 V                                                                       | T <sub>ZCD(TRG)</sub>                 | -    | 45         | 75   | ns   |

Table 3. ELECTRICAL CHARACTERISTICS (continued) ( $V_{CC} = 12 \text{ V}, V_{LVSNS1} = 1.2 \text{ V}, V_{LVSNS2} = 0 \text{ V}, V_{FB} = 2.4 \text{ V}, V_{FAULT} = \text{open}, C_{POLARITY} = 100 \text{ pF}, V_{AUX} = 0 \text{ V}, V_{ZCD} = 0 \text{ V}, C_{VCC} = 100 \text{ nF}, C_{SRL} = C_{SRH} = 100 \text{ pF}, C_{PWML} = C_{PWMH} = 100 \text{ pF}, \text{ for typical values } T_J = 25^{\circ}\text{C}, \text{ for min/max values}, T_J \text{ is } -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}, \text{ unless otherwise noted}$

| Characteristics                                                                                                | Conditions                                                                                                      | Symbol                                                   | Min          | Тур        | Мах          | Unit |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|------------|--------------|------|

| ZCD PIN                                                                                                        |                                                                                                                 |                                                          |              |            |              | -    |

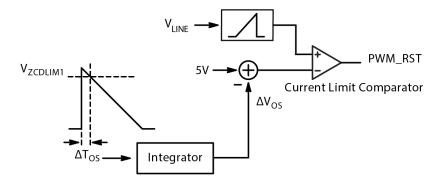

| Low–Line Range ZCD Protection<br>Threshold<br>NCP1680AA<br>NCP1680AB, AC                                       |                                                                                                                 | VZCDLIM1 (LL)                                            | 1.33<br>0.56 | 1.4<br>0.6 | 1.47<br>0.64 | V    |

| High-Line Range ZCD Protection<br>Threshold<br>NCP1680AA                                                       |                                                                                                                 | V <sub>ZCDLIM1(HL)</sub>                                 | 0.80         | 0.84       | 0.88         | V    |

| NCP1680AB, AC                                                                                                  |                                                                                                                 |                                                          | 0.325        | 0.36       | 0.395        |      |

| On–Time in CrM Current Limit                                                                                   | $V_{FB}$ = 2.0, $V_{ZCD}$ pulse 0–2 V LVSNS1 = 1.626, Pulse for 16 $\mu s$ LVSNS1 = 3.253, Pulse for 14 $\mu s$ | T <sub>ON_ZCDLIM(LL)</sub><br>T <sub>ON_ZCDLIM(HL)</sub> |              | 1.9<br>1.3 |              | μs   |

| ZCD Pullup Current Source                                                                                      | V <sub>ZCD</sub> = 0 V<br>V <sub>ZCD</sub> = 2.7 V                                                              | I <sub>ZCD</sub>                                         | 0.7<br>0.7   | 1<br>1     | 1.3<br>1.3   | μΑ   |

| ZCD Minimum Current Threshold<br>for THD Enhancer Enable                                                       | V <sub>ZCD</sub> Increasing                                                                                     | V <sub>ZCD(MIN)</sub>                                    |              |            |              | mV   |

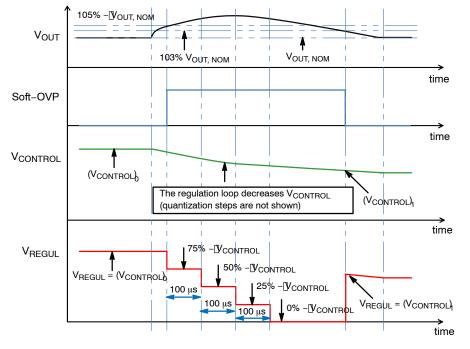

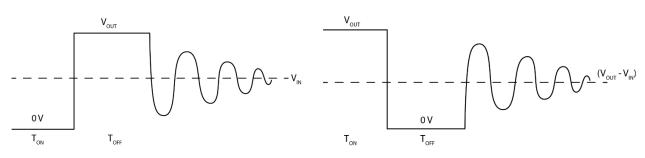

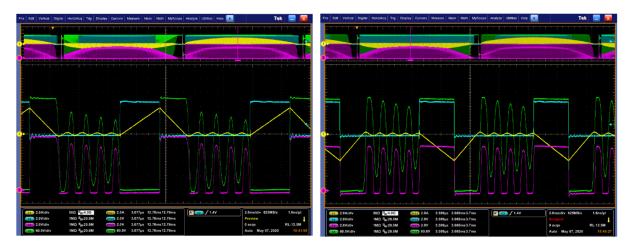

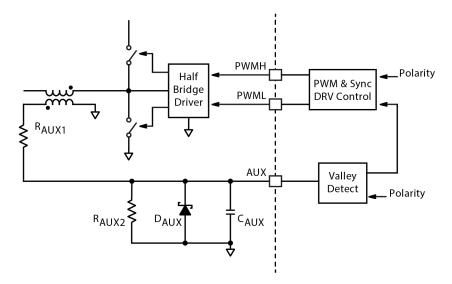

| NCP1680AA<br>NCP1680AB, AC                                                                                     |                                                                                                                 |                                                          | 45<br>5      | 70<br>30   | 95<br>55     |      |