# onsemi

# USB Positive Overvoltage Protection Controller with Internal PMOS FET and Overcurrent Protection

# NCP361, NCV361

The NCP361 disconnects systems at its output when wrong VBUS operating conditions are detected at its input. The system is positive over-voltage protected up to +20 V.

Thanks to an integrated PMOS FET, no external device is necessary, reducing the system cost and the PCB area of the application board.

The NCP361 is able to instantaneously disconnect the output from the input if the input voltage exceeds the overvoltage threshold (5.675 V). Thanks to an overcurrent protection, the integrated PMOS is turning off when the charge current exceeds current limit (see options in ordering information).

The NCP361 provides a negative going flag (FLAG) output, which alerts the system that voltage, current or overtemperature faults have occurred.

In addition, the device has ESD-protected input (15 kV Air) when by passed with a 1  $\mu$ F or larger capacitor.

#### Features

- Overvoltage Protection up to 20 V

- On-chip PMOS Transistor

- Overvoltage Lockout (OVLO)

- Undervoltage Lockout (UVLO)

- Overcurrent Protection

- Alert FLAG Output

- $\overline{\text{EN}}$  Enable Pin

- Thermal Shutdown

- Compliance to IEC61000-4-2 (Level 4) 8 kV (Contact) 15 kV (Air)

- ESD Ratings: Machine Model = B

- Human Body Model = 2

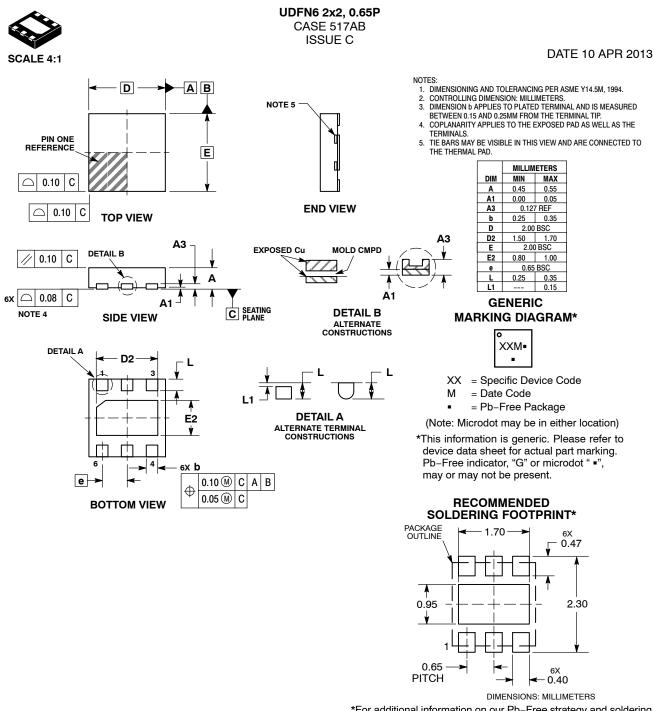

- UDFN6 2x2 mm and TSOP-5 3x3 mm Packages

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- This is a Pb-Free Device

#### Applications

- USB Devices

- Mobile Phones

- Peripheral

- Personal Digital Applications

- MP3 Players

- Set Top Boxes

= Pb-Free Package

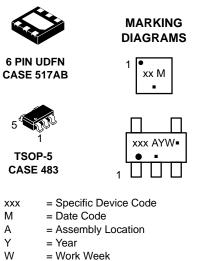

(Note: Microdot may be in either location)

### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 10 of this data sheet.

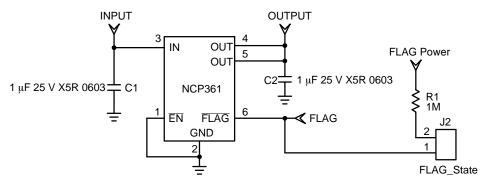

Figure 1. Typical Application Circuit (UDFN Pinout)

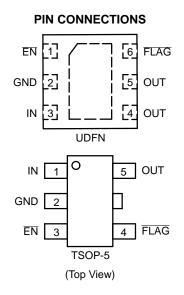

#### PIN FUNCTION DESCRIPTION (UDFN Package)

| Pin No. | Name | Туре   | Description                                                                                                                                                                                                                                                                                       |

|---------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | EN   | INPUT  | Enable Pin. The device enters in shutdown mode when this pin is tied to a high level. In this case the output is disconnected from the input. To allow normal functionality, the EN pin shall be connected to GND or to a I/O pin. This pin does not have an impact on the fault detection.       |

| 2       | GND  | POWER  | Ground                                                                                                                                                                                                                                                                                            |

| 3       | IN   | POWER  | Input Voltage Pin. This pin is connected to the VBUS. A 1 $\mu F$ low ESR ceramic capacitor, or larger, must be connected between this pin and GND.                                                                                                                                               |

| 4, 5    | OUT  | OUTPUT | Output Voltage Pin. The output is disconnected from the VBUS power supply when the input voltage is above OVLO threshold or below UVLO threshold. A 1 $\mu$ F capacitor must be connected to these pins. The two OUT pins must be hardwired to common supply.                                     |

| 6       | FLAG | OUTPUT | Fault Indication Pin. This pin allows an external system to detect a fault on VBUS pin. The $\overline{FLAG}$ pin goes low when input voltage exceeds OVLO threshold. Since the $\overline{FLAG}$ pin is open drain functionality, an external pull up resistor to V <sub>CC</sub> must be added. |

#### PIN FUNCTION DESCRIPTION (TSOP-5 Package)

| Pin No. | Name | Туре   | Description                                                                                                                                                                                                                                                                                                     |  |

|---------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | IN   | POWER  | Input Voltage Pin. This pin is connected to the VBUS. A 1 $\mu F$ low ESR ceramic capacitor, or larger, must be connected between this pin and GND.                                                                                                                                                             |  |

| 2       | GND  | POWER  | Ground                                                                                                                                                                                                                                                                                                          |  |

| 3       | EN   | INPUT  | Enable Pin. The device enters in shutdown mode when this pin is tied to a high level. In this case the output is disconnected from the input. To allow normal functionality, the $\overline{\text{EN}}$ pin shall be connected to GND or to a I/O pin. This pin does not have an impact on the fault detection. |  |

| 4       | FLAG | OUTPUT | Fault Indication Pin. This pin allows an external system to detect a fault on VBUS pin. The $\overline{FLAG}$ pin goes low when input voltage exceeds OVLO threshold. Since the $\overline{FLAG}$ pin is open drain functionality, an external pull up resistor to V <sub>CC</sub> must be added.               |  |

| 5       | OUT  | OUTPUT | Output Voltage Pin. The output is disconnected from the VBUS power supply when the input voltage is above OVLO threshold or below UVLO threshold. A 1 $\mu F$ capacitor must be connected to this pin.                                                                                                          |  |

NOTE: Pin out provided for concept purpose only and might change in the final product

#### **MAXIMUM RATINGS**

| Rating                                                                                                                       | Symbol             | Value                              | Unit         |

|------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------|--------------|

| Minimum Voltage (IN to GND)                                                                                                  | Vmin <sub>in</sub> | -0.3                               | V            |

| Minimum Voltage (All others to GND)                                                                                          | Vmin               | -0.3                               | V            |

| Maximum Voltage (IN to GND)                                                                                                  | Vmax <sub>in</sub> | 21                                 | V            |

| Maximum Voltage (All others to GND)                                                                                          | Vmax               | 7.0                                | V            |

| Maximum DC Current from Vin to Vout (PMOS) (Note 1)                                                                          | Imax               | 600                                | mA           |

| Thermal Resistance, Junction-to-Air TSOP-5<br>UDFN                                                                           | $R_{	hetaJA}$      | 305<br>240                         | °C/W         |

| Operating Ambient Temperature Range                                                                                          | T <sub>A</sub>     | -40 to +85                         | °C           |

| Storage Temperature Range                                                                                                    | T <sub>stg</sub>   | -65 to +150                        | °C           |

| Junction Operating Temperature                                                                                               | TJ                 | 150                                | °C           |

| ESD Withstand Voltage (IEC 61000-4-2)<br>Human Body Model (HBM), Model = 2 (Note 2)<br>Machine Model (MM) Model = B (Note 3) | Vesd               | 15 Air, 8.0 Contact<br>2000<br>200 | kV<br>V<br>V |

| Moisture Sensitivity                                                                                                         | MSL                | Level 1                            | -            |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. With minimum PCB area. By decreasing R<sub>θJA</sub>, the current capability increases. See PCB recommendation page 9.

2. Human Body Model, 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114.

3. Machine Model, 200 pF discharged through all pins following specification JESD22/A115.

#### ELECTRICAL CHARACTERISTICS

(Min/Max limits values (-40 °C <  $T_A$  < +85 °C) and  $V_{in}$  = +5.0 V. Typical values are  $T_A$  = +25 °C, unless otherwise noted.)

| Characteristic                                 | Symbol               | Conditions                                                                                                                                                                                            | Min  | Тур   | Max  | Unit |

|------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| Input Voltage Range                            | V <sub>in</sub>      |                                                                                                                                                                                                       | 1.2  |       | 20   | V    |

| Undervoltage Lockout<br>Threshold              | UVLO                 | V <sub>in</sub> falls down UVLO threshold                                                                                                                                                             | 2.85 | 3.0   | 3.15 | V    |

| Uvervoltage Lockout Hysteresis                 | UVLO <sub>hyst</sub> |                                                                                                                                                                                                       | 50   | 70    | 90   | mV   |

| Overvoltage Lockout Threshold                  | OVLO                 | V <sub>in</sub> rises up OVLO threshold                                                                                                                                                               | 5.43 | 5.675 | 5.9  | V    |

| Overvoltage Lockout Hysteresis                 | OVLO <sub>hyst</sub> |                                                                                                                                                                                                       | 50   | 100   | 125  | mV   |

| V <sub>in</sub> versus V <sub>out</sub> Dopout | V <sub>drop</sub>    | V <sub>in</sub> = 5 V, I charge = 500 mA                                                                                                                                                              |      | 150   | 200  | mV   |

| Overcurrent Limit                              | l <sub>lim</sub>     | V <sub>in</sub> = 5 V                                                                                                                                                                                 | 550  | 750   | 950  | mA   |

| Supply Quiescent Current                       | ldd                  | No Load, V <sub>in</sub> = 5.25 V                                                                                                                                                                     |      | 20    | 35   | μΑ   |

| Standby Current                                | I <sub>std</sub>     | V <sub>in</sub> = 5 V, EN = 1.2 V                                                                                                                                                                     |      | 26    | 37   | μΑ   |

| Zero Gate Voltage Drain Current                | I <sub>DSS</sub>     | $V_{DS} = 20 \text{ V}, \text{ V}_{GS} = 0 \text{ V}$                                                                                                                                                 |      | 0.08  |      | μΑ   |

| FLAG Output Low Voltage                        | Vol <sub>flag</sub>  | V <sub>in</sub> > OVLO<br>Sink 1 mA on FLAG pin                                                                                                                                                       |      |       | 400  | mV   |

| FLAG Leakage Current                           | FLAG <sub>leak</sub> | FLAG level = 5 V                                                                                                                                                                                      |      | 5.0   |      | nA   |

| EN Voltage High                                | V <sub>ih</sub>      | V <sub>in</sub> from 3.3 V to 5.5 V                                                                                                                                                                   | 1.2  |       |      | V    |

| EN Voltage Low                                 | V <sub>il</sub>      | V <sub>in</sub> from 3.3 V to 5.5 V                                                                                                                                                                   |      |       | 0.55 | V    |

| EN Leakage Current                             | ENleak               | EN = 5.5 V or GND                                                                                                                                                                                     |      | 170   |      | nA   |

| TIMINGS                                        |                      |                                                                                                                                                                                                       |      |       |      |      |

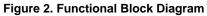

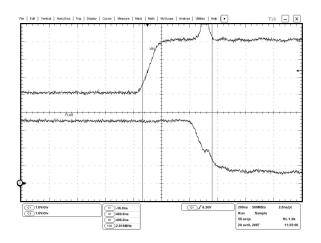

| Start Up Delay                                 | t <sub>on</sub>      | From $V_{in}$ > UVLO to $V_{out}$ = 0.8x $V_{in}$ , See Fig 3 & 9                                                                                                                                     |      | 4.0   | 15   | ms   |

| FLAG going up Delay                            | t <sub>start</sub>   | From $V_{in}$ > UVLO to FLAG = 1.2 V, See Fig 3 & 10                                                                                                                                                  |      | 3.0   |      | μs   |

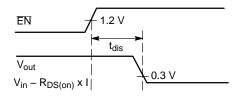

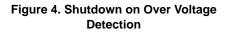

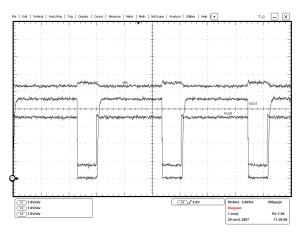

| Output Turn Off Time                           | t <sub>off</sub>     | $\begin{array}{l} \mbox{From $V_{in}$} > \mbox{OVLO to $V_{out}$} \leq 0.3 $V$, See Fig 4 \& 11$ \\ \mbox{$V_{in}$ increasing from 5 $V$ to 8 $V$ at 3 $V$/$$$$$, $No output capacitor.} \end{array}$ |      | 0.7   | 1.5  | μS   |

| Alert Delay                                    | t <sub>stop</sub>    | From $V_{in}$ > OVLO to FLAG $\leq$ 0.4 V, See Fig 4 & 12 $V_{in}$ increasing from 5 V to 8 V at 3 V/µs                                                                                               |      | 1.0   |      | μS   |

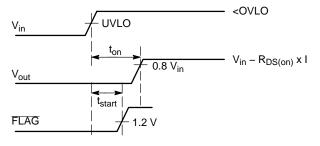

| Disable Time                                   | t <sub>dis</sub>     | From $\overline{EN}$ 0.4 to 1.2V to $V_{out}$ $\leq$ 0.3 V, See Fig 5 & 13 $V_{in}$ = 4.75 V. No output capacitor.                                                                                    |      | 3.0   |      | μS   |

| Thermal Shutdown Temperature                   | T <sub>sd</sub>      |                                                                                                                                                                                                       |      | 150   |      | °C   |

| Thermal Shutdown Hysteresis                    | T <sub>sdhyst</sub>  |                                                                                                                                                                                                       |      | 30    |      | °C   |

Figure 3. Start Up Sequence

FLAG

#### Figure 5. Disable on $\overline{EN} = 1$

Figure 6.  $\overline{FLAG}$  Response with  $\overline{EN} = 1$

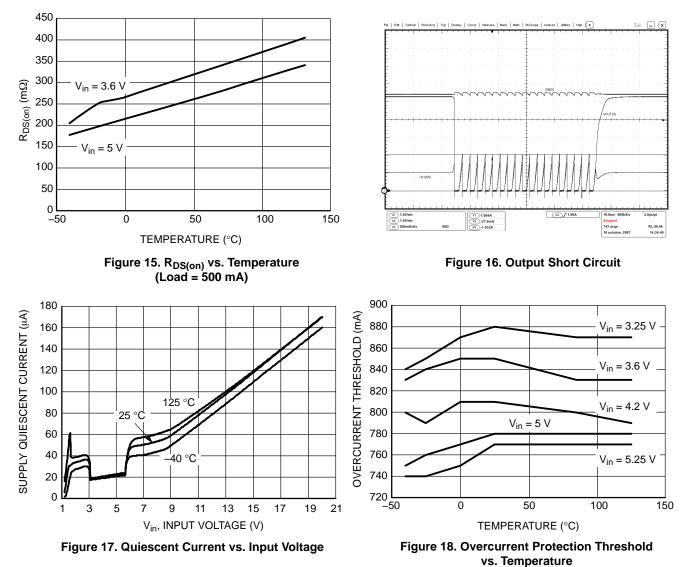

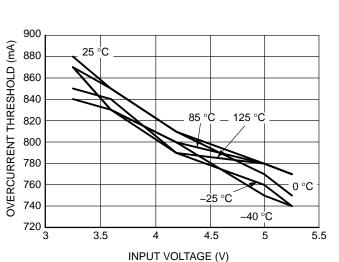

### **TYPICAL OPERATING CHARACTERISTICS**

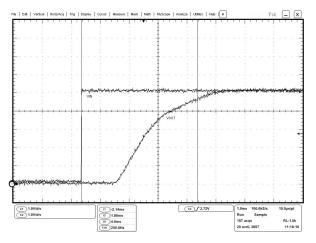

Figure 9. Start Up. Vin=Ch1, Vout=Ch2

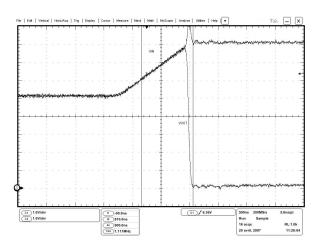

Figure 11. Output Turn Off time. Vin=Ch1, Vout=Ch2

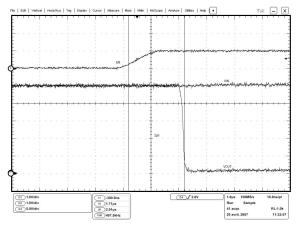

Figure 13. Disable Time. EN=Ch4, Vin=Ch1, Vout=Ch2

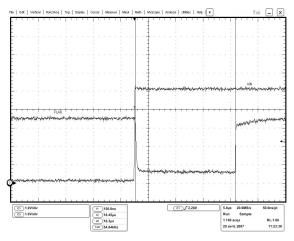

Figure 10. FLAG Going Up Delay. Vin=Ch1, FL:AG=Ch3

Figure 12. Alert Delay. Vout=Ch1, FLAG=Ch3

Figure 14. Thermal Shutdown. Vin=Ch1, Vout=Ch2, FLAG=Ch3

#### **TYPICAL OPERATING CHARACTERISTICS**

Figure 19. Overcurrent Protection Threshold vs. Input Voltage

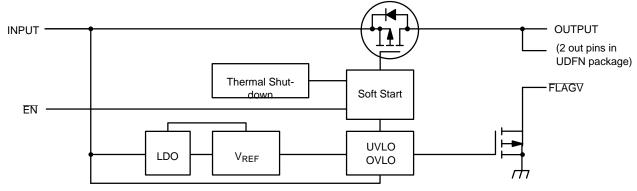

#### Operation

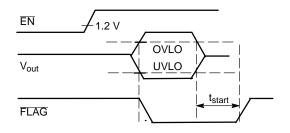

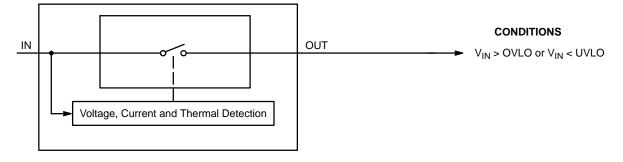

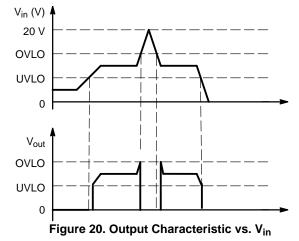

NCP361 provides overvoltage protection for positive voltage, up to 20 V. A PMOS FET protects the systems (i.e.: VBUS) connected on the  $V_{out}$  pin, against positive overvoltage. The Output follows the VBUS level until OVLO threshold is overtaken.

#### Undervoltage Lockout (UVLO)

To ensure proper operation under any conditions, the device has a built-in undervoltage lock out (UVLO) circuit. During  $V_{in}$  positive going slope, the output remains disconnected from input until  $V_{in}$  voltage is above 3.0 V nominal. The FLAGV output is pulled to low as long as  $V_{in}$  does not reach UVLO threshold. This circuit has a 70 mV hysteresis to provide noise immunity to transient condition.

#### **Overvoltage Lockout (OVLO)**

To protect connected systems on  $V_{out}$  pin from overvoltage, the device has a built-in overvoltage lock out (OVLO) circuit. During overvoltage condition (OVLO exceeds), the output remains disabled and  $\overline{FLAG}$  is tied low, as long as the input voltage is higher than OVLO – hysteresis. This circuit has a 100 mV hysteresis to provide noise immunity to transient conditions.

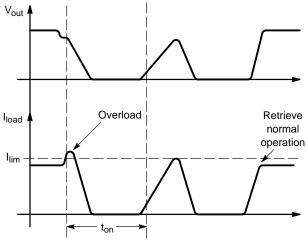

#### **Overcurrent Protection (OCP)**

The NCP361 integrates overcurrent protection to prevent system/battery overload or defect. The current limit threshold is internally set at 750 mA. This value can be changed from 150 mA to 750 mA by a metal tweak, please contact your **onsemi** representative for availability. During current fault, the internal PMOS FET is automatically turned off (5  $\mu$ s) if the charge current exceeds I<sub>lim</sub>. NCP361 goes into turn on and turn off mode as long as defect is present. The internal ton delay (4 ms typical) allows limiting thermal dissipation. The Flag pin goes to low level when an overcurrent fault appears. That allows the microcontroller to count defect events and turns off the PMOS with EN pin.

Figure 21. Overcurrent Event Example

#### **FLAG** Output

NCP361 provides a FLAG output, which alerts external systems that a fault has occurred.

This pin is tied to low as soon as: 1.2 V < V<sub>in</sub> < UVLO, V<sub>in</sub> > OVLO, I<sub>charge</sub> > I<sub>limit</sub>, T<sub>J</sub> > 150 °C. When NCP361 recovers normal condition, FLAG is held high. The pin is an open drain output, thus a pull up resistor (typically 1 M $\Omega$  – Minimum 10 k $\Omega$ ) must be provided to V<sub>CC</sub>. FLAG pin is an open drain output.

#### **EN** Input

To enable normal operation, the  $\overline{\text{EN}}$  pin shall be forced to low or connected to ground. A high level on the pin disconnects OUT pin from IN pin.  $\overline{\text{EN}}$  does not overdrive an OVLO or UVLO fault.

#### Internal PMOS FET

The NCP361 includes an internal PMOS FET to protect the systems, connected on OUT pin, from positive overvoltage. Regarding electrical characteristics, the  $R_{DS(on)}$ , during normal operation, will create low losses on  $V_{out}$  pin, characterized by  $V_{in}$  versus  $V_{out}$  dropout.

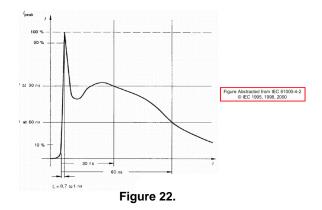

#### ESD Tests

The NCP361 fully supports the IEC61000-4-2, level 4 (Input pin, 1  $\mu$ F mounted on board). That means, in Air condition, V<sub>in</sub> has a ±15 kV ESD protected input. In Contact condition, V<sub>in</sub> has ±8 kV ESD protected input. Please refer to Figure 22 to see the IEC61000-4-2 electrostatic discharge waveform.

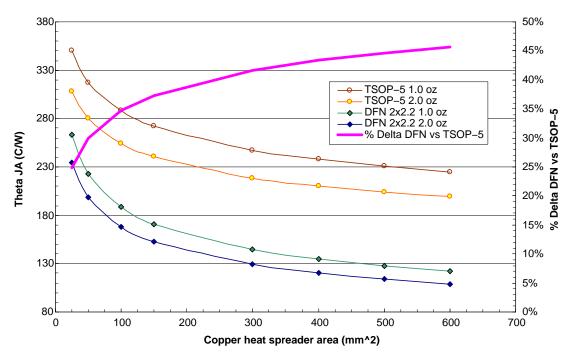

#### **PCB** Recommendations

The NCP361 integrates a 500 mA rated PMOS FET, and the PCB rules must be respected to properly evacuate the heat out of the silicon. The UDFN PAD1 must be connected to ground plane to increase the heat transfer if necessary from an application standpoint. Of course, in any case, this pad shall be not connected to any other potential.

By increasing PCB area, the  $R_{0JA}$  of the package can be decreased, allowing higher charge current to fill the battery.

Taking into account that internal bondings (wires between package and silicon) can handle up to 1 A (higher than thermal capability), the following calculation shows two different example of current capability, depending on PCB area:

- With 305 °C/W (without PCB area), allowing DC current is 500 mA

- With 260 °C/W (200 mm<sup>2</sup>), the charge DC current allows with a 85 °C ambient temperature is:  $I = \sqrt{(T_J - T_A)/(R_{\theta JA} \times R_{DSON})}$

I = 625 mA

In every case, we recommend to make thermal measurement on final application board to make sure of the final Thermal Resistance.

Figure 23. Thermal Resistance of UDFN 2x2 and TSOP Packages as a Function of PCB Area and Thickness

#### **ORDERING INFORMATION**

| Device       | Marking | Package             | Shipping <sup>†</sup> |

|--------------|---------|---------------------|-----------------------|

| NCP361MUTBG  | AD      | UDFN6<br>(Pb-Free)  | 3000 / Tape & Reel    |

| NCP361SNT1G  | ACD     | TSOP-5<br>(Pb-Free) | 3000 / Tape & Reel    |

| NCV361SNT1G* | VET     | TSOP-5<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements

#### SELECTION GUIDE

Part number is designated as follows:

NCP361xxxxTxG a b c d e

| Code | Contents                                   |

|------|--------------------------------------------|

| а    | Overcurrent Threshold<br>–: 750 mA         |

| b    | Package<br>MU: UDFN<br>SN: TSOP-5          |

| с    | UVLO Typical Threshold<br>–: 3.00 V        |

| d    | OVLO Typical Threshold<br>–: 5.675 V       |

| e    | Tape & Reel Type<br>B: = 3000<br>1: = 3000 |

# onsemi

# <u>Onsemi</u>.

\*For additional information on our Pb–Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON22162D      | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | UDFN6 2X2, 0.65P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

|                  |                  |                                                                                                                                                                                     |             |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>