# onsemi

# USB Type-C VCONN Overvoltage Protection IC

# **NCP398**

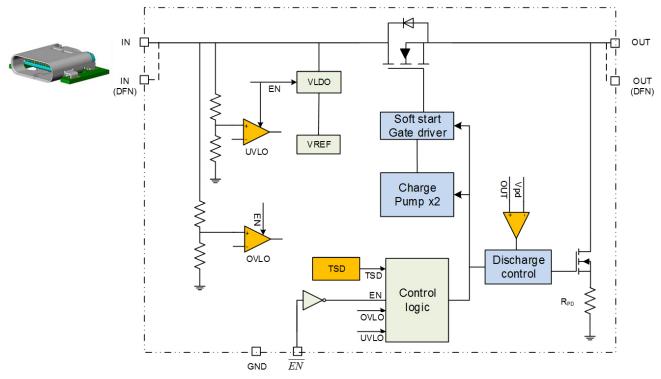

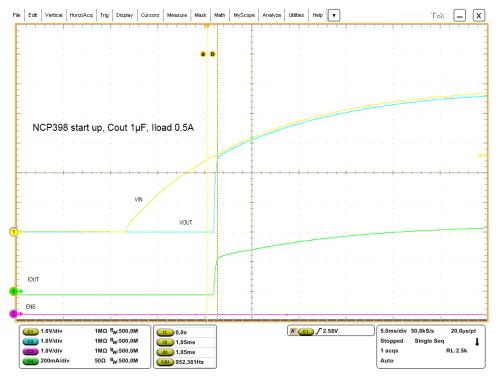

The NCP398 is an overvoltage protection device. It protects VCONN against overvoltages in applications where VCONN is directly derived from the VBUS supply.

At power up, the integrated power MOSFET is automatically controlled to reduce inrush current. The IC continuously monitors undervoltage, overvoltage and thermal events. In case of overvoltage, a very high speed comparator opens the power MOSFET instantaneously.

The part is enabled through the  $\overline{\text{EN}}$  pin. A high level on this pin allows forcing off the internal switch and drastically decreases the current consumption of the NCP398 core.

#### Features

- Over-voltage Protection up to + 28 V

- On-chip Low R<sub>dson</sub> NMOS Transistors: Typical 200 mΩ

- Over-voltage Lockout (OVLO)

- Shutdown EN Input

- Output Discharge Path

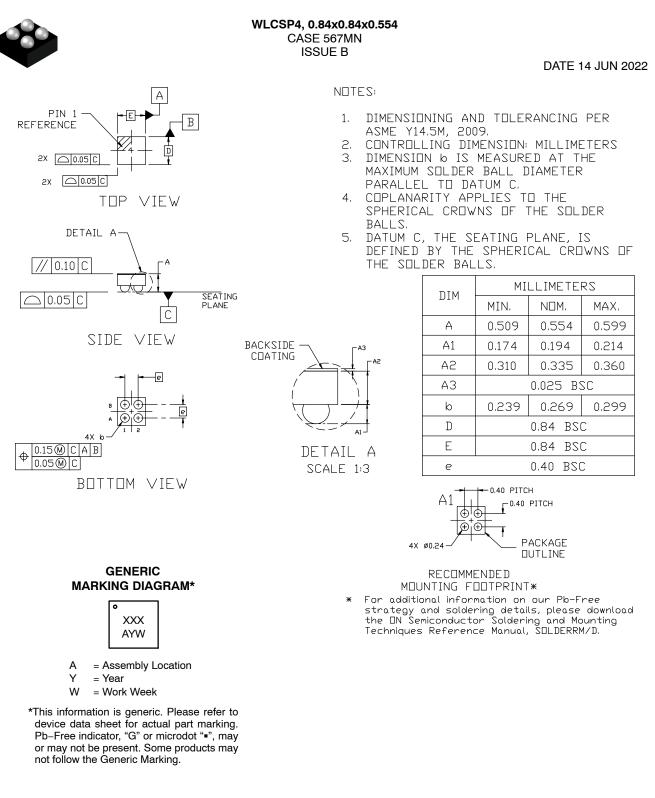

- WLCSP4 Package 0.84 x 0.84 mm, 0.4p

- UDFN6 Package 2 x 2 mm, 0.65p

- These Parts are ROHS Devices

#### **Typical Applications**

- Type–C USB

- Smartphones

- Tablets

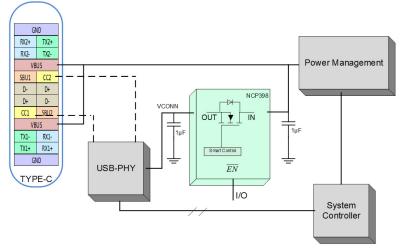

Figure 1. Typical Application Circuit

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 11 of this data sheet.

1

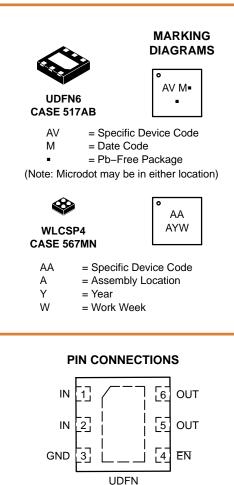

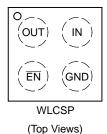

#### Table 1. CSP PINOUT DESCRIPTION

| Pin | Pin Name | Туре   | Description                                                                                                                               |  |

|-----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1  | OUT      | OUTPUT | Output voltage pin.<br>The OUT pin must be connected to the circuitry that is to be protected (VCONN rail).                               |  |

| B1  | EN       | I/O    | Enable pin bar.<br>The device enters in shutdown mode when this pin is tied high in which case the output is disconnected from the input. |  |

| A2  | IN       | POWER  | Input voltage pin.<br>The IN pin must be connected to the input power supply (VBUS).                                                      |  |

| B2  | GND      | POWER  | Ground.<br>Must be connected to the system GND plane.                                                                                     |  |

#### Table 2. DFN PINOUT DESCRIPTION

| Pin | Pin Name | Туре  | Description                                                                                                                                  |

|-----|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1,2 | IN       | POWER | Input voltage pins.<br>The two IN pins must be hardwired together and are connected to the input power supply (VBUS).                        |

| 3   | GND      | POWER | Ground.<br>Must be connected to the system GND plane.                                                                                        |

| 5,6 | OUT      | POWER | Output voltage pins.<br>The two OUT pins must be hardwired together and are connected to the circuitry that is to be protected (VCONN rail). |

| 4   | EN       | I/O   | Enable pin bar.<br>The device enters in shutdown mode when this pin is tied high in which case the output is disconnected from the input.    |

| 7   | PAD      | POWER | DFN package back side pad. Must be connected to ground plane for thermal dissipation optimization.                                           |

#### **Table 3. MAXIMUM RATINGS**

| Rating                                             | Symbol                         | Value              | Unit        |      |

|----------------------------------------------------|--------------------------------|--------------------|-------------|------|

| Minimum Voltage (All to GND)                       | V <sub>MIN</sub>               | -0.3               | V           |      |

| Maximum Voltage (Ins to GND)                       |                                | V <sub>INMAX</sub> | 29          | V    |

| Maximum Voltage (All others to GND)                |                                | V <sub>MAX</sub>   | 7           | V    |

| Maximum DC current                                 |                                | I <sub>MAX</sub>   | 0.8         | А    |

| Thermal Resistance, Junction to Air                | WLCSP (Note 1)<br>DFN (Note 1) | $R_{	hetaJA}$      | 170<br>145  | °C/W |

| Operating Ambient Temperature Range                |                                | T <sub>A</sub>     | -40 to +85  | °C   |

| Storage Temperature Range                          |                                | T <sub>STG</sub>   | -65 to +150 | °C   |

| Junction Operating temperature                     |                                | TJ                 | +125        | °C   |

| Human Body Model (HBM) ESD Rating are (Note 2)     |                                | ESD HBM            | 2           | kV   |

| Charged Device Model (CDM) ESD Rating are (Note 2) |                                | ESD CDM            | 1           | kV   |

| Latch Up Current (Note 3)                          |                                | I <sub>LU</sub>    | 100         | mA   |

| Moisture Sensitivity                               |                                | MSL                | Level 1     |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. The  $R_{\theta JA}$  is highly dependent on the PCB heat sink area. As example UDFN6  $R_{\theta JA}$  is 220°C/W with 50 mm<sup>2</sup> (copper 35  $\mu$ m, 1 oz) and

145°C/W with 200 mm<sup>2</sup> (copper 35 μm, 2 oz).

Human Body Model, 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114, Charged Device Model (CDM) per JEDEC standard: JESD22–C101 Class IV.

3. Latch Up Current per JEDEC standard: JESD78 class II.

#### **Table 4. ELECTRICAL CHARACTERISTICS**

Min / Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and V<sub>IN</sub> = +5 V (Unless otherwise noted). Typical values are T<sub>A</sub> = +25°C.

| Characteristics                           | Symbols Conditions   |                                                                                            | Min  | Тур  | Max  | Unit |

|-------------------------------------------|----------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| Input Voltage Range                       | V <sub>IN</sub>      |                                                                                            | -    | -    | 28   | V    |

| Under Voltage Lockout                     | UVLO                 | Vin rising                                                                                 | 2.4  | -    | 2.8  | V    |

| Under Voltage Lockout Hystere-<br>sis     | UVLO <sub>HYST</sub> | Vin falling                                                                                | -    | 50   | -    | mV   |

| Over voltage Lockout Threshold            | OVLO<br>(Note 4)     | Vin rising                                                                                 | 5.50 | 5.65 | 5.80 | V    |

| Over voltage Lockout Threshold hysteresis | OVLO <sub>HYST</sub> | Vin falling                                                                                | -    | 115  | -    | mV   |

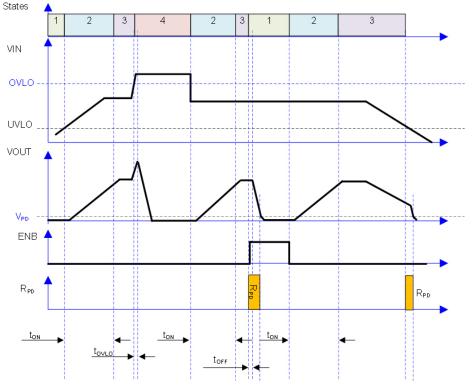

| Vin versus Vout Resistance                | R <sub>DSON</sub>    | Vin = 5 V, EN = low, 25°C, WLCSP                                                           | -    | 190  | 220  | mΩ   |

|                                           |                      | –40°C < TJ < 85°C, WLCSP                                                                   | -    | 230  | 260  | 1    |

|                                           |                      | Vin = 5 V, $\overline{EN}$ = low, 25°C, UDFN                                               | -    | 230  | 260  | 1    |

|                                           |                      | –40°C < T <sub>J</sub> < 85°C, UDFN                                                        | -    | 270  | 300  |      |

| Supply Quiescent Current                  | I <sub>DD</sub>      | No load. EN = low                                                                          | -    | 40   | 60   | μΑ   |

| OFF current                               | I <sub>OFF</sub>     | EN = high                                                                                  | -    | -    | 1.5  | μΑ   |

| Standby current                           | I <sub>STB</sub>     | Vin = 2.4 V                                                                                | -    | -    | 2.5  | μΑ   |

| Output Discharge path                     | R <sub>PD</sub>      | From $\overline{EN}$ = low to high or<br>Vin < UVLO – hysteresis to Vout = V <sub>PD</sub> | 8    | 10   | 12   | kΩ   |

| Output Discharge path level               | V <sub>PD</sub>      | Vout falling                                                                               | -    | 0.63 | -    | V    |

| EN                                        |                      |                                                                                            |      |      |      |      |

| EN Voltage High                           | V <sub>IH</sub>      |                                                                                            | 1.2  | -    | -    | V    |

| EN Voltage Low                            | V <sub>IL</sub>      |                                                                                            | -    | -    | 0.4  | V    |

| EN Input Leakage Current                  | IEN                  | 0 < V <sub>EN</sub> < 5.5 V                                                                | -1   | 0    | +1   | μΑ   |

| TIMINGS                                   |                      |                                                                                            |      |      |      |      |

| Ton Time                                  | T <sub>ON</sub>      | Vin valid, From EN high to low, 90% Vout                                                   | -    | 0.3  | 1    | ms   |

| Disable Time T <sub>OFF</sub>             |                      | From $\overline{\text{EN}}$ low to high, to 90% Vout.<br>R <sub>LOAD</sub> 100 $\Omega$    | -    | 10   | -    | μS   |

| OVLO Turn Off Time                        | T <sub>OVLO</sub>    | Vin exceeding V_{OVLO} at 2 V/µs to Vout starts decreasing. R_LOAD 100 $\Omega$            | -    | 100  | -    | ns   |

| TSD                                       |                      |                                                                                            |      |      |      |      |

| Thermal shutdown                          | TSD                  |                                                                                            | -    | 150  | -    | °C   |

| Thermal shutdown rearming                 | TSD rearm            |                                                                                            | -    | 125  | -    | °C   |

4. Please contact your ON representative for additional OVLO thresholds.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### Operation

The NCP398 device provides overvoltage protection when a wrong input supply is connected or voltage ringing appears on the input line. The internal NMOS Fet is soft start controlled to limit inrush current into the load (capacitors, IC wake up).

The device integrates an enable control pin, undervoltage and overvoltage comparators, and output discharge path to eliminate residual voltage after the turn off.

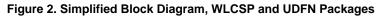

#### **Timings Chronogram and States Description**

The phase 1 sections described below are respectively the OFF state ( $\overline{\text{EN}}$  high) and the standby state (VIN < UVLO)

of the device. When Vin is below the undervoltage comparator (UVLO) or  $\overline{\text{EN}}$  is tied high, NCP398 will be in this state.

Phase 2 corresponds to the defined time for the gate driver soft start. Referring to the electrical parameter, this phase is aligned to Ton time.

Phase 3 is the normal operation, with Vin valid, the part enabled and there is no fault.

The behavior during an overvoltage condition is detailed in the phase number 4.

Figure 3. Timings Diagram

#### Enable Bar Pin (EN)

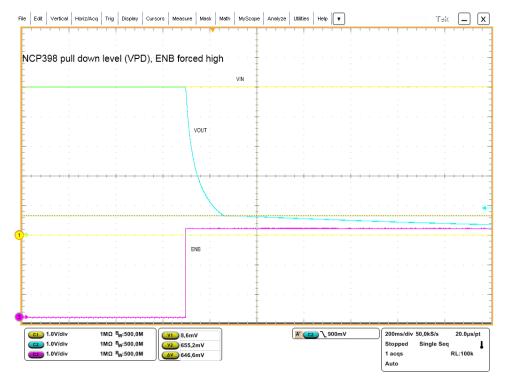

The part is enabled through the  $\overline{\text{EN}}$  pin. In some diagrams and figures, ENB refers to  $\overline{\text{EN}}$ . A high level on this pin allows forcing off the internal switch and drastically decreases the current consumption of the NCP398 core. To exit the OFF state, the  $\overline{\text{EN}}$  pin must be tied low.

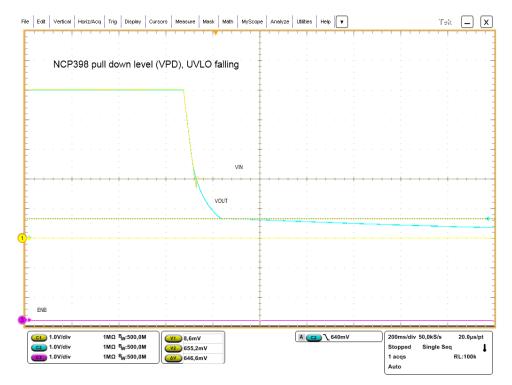

#### Under-voltage Lockout (UVLO)

To ensure proper operation under any conditions, the device integrates an under-voltage lock out (UVLO) comparator. This block has a built-in hysteresis to provide noise immunity to transient conditions.

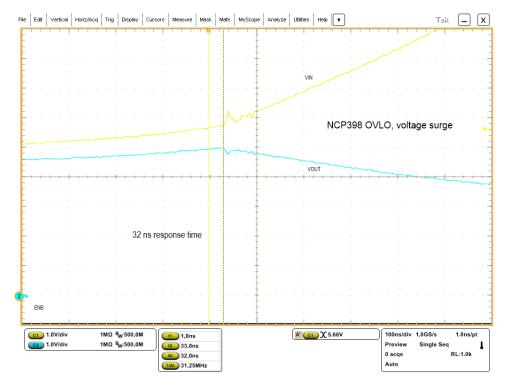

#### Over-voltage Lockout (OVLO)

To protect connected systems on  $V_{OUT}$  pin from over-voltage, a second comparator, over-voltage lock out (OVLO), is embedded. During over-voltage condition, the output remains disabled until the input voltage drops below the OVLO – comparator hysteresis.

#### Auto Discharge – R<sub>PD</sub>

When disabling the NCP398 the output gets automatically discharged by means of the internal pull down resistor Rpd. Once reaching the Vpd level the discharge path is disabled. The auto–discharge is also engaged when Vin drops below the UVLO threshold. The auto–discharge ensures a proper power cycling of peripherals connected to the output of the NCP398.

#### **Thermal Shutdown Protection**

In case of internal overheating, the integrated thermal shutdown (TSD) protection will open the internal NMOS FET in order to instantaneously decrease the device temperature.

Embedded hysteresis allows reengaging the NMOS FET when the junction temperature decreases.

This OFF-ON cycle is repeated until the fault event disappears.

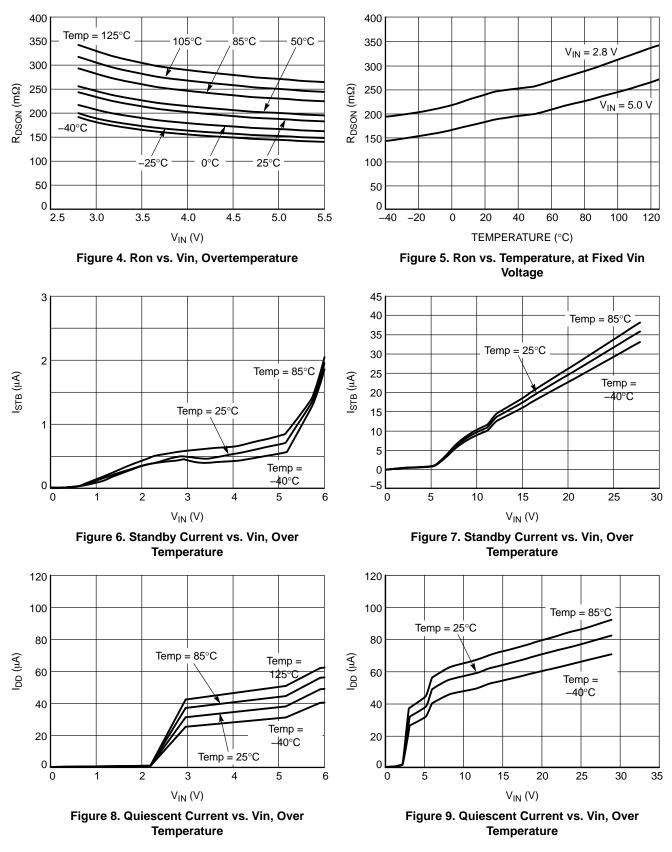

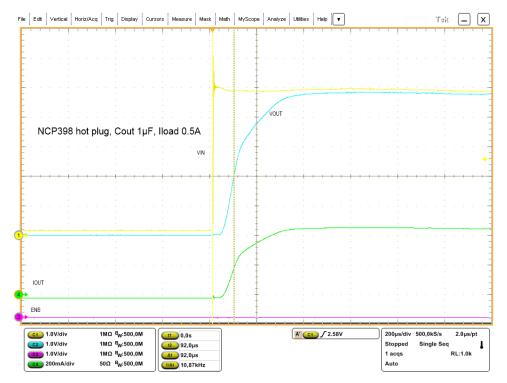

Figure 10. Soft Start Up On Load, Vin: yellow, Vout: blue, EN: pink, IOUT: green

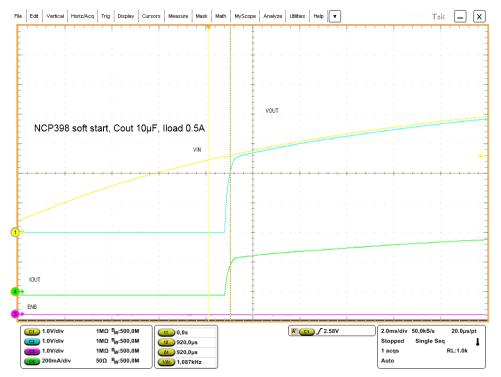

Figure 11. Hot Plug On Load, Vin: yellow, Vout: blue, EN: pink, IOUT: green

Figure 12. Soft Start On Cout 10  $\mu$ F, 500 mA, Vin: yellow, Vout: blue,  $\overline{\text{EN}}$ : pink, IOUT: green

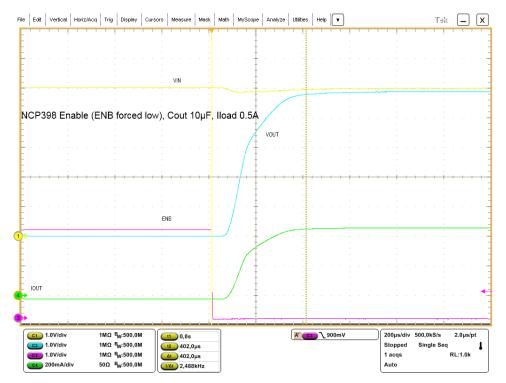

Figure 13. NCP398 Enable (ENB forced low) Vin: yellow, Vout: blue, EN: pink, IOUT: green

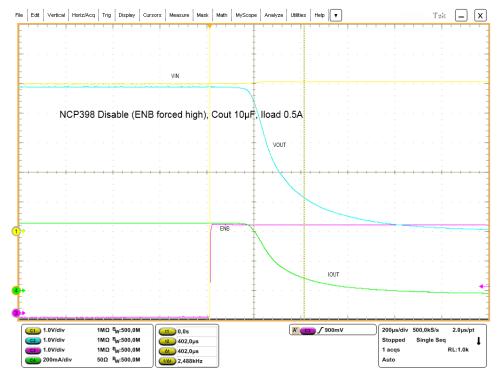

Figure 14. NCP398 Disable (ENB forced high) Vin: yellow, Vout: blue, EN: pink, IOUT: green

Figure 15. NCP398 Overvoltage Time Response, Vin: yellow, Vout: blue

Figure 16. NCP398 Pull Down Level (following disable) Vin: yellow, Vout: blue, EN: pink

Figure 17. NCP398 Pull Down Level (following UVLO) Vin: yellow, Vout: blue, EN: pink

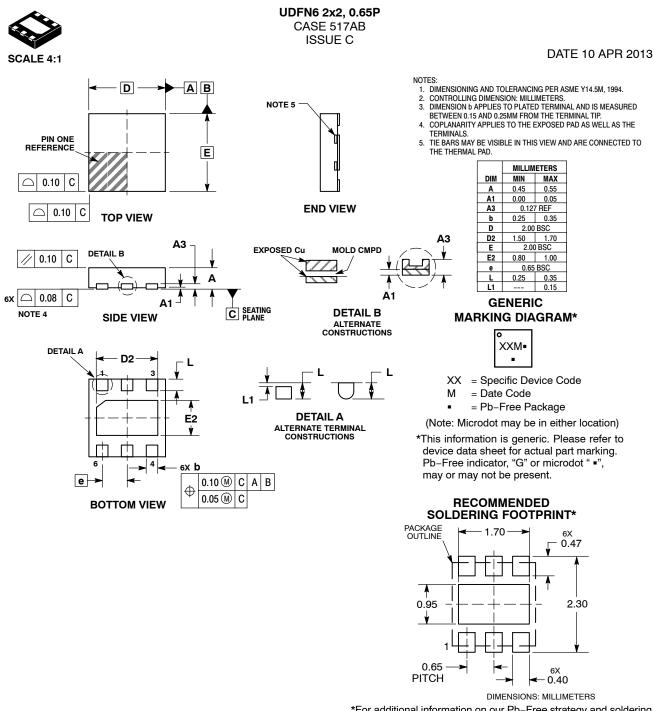

#### **ORDERING INFORMATION**

| Device       | Marking | Package             | Shipping <sup>†</sup> |

|--------------|---------|---------------------|-----------------------|

| NCP398FCCT1G | AA      | WLCSP4 0.84x0.84 mm | 3000 Tape / Reel      |

| NCP398MUTBG  | AV      | UDFN6 2x2 mm        | 3000 Tape / Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# <u>Onsemi</u>.

\*For additional information on our Pb–Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON22162D Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|--|

| DESCRIPTION:     | UDFN6 2X2, 0.65P                                                                                                                                                                               |  | PAGE 1 OF 1 |  |  |

|                  |                                                                                                                                                                                                |  |             |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

# onsemi

| DOCUMENT NUMBER: | 98AON05454G Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:     | WLCSP4, 0.84X0.84X0.554                                                                                                                                                                      |  | PAGE 1 OF 1 |  |

|                  |                                                                                                                                                                                              |  |             |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>