# High Current IGBT Gate Driver

# **NCV5702**

The NCV5702 is a high-current, high-performance stand-alone IGBT driver for high power applications that include solar inverters, motor control and uninterruptible power supplies. The device offers a cost-effective solution by eliminating many external components. Device protection features include Active Miller Clamp, accurate UVLO, EN input, DESAT protection and Active open-drain FAULT output. The driver also features an accurate 5.0 V output and separate high and low (VOH and VOL) driver outputs for system design convenience. The driver is designed to accommodate a wide voltage range of bias supplies including unipolar and bipolar voltages. It is available in a 16-pin SOIC package.

#### **Features**

- High Current Output (+4/-6 A) at IGBT Miller Plateau Voltages

- Low Output Impedance of VOH & VOL for Enhanced IGBT Driving

- Short Propagation Delays with Accurate Matching

- Direct Interface to Digital Isolator/Opto-coupler/Pulse Transformer for Isolated Drive, Logic Compatibility for Non-isolated Drive

- Active Miller Clamp to Prevent Spurious Gate Turn-on

- DESAT Protection with Programmable Delay

- Enable Input for Independent Driver Control

- Tight UVLO Thresholds for Bias Flexibility

- Wide Bias Voltage Range including Negative VEE Capability

- This Device is Pb-Free, Halogen-Free and RoHS Compliant

## **Typical Applications**

- Motor Control

- Uninterruptible Power Supplies (UPS)

- Automotive Power Supplies

- HEV/EV PTC Heaters

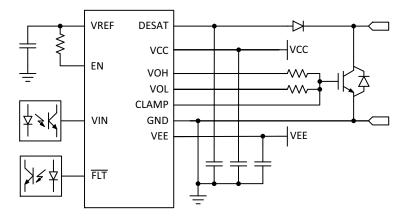

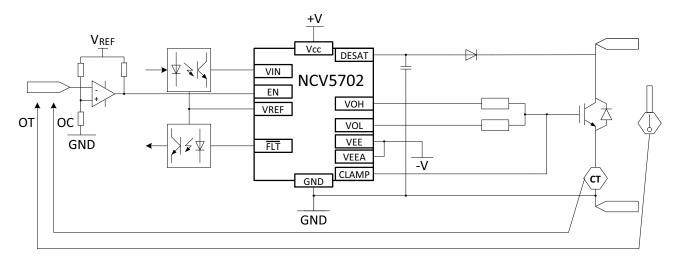

Figure 1. Simplified Application Schematic

#### SOIC-16 D SUFFIX CASE 751B

### MARKING DIAGRAM

A = Assembly Location

WL = Wafer Lot Y = Year

WW = Work Week

G = Pb-Free Package

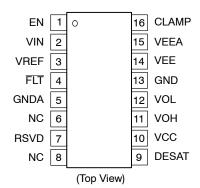

## **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 6 of this data sheet.

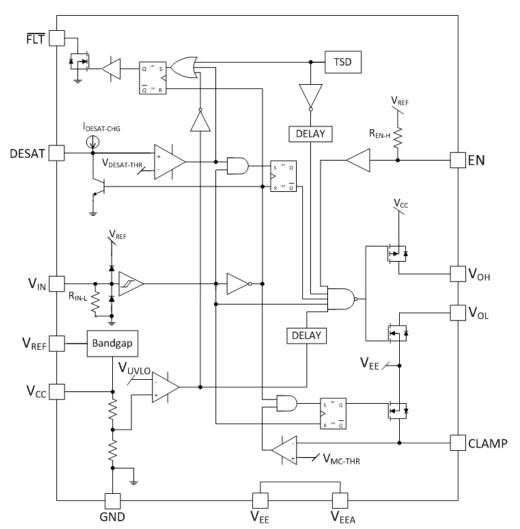

Figure 2. Detailed Block Diagram

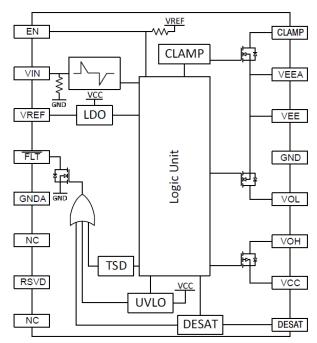

Figure 3. Simplified Block Diagram

## **Table 1. PIN FUNCTION DESCRIPTION**

| Pin Name | No. | I/O/x | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN       | 1   | I     | Enable input allows additional gating of VOH and VOL, and can be used when the driver output needs to be turned off independent of the Microcontroller input. EN is internally clamped to 5 V and has a pull–up resistor of 1 M $\Omega$ .                                                                                                                                                                                                                                                                      |

| VIN      | 2   | I     | Input signal to control the output. In applications which require galvanic isolation, VIN is generated at the opto output, the pulse transformer secondary or the digital isolator output. VOIH/VOL signal is in phase with VIN. VIN is internally clamped to 5 V and has a pull–down resistor of 1 M $\Omega$ to ensure that output is low in the absence of an input signal. A minimum pulse–width is required at VIN before VOH/VOL are activated.                                                           |

| VREF     | 3   | 0     | 5 V Reference generated within the driver is brought out to this pin for external bypassing and for powering low bias circuits (such as digital isolators).                                                                                                                                                                                                                                                                                                                                                     |

| FLT      | 4   | 0     | Fault open drain output (active low) that allows communication to the main controller that the driver has encountered a fault condition and has deactivated the output. Open drain allows easy setting of (inactive) high level and parallel connection of multiple fault signals.  Connect to 10k pull–up resistor recommended. Truth Table is provided in the datasheet to indicate conditions under which this signal is asserted. Capable of driving optos or digital isolators when isolation is required. |

| GNDA     | 5   | х     | This pin provides a convenient connection point for bypass capacitors (e.g REF) on the left side of the package.                                                                                                                                                                                                                                                                                                                                                                                                |

| NC       | 6,8 | х     | Pins not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RSVD     | 7   | х     | Reserved. No connection is allowed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DESAT    | 9   | I     | Input for detecting the desaturation of IGBT due to a fault condition. A capacitor connected to this pin allows a programmable blanking delay every ON cycle before DESAT fault is processed, thus preventing false triggering.                                                                                                                                                                                                                                                                                 |

| VCC      | 10  | х     | Positive bias supply for the driver. The operating range for this pin is from UVLO to the maximum. A good quality bypassing capacitor is required from this pin to GND and should be placed close to the pins for best results.                                                                                                                                                                                                                                                                                 |

| VOH      | 11  | 0     | Driver high output that provides the appropriate drive voltage and source current to the IGBT gate.                                                                                                                                                                                                                                                                                                                                                                                                             |

| VOL      | 12  | 0     | Driver low output that provides the appropriate drive voltage and sink current to the IGBT gate. VOL is actively pulled low during start-up and under Fault conditions.                                                                                                                                                                                                                                                                                                                                         |

| GND      | 13  | х     | This pin should connect to the IGBT Emitter with a short trace. All power pin bypass capacitors should be referenced to this pin and kept at a short distance from the pin.                                                                                                                                                                                                                                                                                                                                     |

| VEE      | 14  | х     | A negative voltage with respect to GND can be applied to this pin and that will allow VOL to go to a negative voltage during OFF state. A good quality bypassing capacitor is needed from VEE to GND. If a negative voltage is not applied or available, this pin must be connected to GND.                                                                                                                                                                                                                     |

| VEEA     | 15  | х     | Analog version of the VEE pin for any signal trace connection. VEE and VEEA are internally connected.                                                                                                                                                                                                                                                                                                                                                                                                           |

| CLAMP    | 16  | I/O   | Provides clamping for the IGBT gate during the off period to protect it from parasitic turn-on. To be tied directly to IGBT gate with minimum trace length for best results.                                                                                                                                                                                                                                                                                                                                    |

Table 2. ABSOLUTE MAXIMUM RATINGS (Note 1)

| Parameter                                                                      | Symbol                                               | Minimum               | Maximum               | Unit |  |

|--------------------------------------------------------------------------------|------------------------------------------------------|-----------------------|-----------------------|------|--|

| Differential Power Supply                                                      | V <sub>CC</sub> -V <sub>EE</sub> (V <sub>max</sub> ) | 0                     | 36                    | V    |  |

| Positive Power Supply                                                          | V <sub>CC</sub> -GND                                 | -0.3                  | 22                    | V    |  |

| Negative Power Supply                                                          | V <sub>EE</sub> -GND                                 | -18                   | 0.3                   | V    |  |

| Gate Output High                                                               | V <sub>OH</sub> -GND                                 |                       | V <sub>CC</sub> + 0.3 | V    |  |

| Gate Output Low                                                                | V <sub>OL</sub> -GND                                 | V <sub>EE</sub> – 0.3 |                       | V    |  |

| Input Voltage                                                                  | V <sub>IN</sub> -GND                                 | -0.3                  | 5.5                   | V    |  |

| Enable Voltage                                                                 | V <sub>EN</sub> -GND                                 | -0.3                  | 5.5                   | V    |  |

| DESAT Voltage                                                                  | V <sub>DESAT</sub> -GND                              | -0.3                  | V <sub>CC</sub> + 0.3 | V    |  |

| FLT Current<br>Sink                                                            | I <sub>FLT</sub> -SINK                               |                       | 20                    | mA   |  |

| Power Dissipation<br>SO-16 package                                             | PD                                                   |                       | 900                   | mW   |  |

| Maximum Junction Temperature                                                   | T <sub>J(max)</sub>                                  |                       | 150                   | °C   |  |

| Storage Temperature Range                                                      | TSTG                                                 |                       | -65 to 150            | °C   |  |

| ESD Capability, Human Body Model (Note 2)                                      | ESDHBM                                               |                       | 4                     | kV   |  |

| ESD Capability, Machine Model (Note 2)                                         | ESDMM                                                |                       | 200                   | ٧    |  |

| Moisture Sensitivity Level                                                     | MSL                                                  |                       | 1                     | -    |  |

| Lead Temperature Soldering Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>                                     |                       | 260                   | °C   |  |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. This device series incorporates ESD protection and is tested by the following methods:

- ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

- Latchup Current Maximum Rating: ≤ 100 mA per JEDEC standard: JÉSD78, 25°C

- 3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

**Table 3. THERMAL CHARACTERISTICS**

| Parameter                                    | Symbol          | Value | Unit |

|----------------------------------------------|-----------------|-------|------|

| Thermal Characteristics, SOIC-16 (Note 4)    |                 |       | °C/W |

| Thermal Resistance, Junction-to-Air (Note 5) | $R_{\theta JA}$ | 145   |      |

- 4. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 5. Values based on copper area of 100 mm<sup>2</sup> (or 0.16 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

Table 4. OPERATING RANGES (Note 6)

| Parameter                 | Symbol                                               | Min               | Max | Unit |

|---------------------------|------------------------------------------------------|-------------------|-----|------|

| Differential Power Supply | V <sub>CC</sub> -V <sub>EE</sub> (V <sub>max</sub> ) |                   | 30  | V    |

| Positive Power Supply     | V <sub>CC</sub>                                      | UVLO              | 20  | V    |

| Negative Power Supply     | V <sub>EE</sub>                                      | -15               | 0   | V    |

| Input Voltage             | V <sub>IN</sub>                                      | 0                 | 5   | V    |

| Enable Voltage            | V <sub>EN</sub>                                      | V <sub>EN</sub> 0 |     | V    |

| Input Pulse Width         | t <sub>on</sub>                                      | 40                |     | ns   |

| Ambient Temperature       | T <sub>A</sub>                                       | -40               | 125 | °C   |

<sup>6.</sup> Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

| Parameter                                                                                                    | Test Conditions                                                                                                                                                                | Symbol                                                         | Min                  | Тур                  | Max                             | Unit |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------|----------------------|---------------------------------|------|

| LOGIC INPUT and OUTPUT                                                                                       |                                                                                                                                                                                | ·                                                              |                      |                      |                                 |      |

| Input Threshold Voltages<br>High-state (Logic 1) Required<br>Low-state (Logic 0) Required<br>No state change | Pulse–Width = 150 ns, V <sub>EN</sub> = 5 V<br>Voltage applied to get output go high<br>Voltage applied to get output go low<br>Voltage applied without change in output state | V <sub>IN-H1</sub><br>V <sub>IN-L1</sub><br>V <sub>IN-NC</sub> | 4.3                  |                      | 0.75<br>3.7                     | V    |

| Enable Threshold Voltages<br>High–state<br>Low–state                                                         | V <sub>IN</sub> = 5 V<br>Voltage applied to get output go high<br>Voltage applied to get output go low                                                                         | V <sub>EN-H</sub><br>V <sub>EN-L</sub>                         | 4.3                  |                      | 0.75                            | V    |

| Enable Current<br>High-state<br>Low-state                                                                    | V <sub>IN-H</sub> /V <sub>EN-H</sub> = 4.5 V<br>V <sub>IN-L</sub> /V <sub>EN-L</sub> = 0.5 V                                                                                   | I <sub>EN-H</sub><br>I <sub>EN-L</sub>                         |                      |                      | 1<br>10                         | μΑ   |

| Input Current<br>High-state<br>Low-state                                                                     | V <sub>IN-H</sub> /V <sub>EN-H</sub> = 4.5 V<br>V <sub>IN-L</sub> /V <sub>EN-L</sub> = 0.5 V                                                                                   | I <sub>IN-H</sub><br>I <sub>IN-L</sub>                         |                      |                      | 10<br>1                         | μΑ   |

| Input Pulse–Width<br>No Response at the Output<br>Guaranteed Response at the<br>Output                       | Voltage thresholds consistent with input specs                                                                                                                                 | t <sub>on-min1</sub><br>t <sub>on-min2</sub>                   | 40                   |                      | 15                              | ns   |

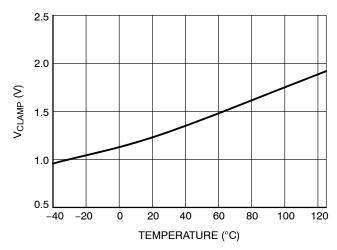

| FLT Threshold Voltage<br>Low State<br>High-state                                                             | (I <sub>FLT</sub> -SINK = 15 mA)<br>Pull-up Externally                                                                                                                         | V <sub>FLT</sub> _L<br>V <sub>FLT</sub> _H                     |                      | 0.5                  | 1.0<br>V <sub>CC</sub> +<br>0.3 | V    |

| DRIVE OUTPUT                                                                                                 |                                                                                                                                                                                | •                                                              |                      |                      |                                 |      |

| Output Low State                                                                                             | I <sub>sink</sub> = 200 mA, T <sub>A</sub> = 25°C<br>I <sub>sink</sub> = 200 mA, T <sub>A</sub> = -40°C to 125°C<br>I <sub>sink</sub> = 1.0 A, T <sub>A</sub> = 25°C           | V <sub>OL1</sub><br>V <sub>OL2</sub><br>V <sub>OL3</sub>       |                      | 0.1<br>0.2<br>0.8    | 0.2<br>0.5<br>1.2               | V    |

| Output High State                                                                                            | I <sub>src</sub> = 200 mA, T <sub>A</sub> = 25°C<br>I <sub>src</sub> = 200 mA, T <sub>A</sub> = -40°C to 125°C<br>I <sub>src</sub> = 1.0 A, T <sub>A</sub> = 25°C              | V <sub>OH1</sub><br>V <sub>OH2</sub><br>V <sub>OH3</sub>       | 14.5<br>14.2<br>13.8 | 14.8<br>14.7<br>14.1 |                                 | V    |

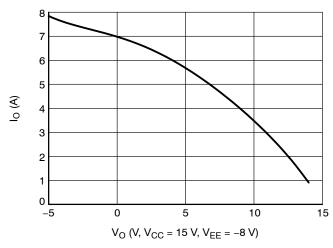

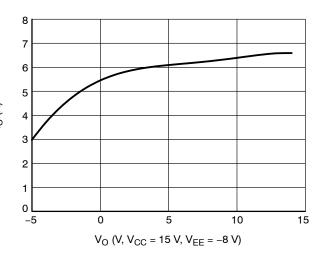

| Peak Driver Current, Sink<br>(Note 7)                                                                        | $R_G$ = 0.1 $\Omega$ , $V_{CC}$ = 15 V, $V_{EE}$ = -8 V $V_O$ = 13 V $V_O$ = 9 V (near Miller Plateau)                                                                         | I <sub>PK-snk1</sub><br>I <sub>PK-snk2</sub>                   |                      | 6.8<br>6.1           |                                 | Α    |

| Peak Driver Current, Source<br>(Note 7)                                                                      | $R_G$ = 0.1 $\Omega$ , $V_{CC}$ = 15 V, $V_{EE}$ = -8 V $V_O$ = -5 V $V_O$ = 9 V (near Miller Plateau)                                                                         | I <sub>PK-src1</sub>                                           |                      | 7.8<br>4.0           |                                 | Α    |

| DYNAMIC CHARACTERISTICS                                                                                      |                                                                                                                                                                                | 1                                                              |                      |                      |                                 | 1    |

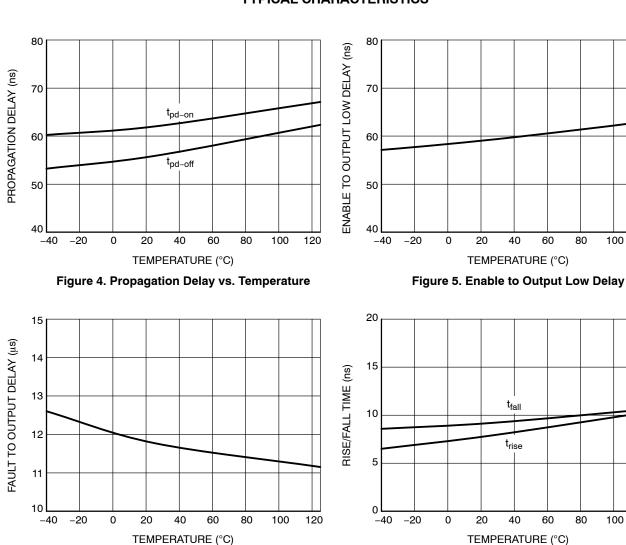

| Turn-on Delay<br>(see timing diagram)                                                                        | Positive input pulse width = 10 μs                                                                                                                                             | t <sub>pd-on</sub>                                             | 45                   | 59                   | 75                              | ns   |

| Turn-off Delay<br>(see timing diagram)                                                                       | Negative input pulse width = 10 μs                                                                                                                                             | t <sub>pd-off</sub>                                            | 45                   | 54                   | 75                              | ns   |

| Propagation Delay Distortion<br>(=t <sub>pd-on</sub> - t <sub>pd-off</sub> )                                 | For input or output pulse width > 150 ns,<br>$T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C$ to 125°C                                                                              | t <sub>distort1</sub><br>t <sub>distort2</sub>                 | -5<br>-25            | 5                    | 15<br>25                        | ns   |

| Prop Delay Distortion between Parts (Note 7)                                                                 |                                                                                                                                                                                | t <sub>distort</sub> -tot                                      | -30                  | 0                    | 30                              | ns   |

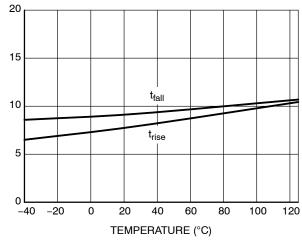

| Rise Time (Note 7)<br>(see timing diagram)                                                                   | C <sub>load</sub> = 1.0 nF                                                                                                                                                     | t <sub>rise</sub>                                              |                      | 9.2                  |                                 | ns   |

<sup>7.</sup> Values based on design and/or characterization.

$\textbf{Table 5. ELECTRICAL CHARACTERISTICS} \ V_{CC} = 15 \ V, \ V_{EE} = 0 \ V, \ Kelvin \ GND \ connected \ to \ V_{EE}. \ For \ typical \ values \ T_A = 25 ^{\circ}C, \ for \ min/max \ values, \ T_A \ is \ the \ operating \ ambient \ temperature \ range \ that \ applies, \ unless \ otherwise \ noted.$

| Parameter                                  | Test Conditions                                                                  | Symbol                    | Min  | Тур       | Max        | Unit |

|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------|------|-----------|------------|------|

| DYNAMIC CHARACTERISTICS                    |                                                                                  | •                         |      |           |            |      |

| Fall Time (Note 7)<br>(see timing diagram) | C <sub>load</sub> = 1.0 nF                                                       | t <sub>fall</sub>         |      | 7.9       |            | ns   |

| Delay from FLT under UVLO/TSD to VOL       |                                                                                  | t <sub>d1-</sub> OUT      | 9    | 12        | 15         | μs   |

| Delay from DESAT to VOL (Note 7)           |                                                                                  | t <sub>d2-OUT</sub>       |      | 220       |            | ns   |

| Delay from UVLO/TSD to FLT (Note 7)        |                                                                                  | t <sub>d3-</sub> FLT      |      | 7.3       |            | μs   |

| MILLER CLAMP                               | •                                                                                | •                         | •    | •         | •          | •    |

| Clamp Voltage                              | $I_{sink}$ = 500 mA, $T_A$ = 25°C<br>$I_{sink}$ = 500 mA, $T_A$ = -40°C to 125°C | $V_{clamp}$               |      | 1.2       | 1.4<br>2.2 | V    |

| Clamp Activation Threshold                 |                                                                                  | V <sub>MC-THR</sub>       | 1.8  | 2.0       | 2.2        | V    |

| DESAT PROTECTION                           |                                                                                  |                           |      |           |            |      |

| DESAT Threshold Voltage                    |                                                                                  | V <sub>DESAT-THR</sub>    | 6.0  | 6.35      | 7.0        | V    |

| Blanking Charge Current                    |                                                                                  | I <sub>DESAT-CHG</sub>    | 0.20 | 0.24      | 0.28       | mA   |

| Blanking Discharge Current                 |                                                                                  | I <sub>DESAT-DIS</sub>    |      | 30        |            | mA   |

| UVLO                                       |                                                                                  |                           |      |           |            |      |

| UVLO Startup Voltage                       |                                                                                  | V <sub>UVLO-OUT-ON</sub>  | 13.2 | 13.5      | 13.8       | V    |

| UVLO Disable Voltage                       |                                                                                  | V <sub>UVLO-OUT-OFF</sub> | 12.2 | 12.5      | 12.8       | V    |

| UVLO Hysteresis                            |                                                                                  | V <sub>UVLO-HYST</sub>    |      | 1.0       |            | V    |

| VREF                                       |                                                                                  |                           |      |           |            |      |

| Voltage Reference                          | I <sub>REF</sub> = 10 mA                                                         | V <sub>REF</sub>          | 4.85 | 5.00      | 5.15       | V    |

| Reference Output Current (Note 7)          |                                                                                  | I <sub>REF</sub>          |      |           | 20         | mA   |

| Recommended Capacitance                    |                                                                                  | C <sub>VREF</sub>         | 100  |           |            | nF   |

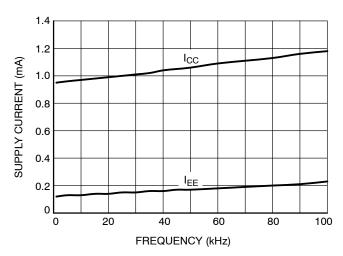

| SUPPLY CURRENT                             |                                                                                  |                           |      |           |            |      |

| Current Drawn from V <sub>CC</sub>         | V <sub>CC</sub> = 15 V<br>Standby (No load on output, <del>FLT</del> , VREF)     | I <sub>CC-SB</sub>        |      | 0.9       | 1.5        | mA   |

| Current Drawn from V <sub>EE</sub>         | V <sub>EE</sub> = -10 V<br>Standby (No load on output, FLT, VREF)                | I <sub>EE-SB</sub>        | -0.2 | -0.1<br>4 |            | mA   |

| THERMAL SHUTDOWN                           |                                                                                  |                           |      |           |            |      |

| Thermal Shutdown Temperature (Note 7)      |                                                                                  | T <sub>SD</sub>           |      | 188       |            | °C   |

| Thermal Shutdown Hysteresis (Note 7)       |                                                                                  | T <sub>SH</sub>           |      | 33        |            | °C   |

<sup>7.</sup> Values based on design and/or characterization.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### **ORDERING INFORMATION**

| Device      | Package            | Shipping <sup>†</sup> |  |  |

|-------------|--------------------|-----------------------|--|--|

| NCV5702DR2G | SO-16<br>(Pb-Free) | 2500 / Tape & Reel    |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

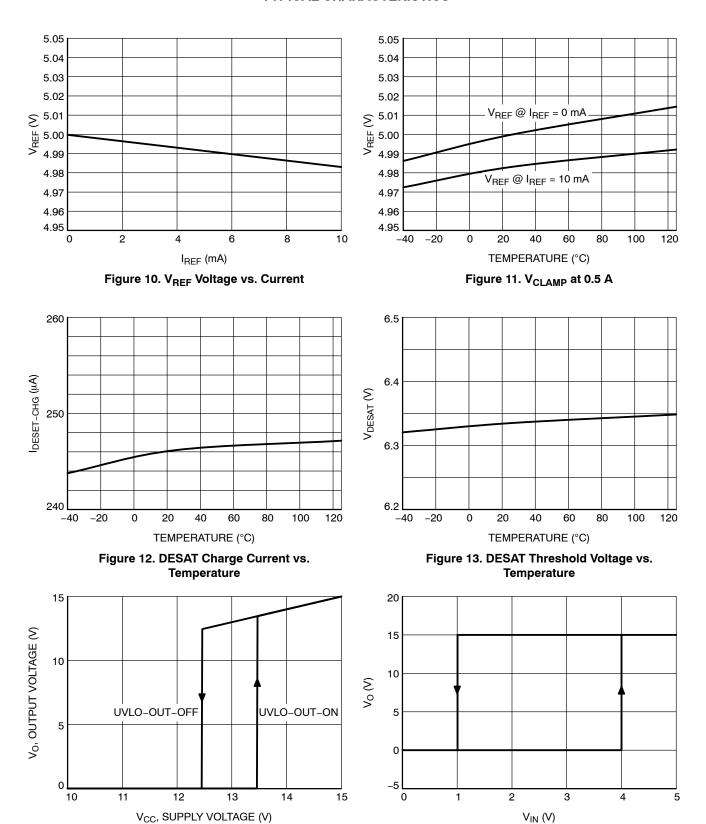

## **TYPICAL CHARACTERISTICS**

Figure 6. Fault to Output Low Delay

Figure 8. Output Source Current vs. Output Voltage

60

80

100

120

40

Figure 7. Output Rise/Fall Time

Figure 9. Output Sink Current vs. Output Voltage

### **TYPICAL CHARACTERISTICS**

Figure 14. UVLO Threshold Voltages

Figure 15.  $V_O$  vs.  $V_{IN}$  at 25°C ( $V_{CC}$  = 15 V,  $V_{EE}$  = 0 V)

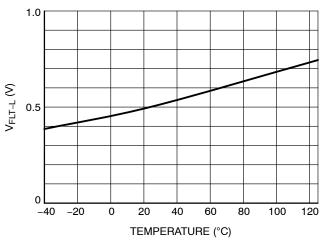

## **TYPICAL CHARACTERISTICS**

Figure 16. Fault Output, Sinking 15 mA

Figure 17. V<sub>CLAMP</sub> at 0.5 A

Figure 18. Supply Current vs. Switching Frequency ( $V_{CC}$  = 15 V,  $V_{EE}$  = -10 V, 25°C)

#### APPLICATIONS AND OPERATING INFORMATION

This section lists the details about key features and operating guidelines for the NCV5702.

## **High Drive Current Capability**

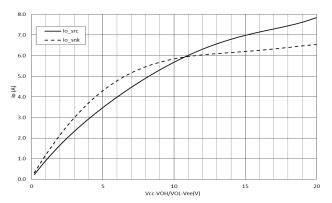

The NCV5702 driver family is equipped with many features which facilitate a superior performance IGBT driving circuit. Foremost amongst these features is the high drive current capability. The drive current of an IGBT driver is a function of the differential voltage on the output pin (V<sub>CC</sub>-VOH for source current, VOL-V<sub>EE</sub> for sink current) as shown in Figure 19. Figure 19 also indicates that for a given VOH/VOL value, the drive current can be increased by using higher V<sub>CC</sub>/V<sub>EE</sub> power supply). The drive current tends to drop off as the output voltage goes up (for turn-on event) or goes down (for turn-off event). As explained in many IGBT application notes, the most critical phase of IGBT switching event is the Miller plateau region where the gate voltage remains constant at a voltage (typically in 9–11 V range depending on IGBT design and the collector current), but the gate drive current is used to charge/discharge the Miller capacitance (C<sub>GC</sub>). By providing a high drive current in this region, a gate driver can significantly reduce the duration of the phase and help reducing the switching losses. The NCV5702 addresses this requirement by providing and specifying a high drive current in the Miller plateau region. Most other gate driver ICs merely specify peak current at the start of switching – which may be a high number, but not very relevant to the application requirement. It must be remembered that other considerations such as EMI, diode reverse recovery performance, etc., may lead to a system level decision to trade off the faster switching speed against low EMI and reverse recovery. However, the use of NCV5702 does not preclude this trade-off as the user can always tune the drive current by employing external series gate resistor. Important thing to remember is that by providing a high internal drive current capability, the NCV5702 facilitates a wide range of gate resistors. Another value of the high current at the Miller plateau is that the initial switching transition phase is shorter and more controlled. Finally, the high gate driver current (which is facilitated by low impedance internal FETs), ensures that even at high switching frequencies, the power dissipation from the drive circuit is primarily in the external series resistor and more easily manageable. Experimental results have shown that the high current drive results in reduced turn-on energy (E<sub>ON</sub>) for the IGBT switching.

Figure 19. Output Current vs. Output Voltage Drop

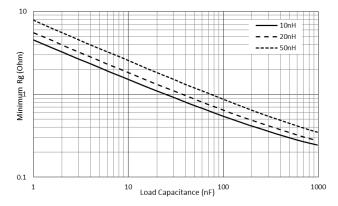

When driving larger IGBTs for higher current applications, the drive current requirement is higher, hence lower  $R_G$  is used. Larger IGBTs typically have high input capacitance. On the other hand, if the NCV5702 is used to drive smaller IGBT (lower input capacitance), the drive current requirement is lower and a higher  $R_G$  is used. Thus, for most typical applications, the driver load RC time constant remains fairly constant. Caution must be exercised when using the NCV5702 with a very low load RC time constant. Such a load may trigger internal protection circuitry within the driver and disable the device. Figure 20 shows the recommended minimum gate resistance as a function of IGBT gate capacitance and gate drive trace inductance.

Figure 20. Recommended Minimum Gate Resistance as a Function of IGBT Gate Capacitance

#### **Gate Voltage Range**

The negative drive voltage for gate (with respect to GND, or Emitter of the IGBT) is a robust way to ensure that the gate voltage does not rise above the threshold voltage due to the Miller effect. In systems where the negative power supply is available, the VEE option offered by NCV5702 allows not only a robust operation, but also a higher drive current for turn–off transition. Adequate bypassing between VEE pin and GND pin is essential if this option is used.

The  $V_{CC}$  range for the NCV5702 is quite wide and allows the user the flexibility to optimize the performance or use available power supplies for convenience.

## **Under Voltage Lock Out (UVLO)**

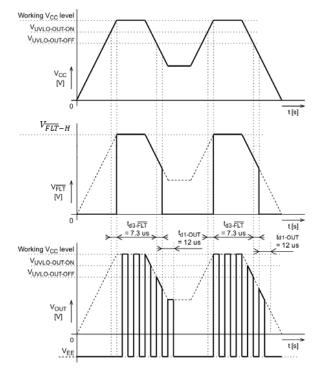

This feature ensures reliable switching of the IGBT connected to the driver output. At the start of the driver's operation when  $V_{CC}$  is applied to the driver, the output remains turned–off. This is regardless of the signals on  $V_{IN}$  until the  $V_{CC}$  reaches the UVLO Output Enabled  $(V_{UVLO-OUT-ON})$  level. After the  $V_{CC}$  rises above the  $V_{UVLO-OUT-ON}$  level, the driver is in normal operation. The state of the output is controlled by signal at  $V_{IN}$ .

If the  $V_{CC}$  falls below the UVLO Output Disabled  $(V_{UVLO-OUT-OFF})$  level during the normal operation of the driver, the Fault output is activated and the output is shut–down (after a delay) and remains in this state. The driver output does not start to react to the input signal on  $V_{IN}$  until the  $V_{CC}$  rises above the  $V_{UVLO-OUT-ON}$  again. The waveform showing the UVLO behavior of the driver is in Figure 21.

In an IGBT drive circuit, the drive voltage level is important for drive circuit optimization. If V<sub>UVI,O-OUT-OFF</sub> is too low, it will lead to IGBT being driven with insufficient gate voltage. A quick review of IGBT characteristics can reveal that driving IGBT with low voltage (in 10-12 V range) can lead to a significant increase in conduction loss. So, it is prudent to guarantee V<sub>UVLO-OUT-OFF</sub> at a reasonable level (above 12 V), so that the IGBT is not forced to operate at a non-optimum gate voltage. On the other hand, having a very high drive voltage ends up increasing switching losses without much corresponding reduction in conduction loss. So, the V<sub>UVLO-OUT-ON</sub> value should not be too high (generally, well below 15 V). These conditions lead to a tight band for UVLO enable and disable voltages, while guaranteeing a minimum hysteresis between the two values to prevent hiccup mode operation. The NCV5702 meets these tight requirements and ensures smooth IGBT operation. It ensures that a 15 V supply with ±8% tolerance will work without degrading IGBT performance, and guarantees that a fault will be reported and the IGBT will be turned off when the supply voltage drops below 12.2 V.

A UVLO event ( $V_{CC}$  voltage going below  $V_{UVLO-OUT-OFF}$ ) also triggers activation of  $\overline{FLT}$  output after a delay of  $t_{d3-FLT}$ . This indicates to the controller that the driver has encountered an issue and corrective action needs to be taken. However, a nominal delay  $t_{d1-OUT}=12~\mu s$  is introduced between the initiation of the  $\overline{FLT}$  output and actual turning off of the output. This delay provides adequate time for the

controller to initiate a more orderly/sequenced shutdown. In case the controller fails to do so, the driver output shutdown ensures IGBT protection after  $t_{d1-OUT}$ .

Figure 21. UVLO Function and Limits

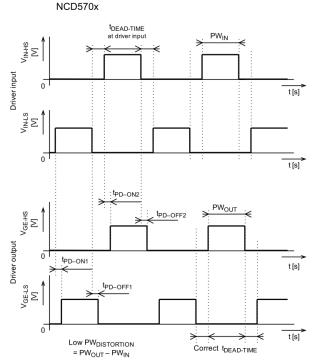

### **Timing Delays and Impact on System Performance**

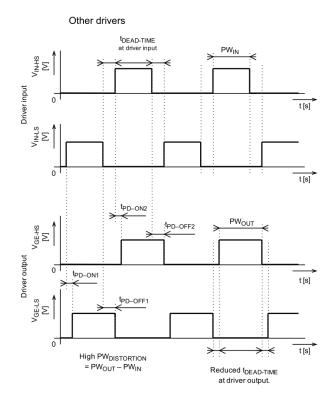

The gate driver is ideally required to transmit the input signal pulse to its output without any delay or distortion. In the context of a high-power system where IGBTs are typically used, relatively low switching frequency (in tens of kHz) means that the delay through the driver itself may not be as significant, but the matching of the delay between different drivers in the same system as well as between different edges has significant importance. With reference to Figure 22(a), two input waveforms are shown. They are typical complementary inputs for high-side (HS) and low-side (LS) of a half-bridge switching configuration. The dead-time between the two inputs ensures safe transition between the two switches. However, once these inputs are through the driver, there is potential for the actual gate voltages for HS and LS to be quite different from the intended input waveforms as shown in Figure 22(a). The end result could be a loss of the intended dead-time and/or pulse-width distortion. The pulse-width distortion can create an imbalance that needs to be corrected, while the loss of dead-time can eventually lead to cross-conduction of the switches and additional power losses or damage to the system.

The NCV5702 driver is designed to address these timing challenges by providing a very low pulse–width distortion and excellent delay matching. As an example, the delay matching is guaranteed to  $t_{DISTORT2} = \pm 25$  ns while many of competing driver solutions can be >250 ns.

Figure 22(a). Timing Waveforms (Other Drivers)

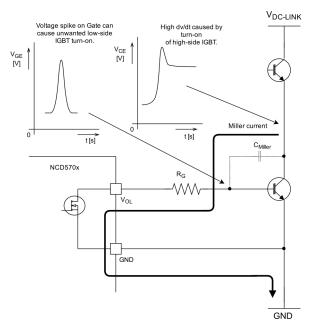

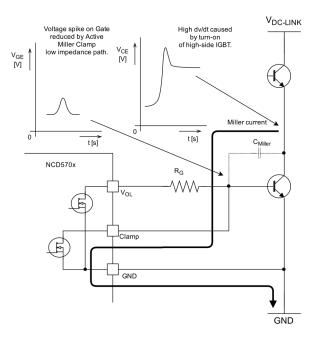

## **Active Miller Clamp Protection**

This feature is a cost savvy alternative to a negative gate voltage. The main requirement is to hold the gate of the turned-off (for example low-side) IGBT below the threshold voltage during the turn-on of the opposite-side (in this example high-side) IGBT in the half bridge. The turn-on of the high-side IGBT causes high dv/dt transition on the collector of the turned-off low-side IGBT. This high dv/dt then induces current (Miller current) through the C<sub>GC</sub> capacitance (Miller capacitance) to the gate capacitance of the low-side IGBT as shown in Figure 23. If the path from gate to GND has critical impedance (caused by R<sub>G</sub>) the Miller current could rise the gate voltage above the threshold level. As a consequence the low-side IGBT could be turned on for a few tens or hundreds of nanoseconds. This causes higher switching losses. One way to avoid this situation is to use negative gate voltage, but this requires second DC source for the negative gate voltage.

Figure 22(b). NCV5702 Timing Waveforms

An alternative way is to provide an additional path from gate to GND with very low impedance. This is exactly what Active Miller Clamp protection does. Additional trace from the gate of the IGBT to the Clamp pin of the gate driver is introduced. After the  $V_{\rm O}$  output has gone below the Active Miler Clamp threshold  $V_{\rm MC-THR}$  the Clamp pin is shorted to GND and thus prevents the voltage on the gate of the IGBT to rise above the threshold voltage as shown in Figure 24. The Clamp pin is disconnected from GND as soon as the signal to turn on the IGBT arrives to the gate driver input. The fact that the Clamp pin is engaged only after the gate voltage drops below the  $V_{\rm MC-THR}$  threshold ensures that the function of this pin does not interfere with the normal turn–off switching performance that is user controllable by choice of  $R_{\rm G}$ .

Figure 23. Current Path without Miller Clamp Protection

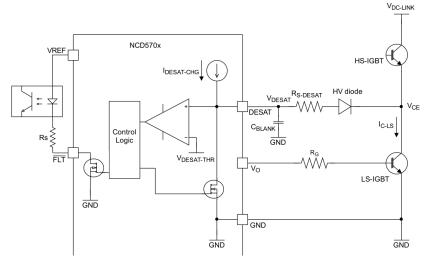

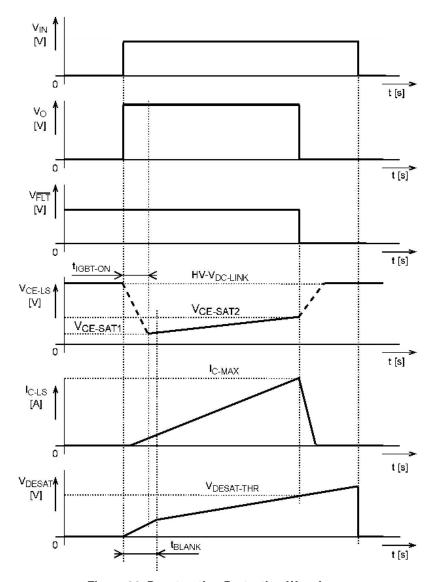

#### **Desaturation Protection (DESAT)**

This feature monitors the collector–emitter voltage of the IGBT in the turned–on state. When the IGBT is fully turned on, it operates in a saturation region. Its collector–emitter voltage (called saturation voltage) is usually low, well below 3 V for most modern IGBTs. It could indicate an overcurrent or similar stress event on the IGBT if the collector–emitter voltage rises above the saturation voltage, after the IGBT is fully turned on. Therefore the DESAT protection circuit compares the collector–emitter voltage with a voltage level VDESAT-THR to check if the IGBT didn't leave the saturation region. It will activate FLT output and shut down driver output (thus turn–off the IGBT), if the saturation voltage rises above the VDESAT-THR. This protection works on every turn–on phase of the IGBT switching period.

At the beginning of turning—on of the IGBT, the collector—emitter voltage is much higher than the saturation voltage level which is present after the IGBT is fully turned on. It takes almost 1 µs between the start of the IGBT turn—on and the moment when the collector—emitter voltage falls to the saturation level. Therefore the comparison is delayed by a configurable time period (blanking time) to prevent false triggering of DESAT protection before the IGBT collector—emitter voltage falls below the saturation level. Blanking time is set by the value of the capacitor C<sub>BLANK</sub>.

The exact principle of operation of DESAT protection is described with reference to Figure 25.

At the turned-off output state of the driver, the DESAT pin is shorted to ground via the discharging transistor ( $Q_{DIS}$ ). Therefore, the inverting input holds the comparator output at low level.

Figure 24. Current Path with Miller Clamp Protection

At the turned–on output state of the driver, the current  $I_{DESAT-CHG}$  from current source starts to flow to the blanking capacitor  $C_{BLANK}$ , connected to DESAT pin. Appropriate value of this capacitor has to be selected to ensure that the DESAT pin voltage does not rise above the threshold level  $V_{DESAT-THR}$  before the IGBT fully turns on. The blanking time is given by following expression. According to this expression, a 47 pF  $C_{BLANK}$  will provide a blanking time of  $(47p *6.5/0.25m =) 1.22 \mu s$ .

$$t_{BLANK} = C_{BLANK} \cdot \frac{V_{DESAT-THR}}{I_{DESAT-CHG}}$$

After the IGBT is fully turned—on, the  $I_{DESAT-CHG}$  flows through the DESAT pin to the series resistor  $R_{S-DESAT}$  and through the high voltage diode and then through the collector and IGBT to the emitter. Care must be taken to select the resistor  $R_{S-DESAT}$  value so that the sum of the saturation voltage, drop on the HV diode and drop on the  $R_{S-DESAT}$  caused by current  $I_{DESAT-CHG}$  flowing from DESAT source current is smaller than the DESAT threshold voltage. Following expression can be used:

$$V_{DESAT-THR} >$$

$R_{S-DESAT} \cdot I_{DESAT-CHG} + V_{F\_HV \, diode} + V_{CESAT\_IGBT}$

Important part for DESAT protection to work properly is the high voltage diode. It must be rated for at least same voltage as the low side IGBT. The safety margin is application dependent.

The typical waveforms for IGBT overcurrent condition are outlined in Figure 26.

Figure 25. Desaturation Protection Schematic

Figure 26. Desaturation Protection Waveforms

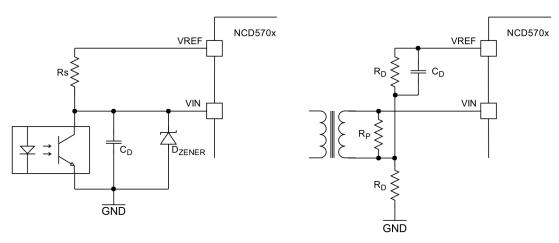

### **Input Signal**

The input signal controls the gate driver output. Figure 27 shows the typical connection diagrams for isolated

applications where the input is coming through an opto-coupler or a pulse transformer.

Figure 27. Opto-coupler or Pulse Transformer At Input

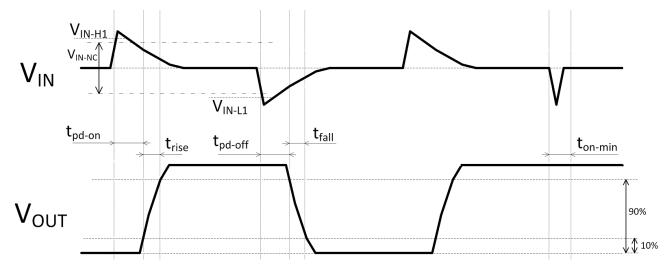

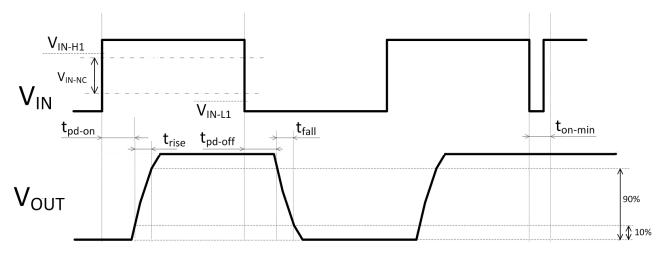

The relationship between gate driver input signal from a pulse transformer (Figure 28) or opto–coupler (Figure 29) and the output is defined by many time and voltage values. The time values include output turn–on and turn–off delays ( $t_{pd-on}$  and  $t_{pd-off}$ ), output rise and fall times ( $t_{rise}$  and  $t_{fall}$ ) and minimum input pulse–width ( $t_{on-min}$ ). Note that the

delay times are defined from 50% of input transition to first 10% of the output transition to eliminate the load dependency. The input voltage parameters include input high  $(V_{IN-H1})$  and low  $(V_{IN-L1})$  thresholds as well as the input range for which no output change is initiated  $(V_{IN-NC}).$

Figure 28. Input and Output Signal Parameters for Pulse Transformer

Figure 29. Input and Output Signal Parameters for Opto-coupler

### **Use of VREF Pin**

The NCV5702 provides an additional 5.0 V output (VREF) that can serve multiple functions. This output is capable of sourcing up to 10 mA current for functions such as opto-coupler interface or external comparator interface. The VREF pin should be bypassed with at least a 100 nF capacitor (higher the better) irrespective of whether it is being utilized for external functionality or not. VREF is

highly stable over temperature and line/load variations (see characteristics curves for details)

## **Fault Output Pin**

This pin provides the feedback to the controller about the driver operation. The situations in which the FLT signal becomes active (low value) are summarized in the Table 6.

| Table 6 | FITI | OGIC | TRUTH | TABLE |

|---------|------|------|-------|-------|

|         |      |      |       |       |

| VIN | ENABLE | UVLO     | DESAT | Internal TSD | VOUT | FLT        | Notes                                                                                                                  |

|-----|--------|----------|-------|--------------|------|------------|------------------------------------------------------------------------------------------------------------------------|

| L   | Н      | Inactive | L     | L            | L    | open-drain | Normal operation – Output Low                                                                                          |

| Н   | Н      | Inactive | L     | L            | Н    | open-drain | Normal operation – Output High                                                                                         |

| Х   | L      | Inactive | Х     | L            | L    | open-drain | Disabled - Output Low, FLT open-drain                                                                                  |

| Х   | Х      | Active   | Х     | L            | L    | L          | UVLO activated – $\overline{FLT}$ Low $(t_{d3-}\overline{FLT})$ , Output Low $(t_{d3-}\overline{FLT})$ + $t_{d1-}OUT)$ |

| Н   | Н      | Inactive | Н     | L            | L    | L          | DESAT activated (only when $V_{IN}$ is High) – Output Low ( $t_{d2\_OUT}$ ), FLT Low                                   |

| Х   | Х      | Inactive | X     | Н            | L    | L          | Internal Thermal Shutdown - FLT Low (t <sub>d3-FLT</sub> ), Output Low (t <sub>d3-FLT</sub> + t <sub>d1-OUT</sub> )    |

#### **Thermal Shutdown**

The NCV5702 also offers thermal shutdown function that is primarily meant to self-protect the driver in the event that the internal temperature gets excessive. Once the temperature crosses the  $T_{SD}$  threshold, the  $\overline{FLT}$  output is activated after a delay of  $t_{d3-\overline{FLT}}$ . After a delay of  $t_{d1-OUT}$

$(12 \,\mu s)$ , the output is pulled low and many of the internal circuits are turned off. The 12  $\mu s$  delay is meant to allow the controller to perform an orderly shutdown sequence as appropriate. Once the temperature goes below the second threshold, the part becomes active again.

## **Additional Use of Enable Pin**

For some applications, Enable is a useful feature as it provides the ability to shut down the power stage without involving the controls such as DSP. It can also be used along

with the VREF pin and a comparator to provide local shutdown protection at fault conditions such as over temperature or over current, as illustrated in Figure 30.

Figure 30. Additional Over Temperature and/or Over Current Shutdown Protection

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

**TECHNICAL PUBLICATIONS:**

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales