# Micro-stepping Motor Driver NCV70517

#### Description

The NCV70517 is a micro-stepping stepper motor driver for bipolar stepper motors. The chip is connected through I/O pins and an SPI interface with an external microcontroller. The NCV70517 contains a current-translation table and takes the next micro-step depending on the clock signal on the "NXT" input pin and the status of the "DIR" (= direction) register or input pin. The chip provides an error message if an electrical error, an under-voltage or an elevated junction temperature is detected. It is using a proprietary PWM algorithm for reliable current control.

NCV70517 is fully compatible with the automotive voltage requirements and is ideally suited for general-purpose stepper motor applications in the automotive, industrial, medical, and marine environment.

Due to the technology, the device is especially suited for use in applications with fluctuating battery supplies.

#### **Features**

- Dual H-bridge for 2-phase Stepper Motors

- Programmable Peak-current up to 800 mA

- Low Temperature Boost Current up to 1100 mA

- On-chip Current Translator

- SPI Interface

- 5 Step Modes from Full-step up to 16 Micro-steps

- Fully Integrated Current-sensing and Current-regulation

- Back-EMF Measurement

- On Chip Stall Detection

- PWM Current Control with Automatic Selection of Fast and Slow Decay

- Fixed PWM Frequency

- Active Fly-back Diodes

- Full Output Protection and Diagnosis

- Thermal Warning and Shutdown

- Compatible with 3.3 V Microcontrollers, 5 V Tolerant Inputs, 5 V Tolerant Open Drain Outputs

- Reset Function

- Overcurrent Protection

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

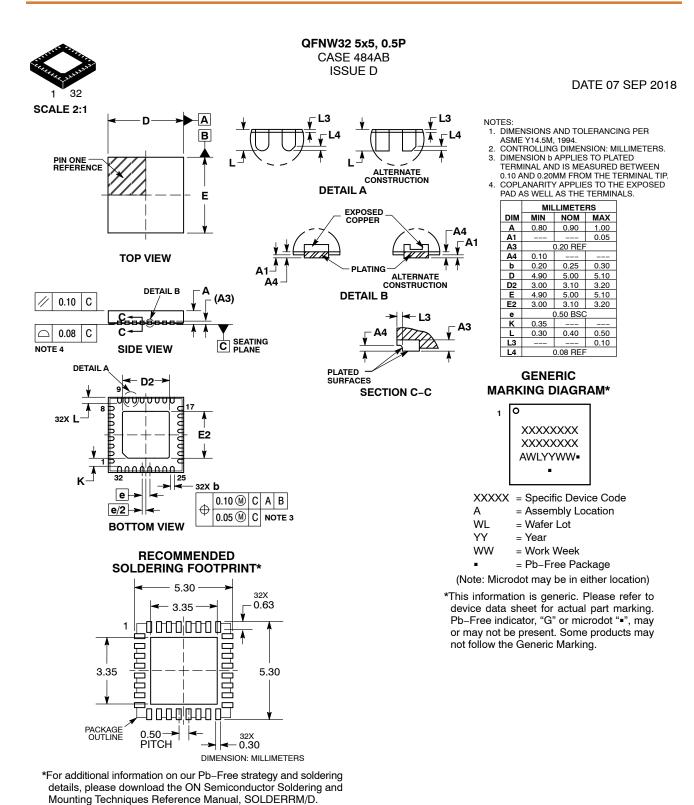

QFNW32 CASE 484AB

#### **MARKING DIAGRAM**

N70517-2 = Specific Device Code

F = Fab Location

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

#### ORDERING INFORMATION

= Pb-Free Package

See detailed ordering and shipping information in the package dimensions section on page 24 of this data sheet.

1

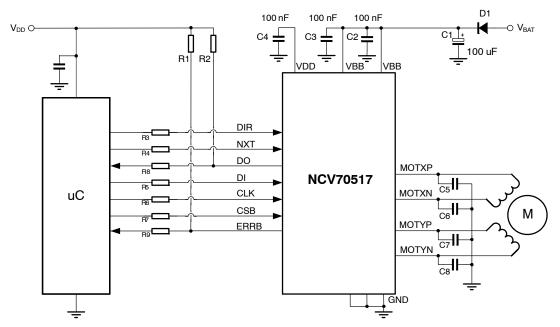

#### TYPICAL APPLICATION SCHEMATIC

The application schematic below shows typical connections for applications with low axis counts and/or with software SPI implementation. For applications with

many stepper motor drivers, some "minimal wiring" examples are shown at the last sections of this datasheet.

Figure 1. Typical Application Schematic

**Table 1. EXTERNAL COMPONENTS**

| Component      | Function                                               | Typ. Value   | Max Tolerance | Unit |

|----------------|--------------------------------------------------------|--------------|---------------|------|

| C1             | V <sub>BB</sub> buffer capacitor (Note 1)              | 22 100       | ±20%          | μF   |

| C2, C3         | V <sub>BB</sub> decoupling capacitor (Note 2)          | 100          | ±20%          | nF   |

| C4             | Optional V <sub>DD</sub> decoupling capacitor (Note 3) | 100          | ±20%          | nF   |

| C5, C6, C7, C8 | Optional EMC filtering capacitor (Note 4)              | 1 3.3 max    | ±20%          | nF   |

| R1, R2         | Pull up resistor                                       | 15           | ±10%          | kΩ   |

| R3 – R7        | Optional resistors                                     | 1            | ±10%          | kΩ   |

| R8, R9         | Optional resistors (Note 5)                            | 100          | ±10%          | Ω    |

| D1             | Optional reverse protection diode                      | e.g. MURD530 |               |      |

<sup>1.</sup> Low ESR <  $4 \Omega$ , mounted as close as possible to the NCV70517. Total decoupling capacitance value has to be chosen properly to reduce the supply voltage ripple and to avoid EM emission.

<sup>2.</sup> C2 and C3 must be close to pins VBB and coupled GND directly.

<sup>3.</sup> Radiated emissions around 100 MHz can be improved by avoiding this capacitor.

<sup>4.</sup> Optional capacitors for improvement of EMC and system ESD performance. The slope times on motor pins can be longer than specified in the AC table.

<sup>5.</sup> Value depends on characteristics of  $\mu\text{C}$  inputs for DO and ERRB signals.

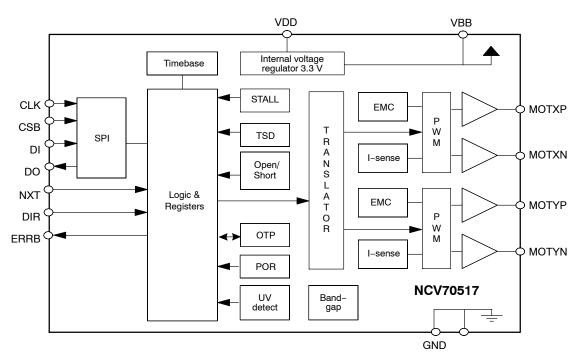

Figure 2. Block Diagram

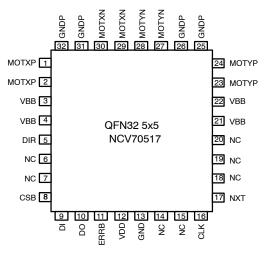

# PACKAGE AND PIN DESCRIPTION

Figure 3. Pin Connections – QFNW32 5x5

# **Table 2. PIN DESCRIPTION**

| Pin No.<br>QFNW32 5x5    | Pin Name | Description                  | I/O Type       |

|--------------------------|----------|------------------------------|----------------|

| 1, 2                     | MOTXP    | Positive end of phase X coil | Driver Output  |

| 3, 4, 21, 22             | VBB      | Battery voltage supply       | Supply         |

| 5                        | DIR      | Direction input              | Digital Input  |

| 6, 7, 14, 15, 18, 19, 20 | NC       | Not Connected                |                |

| 8                        | CSB      | SPI chip select input        | Digital Input  |

| 9                        | DI       | SPI data input               | Digital Input  |

| 10                       | DO       | SPI data output (Open Drain) | Digital Output |

| 11                       | ERRB     | Error Output (Open Drain)    | Digital Output |

| 12                       | VDD      | Internal supply              | Supply         |

| 13                       | GND      | Ground                       | Supply         |

| 16                       | CLK      | SPI clock input              | Digital Input  |

| 17                       | NXT      | Next micro-step input        | Digital Input  |

| 23, 24                   | MOTYP    | Positive end of phase Y coil | Driver Output  |

| 25, 26, 31, 32           | GNDP     | Ground                       | Supply         |

| 27, 28                   | MOTYN    | Negative end of phase Y coil | Driver Output  |

| 29, 30                   | MOTXN    | Negative end of phase X coil | Driver Output  |

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Symbol                | Characteristic                                   | Min  | Max  | Unit |

|-----------------------|--------------------------------------------------|------|------|------|

| $V_{BB}$              | Supply voltage (Note 6)                          | -0.3 | +40  | V    |

| V <sub>IO</sub>       | Digital input/outputs voltage                    | -0.3 | +6.0 | V    |

| Tj                    | Junction temperature range (Note 7)              | -50  | +175 | °C   |

| T <sub>strg</sub>     | Storage Temperature (Note 8)                     | -55  | +160 | °C   |

| V <sub>esd_hbm</sub>  | HBM Electrostatic discharge voltage (Note 9)     | -2   | +2   | kV   |

| V <sub>syst_esd</sub> | System Electrostatic discharge voltage (Note 10) | -8   | +8   | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 6. V<sub>BB</sub> Max is +43 V for limited time < 0.5 s.

- 7. The circuit functionality is not guaranteed.

- 8. For limited time up to 100 hours. Otherwise the max storage temperature is 85°C.

- 9. HBM according to AEC-Q100: EIA-JESD22-A114-B (100 pF via 1.5 kΩ).

- 10. System ESD, 150 pF, 330  $\Omega$ , contact discharge on the connector pin, unpowered.

Operating ranges define the limits for functional operation and parametric characteristics of the device. A mission profile (Note 11) is a substantial part of the

operation conditions; hence the Customer must contact **onsemi** in order to mutually agree in writing on the allowed missions profile(s) in the application.

**Table 4. RECOMMENDED OPERATING RANGES**

| Symbol          | Characteristic                                            | Min | Тур | Max  | Unit |

|-----------------|-----------------------------------------------------------|-----|-----|------|------|

| $V_{BB}$        | Battery Supply voltage                                    | +6  |     | +29  | V    |

| V <sub>IO</sub> | Digital input/outputs voltage                             | 0   |     | +5.5 | V    |

| T <sub>jp</sub> | Parametric operating junction temperature range (Note 12) | -40 |     | +145 | °C   |

| T <sub>jf</sub> | Functional operating junction temperature range (Note 13) | -40 |     | +160 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

## **Package Thermal Characteristic**

The NCV70517 is available in a thermally optimized QFNW32 5x5 package. For the optimizations, the package has an exposed thermal pad which has to be soldered to the PCB ground plane. The ground plane needs thermal vias to conduct the heat to the bottom layer.

For precise thermal cooling calculations the major thermal resistances of the devices are given. The thermal media to which the power of the devices has to be given are:

- Static environmental air (via the case)

- PCB board copper area (via the device pins and exposed pad)

The major thermal resistances of the device are the Rth from the junction to the ambient (Rthja) and the Rth from the junction to the exposed pad (Rthjp).

Using an exposed die pad on the bottom surface of the package is mainly contributing to this performance. In order to take full advantage of the exposed pad, it is most important that the PCB has features to conduct heat away from the package. In the table below, one can find the values for the Rthja and Rthjp:

**Table 5. THERMAL RESISTANCE**

| Package    | Rth, Junction-to-Exposed Pad, Rthjp |

|------------|-------------------------------------|

| QFNW32 5x5 | 6 K/W                               |

<sup>11.</sup> A mission profile describes the application specific conditions such as, but not limited to, the cumulative operating conditions over life time, the system power dissipation, the system's environmental conditions, the thermal design of the customer's system, the modes, in which the device is operated by the customer, etc. No more than 100 cumulated hours in life time above T<sub>tw</sub>.

<sup>12.</sup> The parametric characteristics of the circuit are not guaranteed outside the Parametric operating junction temperature range.

<sup>13.</sup> The maximum functional operating temperature range can be limited by thermal shutdown Ttsd.

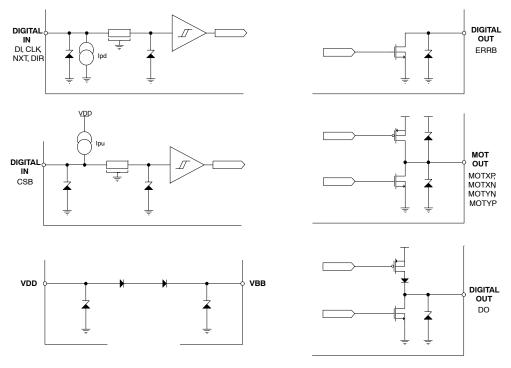

# **EQUIVALENT SCHEMATICS**

The following figure gives the equivalent schematics of the user relevant inputs and outputs. The diagrams are simplified representations of the circuits used.

Figure 4. Input and Output Equivalent Diagrams

# **ELECTRICAL CHARACTERISTICS**

# DC PARAMETERS

The DC parameters are guaranteed over junction temperature from -40 to 145°C and VBB in the operating

range from 6 to 29 V, unless otherwise specified. Convention: currents flowing into the circuit are defined as positive.

**Table 6. DC PATAMETERS**

| Symbol                    | Pin(s)                  | Parameter                                                                 | Test Conditions                                                                                  | Min | Тур  | Max | Uni-<br>t |

|---------------------------|-------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|-----|-----------|

| MOTORDRIVE                | R                       |                                                                           |                                                                                                  |     |      |     |           |

| I <sub>MSmax,Peak</sub>   | MOTXP<br>MOTXN<br>MOTYP | Max current through motor coil in normal operation                        | V <sub>BB</sub> = 14 V                                                                           |     | 800  |     | mA        |

| I <sub>MSboost,Peak</sub> | MOTYN                   | Max current during booster function                                       | $V_{BB} = 14 \text{ V}, T_j = -45^{\circ}\text{C}$                                               |     | 1100 |     | mA        |

| <sup>I</sup> MSabs        |                         | Absolute error on coil current                                            | V <sub>BB</sub> = 14 V, T <sub>j</sub> = 145°C<br>I <sub>MSmax,Peak</sub> = 800 mA<br>and 100 mA | -10 |      | 10  | %         |

| I <sub>MSrel</sub>        |                         | Matching of X & Y coil currents                                           | V <sub>BB</sub> = 14 V<br>I <sub>MSmax,Peak</sub> = 800 mA<br>and 100 mA                         | -7  |      | 7   | %         |

| R <sub>DS(on)</sub>       |                         | On resistance of High side + Low side Driver at the highest current range | T <sub>j</sub> = 145°C                                                                           |     |      | 2.4 | Ω         |

| $R_{mpd}$                 |                         | Motor pin pull-down resistance                                            | HiZ mode                                                                                         |     | 70   |     | kΩ        |

Table 6. DC PATAMETERS (continued)

| Symbol                  | Pin(s)          | Parameter                                                         | Test Conditions                                         | Min                   | Тур | Max      | Uni-<br>t |

|-------------------------|-----------------|-------------------------------------------------------------------|---------------------------------------------------------|-----------------------|-----|----------|-----------|

| LOGIC INPU              | тѕ              |                                                                   | •                                                       | •                     |     | •        | <u></u>   |

| V <sub>inL</sub>        | CSB             | Logic low input level, max                                        |                                                         |                       |     | 0.8      | V         |

| V <sub>inH</sub>        |                 | Logic high input level, min                                       |                                                         | 2.4                   |     |          | V         |

| I <sub>inL_pu</sub>     | 1               | Input pull up current for logic low level (Note 14)               |                                                         |                       | 25  |          | μΑ        |

| I <sub>inL_pu_slp</sub> | 1               | Input pull up current for logic low level in sleep mode (Note 14) |                                                         |                       |     | 3        | μΑ        |

| I <sub>inH_pu</sub>     |                 | Input leakage current for logic high level                        |                                                         |                       |     | 1        | μΑ        |

| V <sub>inL</sub>        | DI, CLK         | Logic low input level, max                                        |                                                         |                       |     | 0.8      | V         |

| V <sub>inH</sub>        |                 | Logic high input level, min                                       |                                                         | 2.4                   |     |          | V         |

| R <sub>inpd</sub>       |                 | DI, CLK pin pull-down resistance (Note 14)                        |                                                         | 75                    | 150 | 300      | kΩ        |

| V <sub>inL</sub>        | NXT, DIR        | Logic low input level, max                                        |                                                         |                       |     | 0.8      | V         |

| V <sub>inH</sub>        |                 | Logic high input level, min                                       |                                                         | 2.4                   |     |          | V         |

| R <sub>inpd</sub>       | 1               | NXT, DIR pin pull-down resistance (Note 14)                       |                                                         | 75                    | 150 | 300      | kΩ        |

| OPEN DRAIN              | LOGIC OUT       | PUT                                                               |                                                         |                       |     | •        |           |

| V <sub>OLmax</sub>      | ERRB            | Output voltage                                                    | 6 mA sink current                                       |                       |     | 0.4      | V         |

| V <sub>OHmax</sub>      |                 | Maximum drain voltage                                             |                                                         |                       |     | 5.5      | V         |

| I <sub>OLmax</sub>      | 1               | Maximum allowed drain current (Note 22)                           |                                                         |                       |     | 12       | mA        |

| PUSH-PULL               | LOGIC OUTF      | PUT WHEN CSB = 0 (Figure 4)                                       |                                                         | <u> </u>              |     | <u>I</u> | .4        |

| V <sub>OLmax</sub>      | DO              | Output voltage low                                                | 6 mA sink current                                       |                       |     | 0.4      | V         |

| V <sub>OHmin</sub>      |                 | Output voltage high without pull-up                               | 4 mA source current                                     | V <sub>DD</sub> – 1.3 |     |          | V         |

| V <sub>OHmax</sub>      |                 | Maximum pin voltage                                               |                                                         |                       |     | 5.5      | V         |

| I <sub>OLmax</sub>      | 1               | Maximum allowed pin current (Note 22)                             |                                                         |                       |     | 12       | mA        |

| THERMAL W               | ARNING & SI     | HUTDOWN                                                           |                                                         | <u> </u>              |     | <u>I</u> | .4        |

| T <sub>tw</sub>         |                 | Thermal warning (Notes 15 and 16)                                 |                                                         | 135                   | 145 | 155      | °C        |

| T <sub>tsd</sub>        |                 | Thermal shutdown (Note 17)                                        |                                                         | 155                   | 165 | 175      | °C        |

| T <sub>low</sub>        |                 | Low temperature level (Note 15)                                   |                                                         | 12                    | 28  | 44       | °C        |

| SUPPLY AND              | VOLTAGE R       | EGULATOR                                                          |                                                         |                       |     | l        |           |

| UV                      | V <sub>BB</sub> | H-Bridge off voltage low threshold                                |                                                         | 5.7                   | 6.0 | 6.3      | V         |

| UV_HYST                 |                 | Under voltage hysteresis                                          |                                                         | 100                   | 250 | 600      | mV        |

| I <sub>bat</sub>        | 1               | Total current consumption (Note 18)                               | Unloaded outputs<br>V <sub>BB</sub> = 29 V              |                       | 4   | 15       | mA        |

| I <sub>bat_s</sub>      | 1               | Sleep mode current consumption at temperature ≤ 85°C (Note 19)    | V <sub>BB</sub> = 5.5 V & 18 V<br>T <sub>j</sub> ≤ 85°C |                       | 12  | 20       | μΑ        |

| V <sub>DD</sub>         | V <sub>DD</sub> | Regulated internal supply (Note 20)                               | 5.5 V < V <sub>BB</sub> < 29 V<br>Load = 0 mA, 15 mA    | 3.0                   | 3.3 | 3.6      | V         |

| V <sub>ddReset</sub>    | 1               | Digital supply reset level @ power down (Note 21)                 |                                                         |                       |     | 3.0      | ٧         |

| I <sub>ddLim</sub>      | 1               | Current limitation                                                | Pin shorted to ground V <sub>BB</sub> = 14 V            |                       |     | 80       | mA        |

- 14. All Pull-up and pull down currents stay activated during sleep to avoid floating input pins. Placing the pin in wrong state during sleep results in higher sleep currents in the application.

- 15. Thermal warning and low temperature level are derived from thermal shutdown ( $T_{tw} = T_{tsd} 20^{\circ}C$ ,  $T_{low} = T_{tsd} 137^{\circ}C$ ).

- 16. No more than 100 cumulated hours in life time above T<sub>tw</sub>.

17. Parameter guaranteed by trimming relevant OTPs in production test at 160°C and VBB = 14 V.

- 18. Dynamic current is with oscillator running, all analogue cells active. Coil currents 0 mA, SPI active, ERRB inactive, no floating inputs.

- 19. All outputs unloaded, no floating inputs. Not tested in production, guaranteed by device characterization.

- 20. Pin VDD must not be used for any external supply.

- 21. The SPI registers content will not be altered above this voltage.

- 22. Maximum allowed drain current that the output can withstand without getting damaged. Not tested in production.

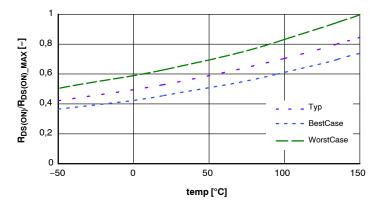

Figure 5. ON Resistance of High Side + Low Side Driver at the Highest Current Range

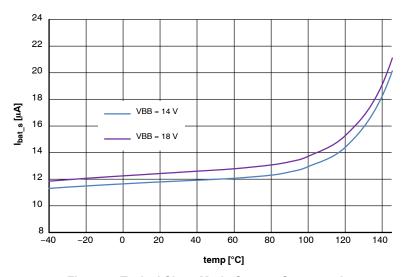

Figure 6. Typical Sleep Mode Current Consumption

# **AC PARAMETERS**

The AC parameters are guaranteed over junction temperature from -40 to 145 °C and VBB in the operating range from 6 to 29 V, unless otherwise specified.

Table 7. AC PARAMETERS

| Symbol                 | Pin(s)      | Parameter                                                                              | Test Conditions                              | Min | Тур  | Max                 | Unit |

|------------------------|-------------|----------------------------------------------------------------------------------------|----------------------------------------------|-----|------|---------------------|------|

| NTERNAL OS             | CILLATOR    |                                                                                        |                                              |     |      |                     |      |

| f <sub>osc</sub>       |             | Frequency of internal oscillator                                                       | V <sub>BB</sub> = 14 V                       | 9   | 10   | 11                  | MHz  |

| MOTORDRIVE             | R           |                                                                                        |                                              |     | •    |                     | •    |

| f <sub>pwm</sub>       | MOTxx       | PWM frequency                                                                          | (Note 23)                                    |     | 28.4 |                     | kHz  |

| f <sub>jit_depth</sub> |             | PWM jitter modulation depth                                                            | SPI bit PWMJen = 1<br>(Note 23)              |     |      | 20                  | %    |

| t <sub>OCdet</sub>     | 1           | Open coil detection with                                                               | SPI bit OpenDet [1:0] = 00                   |     | 5    |                     | ms   |

|                        |             | PWM = 100% (Note 23)                                                                   | SPI bit OpenDet [1:0] = 01                   |     | 25   |                     |      |

|                        |             |                                                                                        | SPI bit OpenDet [1:0] = 10                   |     | 50   |                     |      |

|                        |             |                                                                                        | SPI bit OpenDet [1:0] = 11                   |     | 200  |                     |      |

| t <sub>brise</sub>     |             | Turn-on transient time, between                                                        | SPI bit EMC [1:0] = 00                       |     | 150  |                     | ns   |

|                        |             | 10% and 90%, $I_{MD}$ = 300 mA, $V_{BB}$ = 13.5 V, 1 nF at motor pins                  | SPI bit EMC [1:0] = 01                       |     | 300  |                     |      |

|                        |             |                                                                                        | SPI bit EMC [1:0] = 10                       |     | 1000 |                     |      |

|                        |             |                                                                                        | SPI bit EMC [1:0] = 11                       |     | 2000 |                     |      |

| t <sub>bfall</sub>     |             | Turn-off transient time, between                                                       | SPI bit EMC [1:0] = 00                       |     | 150  |                     | ns   |

|                        |             | 10% and 90%, I <sub>MD</sub> = 200 mA,<br>V <sub>BB</sub> = 13.5 V, 1 nF at motor pins | SPI bit EMC [1:0] = 01                       |     | 300  |                     |      |

|                        |             |                                                                                        | SPI bit EMC [1:0] = 10                       |     | 1000 |                     | 1    |

|                        |             |                                                                                        | SPI bit EMC [1:0] = 11                       |     | 2000 |                     |      |

| UV <sub>time</sub>     | MOTxx       | Under-voltage debounce time                                                            | SPI bit UVtime [1:0] = 00                    |     | 0    |                     | ms   |

|                        |             | (Note: H-bridge off)                                                                   | SPI bit UVtime [1:0] = 01                    |     | 5    |                     |      |

|                        |             |                                                                                        | SPI bit UVtime [1:0] = 10                    |     | 10   |                     | 1    |

|                        |             |                                                                                        | SPI bit UVtime [1:0] = 11                    |     | 30   |                     |      |

| DIGITAL OUTF           | UTS         |                                                                                        |                                              |     | •    | •                   |      |

| t <sub>H2L</sub>       | DO,<br>ERRB | Output fall-time (90% to 10%) from V <sub>InH</sub> to V <sub>InL</sub>                | Capacitive load 200 pF<br>and pull-up 1.5 kΩ |     |      | 50                  | ns   |

| HARD RESET             | FUNCTION    |                                                                                        |                                              |     | •    |                     | •    |

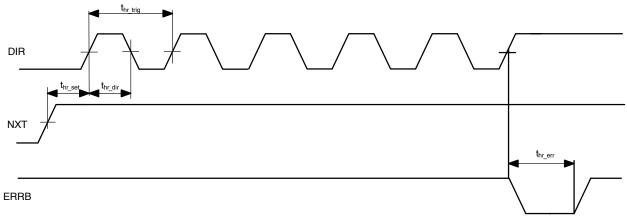

| t <sub>hr_trig</sub>   | DIR         | Hard reset trigger time (Note 23)                                                      | See hard reset function                      | 20  |      |                     | μs   |

| t <sub>hr_dir</sub>    |             | Hard reset DIR pulse width                                                             | (Note 23)                                    | 2.5 |      |                     | μs   |

| t <sub>hr_set</sub>    | NXT         | NXT set-up time                                                                        | (Note 23)                                    | 2.5 |      |                     | μs   |

| t <sub>hr_err</sub>    | ERRB        | Hard reset error indication                                                            | (Note 23)                                    |     | 50   |                     | μs   |

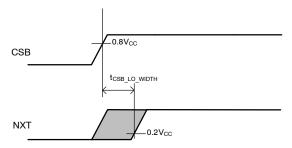

| t <sub>csb_width</sub> | CSB         | CSB wake-up low pulse width                                                            | (Note 23)                                    | 2   |      | 150                 | μs   |

| t <sub>csb_no_wu</sub> |             | CSB no wake-up low pulse width                                                         | (Note 23)                                    | 220 |      |                     | μs   |

| t <sub>wu</sub>        |             | Wake-up time                                                                           | See Sleep Mode                               | 250 |      |                     | μs   |

| NXT/DIR INPU           | TS          |                                                                                        |                                              |     |      |                     | •    |

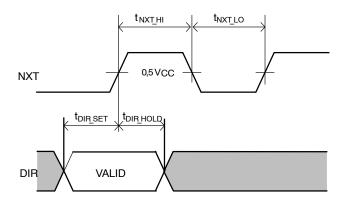

| t <sub>NXT_HI</sub>    | NXT         | NXT minimum, high pulse width                                                          |                                              | 2   |      |                     | μs   |

| t <sub>NXT</sub> LO    | 1           | NXT minimum, low pulse width                                                           |                                              | 2   |      |                     | μs   |

| f <sub>NXT</sub>       | 1           | NXT max repetition rate                                                                |                                              |     |      | f <sub>PWM</sub> /2 | kHz  |

| CSB_LO_WIDT-<br>H      |             | NXT pin trigger after SPI NXT command                                                  |                                              | 1   |      |                     | μs   |

**Table 7. AC PARAMETERS**

| Symbol                | Pin(s)   | Parameter                             | Test Conditions | Min | Тур | Max | Unit |

|-----------------------|----------|---------------------------------------|-----------------|-----|-----|-----|------|

| NXT/DIR INPU          | TS       |                                       |                 |     |     |     |      |

| t <sub>DIR_SET</sub>  | NXT, DIR | NXT set time, following change of DIR |                 | 25  |     |     | μs   |

| <sup>†</sup> DIR_HOLD |          | NXT hold time, before change of DIR   |                 | 25  |     |     | μs   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

23. Derived from the internal oscillator.

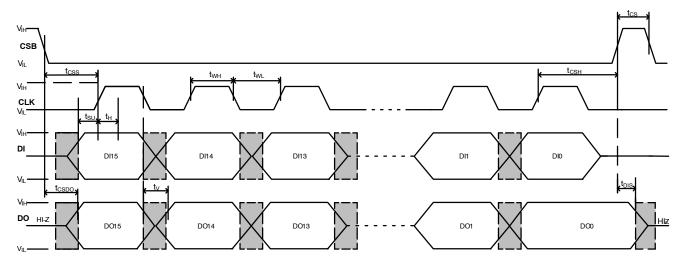

# **Table 8. SPI INTERFACE**

| Symbol                 | Parameter                                            | Min   | Тур | Max          | Unit |

|------------------------|------------------------------------------------------|-------|-----|--------------|------|

| t <sub>CSS</sub>       | CSB setup time (Note 24)                             | 0.5   |     |              | μs   |

| t <sub>CSH</sub>       | CSB hold time                                        | 0.5   |     |              | μs   |

| t <sub>CS</sub>        | CSB high time                                        | 1     |     |              | μs   |

| $t_{WL}$               | CLK low time                                         | 0.5   |     |              | μs   |

| t <sub>WH</sub>        | CLK high time                                        | 0.5   |     |              | μs   |

| t <sub>SU</sub>        | DI set up time, valid data before rising edge of CLK | 0.25  |     |              | μs   |

| t <sub>H</sub>         | DI hold time, hold data after rising edge of CLK     | 0.275 |     |              | μs   |

| t <sub>CSDO</sub>      | CSB low to DO valid                                  |       |     | 0.23         | μs   |

| t <sub>DIS</sub>       | Output (DO) disable time (Note 25)                   | 0.08  |     | 0.32         | μs   |

| $t_{V1 \rightarrow 0}$ | Output (DO) valid (Note 25)                          |       |     | 0.32         | μs   |

| $t_{V0 \rightarrow 1}$ | Output (DO) valid (Note 26)                          |       |     | 0.32 + t(RC) | μs   |

<sup>24.</sup> After leaving sleep mode an additional wait time of 250  $\mu s$  is needed before pulling CSB low.

<sup>26.</sup> Time depends on the SDO load and pull-up resistor.

Figure 7. SPI Timing

<sup>25.</sup> SDO low–side switch activation time.

#### **DETAILED OPERATING DESCRIPTION**

#### **H-Bridge Drivers with PWM Control**

Two H-bridges are integrated to drive a bipolar stepper motor. Each H-bridge consists of two low-side N-type MOSFET switches and two high-side P-type MOSFET switches. One PWM current control loop with on-chip current sensing is implemented for each H-bridge. Depending on the desired current range and the micro-step position at hand, the R<sub>DS(on)</sub> of the low-side transistors will be adapted to maintain current-sense accuracy. A comparator compares continuously the actual winding current with the requested current and feeds back the information to generate a PWM signal, which turns on/off the H-bridge switches. The switching points of the PWM duty-cycle are synchronized to the on-chip PWM clock.

The PWM frequency will not vary with changes in the supply voltage. Also variations in motor-speed or load-conditions of the motor have no effect. There are no external components required to adjust the PWM frequency. In order to avoid large currents through the H-bridge switches, it is guaranteed that the top- and bottom-switches of the same half-bridge are never conductive simultaneously (interlock delay).

In order to reduce the radiated/conducted emission, voltage slope control is implemented in the output switches.

A protection against shorts on motor lines is implemented. When excessive voltage is sensed across a MOSFET for a time longer than the required transition time, then the MOSFET is switched-off.

#### Motor Enable-Disable

The H-bridges and PWM control can be disabled (high-impedance state) by means of a bit <MOTEN> in the SPI control registers. <MOTEN>=0 will only disable the drivers and will not impact the functions of NXT, DIR, SPI bus, etc. The H-bridges will resume normal PWM operation by writing <MOTEN>=1 in the SPI register. PWM current control is then enabled again and will regulate current in both coils corresponding with the position given by the current translator.

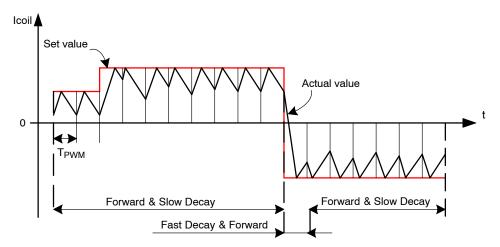

# **Automatic Forward and Slow-Fast Decay**

The PWM generation is in steady-state using a combination of forward and slow-decay. For transition to lower current levels, fast-decay is automatically activated to allow high-speed response. The selection of fast or slow decay is completely transparent for the user and no additional parameters are required for operation.

Figure 8. Forward and Slow/Fast Decay PWM

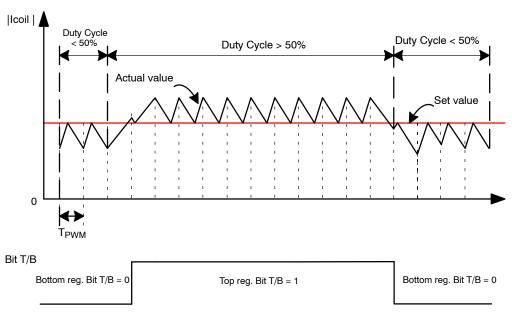

## **Automatic Duty Cycle Adaptation**

If during regulation the set point current is not reached before 75% of  $t_{pwm}$ , the duty cycle of the PWM is adapted automatically to > 50% (top regulation) to maintain the requested average current in the coils. This process is

completely automatic and requires no additional parameters for operation. The state of the duty cycle adaptation mode is represented in the internal T/B bits for both motor windings X and Y. Figure 9 gives a representation of the duty cycle adaptation.

Figure 9. Automatic Duty Cycle Adaptation

#### **Active Break**

Whenever active break is activated (<ACTBR> bit is set), both bottom drivers of active H-bridge (based on actual MSP position) are switched on.

By this mean the position is frozen and current starts recirculating through the bottom drivers, causing faster stopping of the motor.

# STEP TRANSLATOR

#### Step Mode

The step translator provides the control of the motor by means of step mode SPI register SM[2:0], SPI bits DIRP, NXTP and input pins DIR (direction of rotation) and NXT (next pulse). It is translating consecutive steps into corresponding currents in both motor coils for a given step mode.

One out of five possible stepping modes can be selected through SPI-bits SM[2:0]. After power-on or hard reset, the coil-current translator is set to the default to 1/16 micro-stepping at position '8\*'. When remaining in the default step mode, subsequent translator positions are all in the same column and increased or decreased with 1. Table 9 lists the output current versus the translator position.

When the micro-step resolution is reduced, then the corresponding least-significant bits of the translator position are set to "0". This means that the position in the current table moves to the right and in the case that micro-step position of desired new resolution does not overlap the micro-step position of current resolution, the closest value up or down in required column is set depending on the direction of rotation.

When the micro-step resolution is increased, then the corresponding least-significant bits of the translator position are added as "0": the micro-step position moves to the left on the same row.

In general any change of <SM[2:0]> SPI bits have no effect on current micro-step position without consequent occurrence of NXT pulse or <NXTP> SPI command (see NXT input timing below). When NXT pulse or <NXTP> SPI command arrives, the motor moves into next micro-step position according to the current <SM[2:0]> SPI bits value.

Besides the micro-step modes, also full step mode is implemented. Full step mode activates always only one coil at a time.

**Table 9. TRANSLATOR TABLE**

| MSP[5:0] |          |     | mode S |     |     | % of      | f Imax    | MSP[5:0] |          | Step | mode S | M[2:0] |     | % of Imax |           |

|----------|----------|-----|--------|-----|-----|-----------|-----------|----------|----------|------|--------|--------|-----|-----------|-----------|

|          | 000      | 001 | 010    | 011 | 100 |           |           |          | 000      | 001  | 010    | 011    | 100 |           |           |

| MSP[5:0] | 1/1<br>6 | 1/8 | 1/4    | 1/2 | FS  | Coil<br>Y | Coil X    | MSP[5:0] | 1/1<br>6 | 1/8  | 1/4    | 1/2    | FS  | Coil Y    | Coil X    |

| 00 0000  | 0        | 0   | 0      | 0   | 0   | 0         | 100       | 10 0000  | 32       | 16   | 8      | 4      | 2   | 0         | -100      |

| 00 0001  | 1        | -   | -      | -   | -   | 9,8       | 99,5      | 10 0001  | 33       | -    | -      | -      | -   | -9,8      | -99,<br>5 |

| 00 0010  | 2        | 1   | -      | -   | -   | 19,<br>5  | 98,1      | 10 0010  | 34       | 17   | -      | -      | -   | –19,<br>5 | -98,<br>1 |

| 00 0011  | 3        | -   | -      | -   | -   | 29        | 95,7      | 10 0011  | 35       | -    | -      | -      | -   | -29       | -95,<br>7 |

| 00 0100  | 4        | 2   | 1      | -   | -   | 38,<br>3  | 92,4      | 10 0100  | 36       | 18   | 9      | -      | -   | –38,<br>3 | -92,<br>4 |

| 00 0101  | 5        | -   | -      | -   | -   | 47,<br>1  | 88,2      | 10 0101  | 37       | -    | -      | -      | -   | -47,<br>1 | -88,<br>2 |

| 00 0110  | 6        | 3   | -      | -   | -   | 55,<br>6  | 83,1      | 10 0110  | 38       | 19   | -      | -      | -   | –55,<br>6 | -83,<br>1 |

| 00 0111  | 7        | -   | -      | -   | -   | 63,<br>4  | 77,3      | 10 0111  | 39       | -    | -      | -      | -   | -63,<br>4 | -77,<br>3 |

| 00 1000  | 8(*)     | 4   | 2      | 1   | -   | 70,<br>7  | 70,7      | 10 1000  | 40       | 20   | 10     | 5      | -   | -70,<br>7 | -70,<br>7 |

| 00 1001  | 9        | -   | -      | -   | -   | 77,<br>3  | 63,4      | 10 1001  | 41       | -    | -      | -      | -   | -77,<br>3 | -63,<br>4 |

| 00 1010  | 10       | 5   | -      | -   | -   | 83,<br>1  | 55,6      | 10 1010  | 42       | 21   | -      | -      | -   | -83,<br>1 | -55,<br>6 |

| 00 1011  | 11       | -   | -      | -   | -   | 88,<br>2  | 47,1      | 10 1011  | 43       | -    | -      | -      | -   | -88,<br>2 | -47,<br>1 |

| 00 1100  | 12       | 6   | 3      | -   | -   | 92,<br>4  | 38,3      | 10 1100  | 44       | 22   | 11     | -      | -   | -92,<br>4 | -38,<br>3 |

| 00 1101  | 13       | -   | -      | -   | -   | 95,<br>7  | 29        | 10 1101  | 45       | -    | -      | -      | -   | -95,<br>7 | -29       |

| 00 1110  | 14       | 7   | -      | -   | -   | 98,<br>1  | 19,5      | 10 1110  | 46       | 23   | -      | -      | _   | -98,<br>1 | –19,<br>5 |

| 00 1111  | 15       | -   | -      | -   | -   | 99,<br>5  | 9,8       | 10 1111  | 47       | -    | -      | -      | _   | –99,<br>5 | -9,8      |

| 01 0000  | 16       | 8   | 4      | 2   | 1   | 100       | 0         | 11 0000  | 48       | 24   | 12     | 6      | 3   | -100      | 0         |

| 01 0001  | 17       | -   | -      | -   | -   | 99,<br>5  | -9,8      | 11 0001  | 49       | -    | -      | -      | -   | -99,<br>5 | 9,8       |

| 01 0010  | 18       | 9   | -      | -   | -   | 98,<br>1  | –19,<br>5 | 11 0010  | 50       | 25   | -      | -      | -   | -98,<br>1 | 19,5      |

| 01 0011  | 19       | -   | -      | _   | -   | 95,<br>7  | -29       | 11 0011  | 51       | _    | -      | -      | -   | -95,<br>7 | 29        |

| 01 0100  | 20       | 10  | 5      | -   | _   | 92,<br>4  | -38,<br>3 | 11 0100  | 52       | 26   | 13     | -      | _   | -92,<br>4 | 38,3      |

| 01 0101  | 21       | -   | -      | -   | -   | 88,<br>2  | -47,<br>1 | 11 0101  | 53       | -    | -      | -      | -   | -88,<br>2 | 47,1      |

| 01 0110  | 22       | 11  | -      | -   | -   | 83,<br>1  | –55,<br>6 | 11 0110  | 54       | 27   | -      | -      | -   | -83,<br>1 | 55,6      |

| 01 0111  | 23       | -   | -      | -   | -   | 77,<br>3  | -63,<br>4 | 11 0111  | 55       | -    | -      | -      | _   | -77,<br>3 | 63,4      |

| 01 1000  | 24       | 12  | 6      | 3   | -   | 70,<br>7  | -70,<br>7 | 11 1000  | 56       | 28   | 14     | 7      | _   | -70,<br>7 | 70,7      |

| 01 1001  | 25       | -   | -      | -   | -   | 63,<br>4  | -77,<br>3 | 11 1001  | 57       | -    | -      | -      | _   | -63,<br>4 | 77,3      |

**Table 9. TRANSLATOR TABLE**

| 01 1010 | 26 | 13 | _ | _ | _ | 55,<br>6 | -83,<br>1 | 11 1010 | 58 | 29 | -  | _ | _ | -55,<br>6 | 83,1 |

|---------|----|----|---|---|---|----------|-----------|---------|----|----|----|---|---|-----------|------|

| 01 1011 | 27 | -  | - | - | - | 47,<br>1 | -88,<br>2 | 11 1011 | 59 | -  | -  | - | - | -47,<br>1 | 88,2 |

| 01 1100 | 28 | 14 | 7 | - | - | 38,<br>3 | -92,<br>4 | 11 1100 | 60 | 30 | 15 | - | _ | -38,<br>3 | 92,4 |

| 01 1101 | 29 | _  | - | - | - | 29       | –95,<br>7 | 11 1101 | 61 | -  | _  | - | _ | -29       | 95,7 |

| 01 1110 | 30 | 15 | - | - | - | 19,<br>5 | -98,<br>1 | 11 1110 | 62 | 31 | -  | - | - | –19,<br>5 | 98,1 |

| 01 1111 | 31 | _  | - | - | _ | 9,8      | -99,<br>5 | 11 1111 | 63 | -  | -  | - | _ | -9,8      | 99,5 |

$<sup>^{\</sup>star}$   $\,$  Default position after reset of the translator position.

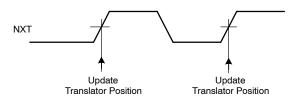

#### **Translator Position**

The translator position can be read and set by the SPI register <MSP[5:0]>. This is a 6-bit number equivalent to the 1/16<sup>th</sup> micro-step from Table 9: Translator Table. The translator position is updated immediately following a next micro-step trigger (see below).

Figure 10. Translator Position Timing Diagram

#### **Direction**

The direction of rotation is selected by means of input pin DIR and its "polarity bit" <DIRP> (SPI register). The polarity bit <DIRP> allows changing the direction of rotation by means of only SPI commands instead of the dedicated input pin.

#### Direction = DIR-pin EXOR < DIRP>

Positive direction of rotation means counter-clockwise rotation of electrical vector Ix + Iy. Also when the motor is disabled (<MOTEN>=0), both the DIR pin and <DIRP> will have an effect on the positioner. The logic state of the DIR pin is visible as a flag in SPI status register.

#### **Next Micro-Step Trigger**

Positive edges on the NXT input – or activation of the "NXT pushbutton" <NXTP> in the SPI input register – will move the motor current one step up/down in the Table 9 – Translator table. The <NXTP> bit in SPI is used to move positioner one (micro-)step by means of only SPI commands. If the bit is set to "1", it is reset automatically to "0" after having advanced the positioner with one micro-step.

Trigger "Next micro-step" = (positive edge on NXT-pin)

OR (<NXTP>=1)

- Also when the motor is disabled (<MOTEN>=0), NXT/DIR functions will move the positioner according to the logic (only if <NXTfilter>=0).

- In order to be sure that both the NXT pin and the <NXTP>

SPI command are individually attended, the following

non overlapping zone has to be respected. In this case it

is guaranteed that both triggers will have effect (2 steps

are taken).

Figure 11. NXT Input Non Overlapping Zone with the <NXTP> SPI Command

For control by means of I/O's, the NXT pin operation with respect to DIR pin should be in a non-overlapped way. See also the timing diagram below (refer to the Table 7 – AC Parameters for the timing values). The <SM[2:0]> SPI bits setting, when changed, is accepted upon the consequent either NXT pin rising edge or <NXTP> SPI command write only. On the other hand, the SPI bits <DIRP>, <SM[2:0]> and <NXTP> can change state at the same time in the same SPI command: the next micro-step will be applied with the new settings. Writing to the SPI register <MSP[5:0]> is accepted and applied to translator table immediately, does not taking actual step mode into account.

Figure 12. NXT input Timing Diagram

# **Motor Current**

On cold temperatures below  $T_{low}$  (see Table 6 – DC Parameters) the current can be boosted to higher values by SPI bit <IBOOST>. After reaching temperature of thermal warning  $T_{tw}$ , current is automatically decreased to unboosted level. Status of the boost function can be read in SPI <IBOOST> bit. The motor current settings correspond to the following current levels:

Table 10. IMOT VALUES (4BIT)

| Register<br>Value | Peak Motor<br>Current IMOT<br>(mA) | Peak Boost Motor<br>Current IMOT<br>(mA) |

|-------------------|------------------------------------|------------------------------------------|

| 0                 | 59                                 | 81                                       |

| 1                 | 71                                 | 98                                       |

| 2                 | 84                                 | 116                                      |

| 3                 | 100                                | 138                                      |

| 4                 | 119                                | 164                                      |

| 5                 | 141                                | 194                                      |

| 6                 | 168                                | 231                                      |

| 7                 | 200                                | 275                                      |

| 8                 | 238                                | 327                                      |

| 9                 | 283                                | 389                                      |

| Α                 | 336                                | 462                                      |

| В                 | 400                                | 550                                      |

| С                 | 476                                | 655                                      |

| D                 | 566                                | 778                                      |

| E                 | 673                                | 925                                      |

| F                 | 800                                | 1100                                     |

Whenever <IMOT[3:0]> is changed, the new coil currents will be updated immediately at the next PWM period.

In case the motor is disabled (<MOTEN>=0), the logic is functional and will have effect on NXT/DIR operation (not on the H-bridges). When the chip is in sleep mode, the logic is not functional and as a result, the NXT pin and DIR pin will have no effect.

Note: The hard-reset function is embedded by means of a special sequence on the DIR pin and NXT pin, see also Hard-Reset Function chapter.

# **Under-voltage Detection**

The NCV70517 has one undervoltage threshold level UV (see Table 6 – DC Parameters).

Undervoltage warning <UVW> bit is activated as when the UV comparator threshold is hit (cleared by read as when the undervoltage condition disappears). This allows the MCU taking actions at system level if required.

When supply voltage VBB drops below UV threshold and stays there longer than set undevoltage debounce time, the undervoltage detection <UV> flag is set and ERRB pin is pulled down. Undervoltage debounce time can be selected by means of <UV\_time[1:0]> register.

Only if the <UV>=0 the motor can be enabled again by writing <MOTEN>=1 in the control register.

Behavior of the H-bridge after UV detection can be selected by <UV\_act> bit. When <UV\_act> = 0, H-bridge goes to Hi-Z state. When <UV\_act> = 1, H-bridge motor brake (shorted to GDN).

Note: When Next pulse is applied (by means of NXT pin or <NXTP> bit via SPI) during undervoltage condition, the step loss bit <SL> is set.

#### Stall and Motion Detection

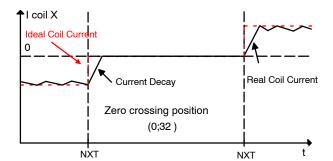

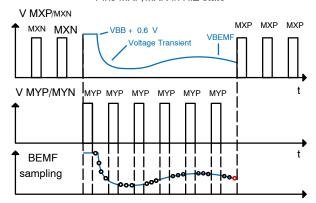

Motion detection is based on the Back Electromotive Force (BEMF or back emf) generated into the running motor. When the motor is blocked, e.g. when it hits the end-position, the velocity and as a result also the generated back emf, is disturbed. The NCV70517 measures the back emf during the current zero crossing phase and makes it available in the SPI status register SR5. The back emf voltage is measured several times in each PWM cycle during zero crossing phase. Samples taken during PWM ON phase of the switches in the second coil are discarded not to add noise to measurement (see Figure 13). Results are then converted into a 5-bits word <Bemf[4:0]> with the following formula:

$$\label{eq:behavior} \mathsf{BEMF\_code}(\mathsf{dec}) \ = \ \mathsf{V\_MOT\_XorY\_diff}(\mathsf{V}) \ \times \ \mathsf{Gain} \ \times \ (\frac{5}{4}) \ \times \ \frac{2^5}{2.41}$$

When the result is ready, it is indicated by <BemfRes> bit in status register.

When using normal mode of back emf measurement (<EnhBemfEn> = 0), last sample before end of current zero crossing phase becomes available in <Bemf[4:0]> register (see the red circle on Figure 13).

When the enhanced back emf measurement mode is set by <EnhBemfEn> bit, all non discarded results are continuously available in <Bemf[4:0]> register (see red and all black circles on Figure 13). This allows microcontroller (when reading content of the register fast enough) to follow back emf signal and its shape during zero crossing phase and use more complex algorithms to optimize the work of driven stepper motor.

Pins MXP/MXN in HiZ state

Figure 13. Back Emf Sampling

For slow speed or when a motion ends at a full step position (there is an absence of next NXT trigger), the end of the zero crossing is taking too long or is non-existing. In this case, the back emf voltage is taken the latest at "stall time-out" time and this value is used also for comparison with  $\langle StThr[3:0] \rangle$  stall threshold to detect stall situation. The "stall time-out" is set in SPI by means of  $\langle StTo[7:0] \rangle$  register and is expressed in counts of  $4/f_{pwm}$  (See AC Parameters), roughly in steps of 0.2 ms. If  $\langle StTo[7:0] \rangle = 0$ , time-out is not active.

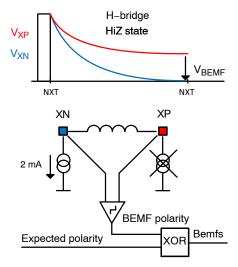

At the end of the current zero crossing phase the internal circuitry compares measured back emf voltages with <StThr[3:0]> register, which determines threshold for stall detection. The last sample of back emf taken before end of zero crossing phase is used for stall detection in normal mode as well as in enhanced back emf mode. When  $\langle StThr[3:0] \rangle = 0$  then stall detection is disabled. When value of <StThr[3:0]> is different from 0 and measured back emf signal is lower than <StThr[3:0]> threshold for 2 succeeding coil current zero-crossings (including both X and Y coil), then the <STALL> bit in SPI status register 1 is set, the current translator table goes 135 degrees in opposite direction and the ERRB pin is pulled down, IMOT is maintained. Direction has to change its state at least once and then <STALL> bit can be cleared by reading the status register 1. With stall bit cleared, the chip reacts on "Next Micro-step Triggers" and ERRB pin becomes inactive again.

#### Notes:

- 1. Used stall detection is covered by patent US 8,058,894B2

- 2. As the stall threshold register <StThr[3:0]> is 4 bits wide, the 4 MSBs of 5-bit <Bemf[4:0]> register are taken for comparison

Stall detection and Bemf measurement are performed only when Speed register value <Sp[7:0]> is less than or equal to Speed threshold register value <SpThr[7:0]>.

Stall detection is disabled if time between two consecutive NXT pulses is lower than 74.5  $\mu$ s (PWMJen = 0) or 80  $\mu$ s (PWMJen = 1).

Range and resolution of Speed register and Speed threshold register are 0 to 5100 us and 20 us/digit for half stepping mode. Accuracy of speed (time) measurement is given by the accuracy of the internal oscillator.

If measured back emf voltage has not expected polarity, the back emf sign flag <Bemfs> is set. Motor pin, where lower voltage is expected, is tied to GND by pull down current. Sign is determined by comparator, which compares the polarity of voltage measured over the coil with expected polarity of voltage.

Figure 14. Back Emf Sign Value

The last measured back emf value <Bemf[4:0]>, sign flag <Bemfs> and coil where the last back emf sample was taken <Bemfcoil> can be read out via SPI.

Table 11. STALL THRESHOLDS SETTINGS (4BIT)

| StThr Index | StThr Level (V) | StThr Level (V) |  |

|-------------|-----------------|-----------------|--|

|             | BemfGain = 0    | BemfGain = 1    |  |

| 0           | Disable         | Disable         |  |

| 1           | 0.48            | 0.24            |  |

| 2           | 0.96            | 0.48            |  |

| 3           | 1.44            | 0.72            |  |

| 4           | 1.92            | 0.96            |  |

| 5           | 2.4             | 1.2             |  |

| 6           | 2.88            | 1.44            |  |

| 7           | 3.36            | 1.68            |  |

| 8           | 3.84            | 1.92            |  |

| 9           | 4.32            | 2.16            |  |

| Α           | 4.8             | 2.4             |  |

| В           | 5.28            | 2.64            |  |

| С           | 5.76            | 2.88            |  |

| D           | 6.24            | 3.12            |  |

| E           | 6.72            | 3.36            |  |

| F           | 7.2             | 3.6             |  |

# WARNING, ERROR DETECTION AND DIAGNOSTICS FEEDBACK

# **Open & Short Circuit Diagnostic**

The NCV70517 stepper driver features an enhanced diagnostic detection and feedback, to be read by the external microcontroller unit (MCU). Among the main items of interest for the application and typical failures, are open coil and the short circuit condition, which may be to ground (chassis), or to supply (battery line).

When in normal mode, the device will continuously check upon errors with respect to the expected behavior.

The open load condition is determined by the fact that the PWM duty cycle keeps 100% value for a time longer than set by <0penDet[1:0]> register. This is valid of course only for the X/Y coil where the current is supposed to circulate, meaning that in full step positions (MSP[5:0] =  $\{0; 16; 32; 48\}$  (dec)) the open load can be detected only for one of the coil at a time (respectively  $\{X; Y; X; Y\}$ ). The same reasoning applies for the short circuits detection.

Due to the timeout value set by <OpenDet[1:0]>, the open coil detection is dependent on the motor speed. In more detail, there is a maximum speed at which it can be done. Table 12 specifies these maxima for the different step modes. For practical reasons, all values are given in full steps per second.

Table 12. MAXIMUM VELOCITIES FOR OPEN COIL DETECTION

| Step Mode | Speed [FS/s] for given <opendet[1:0]></opendet[1:0]> |      |      |     |

|-----------|------------------------------------------------------|------|------|-----|

|           | 00                                                   | 01   | 10   | 11  |

| Full Step | 200                                                  | 40   | 20   | 5   |

| 1/2       | 300                                                  | 60   | 30   | 7.5 |

| 1/4       | 350                                                  | 70   | 35   | 8.8 |

| 1/8       | 375                                                  | 75   | 37.5 | 9.4 |

| 1/16      | 387.5                                                | 77.5 | 38.8 | 9.7 |

When Open coil condition is detected, the appropriate bit (<OPENX> or <OPENY>) together with <ELDEF> bit in the SPI status register are set. Reaction of the H-bridge to Open coil condition depends on the settings of <OpenHiZ> and <OpenDis> bits.

When both <OpenHiZ> and <OpenDis> bits are 0, <MOTEN> bit stays in 1 and only H-bridge where open coil is detected is disabled. When <OpenHiZ> bit is set, both H-bridges are disabled (<MOTEN>=0) in case of Open coil detection. When <OpenDis> bit is set, drivers remain active for both coils independently of <OpenHiZ> bit.

The short circuit detection monitors the load current in each activated output stage. The current is measured in terms of voltage drop over the MOSFETS' R<sub>DS(ON)</sub>. If the load current exceeds the over-current detection threshold, the appropriate over-current flag <SHRTij> together with

<ELDEF> bit are set and the drivers are switched off to protect the integrated circuit. Each driver stage has an individual detection bit for the N side and the P side.

When short circuit is detected, <MOTEN> is set to 0. The positioner, the NXT and DIR stay operational. The flag <ELDEF> (result of OR-ing the latched flags: <SHRTXPT> OR <SHRTXPB> OR <SHRTXNT> OR <SHRTYND> OR <SHRTYPB> OR <SHRTYPB> OR <SHRTYPB> OR <SHRTYNT> OR <SHRTYNT> OR <SHRTYND> OR <OPENX> OR <OPENY>) is reset when the microcontroller reads out the short circuit or open coil status flags in status registers.

To enable the motor again after reading out of the status flags, <MOTEN>=1 has to be written.

#### Notes:

- 1. Successive reading of the <SHRTij> flags and re-enabling the motor in case of a short circuit condition may lead to damage of the drivers.

- 2. Example: SHRTXPT means: Short at X coil, Positive output pin, Top transistor.

- 3. In case of the short from any stepper motor pin to the top side during switching event from bottom to top on motor pin, the flag "short to bottom side" is set instead of the expected "short to top side" flag.

#### **Step Loss Detection**

When Next pulse is applied (by means of NXT pin or <NXTP> bit via SPI) or <MSP> register is written during error condition, the step loss bit <SL> is set.

<SL> = (<UV> OR <TSD> OR <ELDEF>) AND ((NXT OR <NXTP>) OR <MSP> write)

Step loss bit <SL> is cleared after read out.

#### **Thermal Warning and Shutdown**

When junction temperature is above  $T_{tw}$ , the thermal warning bit <TW> is set (SPI register) and the ERRB pin is pulled down (\*). If junction temperature increases above thermal shutdown level, then also the <TSD> flag is set, the ERRB pin is pulled down, the motor is disabled (<MOTEN> = 0) and the hardware reset is disabled. If  $T_j < T_{tw}$  level and <TSD> bit has been read—out, the status of <TSD> is cleared and the ERRB pin is released.

Only if the <TSD>=<TW>=0, the motor can be enabled again by writing <MOTEN>=1 in the control register 1.

During the over temperature condition the hardware reset will not work until  $T_i < T_{tw}$  and the <TSD> readout is done.

In this way it is guaranteed that after a <TSD>=1 event, the die-temperature decreases back to the level of <TW>.

After reaching temperature of thermal warning  $T_{tw}$ , motor current is automatically decreased to unboosted level.

Note (\*): During the <TW> situation the motor is not disabled while the ERRB is pulled down. To be informed about other error situations it is recommended to poll the status registers on a regular base (time base driven by application software in the millisecond domain).

#### **Error Output**

This is an open drain output to flag a problem to the external microcontroller. The signal on this output is active low and the logic combination of:

NOT(ERRB) = (<SPI> OR <ELDEF> OR <TSD> OR <TW> OR <STALL> OR (BemfIntEn AND BemfRes) OR <UV> OR (\*)reset state) AND not (\*\*)sleep mode

Note (\*) reset state: After a power–on or a hard–reset, the ERRB is pulled low during  $t_{hr\_err}$  (Table 7 – AC Parameters).

Note (\*\*) sleep mode: In sleep mode the ERRB is always inactive (high).

# Sleep Mode

The motor driver can be put in a low-power consumption mode (sleep mode). The sleep mode is entered automatically after a power-on or hard reset and can also be activated by means of SPI bit <SLP>. In sleep-mode, all analog circuits are suspended in low-power, logic output pin ERRB is disabled (ERRB has no function) and none of the input pins is functional with the exception of pin CSB. Only CSB pin can wake-up the chip to normal mode (i.e. clear bit <SLP>) by means of a low pulse with a specified width within tcsb\_with time. Time twu (see Table 7 - AC Parameters) is needed to restore all analog and digital circuits after wake-up.

#### Notes:

- The hard-reset function is disabled in sleep mode.

- The CSB low pulse width has to be within t<sub>csb\_with</sub>, (see Table 7 – AC Parameters) to guarantee a correct wake-up.

#### Power-on Reset, Hard-Reset Function

After a power-on or a hard-reset, a flag <HR> in the SPI status register is set and the ERRB is pulled low. The ERRB stays low during this reset state. The typical power-on reset time is given by t<sub>hr\_err</sub> (Table 7 - AC Parameters). After the reset state the device enters sleep mode and the ERRB pin goes high to indicate the motor controller is ready for operation.

By means of a specific pattern on the DIR pin and NXT pin, the complete digital part of driver can be reset without a power-cycle. This hard-reset function is activated when the input pin DIR changes logic state " $0 \rightarrow 1 \rightarrow 0 \rightarrow 1$ " in five consecutive patterns during NXT pin being at high level. See figure below and Table 7 – AC Parameters.

The operation of all analog circuits is suspended during the reset state of the digital. Similar as for a normal power–on, the flag <HR> is set in the SPI register after a hard–reset and the ERRB pin is pulled low during  $t_{hr\_err}$  (Table 7 – AC Parameters).

Figure 15. Hard Reset Timing Diagram

# **SPI INTERFACE**

#### General

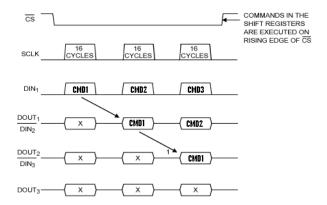

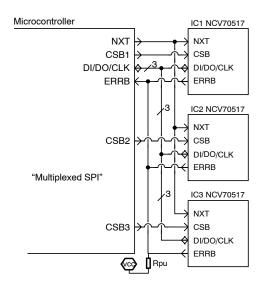

The serial peripheral interface (SPI) is used to allow an external microcontroller (MCU) to communicate with the device. NCV70517 acts always as a slave and it cannot initiate any transmission. The operation of the device is configured and controlled by means of SPI registers, which are observable for read and/or write from the master. The NCV70517 SPI transfer size is 16 bits.

During an SPI transfer, the data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line (CLK) synchronizes shifting

and sampling of the information on the two serial data lines: DO and DI. The DO signal is the output from the Slave (NCV70517), and the DI signal is the output from the Master

A slave or chip select line (CSB) allows individual selection of a slave SPI device in a time multiplexed multiple-slave system.

The CSB line is active low. If an NCV70517 is not selected, DO is in high impedance state and it does not interfere with SPI bus activities. Since the NCV70517 always clocks data out on the falling edge and samples data

in on rising edge of clock, the MCU SPI port must be configured to match this operation.

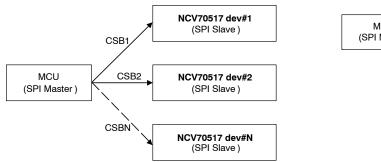

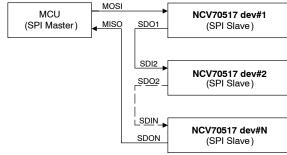

The implemented SPI allows connection to multiple slaves by means of star connection (CSB per slave) or by means of daisy chain.

An SPI star connection requires a bus = (3 + N) total lines, where N is the number of Slaves used, the SPI frame length is 16 bits per communication.

Figure 16. SPI Star vs. Daisy Chain Connection

#### SPI Daisy chain mode

SPI daisy chain connection bus width is always four lines independently on the number of slaves. However, the SPI transfer frame length will be a multiple of the base frame length so N x 16 bits per communication: the data will be interpreted and read in by the devices at the moment the CSB rises.

A diagram showing the data transfer between devices in daisy chain connection is given further: CMDx represents the 16-bit command frame on the data input line transmitted by the Master, shifting via the chips' shift registers through the daisy chain. The chips interpret the command once the chip select line rises.

Figure 17. SPI Daisy Chain Data Shift Between Slaves. The symbol 'x' represents the previous content of the SPI shift register buffer.

The NCV70517 default power up communication mode is "star". In order to enable daisy chain mode, a multiple of 16 bits clock cycles must be sent to the devices, while the SDI line is left to zero.

Note: to come back to star mode the NOP register (address 0x0000) must be written with all ones, with the proper data parity bit and parity framing bit: see SPI protocol for details about parity and write operation.

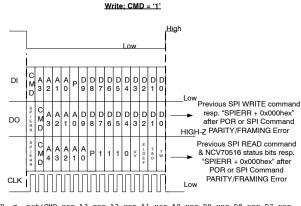

#### **SPI Transfer Format**

Two types of SPI commands (to DI pin of NCV70517) from the micro controller can be distinguished: "Write to a control register" and "Read from register (control or status)".

The frame protocol for the *write operation*:

P = not(CMD xor A3 xor A2 xor A1 xor A0 xor D9 xor D8 xor D7 xor D6 xor D5 xor D4 xor D3 xor D2 xor D1 xor D0)

Figure 18. SPI Write Frame

Referring to the previous picture, the write frame coming from the master (into the DI) is composed from the following fields:

- Bit[15] (MSB): CMD bit = 1 for write operation,

- Bits[14:11]: 4 bits WRITE ADDRESS field,

- Bit[10]: frame parity bit. It is ODD parity formed by the negated XOR of all other bits in the frame,

- Bits[9:0]: 10 bit DATA to write

Device in the same time replies to the master (on the DO):

- If the previous command was a write and no SPI error had occurred, a copy of the command, address and data written fields,

- If the previous command was a read, the response frame summarizes the address used and an overall diagnostic

check (copy of the main detected errors, see Figure 18 and Figure 19 for details),

• In case of previous SPI error or after power-on-reset, only the MSB bit will be 1, followed by zeros.

If parity bit in the frame is wrong, device will not perform command and <SPI> flag will be set.

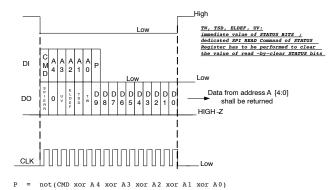

The frame protocol for the <u>read operation</u>:

#### Read; CMD = '0'

Figure 19. SPI Read Frame

Referring to the previous picture, the read frame coming from the master (into the DI) is composed from the following fields:

- Bit[15] (MSB): CMD bit = 0 for read operation,

- Bits[14:10]: 5 bits READ ADDRESS field,

- Bit[10]: frame parity bit. It is ODD parity formed by the negated XOR of all other bits in the frame,

- Bits [8:0]: 9 bits zeroes field.

Device in the same frame provides to the master (on the DO) data from the required address (in frame response), thus achieving the lowest communication latency.

# **SPI Framing and Parity Error**

SPI communication framing error is detected by the NCV70517 in the following situations:

- Not an integer multiple of 16 CLK pulses are received during the active-low CSB signal;

- LSB bits (8..0) of a read command are not all zero;

- SPI parity errors, either on write or read operation.

Once an SPI error occurs, the <SPI> flag can be reset only by reading the status register in which it is contained (using in the read frame the right communication parity bit). This request will reset the SPI error bit and release the ERRB pin (high).

# **SPI Control Registers (CR)**

All SPI control registers have Read/Write access.

Table 13. SPI CONTROL REGISTERS (CR)

| 5-bit<br>Address | Bit 9     | Bit 8   | Bit 7    | Bit 6         | Bit 5         | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default after Res. |

|------------------|-----------|---------|----------|---------------|---------------|----------|--------|--------|--------|--------|--------------------|

| 00h              | NOP       | NOP     | NOP      | NOP           | NOP           | NOP      | NOP    | NOP    | NOP    | NOP    | 00 0000<br>0000    |

| 01h (CR1)        | NXTfilter | NXTP    | MOTEN    | DIRP          | IBOOST        | ACTBR    | ІМОТ3  | IMOT2  | IMOT1  | IMOT0  | 00 0000<br>0000    |

| 02h (CR2)        | -         | PWMJen  | OpenDet1 | OpenDet0      | OpenDis       | OpenHiZ  | SLP    | SM2    | SM1    | SM0    | 00 1000<br>1000    |

| 03h (CR3)        | UVact     | UVtime1 | UVtime0  | BemfIntE<br>n | EnhBemfE<br>n | BemfGain | StThr3 | StThr2 | StThr1 | StThr0 | 00 0000<br>0000    |

| 04h (CR4)        | -         | -       | -        | -             | MSP5          | MSP4     | MSP3   | MSP2   | MSP1   | MSP0   | 00 0000<br>1000    |

| 0Bh<br>(CR5)     | EMC1      | EMC0    | StTo7    | StTo6         | StTo5         | StTo4    | StTo3  | StTo2  | StTo1  | StTo0  | 01 0001<br>0000    |

| 0Ch<br>(CR6)     | -         | -       | SpThr7   | SpThr6        | SpThr5        | SpThr4   | SpThr3 | SpThr2 | SpThr1 | SpThr0 | 00 0000<br>0000    |

**Table 14. BIT DEFINITION**

| Symbol    | MAP position            | Description                                                                                               |

|-----------|-------------------------|-----------------------------------------------------------------------------------------------------------|

| NOP       | Bits [9:0] – ADDR_0x00  | NOP register (read/write operation ignored)                                                               |

| NXTfilter | Bit 9 – ADDR_0x01 (CR1) | Filters out pulses coming from the NXT pin when the motor (H-bridge) is disabled                          |

| NXTP      | Bit 8 – ADDR_0x01 (CR1) | Push button pin, generating next step in position table                                                   |

| MOTEN     | Bit 7 – ADDR_0x01 (CR1) | Enables the H-bridges (motor activated)                                                                   |

| DIRP      | Bit 6 – ADDR_0x01 (CR1) | Polarity of DIR pin, which controls direction status; DIRP = 1 inverts the logic polarity of the DIR pin) |

| IBOOST    | Bit 5 – ADDR_0x01 (CR1) | Current boost function activation and status                                                              |

| ACTBR     | Bit 4 – ADDR_0x01 (CR1) | Active break                                                                                              |

Table 14. BIT DEFINITION (continued)

| IMOT[3:0]    | Bits [3:0] - ADDR_0x01 (CR1) | Current amplitude                                                                                                                                                                          |

|--------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWMJen       | Bit 8 – ADDR_0x02 (CR2)      | Enable PWM jittering function to spread spectrum of PWM modulation                                                                                                                         |

| OpenDet[1:0] | Bits [7:6] - ADDR_0x02 (CR2) | Open Coil detection time setting bits (see Table 7 - AC Parameters)                                                                                                                        |

| OpenDis      | Bit 5 – ADDR_0x02 (CR2)      | When bit is set, Open Coil detection status is flagged, but drivers control remain active for both coils, <opendis> bit setting has higher priority than <openhiz> bit</openhiz></opendis> |

| OpenHiZ      | Bit 4 – ADDR_0x02 (CR2)      | When bit is set, during Open Coil detection both drivers are deactivated (MOTEN=0)                                                                                                         |

| SLP          | Bit 3 – ADDR_0x02 (CR2)      | Places device in sleep mode with low current consumption (when 1)                                                                                                                          |

| SM[2:0]      | Bits [2:0] - ADDR_0x02 (CR2) | Step mode selection                                                                                                                                                                        |

| UVact        | Bit 9 – ADDR_0x03 (CR3)      | "0": H bridge left open upon under voltage detection; "1": H bridge motor brake (shorted to GND), when undervoltage is detected                                                            |

| UVtime[1:0]  | Bits [8:7] - ADDR_0x03 (CR3) | Under-voltage filter (debounce) time (see Table 7 - AC Parameters)                                                                                                                         |

| BemfIntEn    | Bit 6 – ADDR_0x03 (CR3)      | BEMF result interrupt enable                                                                                                                                                               |

| EnhBemfEn    | Bit 5 – ADDR_0x03 (CR3)      | Enhanced BEMF measurement functionality is activated when bit is set                                                                                                                       |

| BemfGain     | Bit 4 – ADDR_0x03 (CR3)      | Gain of BEMF measurement channel = "0": gain 0.5, "1": gain 0.25                                                                                                                           |

| StThr[3:0]   | Bits [3:0] - ADDR_0x03 (CR3) | Threshold level for stall detection, when "0", stall detection is disabled                                                                                                                 |

| MSP[5:0]     | Bit [5:0] - ADDR_0x04 (CR4)  | Setting or status of translator micro-step position                                                                                                                                        |

| EMC[1:0]     | Bits [9:8] - ADDR_0x0B (CR5) | Voltage slope defining bits for motor driver switching (see Table 7 – AC Parameters)                                                                                                       |

| StTo[7:0]    | Bits [7:0] – ADDR_0x0B (CR5) | tall time-out. Max difference between two successive full step next pulse periods (time-out), after this time the BEMF sample is taken to verify stall                                     |

| SpThr[7:0]   | Bits [7:0] - ADDR_0x0C (CR6) | Speed threshold register, BEMF measurement and stall detection is activated when Speed register value is less than or equal to <spthr> value</spthr>                                       |

# **SPI Status Registers (SR)**

All SPI status registers have Read Only Access, with the odd parity on Bit8. Parity bit makes the numbers of 1 in the byte odd.

Table 15. SPI STATUS REGISTERS (SR)