## **Quad Driver**

This automotive grade product provides a versatile interface between control logic and many types of loads. The inputs accept a wide range of control signal levels while the open-collector outputs feature independent thermal and current limiting. Integral transient suppression diodes are provided at all inputs and outputs.

## Features

- Operation in -40°C 125°C Environment

- TTL/DTL/CMOS Compatible Inputs

- NAND Logic with Common Enable

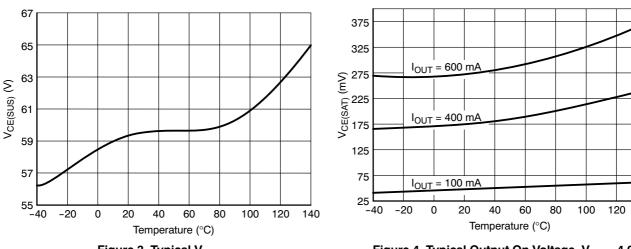

- $V_{CEX} \ge 60 \text{ V}, V_{CE(SUS)} \ge 40 \text{ V}$

- $V_{CE(SAT)} \le 650 \text{ mV}$  @  $I_C = 600 \text{ mA}$

- Thermally Efficient Fused-Lead Package

- Pin Compatible with:

- CA3242/CA3262

- UDx2543/UDx2549/UDx2559

- L6220/L6221/L9222

- AEC Qualified

- PPAP Capable

- Pb-Free Package is Available\*

## **Typical Applications**

- Body and Drivetrain Electronics

- Incandescent Lamp/LED Loads

- Solenoid/Relay/Inductor Loads

- Heater/Resistor Loads

- Stepper/DC Motor Loads

## **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                            | Value       | Unit         |

|---------------------------------------------------------------------------------------------------|-------------|--------------|

| V <sub>CC</sub>                                                                                   | -0.3 to 7.0 | V            |

| Logic Input Voltage (INA, INB, INC, IND, ENABLE)                                                  | -0.3 to 15  | V            |

| Power Output (OUTA, OUTB, OUTC, OUTD)                                                             | -0.3 to 60  | V            |

| Junction Temperature Range, TJ                                                                    | -40 to 150  | °C           |

| Storage Temperature Range                                                                         | -55 to 150  | °C           |

| ESD Susceptibility (Human Body Model)                                                             | 2.0         | kV           |

| Package Thermal Resistance Junction-to-Case, $R_{\theta JC}$ Junction-to-Ambient, $R_{\theta JA}$ | 15<br>50    | °C/W<br>°C/W |

| Lead Temperature Soldering: Wave Solder (through hole styles only) (Note 1)                       | 260 peak    | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. 10 second maximum.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **ON Semiconductor®**

http://onsemi.com

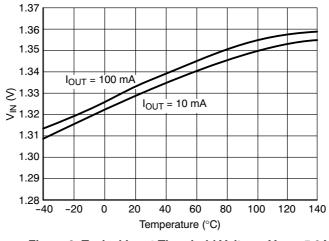

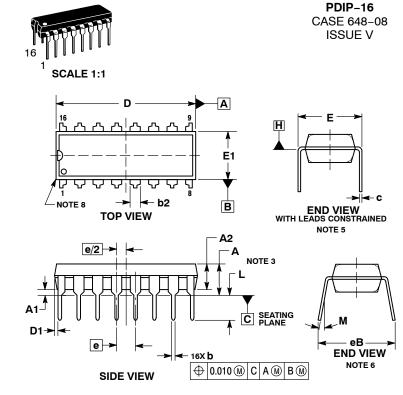

PDIP-16 P SUFFIX CASE 648

## MARKING DIAGRAM

| 4 | = Asse | mbly | Location |

|---|--------|------|----------|

|   |        |      |          |

- WL = Wafer Lot

- YY = Year

- WW = Work Week G = Pb-Free Package

## **PIN CONNECTIONS**

| 1<br>OUTA کے<br>CLAMPAB | 0 | 16<br>СУ INA<br>СУ INB |

|-------------------------|---|------------------------|

|                         |   |                        |

| GND C                   |   |                        |

| GND 🧲                   |   | Ъ GND                  |

| оитс 🕻                  |   | ₽v <sub>cc</sub>       |

| CLAMPCD 🗧               |   | Ъ INC                  |

| Ουτο 🧲                  |   | Биис                   |

## **ORDERING INFORMATION**

| Device    | Package              | Shipping      |

|-----------|----------------------|---------------|

| NCV7601P  | PDIP-16              | 25 Units/Rail |

| NCV7601PG | PDIP-16<br>(Pb-Free) | 25 Units/Rail |

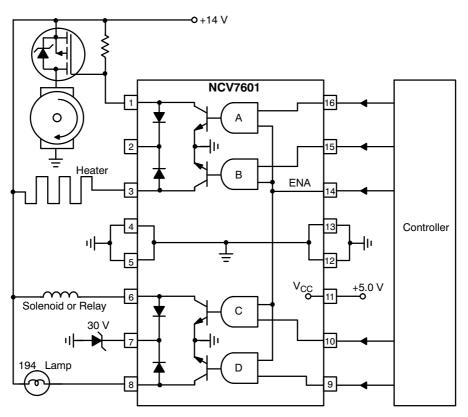

**Figure 1. Typical Driver Applications**

## $\textbf{ELECTRICAL CHARACTERISTICS} ~ (4.0~V \leq V_{CC} \leq 5.5~V,~-40^{\circ}C \leq T_J \leq 125^{\circ}C,~unless~otherwise~specified.)~Note~20^{\circ}C \leq 125^{\circ}C < 125^{\circ}C < 125^$

| Characteristic Test Conditions                 |                                                                                                       | Min      | Тур | Max      | Unit     |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|-----|----------|----------|

| GENERAL                                        |                                                                                                       |          |     |          |          |

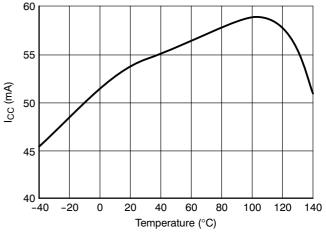

| V <sub>CC</sub> Supply Current                 | Outputs Off, $V_{CC}$ = 5.5 V<br>Note 3 I <sub>OUT</sub> = 600 mA, $V_{CC}$ = V <sub>IN</sub> = 5.5 V |          | -   | 5.0      | mA       |

|                                                | (four outputs on)<br>(one output on)                                                                  | -        | -   | 65<br>20 | mA<br>mA |

| OUTPUT DRIVERS                                 |                                                                                                       | <u>.</u> |     |          |          |

| Saturation Voltage                             | $I_{OUT}$ = 600 mA, $V_{IN}$ = 2.0 V, $V_{CC}$ = 4.0 V                                                | -        | -   | 650      | mV       |

| Leakage Current                                | $V_{OUT}$ = 60 V, $V_{IN}$ = 0.8 V, $V_{CC}$ = 5.5 V                                                  | -        | -   | 50       | μA       |

| Current Limit                                  | $4.5 \text{ V} < \text{V}_{\text{OUT}} < 16 \text{ V}, \text{V}_{\text{CC}} = 5.0 \text{ V}$          | -        | -   | 1.8      | Α        |

| Thermal Shutdown                               | -                                                                                                     |          | 180 | 210      | °C       |

| Sustaining Voltage, V <sub>CE(SUS)</sub>       | V <sub>CC</sub> = 5.5 V                                                                               |          | -   | -        | V        |

| CLAMP DIODES                                   |                                                                                                       | _        |     | _        |          |

| Forward Voltage                                | I <sub>F</sub> = 1.5 A, V <sub>CC</sub> = 5.5 V                                                       | -        | -   | 2.0      | V        |

| Leakage Current $V_{R} = 60 V, V_{CC} = 5.5 V$ |                                                                                                       | -        | -   | 100      | μΑ       |

| INPUT                                          |                                                                                                       |          |     |          |          |

| Input Current                                  | $0 V \le V_{IN} \le V_{CC}$                                                                           |          | -   | 10       | μA       |

| Input High Voltage                             | I <sub>OUT</sub> = 600 mA 2.0                                                                         |          | -   | -        | V        |

| Input Low Voltage                              | I <sub>OUT</sub> = 600 mA                                                                             |          | -   | 0.8      | V        |

| AC CHARACTERISTICS (Note 4)                    |                                                                                                       |          |     |          |          |

| Turn-On Delay, Turn-Off Delay                  | I <sub>OUT</sub> = 500 mA                                                                             | -        | -   | 10       | μs       |

3. Pulse test. 4. Input rise time  $\leq$  10 ns, falltime  $\leq$  10 ns, measured at 50% points.

## PACKAGE PIN DESCRIPTION

| PACKAGE PIN # | PIN SYMBOL      | FUNCTION                             |

|---------------|-----------------|--------------------------------------|

| 1             | OUTA            | Driver A Output                      |

| 2             | CLAMPAB         | Diode Clamp to Driver A and Driver B |

| 3             | OUTB            | Driver B Output                      |

| 4             | GND             | Ground                               |

| 5             | GND             | Ground                               |

| 6             | OUTC            | Driver C Output                      |

| 7             | CLAMPCD         | Diode Clamp to Driver C and Driver D |

| 8             | OUTD            | Driver D Output                      |

| 9             | IND             | Driver D Input                       |

| 10            | INC             | Driver C Input                       |

| 11            | V <sub>CC</sub> | 5.0 V Input Supply Voltage           |

| 12            | GND             | Ground                               |

| 13            | GND             | Ground                               |

| 14            | ENABLE          | ENABLE Input to all Drivers          |

| 15            | INB             | Driver B Input                       |

| 16            | INA             | Driver A Input                       |

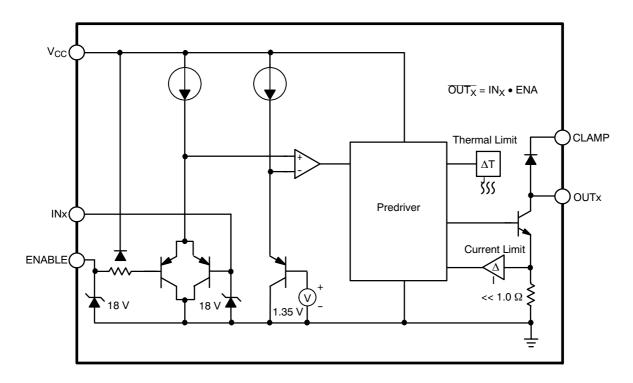

Figure 2. Simplified Block Diagram – Each Driver

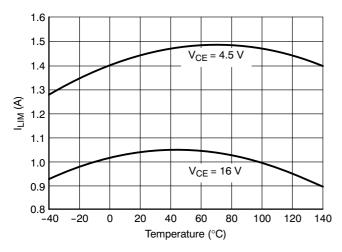

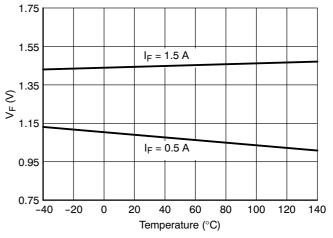

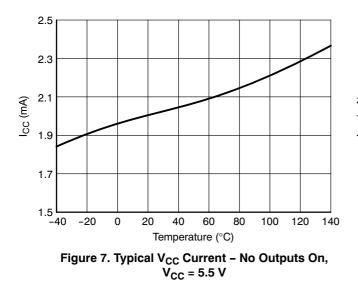

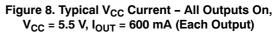

## **TYPICAL PERFORMANCE CHARACTERISTICS**

140

Figure 5. Typical Output Current Limit,  $V_{CC} = 5.0 V$

Figure 6. Typical Clamp Diode Forward Voltage

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 9. Typical Input Threshold Voltage, V<sub>CC</sub> = 5.0 V

#### **DETAILED OPERATING DESCRIPTION**

The NCV7601 Quad Driver consists of four identical driver sections with output clamp diodes and a common bias generator.

Each driver input (Figure 2) is buffered by a PNP emitter follower for reduced input bias current and features a nominal 18 V Zener input clamp for transient protection. Each input is compared to a separate temperature-compensated reference, which provides a nominal 1.35 V comparison threshold. With the addition of an external series resistor, the inputs can be interfaced directly to +14 V automotive system voltages. Floating inputs are interpreted as high.

Each driver output NPN is supplied with a substantially fixed base current from the +5.0 V  $V_{CC}$  pin by a pre-driver.

#### **APPLICATIONS INFORMATION**

The NCV7601 Quad Driver interfaces high power loads to low power control signals. The four open-collector NAND drivers with common ENABLE are TTL, DTL and CMOS compatible. Any number of drivers may be parallel connected to drive loads greater than each driver's nominal capability. Power for the Quad's control logic and output pre-drive is supplied from the +5.0 V V<sub>CC</sub> pin, and is proportional to the number of active inputs. Minimum standby power is consumed when the ENABLE input is low. Each driver is individually protected with current limit and thermal limit circuitry. Drivers with fault loads are protected while drivers with normal loads continue to operate, provided that sufficient heat sinking maintains a good thermal gradient between all drivers.

Clamp diodes at each driver output provide a means for managing inductive load transients. The common cathode pin for each driver pair can be connected to the load supply voltage for suppression of minor transients resulting from enable input is high. Current limit and thermal limit circuits act independently within the pre-driver to reduce base drive to the output NPN. The independent limit operation allows the driver to handle inrush current from lamp loads while protecting the driver from fault conditions that exist long enough to raise the temperature at that driver to its thermal limit threshold. Each driver has its temperature-sensing device located in close proximity to the output NPN. The separate sensing devices are strategically placed at the corners of the die to reduce interaction between them.

Each pre-driver multiplies a temperature-compensated

reference current when its control input and the common

wiring harness inductances. The use of an external Zener diode or TVS (Transient Voltage Suppressor) device such as the ON Semiconductor 1.5SMCXXXAT3 series is strongly recommended when driving large inductive loads or when load supply transients can be expected to exceed the Quad Driver's VCE(SUS) rating. The use of a TVS device provides an additional benefit by reducing the decay time of inductive loads. More information on safeguarding the Quad's output NPN's and about transient suppression methods and device selection is available in ON Semiconductor application notes "Understanding Power Transistors Breakdown Parameters", document number AN1628/D, "A Review of Transients and their Means Of Suppression", document number AN843/D and "Transient Power Capability of Zener Diodes", document number AN784/D. All application notes are available through the Literature Distribution website Center or via our at http://www.onsemi.com.

| STYLE 1 | :       | STYLE 2 | :            |

|---------|---------|---------|--------------|

| PIN 1.  | CATHODE | PIN 1.  | COMMON DRAIN |

| 2.      | CATHODE | 2.      | COMMON DRAIN |

| 3.      | CATHODE | 3.      | COMMON DRAIN |

| 4.      | CATHODE | 4.      | COMMON DRAIN |

| 5.      | CATHODE | 5.      | COMMON DRAIN |

| 6.      | CATHODE | 6.      | COMMON DRAIN |

| 7.      | CATHODE | 7.      | COMMON DRAIN |

| 8.      | CATHODE | 8.      | COMMON DRAIN |

| 9.      | ANODE   | 9.      | GATE         |

| 10.     | ANODE   | 10.     | SOURCE       |

| 11.     | ANODE   | 11.     | GATE         |

| 12.     | ANODE   | 12.     | SOURCE       |

| 13.     | ANODE   | 13.     | GATE         |

| 14.     | ANODE   | 14.     | SOURCE       |

| 15.     | ANODE   | 15.     | GATE         |

| 16.     | ANODE   | 16.     | SOURCE       |

NOTES

1. 2.

DATE 22 APR 2015

- З.

- DTES:

DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: INCHES.

DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3.

DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH.

DIMENSION E IS MEASURED AT A POINT 0.016 PEI OW DATUM 4

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR 5.

- TO DATUM C. DIMENSION eB IS MEASURED AT THE LEAD TIPS WITH THE 6.

- DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BOTTOM OF THE LEADS, WHERE THE LEADS EXIT THE BODY. PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE 7.

- 8 CORNERS).

|     | INCHES    |       | MILLIMETER |       |  |

|-----|-----------|-------|------------|-------|--|

| DIM | MIN       | MAX   | MIN        | MAX   |  |

| Α   |           | 0.210 |            | 5.33  |  |

| A1  | 0.015     |       | 0.38       |       |  |

| A2  | 0.115     | 0.195 | 2.92       | 4.95  |  |

| b   | 0.014     | 0.022 | 0.35       | 0.56  |  |

| b2  | 0.060 TYP |       | 1.52 TYP   |       |  |

| С   | 0.008     | 0.014 | 0.20       | 0.36  |  |

| D   | 0.735     | 0.775 | 18.67      | 19.69 |  |

| D1  | 0.005     |       | 0.13       |       |  |

| Е   | 0.300     | 0.325 | 7.62       | 8.26  |  |

| E1  | 0.240     | 0.280 | 6.10       | 7.11  |  |

| е   | 0.100 BSC |       | 2.54 BSC   |       |  |

| eB  |           | 0.430 |            | 10.92 |  |

| L   | 0.115     | 0.150 | 2.92       | 3.81  |  |

| М   |           | 10°   |            | 10°   |  |

### GENERIC **MARKING DIAGRAM\***

XXXXX = Specific Device Code

- = Assembly Location

- WL = Wafer Lot

- YY = Year

Α

- WW = Work Week

- G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| DOCUMENT NUMBER: | 98ASB42431B Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|--|

| DESCRIPTION:     | PDIP-16                                                                                                                                                                                         |  | PAGE 1 OF 1 |  |

|                  |                                                                                                                                                                                                 |  | -           |  |

onsemi and ONSEMi. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products herein. special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>