# onsemi

## **Remote 16-bit I/O Expander** for I<sup>2</sup>C Bus with Interrupt

## **PCA9655E**

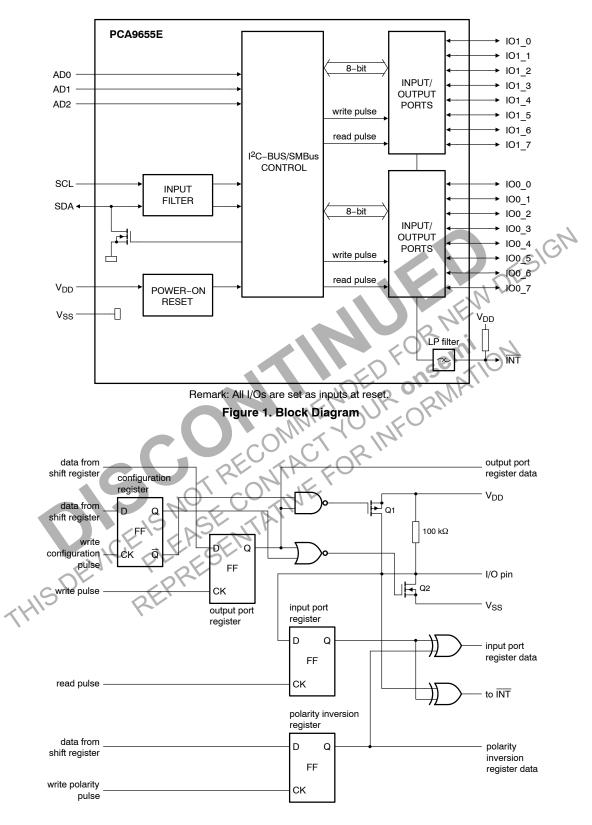

The PCA9655E provides 16 bits of General Purpose parallel Input / Output (GPIO) expansion through the I<sup>2</sup>C-bus / SMBus.

The PCA9655E consists of two 8-bit Configuration (Input or Output selection); Input, Output and Polarity Inversion (active-HIGH or active-LOW operation) registers. At power on, all I/Os default to inputs. Each I/O may be configured as either input or output by writing to its corresponding I/O configuration bit. The data for each Input or Output is kept in its corresponding Input or Output register. The Polarity Inversion register may be used to invert the polarity of the read register. All registers can be read by the system master.

The PCA9655E provides an open-drain interrupt output which is activated when any input state differs from its corresponding input port register state. The interrupt output is used to indicate to the system master that an input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine.

Three hardware pins (AD0, AD1, AD2) are used to configure the I<sup>2</sup>C-bus slave address of the device. Up to 64 devices are allowed to SNOT RECONTACT share the same I<sup>2</sup>C-bus / SMBus.

#### Features

- V<sub>DD</sub> Operating Range: 1.65 V to 5.5 V

- SDA Sink Capability: 30 mA

- 5.5 V Tolerant I/Os

- Polarity Inversion Register

- Active LOW Interrupt Output

- Low Standby Current

- Noise Filter on SCL/SDA Inputs

- No Glitch on Power-up

- Internal Power-on Reset

- 64 Programmable Slave Addresses Using Three Address Pins

- 16 I/O Pins Which Default to 16 Inputs

- I<sup>2</sup>C SCL Clock Frequencies Supported: Standard Mode: 100 kHz Fast Mode: 400 kHz Fast Mode +: 1 MHz

- ESD Performance: 2000 V Human Body Model, 200 V Machine Model

- These are Pb-Free Devices

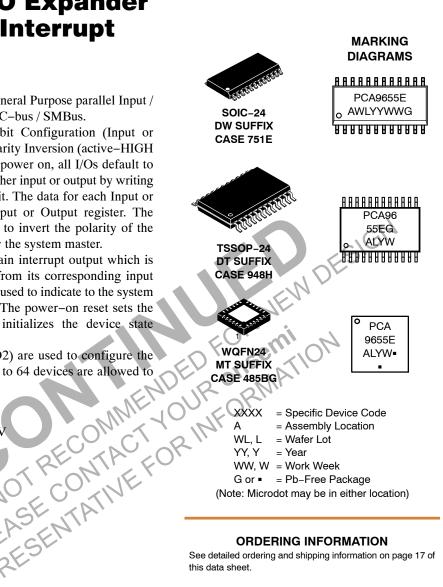

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 17 of this data sheet

#### **BLOCK DIAGRAM**

At power-on reset, all registers return to default values.

#### Figure 2. Simplified Schematic of I/Os

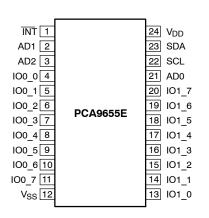

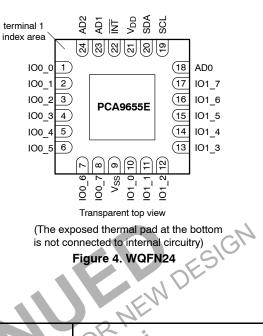

#### **PIN ASSIGNMENT**

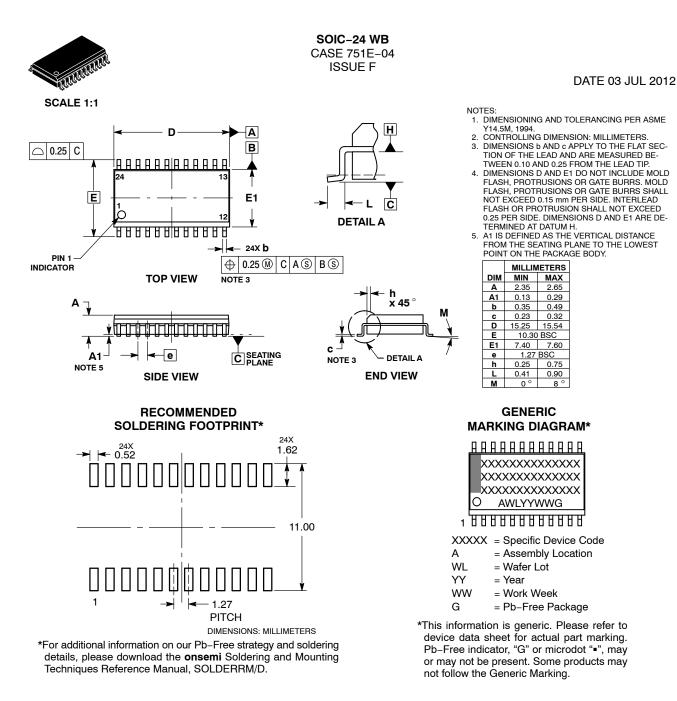

#### Figure 3. SOIC24 / TSSOP24

#### **Table 1. PIN DESCRIPTIONS**

|                 | P               | in            |                                                                            |

|-----------------|-----------------|---------------|----------------------------------------------------------------------------|

| Symbol          | SOIC24, TSSOP24 | WQFN24        | Description                                                                |

| INT             | 1               | 22 DE         | Interrupt Output (active–LOW), connect to<br>GND recommended if not in use |

| AD1             | 2               | 23            | Address Input 1                                                            |

| AD2             | 3               | 24            | Address Input 2                                                            |

| IO0_0           | 4               | C, C, R       | Port 0 I/O 0                                                               |

| IO0_1           | 5 2             | 2 - 0 - 2 - 0 | Port 0 I/O 1                                                               |

| IO0_2           | 6               | 0 3           | Port 0 I/O 2                                                               |

| IO0_3           | 5               | 4             | Port 0 I/O 3                                                               |

| IO0_4           | 8               | 5             | Port 0 I/O 4                                                               |

| IO0_5           | 9-1-5F          | 6             | Port 0 I/O 5                                                               |

| IO0_6           | 10 24           | 7             | Port 0 I/O 6                                                               |

| 100_7 S         | OW              | 8             | Port 0 I/O 7                                                               |

| Vss             | 12              | 9             | Supply Ground                                                              |

| IO1_0           | 13              | 10            | Port 1 I/O 0                                                               |

| IO1_1           | 14              | 11            | Port 1 I/O 1                                                               |

| IO1_2           | 15              | 12            | Port 1 I/O 2                                                               |

| IO1_3           | 16              | 13            | Port 1 I/O 3                                                               |

| IO1_4           | 17              | 14            | Port 1 I/O 4                                                               |

| IO1_5           | 18              | 15            | Port 1 I/O 5                                                               |

| IO1_6           | 19              | 16            | Port 1 I/O 6                                                               |

| IO1_7           | 20              | 17            | Port 1 I/O 7                                                               |

| AD0             | 21              | 18            | Address Input 0                                                            |

| SCL             | 22              | 19            | Serial Clock Line                                                          |

| SDA             | 23              | 20            | Serial Data Line                                                           |

| V <sub>DD</sub> | 24              | 21            | Supply Voltage                                                             |

#### **Table 2. MAXIMUM RATINGS**

| Symbol               | Parameter                                                                 | Value                | Unit |

|----------------------|---------------------------------------------------------------------------|----------------------|------|

| V <sub>DD</sub>      | DC Supply Voltage                                                         | -0.5 to +7.0         | V    |

| V <sub>I/O</sub>     | Input / Output Pin Voltage                                                | -0.5 to +7.0         | V    |

| I <sub>I</sub>       | Input Current                                                             | ±20                  | mA   |

| Ι <sub>Ο</sub>       | Output Current                                                            | ±50                  | mA   |

| I <sub>DD</sub>      | DC Supply Current                                                         | ±100                 | mA   |

| I <sub>GND</sub>     | DC Ground Current                                                         | ±600                 | mA   |

| P <sub>TOT</sub>     | Total Power Dissipation                                                   | 600                  | mW   |

| P <sub>OUT</sub>     | Power Dissipation per Output                                              | 200                  | mW   |

| T <sub>STG</sub>     | Storage Temperature Range                                                 | -65 to +150          | °C   |

| ΤL                   | Lead Temperature, 1 mm from Case for 10 Seconds                           | 260                  | °C   |

| TJ                   | Junction Temperature Under Bias                                           | 150                  | °C   |

| $\theta_{JA}$        | Thermal Resistance (Note 1) SOIC-24<br>TSSOP-24<br>WQFN24                 | 85<br>91<br>68       | °C/W |

| MSL                  | Moisture Sensitivity                                                      | Level 1              |      |

| F <sub>R</sub>       | Flammability Rating Oxygen Index: 28 to 34                                | UL 94 V-0 @ 0.125 in |      |

| $V_{ESD}$            | ESD Withstand Voltage Human Body Model (Note 2)<br>Machine Model (Note 3) | > 2000<br>> 200      | V    |

| I <sub>LATCHUP</sub> | Latchup Performance Above V <sub>DD</sub> and Below GND at 125°C (Note 4) | ±300                 | mA   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Measured with minimum pad spacing on an FR4 board, using 10 mm-by-1 inch, 2 ounce copper trace no air flow.

| <ol> <li>Tested to</li> <li>Tested to</li> <li>Tested to</li> </ol> | <ol> <li>Measured with minimum pad spacing on an FR4 board, using 10 mm-by-1 inch, 2 ounce copper trace no air flow.</li> <li>Tested to EIA / JESD22-A114-A.</li> <li>Tested to EIA / JESD22-A115-A.</li> <li>Tested to EIA / JESD78.</li> </ol> Table 3. RECOMMENDED OPERATING CONDITIONS |      |     |      |  |  |  |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--|--|--|--|--|

| Symbol                                                              | Parameter                                                                                                                                                                                                                                                                                  | Min  | Max | Unit |  |  |  |  |  |

| V <sub>DD</sub>                                                     | Positive DC Supply Voltage                                                                                                                                                                                                                                                                 | 1.65 | 5.5 | V    |  |  |  |  |  |

| V <sub>I/O</sub>                                                    | Switch Input / Output Voltage                                                                                                                                                                                                                                                              | 0    | 5.5 | V    |  |  |  |  |  |

| T <sub>A</sub>                                                      | T <sub>A</sub> Operating Free-Air Temperature -55 +125 °C                                                                                                                                                                                                                                  |      |     |      |  |  |  |  |  |

| 71                                                                  | HIS DE REPT                                                                                                                                                                                                                                                                                |      |     |      |  |  |  |  |  |

#### Table 4. DC ELECTRICAL CHARACTERISTICS $V_{DD}$ = 1.65 V to 5.5 V, unless otherwise specified.

|                      |                                            | T <sub>A</sub> = -                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |                      |                       |          |  |

|----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|-----------------------|----------|--|

| Symbol               | Parameter                                  | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min                                                  | Тур                  | Max                   | Unit     |  |

| SUPPLIES             | •                                          | -                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      |                      |                       |          |  |

| I <sub>STB</sub>     | Standby Current                            | Standby mode; no load;<br>V <sub>I</sub> = 0 V; f <sub>SCL</sub> = 0 Hz; I/O = inputs<br>V <sub>I</sub> = V <sub>DD</sub> ; f <sub>SCL</sub> = 0 Hz; I/O = inputs                                                                                                                                                                                                                                                                                              |                                                      | 1.1<br>0.25          | 1.5<br>1              | mA<br>μA |  |

| V <sub>POR</sub>     | Power-On Reset Voltage<br>(Note 5)         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 1.5                  | 1.65                  | V        |  |

| INPUT SCL            | ; Input / Output SDA                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |                      |                       |          |  |

| V <sub>IH</sub>      | High-Level Input Voltage                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $0.7 	ext{ x V}_{	ext{DD}}$                          |                      |                       | V        |  |

| V <sub>IL</sub>      | Low-Level Input Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |                      | 0.3 x V <sub>DD</sub> | V        |  |

| I <sub>OL</sub>      | Low-Level Output Current                   | $V_{OL}$ = 0.4 V; $V_{DD}$ < 2.3 V                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                   |                      |                       | mA       |  |

|                      |                                            | $V_{DD} \ge 2.3 V$                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20                                                   |                      |                       |          |  |

| ١L                   | Leakage Current                            | $V_{I} = V_{DD}$ or 0 V                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |                      | ±G                    | μA       |  |

| Cl                   | Input Capacitance                          | $V_{I} = 0 V$                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      | 4.6                  | 6                     | pF       |  |

| I/Os                 |                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |                      | )~                    |          |  |

| V <sub>IH</sub>      | High-Level Input Voltage                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.7 x V <sub>DD</sub>                                |                      |                       | V        |  |

| VIL                  | Low-Level Input Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                    | *.                   | 0.3 x V <sub>DD</sub> | V        |  |

| I <sub>OL</sub>      | Low-Level Output Current<br>(Note 6)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8<br>12<br>17<br>25                                  | 20<br>28<br>35<br>42 | 1                     | mA       |  |

| I <sub>OL(tot)</sub> | Total Low-Level Output Current<br>(Note 6) | $V_{OL} = 0.5 V; V_{DD} = 4.5 V$                                                                                                                                                                                                                                                                                                                                                                                                                               | ORIN                                                 |                      | 400                   | mA       |  |

| V <sub>OH</sub>      | High-Level Output Voltage                  | $\begin{split} I_{OH} &= -3 \text{ mA; } V_{DD} = 1.65 \text{ V} \\ I_{OH} &= -4 \text{ mA; } V_{DD} = 1.65 \text{ V} \\ I_{OH} &= -8 \text{ mA; } V_{DD} = 2.3 \text{ V} \\ I_{OH} &= -10 \text{ mA; } V_{DD} = 2.3 \text{ V} \\ I_{OH} &= -10 \text{ mA; } V_{DD} = 3.0 \text{ V} \\ I_{OH} &= -10 \text{ mA; } V_{DD} = 3.0 \text{ V} \\ I_{OH} &= -8 \text{ mA; } V_{DD} = 4.5 \text{ V} \\ I_{OH} &= -10 \text{ mA; } V_{DD} = 4.5 \text{ V} \end{split}$ | 1.2<br>1.1<br>1.8<br>1.7<br>2.6<br>2.5<br>4.1<br>4.0 |                      |                       | V        |  |

| I <sub>LH</sub>      | Input Leakage Current                      | $V_{DD} = 5.5 \text{ V}; \text{ V}_{I} = \text{V}_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |                      | 1                     | μA       |  |

| ILL                  | Input Leakage Current                      | V <sub>DD</sub> = 5.5 V; V <sub>I</sub> = 0 V                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                      |                      | -100                  | μA       |  |

| C <sub>I/O</sub>     | Input / Output Capacitance<br>(Note 7)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 5.0                  | 6.0                   | pF       |  |

| INTERRUP             | T (INT)                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                    |                      | -                     |          |  |

| I <sub>OL</sub>      | Low-Level Output Current                   | V <sub>OL</sub> = 0.4 V                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.0                                                  |                      |                       | mA       |  |

| CO                   | Output Capacitance                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      | 5.0                  | 5.5                   | pF       |  |

| INPUTS AD            | D0, AD1, AD2                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                      | -                    | -                     |          |  |

| V <sub>IH</sub>      | High-Level Input Voltage                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.7 x V <sub>DD</sub>                                |                      |                       | V        |  |

| VIL                  | Low-Level Input Voltage                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                    |                      | 0.3 x V <sub>DD</sub> | V        |  |

| ۱ <sub>L</sub>       | Leakage Current                            | V <sub>I</sub> = V <sub>DD</sub> or 0 V                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                      |                      | ±1                    | μA       |  |

| C                    | Input Capacitance                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                    | 45                   | 5.0                   | nF       |  |

Image Current

$v_I = v_{DD}$  or 0 v

$\pm 1$   $\mu A$

C\_1

Input Capacitance

4.5

5.0

pF

5. The power-on reset circuit resets the I<sup>2</sup>C bus logic with  $V_{DD} < V_{POR}$  and set all I/Os to logic 1 upon power-up. Thereafter,  $V_{DD}$  must be lower

than 0.2 V to reset the part.Each bit must be limited to a maximum of 25 mA and the total package limited to 400 mA due to internal bussing limits.

7. The value is not tested, but verified on sampling basis.

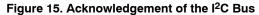

|                     |                                                            |     | ndard<br>ode | Fast Mo                             | Fast M |      |      |      |

|---------------------|------------------------------------------------------------|-----|--------------|-------------------------------------|--------|------|------|------|

| Symbol              | Parameter                                                  | Min | Max          | Min                                 | Max    | Min  | Max  | Unit |

| f <sub>SCL</sub>    | SCL Clock Frequency                                        | 0   | 0.1          | 0                                   | 0.4    | 0    | 1.0  | MHz  |

| t <sub>BUF</sub>    | Bus-Free Time between a STOP and START<br>Condition        | 4.7 |              | 1.3                                 |        | 0.5  |      | μs   |

| t <sub>HD:STA</sub> | Hold Time (Repeated) START Condition                       | 4.0 |              | 0.6                                 |        | 0.26 |      | μs   |

| t <sub>SU:STA</sub> | Setup Time for a Repeated START Condition                  | 4.7 |              | 0.6                                 |        | 0.26 |      | μs   |

| t <sub>SU:STO</sub> | Setup Time for STOP Condition                              | 4.0 |              | 0.6                                 |        | 0.26 |      | μs   |

| t <sub>HD:DAT</sub> | Data Hold Time                                             | 0   |              | 0                                   |        | 0    |      | ns   |

| t <sub>VD:ACK</sub> | Data Valid Acknowledge Time (Note 8)                       | 0.3 | 3.45         | 0.1                                 | 0.9    | 0.05 | 0.45 | μs   |

| t <sub>VD:DAT</sub> | Data Valid Time (Note 9)                                   | 300 |              | 50                                  |        | 50   | 450  | ns   |

| t <sub>SU:DAT</sub> | Data Setup Time                                            | 250 |              | 100                                 |        | 50   | 2    | ns   |

| t <sub>LOW</sub>    | LOW Period of SCL                                          | 4.7 |              | 1.3                                 | N      | 0.5  |      | μs   |

| t <sub>HIGH</sub>   | HIGH Period of SCL                                         | 4.0 |              | 0.6                                 | R      | 0.26 |      | μs   |

| t <sub>f</sub>      | Fall Time of SDA and SCL (Notes 11 and 12)                 |     | 300          | 20 + 0.1C <sub>b</sub><br>(Note 10) | 300    | 1    | 120  | ns   |

| t <sub>r</sub>      | Rise Time of SDA and SCL                                   |     | 1000         | 20 + 0.1C <sub>b</sub><br>(Note 10) | 300    | У.   | 120  | ns   |

| t <sub>SP</sub>     | Pulse Width of Spikes Suppressed by Input Filter (Note 13) | NER | 50           | SORN                                | 50     |      | 50   | ns   |

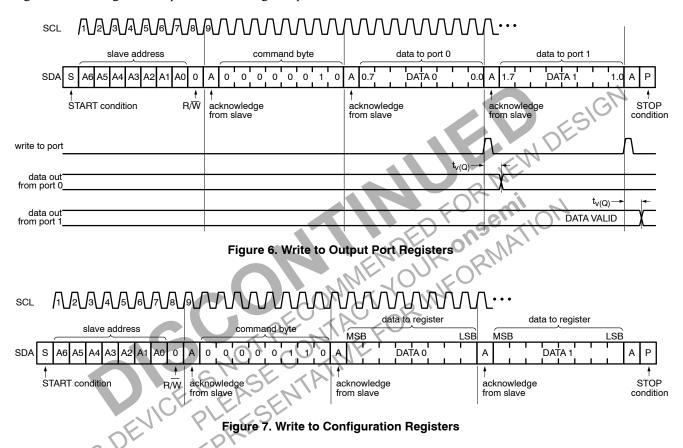

PORT TIMING: C<sub>L</sub> ≤ 100 pF (See Figures 6, 9 and 10)

| t <sub>V(Q)</sub>  | Data Output Valid Time         (V <sub>DD</sub> = 4.5 V to 5.5 V)<br>(V <sub>DD</sub> = 2.3 V to 4.5 V)<br>(V <sub>DD</sub> = 1.65 V to 2.3 V)         200<br>350 |     | 200<br>350<br>550 |     | 200<br>350<br>550 | ns |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|-----|-------------------|----|

| t <sub>SU(D)</sub> | Data Input Setup Time 100                                                                                                                                         | 100 |                   | 100 |                   | ns |

| t <sub>H(D)</sub>  | Data Input Hold Time G                                                                                                                                            | 1   |                   | 1   |                   | μs |

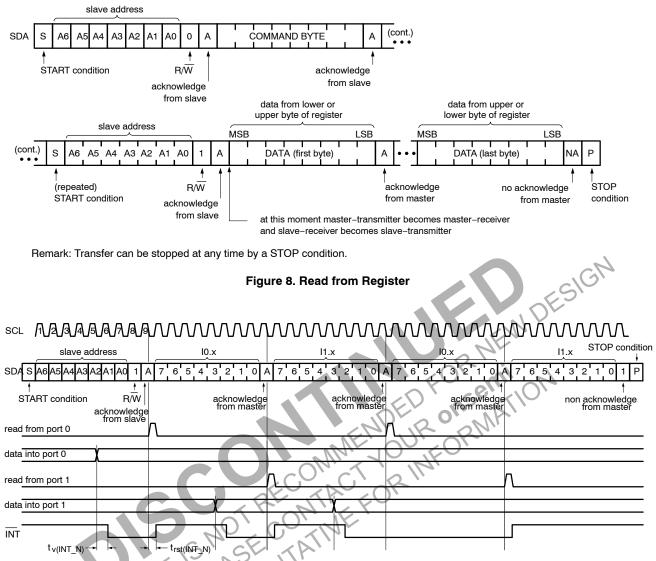

**INTERRUPT TIMING:**  $C_{L} \leq 100 \text{ pF}$  (See Figures 9 and 10)

| t <sub>V(INT_N)</sub>   | Data Valid Time  | 4 | 4 | 4 | μs |

|-------------------------|------------------|---|---|---|----|

| t <sub>RST(INT_N)</sub> | Reset Delay Time | 4 | 4 | 4 | μs |

8. t<sub>VD:ACK</sub> = time for Acknowledgment signal from SCL LOW to SDA (out) LOW.

9. t<sub>VD:DAT</sub> = minimum time for SDA data out to be valid following SCL LOW.

10. C<sub>b</sub> = total capacitance of one bus line in pF.

11. A master device must internally provide a hold time of al least 300 ns for the SDA signal (refer to V<sub>IL</sub> of the SCL signal) in order to bridge the undefined region SCL's falling edge.

12. The maximum t<sub>f</sub> for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage t<sub>f</sub> is specified at 250 ns. This allows series protection resistors to be connected between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified t<sub>f</sub>.

13. Input filters on the SDA and SCL inputs suppress noise spikes less than 50 ns.

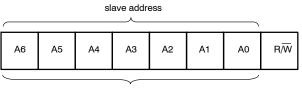

#### **Device Address**

Before the bus master can access a slave device, it must send the address of the slave it is accessing and the operation it wants to perform (read or write) following a START condition. The slave address of the PCA9655E is shown in Figure 5. Address pins AD2, AD1, and AD0 choose 1 of 64 slave addresses. To conserve power, no internal pull–up resistors are provided on AD2, AD1, and AD0.

A logic 1 on the last bit of the first byte selects a read operation while a logic 0 selects a write operation.

programmable

Figure 5. PCA9655E device Address

|     | Address Inpu | ıt  |      |    |               | Slav | <mark>e Address</mark> |     |     |     |

|-----|--------------|-----|------|----|---------------|------|------------------------|-----|-----|-----|

| AD2 | AD1          | AD0 | A6   | A5 | A4            | A3   | A2                     | A1  | A0  | HEX |

| GND | SCL          | GND | 0    | 0  | 1             | 0    | 0                      | 0   | 0   | 20h |

| GND | SCL          | VDD | 0    | 0  | 1             | 0    | 0                      | 0   | 1   | 22h |

| GND | SDA          | GND | 0    | 0  | 1             | 0    | 0                      | 1   | 0.0 | 24h |

| GND | SDA          | VDD | 0    | 0  | 1             | 0    | 0                      | 1   | Or  | 26h |

| VDD | SCL          | GND | 0    | 0  | 1             | 0    | 1                      | 0   | 0   | 28h |

| VDD | SCL          | VDD | 0    | 0  | 1             | 0    | 1                      | 0   | 1   | 2Ah |

| VDD | SDA          | GND | 0    | 0  | 1             | 0    | 20                     | 1   | 0   | 2Ch |

| VDD | SDA          | VDD | 0    | 0  | 1             | 0    |                        | 61. | O1  | 2Eh |

| GND | SCL          | SCL | 0    | 0  | 1             |      | 0                      | 0   | 0   | 30h |

| GND | SCL          | SDA | 0    | 0  | 1             | 1    | 0                      | 0   | 1   | 32h |

| GND | SDA          | SCL | 0    | 0  | W             | 70   | 0                      | 1   | 0   | 34h |

| GND | SDA          | SDA | 0    | 0  |               | 2    | 0                      | 1   | 1   | 36h |

| VDD | SCL          | SCL | 0    | 0  | <rp>&lt;</rp> | 0    | 1                      | 0   | 0   | 38h |

| VDD | SCL          | SDA | 0    | 0  | 16            | 1    | 1                      | 0   | 1   | 3Ah |

| VDD | SDA          | SCL | 0    | 9  |               | 1    | 1                      | 1   | 0   | 3Ch |

| VDD | SDA          | SDA | 185  | 0  | 1             | 1    | 1                      | 1   | 1   | 3Eh |

| GND | GND          | GND | VO C | Г  | 0             | 0    | 0                      | 0   | 0   | 40h |

| GND | GND          | VDD | 0    | 1  | 0             | 0    | 0                      | 0   | 1   | 42h |

| GND | VDD          | GND | 0    | 1  | 0             | 0    | 0                      | 1   | 0   | 44h |

| GND | VDD          | VDD | 0    | 1  | 0             | 0    | 0                      | 1   | 1   | 46h |

| VDD | GND          | GND | 0    | 1  | 0             | 0    | 1                      | 0   | 0   | 48h |

| VDD | GND          | VDD | 0    | 1  | 0             | 0    | 1                      | 0   | 1   | 4Ah |

| VDD | VDD          | GND | 0    | 1  | 0             | 0    | 1                      | 1   | 0   | 4Ch |

| VDD | VDD          | VDD | 0    | 1  | 0             | 0    | 1                      | 1   | 1   | 4Eh |

| GND | GND          | SCL | 0    | 1  | 0             | 1    | 0                      | 0   | 0   | 50h |

| GND | GND          | SDA | 0    | 1  | 0             | 1    | 0                      | 0   | 1   | 52h |

| GND | VDD          | SCL | 0    | 1  | 0             | 1    | 0                      | 1   | 0   | 54h |

| GND | VDD          | SDA | 0    | 1  | 0             | 1    | 0                      | 1   | 1   | 56h |

| VDD | GND          | SCL | 0    | 1  | 0             | 1    | 1                      | 0   | 0   | 58h |

| VDD | GND          | SDA | 0    | 1  | 0             | 1    | 1                      | 0   | 1   | 5Ah |

| VDD | VDD          | SCL | 0    | 1  | 0             | 1    | 1                      | 1   | 0   | 5Ch |

| VDD | VDD          | SDA | 0    | 1  | 0             | 1    | 1                      | 1   | 1   | 5Eh |

#### Table 6. PCA9655E ADDRESS MAP

#### Table 6. PCA9655E ADDRESS MAP

|     | Address Inpu | ıt  |    |    |            | Slav | <mark>e Address</mark> |     |    |     |

|-----|--------------|-----|----|----|------------|------|------------------------|-----|----|-----|

| AD2 | AD1          | AD0 | A6 | A5 | <b>A</b> 4 | A3   | A2                     | A1  | A0 | HEX |

| SCL | SCL          | GND | 1  | 0  | 1          | 0    | 0                      | 0   | 0  | A0h |

| SCL | SCL          | VDD | 1  | 0  | 1          | 0    | 0                      | 0   | 1  | A2h |

| SCL | SDA          | GND | 1  | 0  | 1          | 0    | 0                      | 1   | 0  | A4h |

| SCL | SDA          | VDD | 1  | 0  | 1          | 0    | 0                      | 1   | 1  | A6h |

| SDA | SCL          | GND | 1  | 0  | 1          | 0    | 1                      | 0   | 0  | A8h |

| SDA | SCL          | VDD | 1  | 0  | 1          | 0    | 1                      | 0   | 1  | AAh |

| SDA | SDA          | GND | 1  | 0  | 1          | 0    | 1                      | 1   | 0  | ACh |

| SDA | SDA          | VDD | 1  | 0  | 1          | 0    | 1                      | 1   | 1  | AEh |

| SCL | SCL          | SCL | 1  | 0  | 1          | 1    | 0                      | 0   | 0  | B0h |

| SCL | SCL          | SDA | 1  | 0  | 1          | 1    | 0                      | 0   | 1  | B2h |

| SCL | SDA          | SCL | 1  | 0  | 1          | 1    | 0                      | 1   | 0  | B4h |

| SCL | SDA          | SDA | 1  | 0  | 1          | 1    | 0                      |     |    | B6h |

| SDA | SCL          | SCL | 1  | 0  | 1          | 1    | 1                      | 0   | 0  | B8h |

| SDA | SCL          | SDA | 1  | 0  | 1          | 1    |                        | 0   | 1  | BAh |

| SDA | SDA          | SCL | 1  | 0  | 1          | 1    | 1                      | 1 . | 0  | BCh |

| SDA | SDA          | SDA | 1  | 0  | 1          | 1    | R I                    | 1   | F  | BEh |

| SCL | GND          | GND | 1  | 1  | 0          | 0    | 0                      | 0   | 0  | C0h |

| SCL | GND          | VDD | 1  | 1  | 0          | 0    | 20                     | 0   | 1  | C2h |

| SCL | VDD          | GND | 1  | 1  | 9          |      | _00                    | 1   | 0  | C4h |

| SCL | VDD          | VDD | 1  | 1  | 0          | 0    | 0                      | 1   | 1  | C6h |

| SDA | GND          | GND | 1  |    | 10         |      | 1                      | 0   | 0  | C8h |

| SDA | GND          | VDD | 1  |    | 0          | 0    | 1                      | 0   | 1  | CAh |

| SDA | VDD          | GND |    | 0  | 0          | 0    | 1                      | 1   | 0  | CCh |

| SDA | VDD          | VDD | 10 | XP | 0          | 0    | 1                      | 1   | 1  | CEh |

| SCL | GND          | SCL |    | t  | 1          | 0    | 0                      | 0   | 0  | E0h |

| SCL | GND          | SDA |    | 1  | 1          | 0    | 0                      | 0   | 1  | E2h |

| SCL | VDD          | SCL |    | 1  | 1          | 0    | 0                      | 1   | 0  | E4h |

| SCL | VDD          | SDA | 1  | 1  | 1          | 0    | 0                      | 1   | 1  | E6h |

| SDA | GND          | SCL | 1  | 1  | 1          | 0    | 1                      | 0   | 0  | E8h |

| SDA | GND          | SDA | 1  | 1  | 1          | 0    | 1                      | 0   | 1  | EAh |

| SDA | VDD          | SCL | 1  | 1  | 1          | 0    | 1                      | 1   | 0  | ECh |

| SDA | VDD          | SDA | 1  | 1  | 1          | 0    | 1                      | 1   | 1  | EEh |

#### REGISTERS

#### **Command Byte**

During a write transmission, the address byte is followed by the command byte. The command byte determines which of the following registers will be written or read.

#### Table 7. COMMAND BYTE

| COMMAND | REGISTER                  |

|---------|---------------------------|

| 0       | Input Port 0              |

| 1       | Input Port 1              |

| 2       | Output Port 0             |

| 3       | Output Port 1             |

| 4       | Polarity Inversion Port 0 |

| 5       | Polarity Inversion Port 1 |

| 6       | Configuration Port 0      |

| 7       | Configuration Port 1      |

#### **Registers 0 and 1: Input Port Registers**

#### Table 8. INPUT PORT 0 REGISTER

| Registers 0 an                                                                                                                                                   | d 1: Input Por | t Registers | The externally-             | The externally-applied logic level determines the default |      |      |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|-----------------------------|-----------------------------------------------------------|------|------|--|--|

|                                                                                                                                                                  |                |             | ect the incoming value 'X'. | Ri                                                        |      |      |  |  |

| logic levels of the pins, regardless of whether the pin is<br>defined as an input or an output by Registers 6 or 7. Writes<br>to these registers have no effect. |                |             |                             |                                                           |      |      |  |  |

| C                                                                                                                                                                | T PORT 0 RE    |             | ENDER                       | RMA                                                       |      |      |  |  |

| Bit                                                                                                                                                              |                |             |                             |                                                           |      |      |  |  |

| Symbol                                                                                                                                                           | 10.7           | 10.6        | 10.5 10.4 10.3              | 10.2                                                      | l0.1 | 10.0 |  |  |

| Default X X X X X X X X X X                                                                                                                                      |                |             |                             |                                                           |      |      |  |  |

## Table 9. INPUT PORT 1 REGISTER

| Bit     | 7    | 6 5  | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|

| Symbol  | 11.7 | 11.6 | l1.4 | l1.3 | l1.2 | l1.1 | l1.0 |

| Default | ×    | х    | Х    | Х    | Х    | Х    | Х    |

#### **Registers 2 and 3: Output Port Registers**

These registers are output-only. They reflect the outgoing logic levels of the pins defined as outputs by Registers 6 and 7. Bit values in these registers have no effect on pins defined

as inputs. In turn, reads from these registers reflect the values that are in the flip-flops controlling the output selection, not the actual pin values.

#### Table 10. OUTPUT PORT 0 REGISTER

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### Table 11. OUTPUT PORT 1 REGISTER

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | 01.7 | O1.6 | O1.5 | 01.4 | O1.3 | 01.2 | 01.1 | O1.0 |

| Default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

#### **Registers 4 and 5: Polarity Inversion Registers**

These registers allow the polarity of the data in the input port registers to be inverted. The input port data polarity will be inverted when its corresponding bit in these registers is set (written with '1'), and retained when the bit is cleared (written with a '0').

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### Table 13. POLARITY INVERSION PORT 1 REGISTER

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|---------|------|------|------|------|------|------|------|------|

| Symbol  | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| Default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

#### **Registers 6 and 7: Configuration Registers**

The I/O pin directions are configured through the configuration registers. When a bit in the configuration registers is set (written with '1'), the bit's corresponding port pin is enabled as an input with the output driver in

high-impedance. When a bit is cleared (written with '0'), the corresponding port pin is enabled as an output. Note that there is a high value resistor tied to  $V_{DD}$  at each pin. At reset, the device's ports are inputs with a pull-up to  $V_{DD}$ .

#### Table 14. CONFIGURATION PORT 0 REGISTER

| Bit     | 7    | 6    | 5 4       | 3    | S2            | $\mathcal{O}_1$ | 0    |

|---------|------|------|-----------|------|---------------|-----------------|------|

| Symbol  | C0.7 | C0.6 | C0.5 C0.4 | C0.3 | C0.2          | C0.1            | C0.0 |

| Default | 1    | 1    | 1 1       |      | $\mathcal{O}$ | 1               | 1    |

#### Table 15. CONFIGURATION PORT 1 REGISTER

| Bit     | 7 6       | 5 4       | О` <sub>3</sub> | 2    | 1    | 0    |

|---------|-----------|-----------|-----------------|------|------|------|

| Symbol  | C1.7 C1.6 | C1.5 C1.4 | C1.3            | C1.2 | C1.1 | C1.0 |

| Default | 1         |           | 1               | 1    | 1    | 1    |

#### Power-on Reset

Upon application of power, an internal Power–On Reset (POR) holds the PCA9655E in a reset condition while  $V_{DD}$  is ramping up. When  $V_{DD}$  has reached  $V_{POR}$ , the reset condition is released and the PCA9655E registers and SMBus state machine will initialize to their default states. The reset is typically completed by the POR and the part enabled by the time the power supply is above  $V_{POR}$ . However, when doing a power reset cycle, it is necessary to lower the power supply below 0.2 V, and then restored to the operating voltage. Please refer to application note AND9169/D for recommended power–up and power–cycle reset profiles.

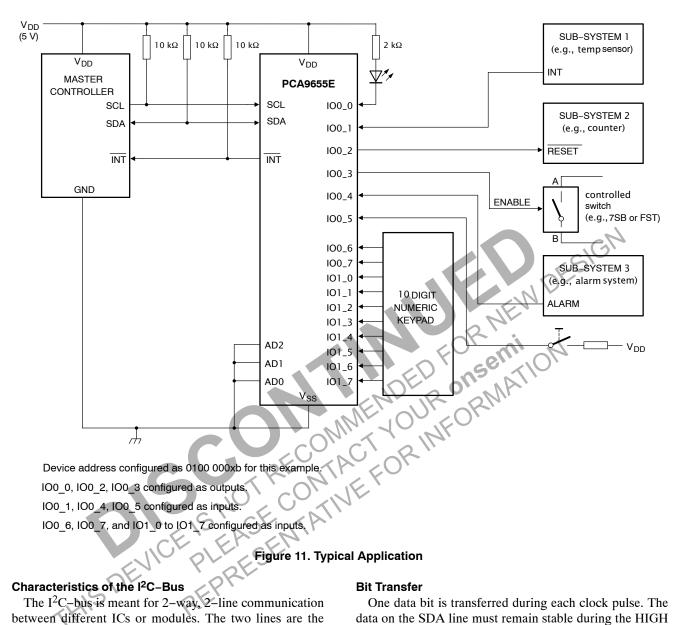

#### I/O Port (see Figure 2)

When an I/O pin is configured as an input, FETs Q1 and Q2 are off, creating a high–impedance input with a weak pull–up (100 k $\Omega$  typ) to V<sub>DD</sub>. The input voltage may be raised above V<sub>DD</sub> to a maximum of 5.5 V.

When the I/O pin is configured as an output, then either Q1 or Q2 is enabled, depending on the state of the Output Port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low-impedance path that exists between the pin and either  $V_{DD}$  or  $V_{SS}$ .

#### **BUS TRANSACTIONS**

#### Writing to the Port Registers

To transmit data to the PCA9655E, the bus master must first send the device address with the least significant bit set to logic 0 (see Figure 5 "PCA9655E device address"). The command byte is sent after the address and determines which registers will receive the data following the command byte.

There are eight registers within the PCA9655E. These registers are configured to operate as four register pairs:

Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. Data bytes are sent alternately to each register in a register pair (see Figures 6 and 7). For example, if one byte is sent to Output Port 1 (register 3), then the next byte will be stored in Output Port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8–bit register may be updated independently of the other registers.

#### Reading the Port Registers

To read data from the PCA9655E, the bus master must first send the PCA9655E address with the least significant bit set to logic 0 (see Figure 5 "PCA9655E device address"). The command byte is sent after the address and determines which register will be accessed.

After a restart, the device address must be sent again, but this time, the least significant bit is set to logic 1. Data from the register defined by the command byte will then be sent by the PCA9655E (see Figures 8, 9 and 10). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but with data alternately coming from each register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the bus master must not acknowledge the data for the final byte received.

Remark: Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to '00' (read Input Port register). THISDE

Figure 9. Read from Input Port Register, Scenario 1

| SCL ALAJA                       |                                | w                                | $\mathcal{M}$              | Ŵ | Л              | VVV     | W                                       | Л              | Ŵ | Ŵ        | W               | M             | ЛЛ       | $\overline{M}$ | Ŵ                    | ſ         |

|---------------------------------|--------------------------------|----------------------------------|----------------------------|---|----------------|---------|-----------------------------------------|----------------|---|----------|-----------------|---------------|----------|----------------|----------------------|-----------|

| slave_a                         | ddress R/W                     | 10                               | .x                         |   |                | l1.x    |                                         |                |   | 10.x     |                 | _             |          | l <u>1</u> .x  | STOP                 | condition |

| SDA S A6 A5 A4 A3               | A2A1A0 1 A                     | DAT                              | 400                        | A | 1 1            | DATA 10 |                                         | А              |   | DATA 03  | <br>            | Α             |          | DATA 12        |                      | 1 P       |

| START condition                 | t<br>acknowledge<br>from slave | <del>•</del> — <sup>‡</sup> h(D) | acknowledge<br>from master |   |                |         | nowled<br>om mas<br>su(D <del>) *</del> | †<br>ge<br>ter | _ | ac<br>fr | knowle<br>om ma | edge<br>aster |          | non a<br>fi    | acknowle<br>rom mast | dge<br>er |

| read from port 0                |                                | 41(D)                            |                            |   |                |         | su(D)                                   | _[             | \ |          |                 |               |          |                |                      |           |

| data into port 0                | DATA 00                        |                                  | DATA 01                    |   | $\square$      | DATA 0  | 2                                       |                |   | DATA 0   | 3               |               |          |                |                      |           |

| read from port 1                |                                |                                  |                            | λ | t <sub>h</sub> | (D)     |                                         |                |   | ts       | u(D) +          |               | <u>`</u> |                |                      |           |

| data into port 1                | DA                             | TA 10                            |                            |   |                |         | Dł                                      | TA 1           | 1 |          |                 |               |          | DATA 12        | 2                    |           |

| INT<br>t <sub>v</sub> (int n) – | +<br>+<br>+<br>+<br>+          | - t <sub>rst(INT N</sub>         | )                          |   |                |         |                                         |                |   |          |                 |               |          |                |                      |           |

Remark: Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to '00' (read Input Port register).

Figure 10. Read from Input Port Register, Scenario 2

#### Interrupt Output

The open-drain interrupt output is activated when an I/O pin configured as an input changes state. The interrupt is deactivated when the input pin returns to its previous state or when the Input Port register is read (see Figure 9). A pin configured as an output cannot cause an interrupt. Since

each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way

Remark: Changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.

#### APPLICATION INFORMATION

#### Characteristics of the I<sup>2</sup>C-Bus

The I<sup>2</sup>C-bus is meant for 2-way, 2-line communication between different ICs or modules. The two lines are the serial data line (SDA) and the serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may only be initiated when the bus is not busy.

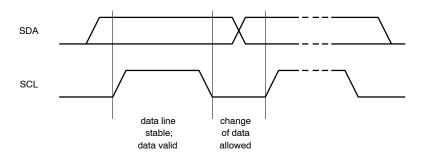

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse. Changes in the data line during the HIGH period of the clock pulse will be interpreted as control signals (see Figure 12).

Figure 12. Bit Transfer

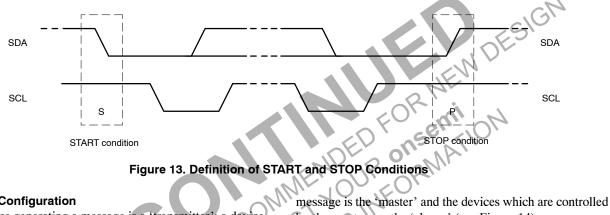

#### START and STOP Conditions

Both data and clock lines remain HIGH when the bus is not busy. A START condition (S) occurs when there is a HIGH-to-LOW transition of the data line while the clock is HIGH. A STOP condition (P) occurs when there is a LOW-to-HIGH transition of the data line while the clock is HIGH (see Figure 13).

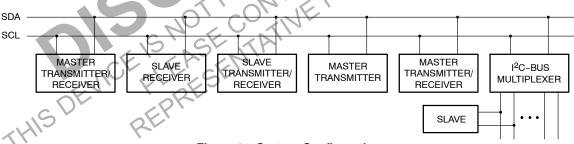

#### **System Configuration**

A device generating a message is a 'transmitter'; a device The device that controls the receiving is the 'receiver'.

by the master are the 'slaves' (see Figure 14).

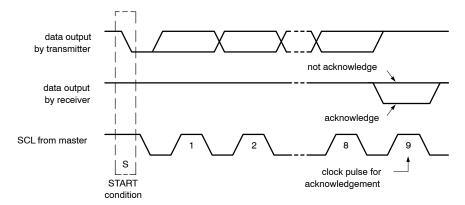

#### Acknowledge

The number of data bytes transferred between the START and the STOP conditions from transmitter to receiver is not limited. Each 8-bit byte is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter, whereas the master generates an extra clock pulse for the acknowledge bit.

A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also, a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The

device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, such that the SDA line is stable LOW during the HIGH period of the acknowledge clock pulse; set-up time and hold time must be taken into account.

A master receiver signals an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this event, the transmitter must leave the data line HIGH to enable the master to generate a STOP condition.

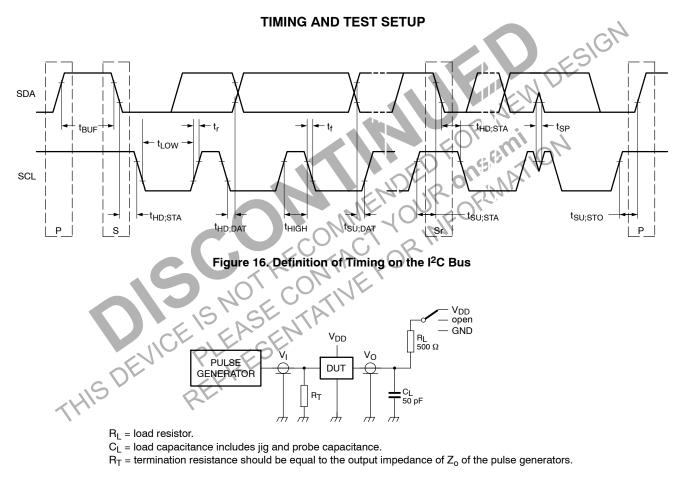

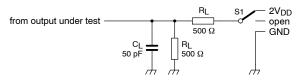

Figure 17. Test Circuitry for Switching Times

Figure 18. Load Circuit

#### ORDERING INFORMATION

| Device        | Package               | Shipping <sup>†</sup> |

|---------------|-----------------------|-----------------------|

| PCA9655EDWR2G | SOIC-24<br>(Pb-Free)  | 1000 / Tape & Reel    |

| PCA9655EDTR2G | TSSOP-24<br>(Pb-Free) | 2500 / Tape & Reel    |

| PCA9655EMTTXG | WQFN24<br>(Pb–Free)   | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

# onsemi

| DOCUMENT NUMBER:                                                                     | 98ASB42344B Electronic versions are uncontrolled except when accessed directly from the Document Report<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |                                                                                                                                                                                                                                                                                                                 |                           |  |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

| DESCRIPTION:                                                                         | DESCRIPTION: SOIC-24 WB                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                 |                           |  |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume an | er notice to any products herein. <b>onsemi</b> make<br>ny liability arising out of the application or use                                                                                 | LLC dba <b>onsemi</b> or its subsidiaries in the United States and/or other cours<br>so no warranty, representation or guarantee regarding the suitability of its pr<br>of any product or circuit, and specifically disclaims any and all liability, inc<br>e under its patent rights nor the rights of others. | oducts for any particular |  |  |  |

# semi

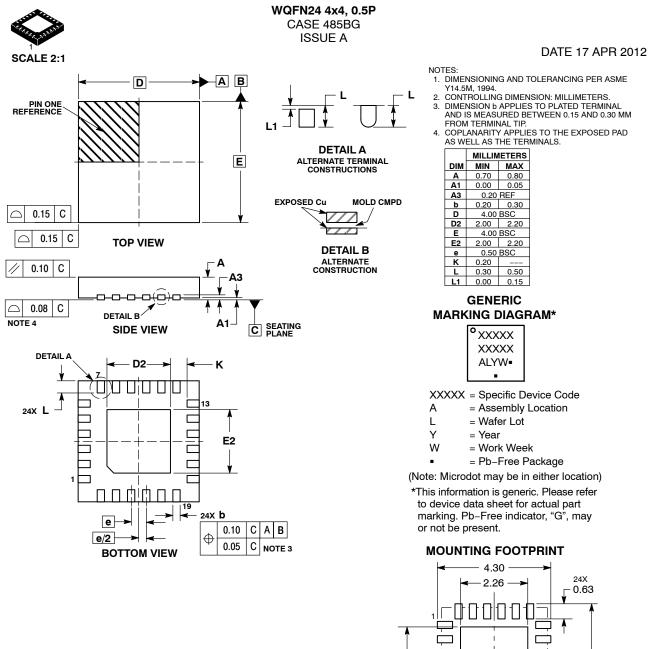

| 2.26                |  |     | 4.30     |

|---------------------|--|-----|----------|

| PACKAGE_<br>OUTLINE |  | 24X | <b>¥</b> |

DIMENSIONS: MILLIMETERS

| DOCUMENT NUMBER: | 98AON48315E      | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | WQFN24 4X4, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 1 |

onsemi and ONSEMi. are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. **onsemi** makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

XXXX = Specific Device Code A = Assembly Location L = Wafer Lot Y = Year W = Work Week G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

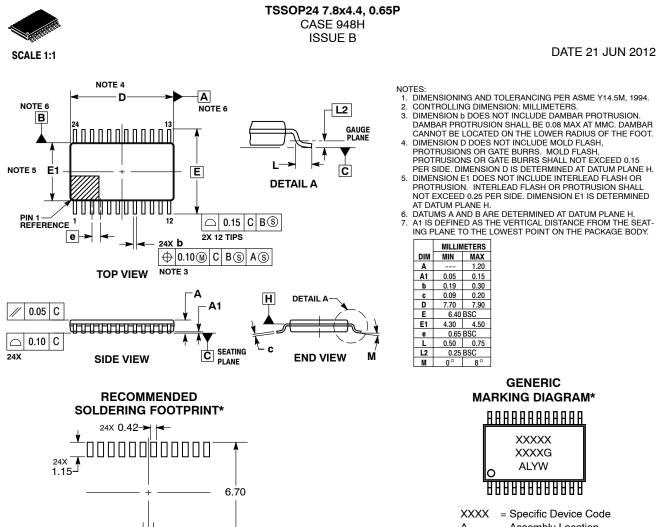

| DOCUMENT NUMBER:                                                                                                                                                          | 98ASH70248A            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:                                                                                                                                                              | TSSOP24 7.8X4.4, 0.65P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |

| onsemi and ONSEMI, are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves |                        |                                                                                                                                                                                     |             |  |

the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **Onsemi** does not convey any license under its pattern rights of others.

ппппп

Techniques Reference Manual, SOLDERRM/D.

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the **onsemi** Soldering and Mounting

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>