# JN Semiconductor®

To kara more about Old Semiconductor, please visit our website at

Please note. As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">questions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

December 2011

# RV4141A Low-Power, Ground-Fault Interrupter

#### **Features**

- Powered from the AC Line

- Built-In Rectifier

- Direct Interface to SCR

- 500µA Quiescent Current

- Precision Sense Amplifier

- Adjustable Time Delay

- Minimum External Components

- Meets UL 943 Requirements

- Compatible with 110V or 220 Systen

- Available in an 8-Pir

### **Description**

The RV4141A is a re-power controller for AC-receptacle, round-ult interrupters. These devices tec azaro scurrent prins to ground and ground to reur facts. The circuit interrupter then disc the local from the line before a harmful or that hock are.

Int. pall, the RV4141A contains a diode rectifier, shunt regulator, precision sense amplifier current reference, time-delayourum, and SoR driver.

Two sense transionners, SCR solenoid, three resistors, and four capacitors complete the design of the basic circuit interrupter. The simple layout and minimum component count and ure ease of application and long-term reliability. Features not found in other GFCI controllers include a low offset voltage sense amplifier, eliminating the need for a coupling capacitor between the sense transformer and sense amplifier, and an internal rectifier to eliminate high-voltage rectifying diodes.

The RV4141A is powered only during the positive half period of the line voltage, but can sense current faults independent of its phase relative to the line voltage. The gate of the SCR is driven only during the positive half cycle of the line voltage.

# Ordering Information

| Part Number | Operating<br>Temperature<br>Range | Package                                                 | Packing<br>Method |

|-------------|-----------------------------------|---------------------------------------------------------|-------------------|

| RV4141AN    | -35 to +80°C                      | 8-Lead, Plastic Dual-Inline Package (DIP)               | Rails             |

| RV4141AMT   | -35 to +80°C                      | 8-Lead, Plastic Small-Outline Integrated Circuit (SOIC) | Tape and Reel     |

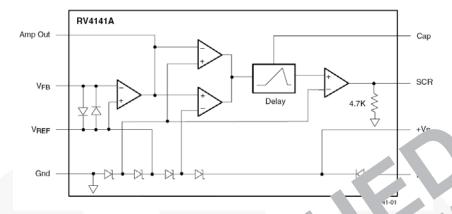

## **Block Diagram**

Figure 1. Block Diagram

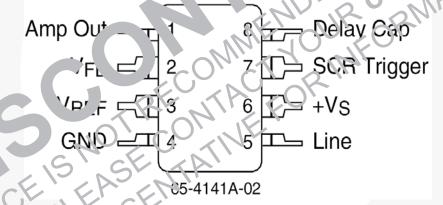

# **Pin Configuration**

Figure 2. Pin Assignment

#### Pin Definitions

| Pin# | Name                                                                                                                      | Description                                                                                            |  |

|------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| 1    | Amp Out                                                                                                                   | Sense Amplifier Output – an external resistor to V <sub>FB</sub> sets the I <sub>FAULT</sub> threshold |  |

| 2    | $V_{FB}$                                                                                                                  | Sense amplifier negative input                                                                         |  |

| 3    | $V_{REF}$                                                                                                                 | Sense amplifier positive input – biased internally at +V <sub>S</sub> /2                               |  |

| 4    | GND                                                                                                                       | Substrate ground for all circuitry                                                                     |  |

| 5    | Line                                                                                                                      | Anode of internal diode connected to supply voltage                                                    |  |

| 6    | +V <sub>S</sub>                                                                                                           | V <sub>S</sub> Supply input for RV4141A circuitry                                                      |  |

| 7    | SCR Trigger Output for triggering external SCR when a fault is detected                                                   |                                                                                                        |  |

| 8    | Delay Cap  An external capacitor to ground sets the delay time for a ground fault to be present before triggering the SCR |                                                                                                        |  |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                   |                  |  | Max. | Unit |

|------------------|-----------------------------|------------------|--|------|------|

| V <sub>CC</sub>  | Power Supply                |                  |  | 10   | mA   |

| $P_D$            | Internal Power Dissipation  |                  |  | 500  | mW   |

| T <sub>STG</sub> | Storage Temperature Range   |                  |  | +150 | °C   |

| T <sub>A</sub>   | Operating Temperature Range |                  |  | +80  | °C   |

| TJ               | Junction Temperature        |                  |  | 125  | °C   |

| T <sub>L</sub>   | Lead Soldering Temperature  | 10 Seconds, SOIC |  | + 30 | ° C  |

|                  |                             | 60 Seconds, DIP  |  | ٥٥   | (2)  |

### **Thermal Characteristics**

| Symbol        |                    | Paramete: | Typ Max. Unit |

|---------------|--------------------|-----------|---------------|

| $\Theta_{JA}$ | Thermal Resistance | SUIC      | 2+0 °C/W      |

### **Electrical Characteristics**

$I_{LINE}$  = 1.5mA and  $T_A$  = +25°C,  $R_{SET}$ = 650k $\Omega$ .

| Symbol            | Parameter                | Conditions                                | Min.  | Тур. | Max. | Units |

|-------------------|--------------------------|-------------------------------------------|-------|------|------|-------|

| Shunt Regula      | tor (Pins 5 to 4)        |                                           |       |      | •    |       |

| $V_{REG}$         | Regulated Voltage        | I <sub>2-3</sub> = 11μA                   | 25    | 27   | 29   | V     |

|                   |                          | $I_{LINE} = 750 \mu A, I_{2-3} = 9 \mu A$ | 25    | 27   | 29   |       |

| IQ                | Quiescent Current        | V <sub>5-4</sub> = 24V                    |       | 500  |      | μA    |

| Sense Amplif      | ier (Pins 2 to 3)        |                                           |       |      |      |       |

| $V_{OFF}$         | Offset Voltage           |                                           | -200  | 0    | 200  | μV    |

| GBW               | Gain Bandwidth           | Design Value                              |       | 3    |      | MHz   |

| t <sub>sk</sub>   | Slew Rate                | Design Value                              |       |      |      | V/µS  |

| I <sub>BIAS</sub> | Input Bias Current       | Design Value                              |       | 30   | 10   | rA    |

| SCR Trigger (     | (Pins 7 to 4)            |                                           |       |      | 1/1. |       |

| R <sub>OUT</sub>  | Output Resistance        | $V_{7-4}$ = Open, $I_{2-3}$ = $\mu A$     | 7.8   | 4.   | 5.6  | kΩ    |

| V                 | Output Voltage           | I <sub>2-3</sub> = 9μA                    |       | 0.1  | 10.0 | mV    |

| $V_{OUT}$         |                          | I <sub>2-3</sub> = 11μA                   | 3.0   | 3.5  | 4.5  | V     |

| I <sub>OUT</sub>  | Output Current           | V <sub>7-4</sub> = 0V = 11,               | 400   | 600  | 3/11 | μA    |

| Reference Vo      | Itage (Pins 3 to 4)      |                                           | 7     | 109  | 77   |       |

| $V_{REF}$         | Reference Voltage        | = 50µA                                    | 12    | 13   | 14   | V     |

| Delay Timer (     | Pins 8 to 4)             | 181                                       | 0///  | OR   | 7.   |       |

|                   | Discharge / Char = Ratio | I <sub>2-3</sub> 0/11μ'Α                  | 1.8   | 2.5  | 3.0  | μΑ/μΑ |

| t <sub>DLY</sub>  | Delay Ti                 | $C_{8-4} = 12nF$                          | 2/1/2 | 2    |      | ms    |

| I <sub>DLY</sub>  | Delay ( rrent            | 12.2 = 1/µA                               | 30    | 40   | 50   | μA    |

#### Notes:

1. Delay time the scarting when the instantaneous sense current ( $I_{2-3}$ ) exceeds 6.5V/R<sub>SET</sub> and ending when the SC trigger vol. ge  $V_{7-6}$  goes HIGH.

### **Circuit Operation**

(Refer to Figure 1 and Figure 3.)

The precision op amp connected to pins 1 through 3 senses the fault current flowing in the secondary of the sense transformer, converting it to a voltage at pin 1. The ratio of secondary current to output voltage is directly proportional to feedback resistor,  $R_{\text{SET}}$ .

$R_{\text{SET}}$  converts the sense transformer secondary current to a voltage at pin 1. Due to the virtual ground created at the sense amplifier input by its negative feedback loop, the sense transformer's burden is equal to the value of  $R_{\text{IN}}.$  From the transformer's point of view, the ideal value for  $R_{\text{IN}}$  is  $0\Omega.$  This causes it to operate as a true current transformer with minimal error. However, making  $R_{\text{IN}}$  equal to zero creates a large offset voltage at pin 1 due to the sense amplifier's very high DC gain.  $R_{\text{IN}}$  should be selected as high as possible, consistent with preserving the transformer's operation as a true current mode transformer. A typical value for  $R_{\text{IN}}$  is between 200 and  $1000\Omega.$

As seen in Equation (1), maximizing  $R_{\text{IN}}$  minimizes the DC offset error at the sense amplifier output. The DC offset voltage at pin 1 contributes directly to the tricurrent error. The offset voltage at pin 1 is:

$$V_{\rm OS} \times R_{\rm SET} / (R_{\rm IN} + RS_{\rm EC}) \tag{1}$$

where:

Vos = Input offset voltage of sense amplia

R<sub>SET</sub> = Feedback resistor;

$R_{IN}$  = Input resistor;

R<sub>SEC</sub> = Transformer sec idary wino. Listance.

The sense am ha a spriffed maximum offset voltage of 20 IV to minitude program terrors. Two comparations of the sense an pliffer of the tare configured a windor detector whose references are not on 3. When the sense it is sform secondary RMS current exceeds 4.6/F SET, the utput if the window detector stands the dislay circuit. If the condary current exceeds the predictermined trip current for longer than (no delay time, a current pulse appears at pin 7, triggering the SCR.

The SCR anode is directly connected to a solenoid or relay coil. The SCR can be tripped only when its anode is more positive than its cathode.

### **Supply Current Requirements**

The RV4141A is powered directly from the line through a series-limiting resistor called  $R_{LINE}$ ; its value is between 24k $\Omega$  and 91k $\Omega$ .

The controller IC has a built-in diode rectifier, eliminating the need for external power diodes. The recommended value for  $R_{\text{LINE}}$  is  $24 k\Omega$  to  $47 k\Omega$  for 110V systems and  $47 k\Omega$  to  $91 k\Omega$  for 220V systems. When  $R_{\text{LINE}}$  is  $47 k\Omega$ , the shunt regulator current is limited to 3.6mA. The recommended maximum peak line current through  $R_{\text{LINE}}$  is 10mA.

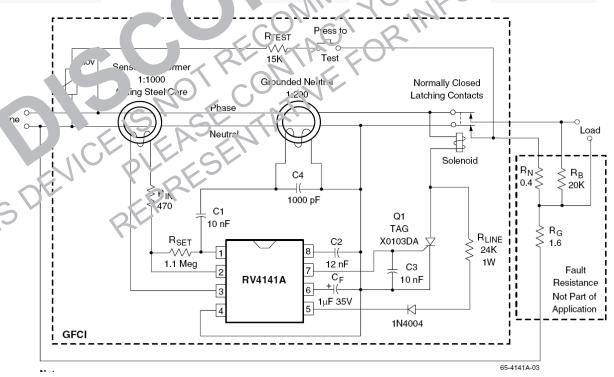

### **GFCI Application**

(Refer to Figure 3)

The GFCI detects a ground fault by sensing a difference in current in the line and neutral wires. The difference in current is assumed to be a fault current creating a potentially hazardous path from line to ground. Since the line and neutral wires pass through the center of the sense transformer, only the differential primary current is transferred to the secondary. Assuming the turns ratio is 1:1000, the secondary current is 1/1000th the fault current. The RV4141A's sense amplifier converts the secondary current to a voltage and with either of the two window detector reference voltages. If the fault current exceeds the design value of the uration of any programmed time delate the V411 sends a surrent pulse to the gate of the secondary current with a sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the gate of the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent pulse to the secondary current with sends a surrent sends a surrent sends a surrent sen

Detecting grand-to-inutral cults is more difficult.  $R_B$  represent a normal gound fault resistance.  $R_N$  is the wire resistance of the electrical circuit between load/neuronal represents the ground-to-inutral fault condition. According to u'L 943, the GFCI must trip when  $R_N=0.4\Omega,\ R_G=1.5\Omega,\ and\ trip normal ground fault is 6nA$

Assuming the ground flut to be 5n A, 1mA, and 4mA goes inclugh  $P_G$  and  $R_N$  respectively, causing an effective 1mA fault current. This current is detected by the sense transformer and amplified by the sense amplifier. The ground I neutral and sense transformers are mutually coupled by  $R_G$ ,  $R_N$ , and the neutral wire ground loop, producing a positive feedback loop around the sense amplifier. The newly created feedback loop causes the sense amplifier to oscillate at a frequency determined by ground/neutral transformer secondary nauctance and C4, which occurs at 8KHz.

C2 is used to program the time required for the fault to be present before the SCR is triggered. Refer to Equation (2) for calculating the value of C2. Its typical value is 12nF for a 2ms delay.  $R_{\text{SET}}$  is used to set the fault current at which the GFCI trips. When used with a 1:1000 sense transformer, its typical value is  $1\text{M}\Omega$  for a GFCI designed to trip at 5mA.

$R_{\text{IN}}$  should be the highest value possible that ensures a predictable secondary current from the sense transformer. If  $R_{\text{IN}}$  is set too high, normal production variations in the transformer permeability causes unit-to-unit variations in the secondary current. If it is too low, a large offset voltage error at pin 1 is present. This error voltage in turn creates a trip current error proportional to the input offset voltage of the sense amplifier. As an example, if  $R_{\text{IN}}$  is  $500\Omega,~R_{\text{SET}}$  is  $1M\Omega,~R_{\text{SEC}}$  is  $45\Omega,$  and the  $V_{\text{OS}}$  of the sense amplifier is its maximum of  $200\mu\text{V};$  the trip current error is  $\pm 5.6\%.$

The SCR anode is directly connected to a solenoid or relay coil. It can be tripped only when its anode is more positive than its cathode. It must have a high dV/dt rating to ensure that line noise (generated by electrically noisy appliances) does not falsely trigger it. Also the SCR must have a gate drive requirement less than  $200\mu A$ . C3 is a noise filter that prevents high-frequency line pulses from triggering the SCR. The relay solenoid should have a response time of 3ms or less to meet the UL 943 timing requirement.

#### **Sense Transformers and Cores**

The sense and ground/neutral transformer cores are usually fabricated using high-permeability laminated steel rings. Their single-turn primary is created by passing the line and neutral wires through the center of its core. The secondary is usually from 200 to 1500 turns. Transformers may be obtained from Magnetic Metals, Inc. (www.magmet.com).

### Calculating the Values of R<sub>SET</sub> and C2

Determine the nominal ground-fault trip-current requirement. This is typically 5mA in North America (117V $_{AC}$ ) and 22mA in the UK and Europe (220V $_{AC}$ ). Determine the minimum delay time required to prevent nuisance tripping, typically 1 to 2ms. The value of C2 required to provide the desired delay time is:

$$C2 = 6 \times t \tag{2}$$

where:

C2 is in Nf and t is the desired delay time in ms.

The value of R<sub>SET</sub> to meet the nominal ground fault trip current specification is:

$$R_{SET} = \frac{4.6 \times N}{I_{FAULT} \times CO^{c} \cdot sO(t/P)}$$

(3)

where

$R_{SET}$  is in  $k\Omega$ :

t is the time a by in n

P is the pool of the line frequency in rus;

I<sub>FAL</sub> the estimated the current in mA RMS; is a condary turns.

#### No 1

2. his formula assumes an ideal sence transformer is used. The calculated value of R<sub>SE</sub>, may have to be changed up to 30% when using a non-ideal transformer.

Figure 3. GFI Application Circuit

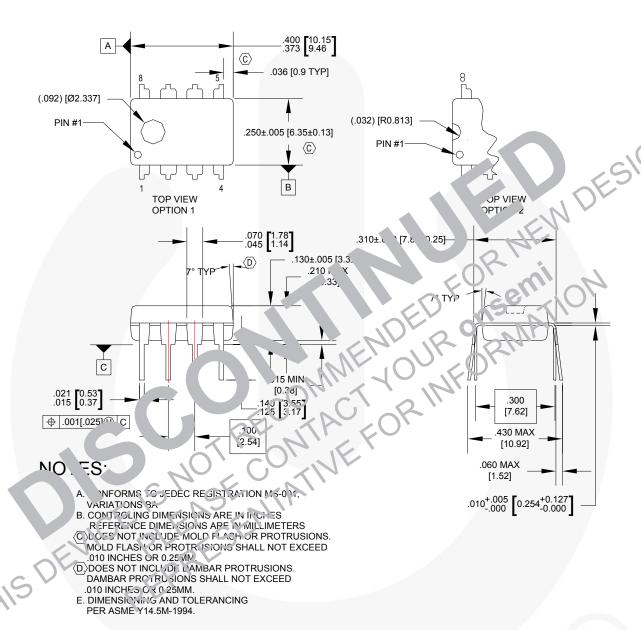

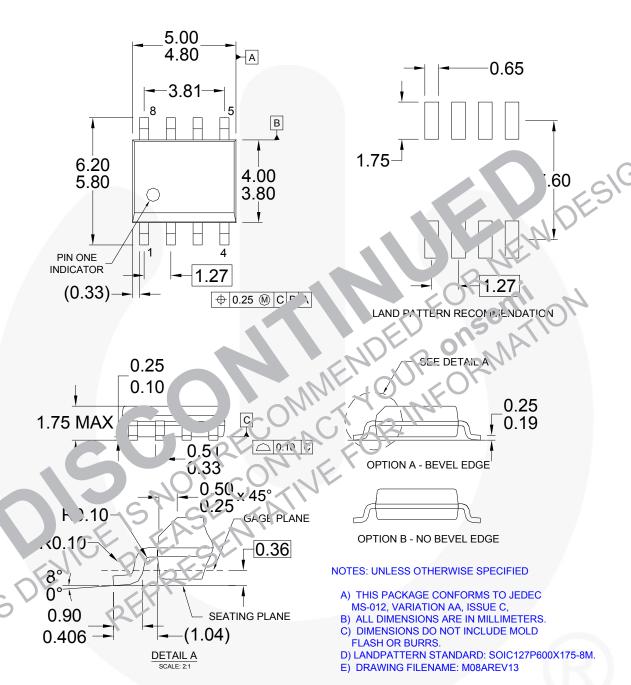

### **Physical Dimensions**

### N08EREVG

Figure 4. 8-Lead, Plastic Dual-Inline Package (DIP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

### **Physical Dimensions**

Figure 5. 8-Lead, Plastic Small-Outline Integrated Circuit (SOIC)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

2Cool™

FPS™

AccuPower™

F-PFS™

Auto-SPM™

FRFET®

AX-CAP™\*

Global Power Resource

BitSiC™

GreenBridge™

Build it Now™

Green FPS™

CorePLUS™

Green FPS™ e-Series™

CorePLUS™ Green FPS™  $\epsilon$ CorePOWER™ Gmax™ CROSSVOLT™ GTO™ CTL™ IntelliMAX™

Current Transfer Logic™ ISOPLANAR™

DEUXPEED<sup>®</sup> Making Small Speakers Sound Louder

Dual Cool™ and Better™

Dual Cool™

and Better™

EcoSPARK®

MegaBuck™

EfficientMax™

MICROCOUPLER™

ESBC™

MicroFET™

MicroPak™

MicroPak2™ Fairchild® MillerDrive™ Fairchild Semiconductor® MotionMax™ FACT Quiet Series™ Motion-SPM™ FACT mWSaver™ FAST<sup>®</sup> OptoHiT™ FastvCore™ OPTOLOGIC® FFTBench™ OPTOPLANAR® FlashWriter®\*

PowerTrench<sup>®</sup> PowerXS™

Programmable Active Droop™

QFET<sup>®</sup> QS™ Quiet Series™ RapidConfigure™

Saving our world, 1mW/W/kW at a time™

SignalWise™ SmartMax™ SMART START™ Solutions for Your S

Solutions for Your Successions

SPM°

STEALTH™

SuperFET®

SuperSOT™-3

Super OT™-6

Super

Syn ock

The Power Franchise®

Franchise

TinyBoost™

TinyBuck™

TinyCalc™

TinyLogic®

TINYOPTO™

TinyPower™

TinyPower™

TranSiC Fault D ct™ IECU' .ENT®

UHC® U'tr': AFET™ 'CX™ Visuali Max™ Voltr': Ç əh'us™

\* Trademarks of System General Corporation, used un "ense Fairchild miconducto

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES ZRIGI ON 'E CHANGES WITH SUMPRUTER IN ONCE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN, FAIR HILD DOE OF THE SUMPRUTE OF THE SUMPRUTE

#### LIFE SUPPORT POUR

FAIRCHILD'S PROJUCTS ARE IN TAIL OF A RIVER PROVIDED FOR SUSTEMS WITHOUT THE EXPRESS WRITE IN TAIL OF THE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITE IN TAIL OF THE SUPPORT ON THE SUPPORT ON THE SUPPORT OF T

#### As used her.

1 "fo sup at devices systems and devices or systems which (a) are tent for sugical implant into the forty or (b) support or sustable if (c) whose failure to perform whom properly load in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a sign float injury of not ser.

A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### ANTI JUNTERNEITING POLICY

Fairchild Semicon luctor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Salice Support.

Courtefe ting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed april lications, and increased country of production and manufacturing delays. Fairchild is taking strong measures to protect curselves and our customers from the proliferation of counterfeit parts, real-child strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

#### PRODUCT STATUS DEFINITIONS

#### Definition of Terms

| Definition of Terms      |                             |                                                                                                                                                                                                        |  |

|--------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Datasheet Identification | n Product Status Definition |                                                                                                                                                                                                        |  |

| Advance Information      | Formative / In Design       | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                          |  |

| Preliminary              | First Production            | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild<br>Semiconductor reserves the right to make changes at any time without notice to improve design. |  |

| No Identification Needed | Full Production             | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                                  |  |

| Obsolete                 | Not In Production           | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                       |  |

Rev. 160

ON Semiconductor and III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns me rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.

Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative