### Silicon Carbide (SiC) Combo JFET – EliteSiC, Power N-Channel, TO247-4, 750 V, 5.9 mohm

#### SiC JFET w/ Si MOSFET

### UG4SC075006K4S

#### Description

onsemi's UG4SC075006K4S "Combo-FET" integrates both a 750 V SiC JFET and a Low Voltage Si MOSFET into a single TO247-4 package. This innovative approach allows users to create circuitry that would enable a normally-off switch while leveraging the benefits of a normally-on SiC JFET. These benefits include ultra-low on-resistance (R<sub>DS(on)</sub>) to minimize conduction losses and the exceptional robustness characteristic of a simplified JFET device structure, making it capable of handling the high-energy switching required in circuit protection applications. For switch-mode power conversion application, this device provides separate access to the JFET and MOSFET gates for improved speed control and ease of paralleling multiple devices.

#### **Features**

- Single Digit R<sub>DS(on)</sub>

- Normally-off Capability

- Improved Speed Control

- Improved Parallel Device Operation (3+ FETs)

- Operating Temperature: 175 °C (Max)

- High Pulse Current Capability

- Excellent Device Robustness

- Silver-sintered Die Attach for Excellent Thermal Resistance

- Short Circuit Rated

- This Device is Pb-Free, Halogen Free and is RoHS Compliant

1

#### **Typical Applications**

- Solid State / Semiconductor Circuit Breaker

- Solid State / Semiconductor Relay

- Battery Disconnects

- Surge Protection

- Inrush Current Control

- High Power Switch Mode Converters (>25 kW)

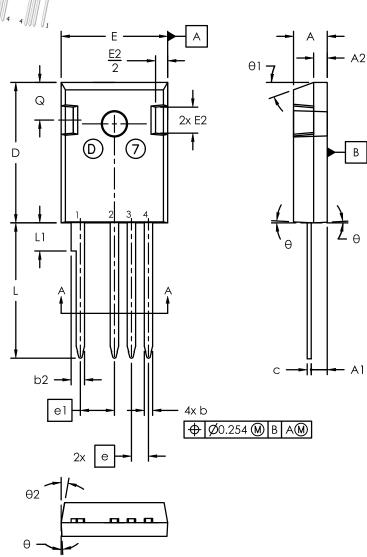

TO247-4 15.90x20.96x5.03, 5.44P CASE 340AN

#### **MARKING DIAGRAM**

UG4SC075006K4S = Specific Device Code A = Assembly Location

YY = Year WW = Work Week ZZZ = Lot ID

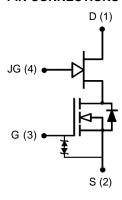

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 9 of this data sheet.

#### **MAXIMUM RATINGS**

| Parameter                               | Symbol                            | Test Conditions                                               | Value      | Unit |

|-----------------------------------------|-----------------------------------|---------------------------------------------------------------|------------|------|

| Drain-source Voltage                    | V <sub>DS</sub>                   |                                                               | 750        | V    |

| JFET Gate (JG) to Source Voltage        | $V_{JGS}$                         | DC                                                            | -30 to +3  | V    |

|                                         |                                   | AC (Note 1)                                                   | -30 to +30 | V    |

| MOSFET Gate (G) to Source Voltage       | $V_{GS}$                          | DC                                                            | -20 to +20 | V    |

|                                         |                                   | AC (f > 1 Hz)                                                 | -25 to +25 | V    |

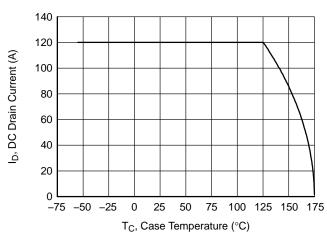

| Continuous Drain Current (Note 2)       | I <sub>D</sub>                    | T <sub>C</sub> < 125 °C                                       | 120        | Α    |

| Pulsed Drain Current (Note 3)           | I <sub>DM</sub>                   | T <sub>C</sub> = 25 °C                                        | 588        | Α    |

| Single Pulsed Avalanche Energy (Note 4) | E <sub>AS</sub>                   | L = 15 mH, I <sub>AS</sub> = 6.5 A                            | 316        | mJ   |

| Short Circuit Withstand Time            | t <sub>SC</sub>                   | $V_{DS} = 400 \text{ V}, T_{J(START)} = 175 ^{\circ}\text{C}$ | 5          | μs   |

| SiC FET dv/dt Ruggedness                | dv/dt                             | V <sub>DS</sub> < 500 V                                       | 100        | V/ns |

| Power Dissipation                       | P <sub>tot</sub>                  | T <sub>C</sub> = 25 °C                                        | 714        | W    |

| Maximum Junction Temperature            | $T_{J,max}$                       |                                                               | 175        | °C   |

| Operating and Storage Temperature       | T <sub>J</sub> , T <sub>STG</sub> |                                                               | -55 to 175 | °C   |

| Max. Lead Temperature for Soldering     | TL                                |                                                               | 250        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. +30 V ac rating applies for turn-on pulses <200 ns applied with external R<sub>G</sub> > 1  $\Omega$ .

- Limited by bondwires

Pulse width t<sub>p</sub> limited by T<sub>J,max</sub>

Starting T<sub>J</sub> = 25 °C

#### THERMAL CHARACTERISTICS

| Parameter                            | Symbol          | Test Conditions | Min | Тур  | Max  | Unit |

|--------------------------------------|-----------------|-----------------|-----|------|------|------|

| Thermal Resistance, Junction-to-Case | $R_{\theta JC}$ |                 | _   | 0.16 | 0.21 | °C/W |

#### **ELECTRICAL CHARACTERISTICS** ( $T_J = +25$ °C and $V_{JGS} = 0$ V unless otherwise specified)

| Parameter                                 | Symbol               | Test Conditi                                                                                           | ons                                               | Min  | Тур  | Max  | Unit |

|-------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|------|------|

| TYPICAL PERFORMANCE - STATIC              |                      |                                                                                                        |                                                   |      |      |      |      |

| Drain-source Breakdown Voltage            | BV <sub>DS</sub>     | V <sub>GS</sub> = 0 V, V <sub>JGS</sub> = 0 V,                                                         | I <sub>D</sub> = 1 mA                             | 750  | _    | _    | V    |

| Total Drain Leakage Current               |                      | $V_{DS} = 750 \text{ V}, V_{GS} = 0 \text{ V}, V_{JGS} = 0 \text{ V}, T_{J} = 25 ^{\circ}\text{C}$     |                                                   | -    | 6    | 130  | μΑ   |

|                                           |                      | $V_{DS} = 750 \text{ V}, V_{GS} = 0 \text{ V}$<br>$V_{JGS} = 0 \text{ V}, T_{J} = 175^{\circ}\text{C}$ |                                                   | -    | 45   | _    |      |

| Total JFET Gate Leakage Current           | I <sub>JGSS</sub>    | $V_{\rm JGS} = -20 \text{ V}, V_{\rm GS} = 1$                                                          | 2 V                                               | -    | 0.1  | 100  | μΑ   |

| Total MOSFET Gate Leakage Current         | I <sub>GSS</sub>     | $V_{GS} = -20 \text{ V} / +20 \text{ V}$                                                               |                                                   | -    | 6    | 20   | μΑ   |

| Drain-source On-resistance                | R <sub>DS(on)</sub>  | $V_{GS} = 12 \text{ V}, I_D = 80 \text{ A}$                                                            | V <sub>JGS</sub> = 2 V,<br>T <sub>J</sub> = 25 °C | -    | 5.3  | -    | mΩ   |

|                                           |                      |                                                                                                        | T <sub>J</sub> = 25 °C                            | -    | 5.9  | 7.5  |      |

|                                           |                      |                                                                                                        | T <sub>J</sub> = 125 °C                           | _    | 9.8  | _    | 1    |

|                                           |                      |                                                                                                        | T <sub>J</sub> = 175 °C                           | -    | 12.9 | _    |      |

| JFET Gate Threshold Voltage               | V <sub>JG(th)</sub>  | $V_{DS} = 5 \text{ V}, V_{GS} = 12 \text{ V}$                                                          | , I <sub>D</sub> = 180 mA                         | -8.3 | -6.0 | -3.7 | V    |

| MOSFET Gate Threshold Voltage             | $V_{G(th)}$          | $V_{DS} = 5 \text{ V}, V_{JGS} = 0 \text{ V},$                                                         | I <sub>D</sub> = 10 mA                            | 4    | 4.7  | 6    | V    |

| JFET Gate Resistance                      | $R_{JG}$             | f = 1 MHz, open drain                                                                                  |                                                   | -    | 0.8  | _    | Ω    |

| MOSFET Gate Resistance                    | $R_{G}$              | f = 1 MHz, open drain                                                                                  |                                                   | _    | 0.8  | _    | Ω    |

| TYPICAL PERFORMANCE - REVERSE DIO         | DE                   |                                                                                                        |                                                   |      |      |      |      |

| Diode Continuous Forward Current (Note 5) | I <sub>S</sub>       | T <sub>C</sub> < 125 °C                                                                                |                                                   | _    | _    | 120  | Α    |

| Diode Pulse Current (Note 6)              | I <sub>S,pulse</sub> | T <sub>C</sub> = 25 °C                                                                                 |                                                   | _    | -    | 588  | Α    |

#### **ELECTRICAL CHARACTERISTICS** ( $T_J = +25$ °C and $V_{JGS} = 0$ V unless otherwise specified) (continued)

| Parameter                                    | Symbol               | Test Conditions                                                                                                   | Min           | Тур  | Max  | Unit |

|----------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|---------------|------|------|------|

| TYPICAL PERFORMANCE – REVERSE DIOD           | Ε                    |                                                                                                                   |               |      |      |      |

| Forward Voltage                              | V <sub>FSD</sub>     | $V_{GS} = 0 \text{ V}, V_{JGS} = 0 \text{ V}, I_{S} = 50 \text{ A},$<br>$T_{J} = 25 ^{\circ}\text{C}$             | _             | 1.03 | 1.16 | V    |

|                                              |                      | $V_{GS} = 0 \text{ V, } V_{JGS} = 0 \text{ V, } I_{S} = 50 \text{ A,}$<br>$T_{J} = 175 ^{\circ}\text{C}$          | _             | 1.06 | -    |      |

| Reverse Recovery Charge                      | Q <sub>rr</sub>      | $V_{DS} = 400 \text{ V}, I_{S} = 80 \text{ A}, V_{GS} = 0 \text{ V}, V_{JGS} = 0 \text{ V}, R_{JG} = 0.7 \Omega,$ | _             | 377  | -    | nC   |

| Reverse Recovery Time                        | t <sub>rr</sub>      | $di/dt = 2400 \text{ A/}\mu\text{s}, T_J = 25 ^{\circ}\text{C}$                                                   | 1             | 70   | -    | ns   |

| Reverse Recovery Charge                      | Q <sub>rr</sub>      | $V_{DS} = 400 \text{ V}, I_{S} = 80 \text{ A}, V_{GS} = 0 \text{ V}, V_{JGS} = 0 \text{ V}, R_{JG} = 0.7 \Omega,$ | -             | 427  | -    | nC   |

| Reverse Recovery Time                        | t <sub>rr</sub>      | $di/dt = 2400 \text{ A/}\mu\text{s}, T_J = 150 ^{\circ}\text{C}$                                                  | 1             | 78   | 1    | ns   |

| TYPICAL PERFORMANCE - DYNAMIC WITH           | MOSFET (             | SATE AS CONTROL TERMINAL AND                                                                                      | $V_{JGS} = 0$ | V    |      |      |

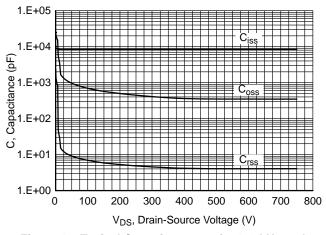

| MOSFET Input Capacitance                     | C <sub>iss</sub>     | V <sub>DS</sub> = 400 V, V <sub>GS</sub> = 0 V,                                                                   | _             | 8374 | _    | pF   |

| Output Capacitance                           | C <sub>oss</sub>     | f = 100 kHz                                                                                                       | _             | 362  | -    | 1    |

| Reverse Transfer Capacitance                 | C <sub>rss</sub>     |                                                                                                                   | _             | 4    | -    | 1    |

| Effective Output Capacitance, Energy Related | C <sub>oss(er)</sub> | V <sub>DS</sub> = 0 V to 400 V, V <sub>GS</sub> = 0 V                                                             | _             | 475  | -    | pF   |

| Effective Output Capacitance, Time Related   | C <sub>oss(tr)</sub> |                                                                                                                   | _             | 950  | -    | pF   |

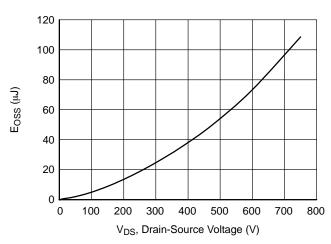

| C <sub>OSS</sub> Stored Energy               | E <sub>oss</sub>     | V <sub>DS</sub> = 400 V, V <sub>GS</sub> = 0 V                                                                    | _             | 38   | -    | μJ   |

| Total Gate Charge                            | $Q_{G}$              | $V_{DS} = 400 \text{ V}, I_{D} = 80 \text{ A}, V_{GS} = 0 \text{ V to } 15 \text{ V}$                             | _             | 164  | _    | nC   |

| Gate-drain Charge                            | $Q_{GD}$             |                                                                                                                   | _             | 24   | -    |      |

| Gate-source Charge                           | $Q_{GS}$             |                                                                                                                   | _             | 46   | -    |      |

| Turn-on Delay Time                           | t <sub>d(on)</sub>   | Notes 7 and 8                                                                                                     | _             | 30   | -    | ns   |

| Rise Time                                    | t <sub>r</sub>       | $V_{DS} = 400 \text{ V}, I_{D} = 80 \text{ A},$<br>$V_{GS} = 0 \text{ V to } +15 \text{ V}, R_{G ON} = 1 \Omega,$ | _             | 116  | -    | 1    |

| Turn-off Delay Time                          | t <sub>d(off)</sub>  | $R_{G OFF} = 10 \Omega$ , $R_{JG ON} = 0.7 \Omega$ ,                                                              | _             | 148  | -    | 1    |

| Fall Time                                    | t <sub>f</sub>       | $R_{JG\_OFF} = 10 \Omega$ , Inductive Load,<br>FWD: same device with $V_{GS} = 0 V$ ,                             | _             | 120  | -    |      |

| Turn-on Energy                               | E <sub>ON</sub>      | $R_G = 10 \Omega$ , $R_{JGON} = 0.7 \Omega$ ,                                                                     | -             | 2185 | -    | μJ   |

| Turn-off Energy                              | E <sub>OFF</sub>     | T <sub>J</sub> = 25 °C                                                                                            | _             | 1690 | -    | 1    |

| Total Switching Energy                       | E <sub>TOT</sub>     |                                                                                                                   | _             | 3875 | -    | 1    |

| Turn-on Delay Time                           | t <sub>d(on)</sub>   | Notes 7 and 8                                                                                                     | -             | 28   | -    | ns   |

| Rise Time                                    | t <sub>r</sub>       | $V_{DS} = 400 \text{ V}, I_{D} = 80 \text{ A},$<br>$V_{GS} = 0 \text{ V to } +15 \text{ V}, R_{G ON} = 1 \Omega,$ | -             | 124  | -    | 1    |

| Turn-off Delay Time                          | t <sub>d(off)</sub>  | $R_{G OFF} = 10 \Omega$ , $R_{JG ON} = 0.7 \Omega$ ,                                                              | _             | 156  | -    | 1    |

| Fall Time                                    | t <sub>f</sub>       | $R_{JG\_OFF} = 10 \Omega$ , Inductive Load,<br>FWD: same device with $V_{GS} = 0 V$ ,                             | _             | 103  | -    | 1    |

| Turn-on Energy                               | E <sub>ON</sub>      | $R_G = 10 \Omega$ , $R_{JG ON} = 0.7 \Omega$ ,                                                                    | _             | 2377 | -    | μJ   |

| Turn-off Energy                              | E <sub>OFF</sub>     | T <sub>J</sub> = 150 °C                                                                                           | _             | 1569 | -    | 1    |

| Total Switching Energy                       | E <sub>TOT</sub>     |                                                                                                                   | _             | 3946 | -    |      |

| TYPICAL PERFORMANCE - DYNAMIC WITH           | JFET GAT             | E AS CONTROL TERMINAL AND $V_{GS}$                                                                                | s = +12 V     |      |      |      |

| JFET Input Capacitance                       | $C_{Jiss}$           | $V_{DS} = 400 \text{ V}, V_{JGS} = -20 \text{ V},$                                                                | _             | 3028 | _    | pF   |

| JFET Output Capacitance                      | C <sub>Joss</sub>    | f = 100 kHz                                                                                                       | -             | 364  | -    | 1    |

| JFET Reverse Transfer Capacitance            | C <sub>Jrss</sub>    | 1                                                                                                                 | _             | 360  | -    | 1    |

| JFET Total Gate Charge                       | $Q_{JG}$             | V <sub>DS</sub> = 400 V, I <sub>D</sub> = 80 A,                                                                   | -             | 400  | -    | nC   |

| JFET Gate-drain Charge                       | $Q_{JGD}$            | $V_{JGS} = -18 \text{ V to } 0 \text{ V}$                                                                         | -             | 270  | -    | 1    |

| JFET Gate-source Charge                      | Q <sub>JGS</sub>     | 1                                                                                                                 | _             | 60   | _    | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. Limited by bondwires.

- Pulse width t<sub>p</sub> limited by T<sub>J,max</sub>.

Measured with the half-bridge mode switching test circuit in Figure 23.

Devices are driven with the ClampDRIVE method as described in the section "Recommended Gate Drive Approach: ClampDRIVE".

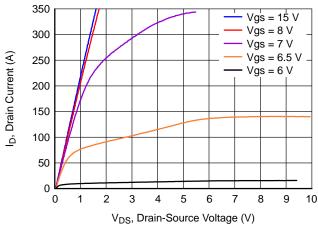

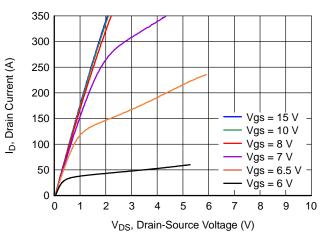

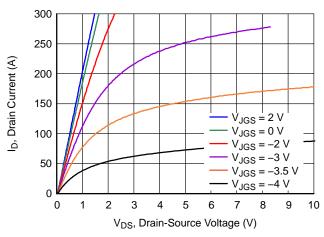

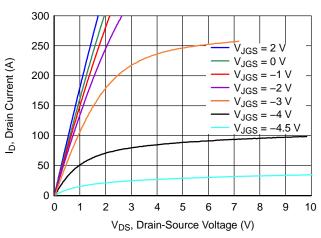

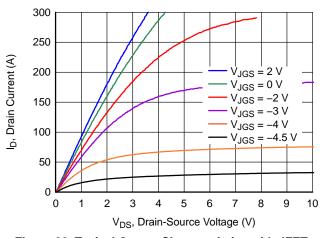

#### TYPICAL PERFORMANCE DIAGRAMS - MOSFET GATE AS CONTROL TERMINAL AND V.IGS = 0 V

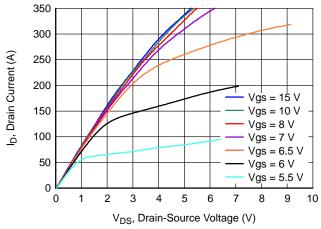

Figure 1. Typical Output Characteristics at  $T_J$  = -55 °C,  $t_p$  < 250  $\mu s$

Figure 2. Typical Output Characteristics at  $T_J$  = 25 °C,  $t_p$  < 250  $\mu s$

Figure 3. Typical Output Characteristics at  $T_J$  = 175 °C,  $t_p$  < 250  $\mu s$

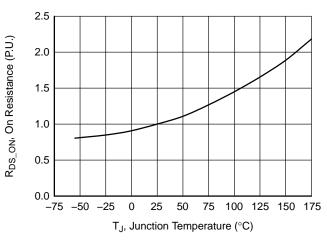

Figure 4. Normalized On-Resistance vs. Temperature at  $V_{GS}$  = 12 V and  $I_D$  = 80 A

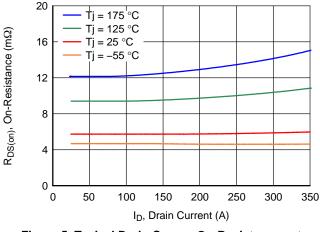

Figure 5. Typical Drain-Source On-Resistances at  $V_{GS} = 12 \text{ V}$

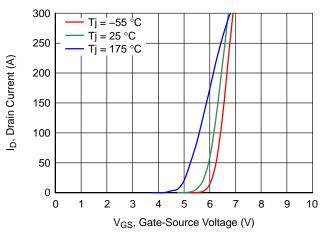

Figure 6. Typical Transfer Characteristics at V<sub>DS</sub> = 5 V

### TYPICAL PERFORMANCE DIAGRAMS – MOSFET GATE AS CONTROL TERMINAL AND $V_{JGS} = 0 V$ (CONTINUED)

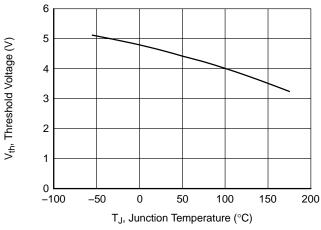

Figure 7. Threshold Voltage vs. Junction Temperature at  $V_{DS} = 5 \text{ V}$  and  $I_{D} = 10 \text{ mA}$

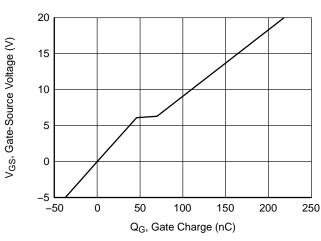

Figure 8. Typical Gate Charge at  $V_{DS}$  = 400 V and  $I_{D}$  = 80 A

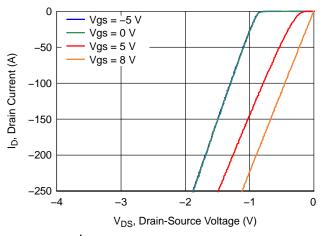

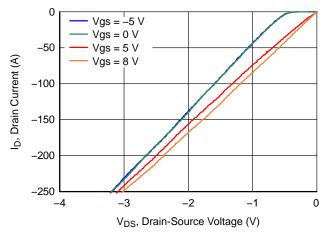

Figure 9.  $3^{rd}$  Quadrant Characteristics at  $T_J = -55$  °C

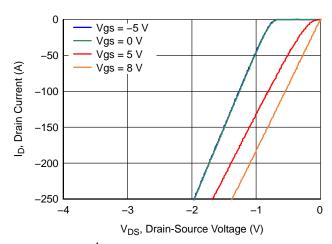

Figure 10.  $3^{rd}$  Quadrant Characteristics at  $T_J = 25$  °C

Figure 11. 3<sup>rd</sup> Quadrant Characteristics at T<sub>J</sub> = 175 °C

Figure 12. Typical Stored Energy in  $C_{OSS}$  at  $V_{GS} = 0 \text{ V}$

# TYPICAL PERFORMANCE DIAGRAMS – MOSFET GATE AS CONTROL TERMINAL AND $V_{JGS} = 0 V$ (CONTINUED)

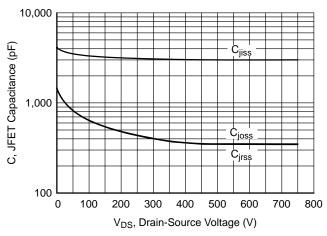

Figure 13. Typical Capacitances at f = 100 kHz and  $V_{GS}$  = 0 V

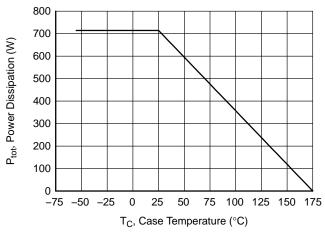

Figure 14. DC Drain Current Derating

Figure 15. Total Power Dissipation

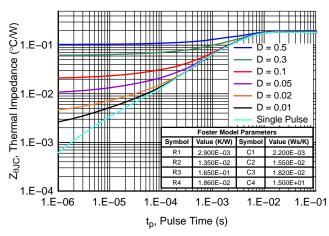

Figure 16. Maximum Transient Thermal Impedance

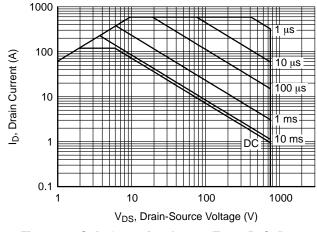

Figure 17. Safe Operation Area at  $T_C = 25$  °C, D = 0, Parameter  $t_D$

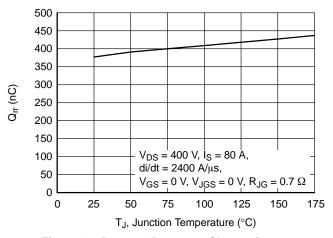

Figure 18. Reverse Recovery Charge Q<sub>rr</sub> vs. Junction Temperature

## TYPICAL PERFORMANCE DIAGRAMS – MOSFET GATE AS CONTROL TERMINAL AND $V_{JGS} = 0 V$ (CONTINUED)

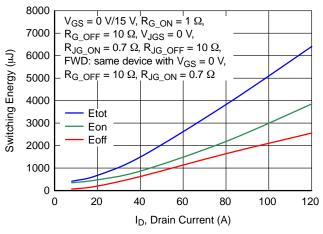

Figure 19. Clamped Inductive Switching Energy vs. Drain Current at  $V_{DS}$  = 400 V and  $T_J$  = 25 °C

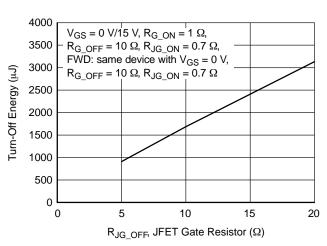

Figure 20. Clamped Inductive Turn-Off Energy vs. JFET Gate Resistor  $R_{JG\_OFF}$  at  $V_{DS}$  = 400 V,  $I_D$  = 80 A, and  $T_J$  = 25 °C

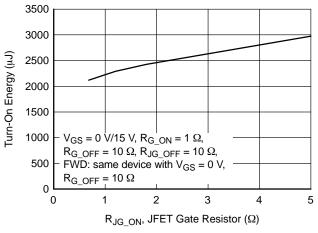

Figure 21. Clamped Inductive Turn-On Energy vs. JFET Gate Resistor  $R_{JG\_ON}$  at  $V_{DS}$  = 400 V,  $I_D$  = 80 A, and  $T_{J}$  = 25 °C

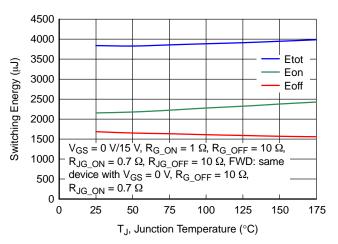

Figure 22. Clamped Inductive Switching Energy vs. Junction Temperature at  $V_{DS}$  = 400 V and  $I_{D}$  = 80 A

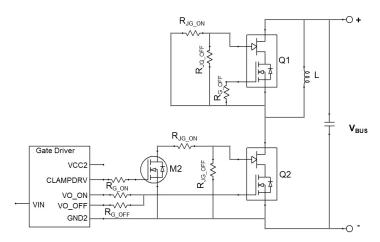

Figure 23. Schematic of the Half-bridge Mode Switching Test Circuit with ClampDRIVE Method

#### TYPICAL PERFORMANCE DIAGRAMS – JFET GATE AS CONTROL TERMINAL AND $V_{GS}$ = +12 V

Figure 24. Typical Output Characteristics with JFET Gate as Control at  $T_J$  = -55 °C,  $t_p$  < 250  $\mu s$

Figure 25. Typical Output Characteristics with JFET Gate as Control at  $T_J$  = 25 °C,  $t_p$  < 250  $\mu s$

Figure 26. Typical Output Characteristics with JFET Gate as Control at  $T_J$  = 175 °C,  $t_p$  < 250  $\mu s$

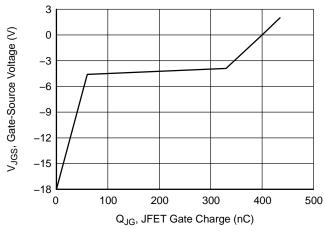

Figure 27. Typical JFET gate charge at  $V_{DS}$  = 400 V and  $I_{D}$  = 80 A

Figure 28. Typical JFET Capacitances at f = 100 kHz and  $V_{\rm JGS}$  = -20 V

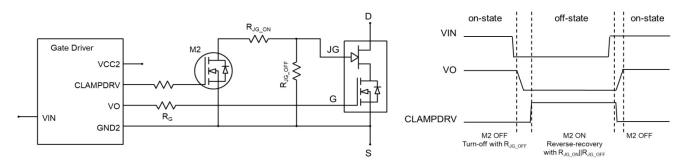

#### RECOMMENDED GATE DRIVE APPROACH: CLAMPDRIVE METHOD

Since both JFET gate and MOSFET gate are accessible. more parameters and approaches can be used to control the switching behavior of the device and make the device suitable for a wide range applications from solid state circuit breakers requiring ultra-high current turn-off capability to motor drives requiring well controlled switching speed. The recommended gate drive approach is the ClampDRIVE method, with which the desired turn-on speed, turn-off speed and reverse recovery performance can be achieved at the same time. The main idea of this method is to dynamically tune the JFET gate resistor value R<sub>JG</sub> such that, in the off-state, R<sub>IG</sub> is small enough not to cause a reverse recovery issue, and during turn-off transient, R<sub>JG</sub> is set to a higher value for the desired turn-off performance. This method can be easily implemented using a commercial off-the-shelf gate driver with miller clamp pre-driver output, as illustrated in Figure 29. VIN is the gate driver input signal. VO is the gate driver output and CLAMPDRV is the gate driver miller clamp pre-driver output. M2 is the clamp MOSFET used to control the JFET gate resistance. The MOSFET M2 is directly controlled by the CLAMPDRV signal.

In the on-state, CLAMPDRV is low which turns the MOSFET M2 off, thus, the effective JFET gate resistance is R<sub>JG\_OFF</sub>. During the turn-off transient, CLAMPDRV is kept low until the device is fully off. This means the JFET gate resistance is R<sub>JG\_OFF</sub> during the turn-off process, and R<sub>GJ\_OFF</sub> can be used to effectively control turn-off speed. After the device is fully off, CLAMPDRV is changed to high level, which turns the MOSFET M2 on.

In the off-state, CLAMPDRV is high and the clamp MOSFET M2 is in on-state. The effective JFET gate resistance is equal to the parallel combination of  $R_{JG\_OFF}$  and  $R_{JG\_ON}$ .  $R_{JG\_ON}$  can be selected small enough to prevent the reverse recovery issue. During the turn-on transient, the JFET gate current may flow from the cascode source through the body diode of the MOSFET M2 and  $R_{JG\_ON}$  into the JFET gate, so, the turn-on process is also determined by  $R_{JG\_ON}$ .

In summary, the optimum switching performance of the SiC cascode FETs can be realized with the ClampDRIVE method by selecting proper JFET gate resistors  $R_{\text{JG\_ON}}$  and  $R_{\text{JG\_OFF}}$ .

Figure 29. Circuit Schematic and Timing Diagram of the ClampDRIVE Method

#### **ORDERING INFORMATION**

| Part Number    | Marking        | Package                                                    | Shipping <sup>†</sup> |

|----------------|----------------|------------------------------------------------------------|-----------------------|

| UG4SC075006K4S | UG4SC075006K4S | TO247-4 15.90x20.96x5.03, 5.44P<br>(Pb-Free, Halogen Free) | 600 / Tube            |

**DATE 14 APR 2025**

| <b>♦</b> Ø0.635 <b>M</b> | BAM |

|--------------------------|-----|

| ØP \                     |     |

| \$                       |     |

| ØP1                      |     |

| 4 3 2                    | 1 1 |

|                          | EI  |

| CVAA   |          | millimeters |       |  |  |

|--------|----------|-------------|-------|--|--|

| SYM    | MIN      | NOM         | MAX   |  |  |

| Α      | 4.70     | 5.03        | 5.31  |  |  |

| A1     | 2.21     | 2.40        | 2.59  |  |  |

| A2     | 1.50     | 2.03        | 2.49  |  |  |

| b      | 0.99     | 1.20        | 1.40  |  |  |

| b2     | 1.65     | 2.03        | 2.39  |  |  |

| C<br>D | 0.38     | 0.60        | 0.89  |  |  |

| D      | 20.80    | 20.96       | 21.46 |  |  |

| D1     | 13.08    | _           | 1     |  |  |

| D2     | 0.51     | 1.19        | 1.35  |  |  |

| Е      | 15.49    | 15.90       | 16.26 |  |  |

| е      | 2.54 BSC |             |       |  |  |

| e1     |          | 5.08 BSC    |       |  |  |

| E1     | 13.46    | _           | ı     |  |  |

| E2     | 3.43     | 3.89        | 5.20  |  |  |

| L      | 19.81    | 20.17       | 20.32 |  |  |

| L1     | -        | _           | 4.50  |  |  |

| ØP     | 3.40     | 3.60        | 3.80  |  |  |

| ØP1    | 7.06     | 7.19        | 7.39  |  |  |

| Q      | 5.38     | 5.62        | 6.20  |  |  |

| S      | 6.17 BSC |             |       |  |  |

| θ      |          | 3°          |       |  |  |

| θ1     | 20°      |             |       |  |  |

| θ2     | 10°      |             |       |  |  |

#### NOTE:

- 1. Dimensioning and tolerancing as per ASME Y14.5 2018

- 2. Controlling dimension: millimeters

- Package Outline in compliance with JEDEC standard var. AD.

- 4. Dimensions D & E does not include mold flash.

- 5. ØP to have max draft angle of 1.7° to the top with max. hole diameter of 3.91mm.

- 5. Through Hole diameter value = End Hole diameter

- 6. PCB Through Hole pattern as per IPC-2221/IPC-2222

| DOCUMENT NUMBER: | 98AON86067F              | Electronic versions are uncontrolled except when accessed directly from the Document Repository<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |

|------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DESCRIPTION:     | TO247-4 15.90x20.96x5.03 | TO247-4 15.90x20.96x5.03, 5.44P                                                                                                                                                    |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

**DATE 14 APR 2025**

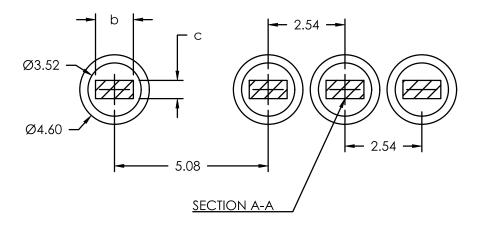

#### RECOMMENDED PCB THROUGH HOLE

NOTE: LAND PATTERN AND THROUGH HOLE DIMENSIONS SERVE ONLY AS AN INITIAL GUIDE. END-USER PCB DESIGN RULES AND TOLERANCES SHOULD ALWAYS PREVAIL.

| DOCUMENT NUMBER: | 98AON86067F              | PRAON86067F Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |

|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DESCRIPTION:     | TO247-4 15.90x20.96x5.03 | TO247-4 15.90x20.96x5.03, 5.44P                                                                                                                                                              |  |

onsemi and Onsemi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems. or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales