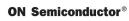

### NCP730ASNADJT1GEVB (TSOP-5) Evaluation Board – Schematic Main part

#### JP1 (ADJ/FIX):

Leave this jumper open all the times (for ADJ and FIX versions as well). Could be used (shorted) for testing of ADJ version without  $R_1$  and  $R_2$  ( $V_{OUT}$ =1.2V) only.

#### JP3 (FB-C):

Open -> ADJ/PG pin not connected to PCB edge connector (default) Short -> ADJ/PG pin connected to PCB edge connector

#### JP5 (EN-SEL):

1 – 2 -> LDO is enabled (default)

2 – 3 -> LDO is disabled

NO -> LDO is controlled by externa

NO -> LDO is controlled by externa EN signal

#### $R_1$ , $R_2$ , $C_{FF}$ :

ADJ version (pin-4 = ADJ): Use R<sub>1</sub>, R<sub>2</sub> and C<sub>FF</sub> from the table above to set V<sub>OUT</sub> voltage to desired level. For more information see datasheet. FIX non-PG version (pin-4 = NC): Remove R<sub>1</sub>, R<sub>2</sub> (and C<sub>FF</sub>) from PCB as they have no functionality, R1 and R2 just consumes current I<sub>R1R2</sub>. FIX PG version (pin-4 = PG): Use R<sub>1</sub> as a PG pull-up resistor (100 kOhm for example) to OUT, remove R<sub>2</sub> and C<sub>FF</sub>.

# ON

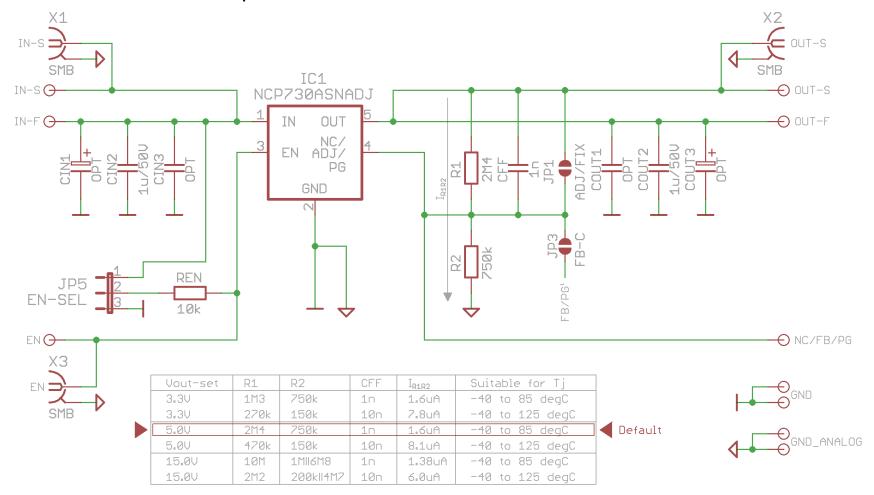

## NCP730ASNADJT1GEVB (TSOP-5) Evaluation Board – Schematic PCB edge connector (optional test I/F)

Appropriate receptacle type is SAMTEC MECF–20–01–L–DV–WT