# Onsemi

# **Enhanced, High-Efficiency Power Factor Controller**

# NCP1623

# Features

- Valley Synchronized Frequency Fold-back (VSFF):

- · CrM at Heavy Load

- DCM at Light Load by Dead Time Control

- Valley Switching in Both CrM and DCM

- On-time Modulation for High PFC in Both CrM and DCM

- Follower Boost Capability (NCP1623A Only)

- Lowered Output Voltage Regulation at Low Line

- High–Efficient Boost Stage and Downsized Inductor Design

- Skip Mode for Light Load Regulation

- Sleep Mode with Low Current Consumption (SOIC8 Only)

- Fast Line / Load Transient Control

- Dynamic Response Enhancer at Output Undershoot

- Soft OVP and Fast OVP at Output Overshoot

- Excessive Current Protection

- Over Current Protection (OCP)

- Over Stress Protection (OVS)

- Brown Out Protection

- Second Over Voltage Protection (OVP2)

- These are Pb-Free Devices

# **Typical Applications**

- USB-PD

- Flat TV

- Industrial Power Supplies

- All Off-line Appliances Requiring Power Factor Correction

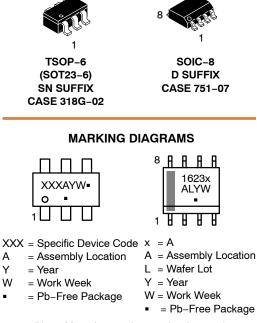

PACKAGE PICTURES

(Note: Microdot may be in either location)

Α

Υ

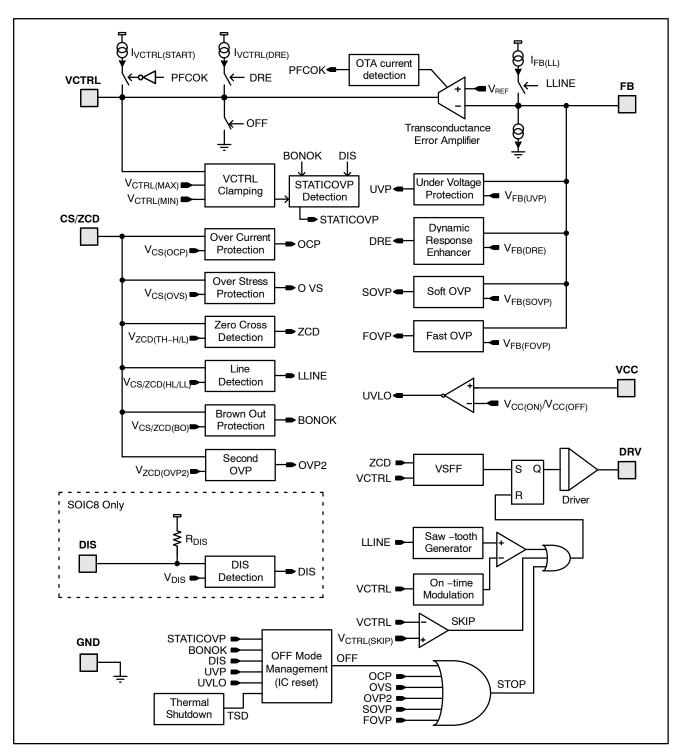

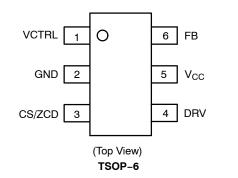

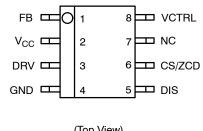

# **PIN CONNECTIONS**

# **ORDERING INFORMATION**

See detailed ordering, marking and shipping information in the package dimensions section on page 16 of this data sheet.

1

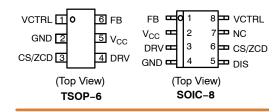

Figure 1. Application Schematic

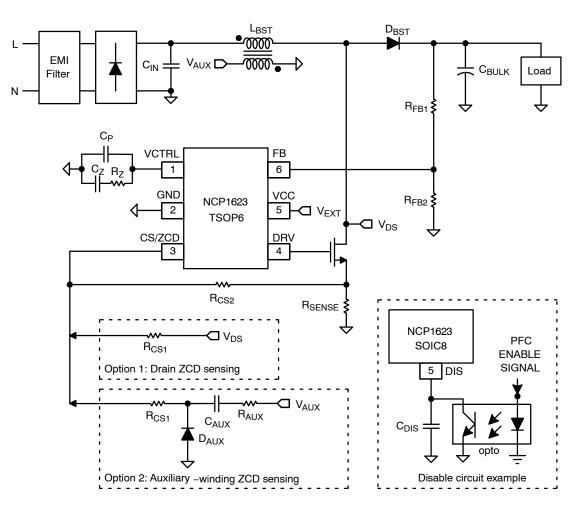

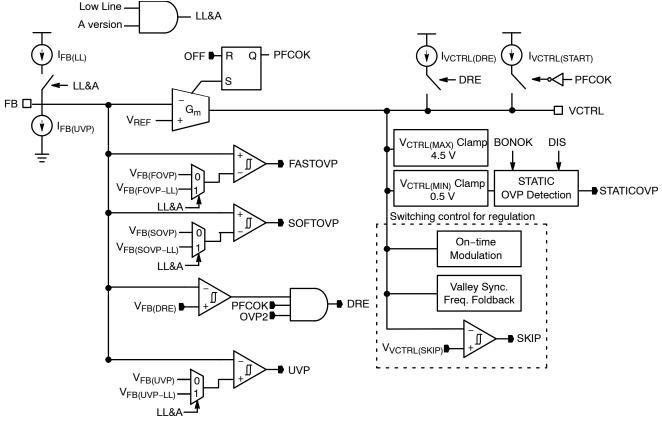

Figure 2. Simplified Block Diagram

# **PIN CONNECTIONS**

# Table 1. PIN DESCRIPTION

| Pin Number<br>TSOP-6 | Pin Number<br>SOIC-8 | Pin Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|----------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | 8                    | VCTRL           | The error amplifier output is connected to this pin. The regulation loop bandwidth is adjusted by the feedback compensation network connected between this pin and ground. When IC is reset at off mode, the NCP1623 grounds the VCTRL pin to provide a soft-start function at a subsequent startup.                                                                                                                                                                                                                                                                                                             |

| 2                    | 4                    | GND             | Power Supply Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                    | 6                    | CS/ZCD          | Based on a novel technique, this multi-functional pin is designed to monitor inductor current, ZCD signal and input/output voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4                    | 3                    | DRV             | The high-current capability of the totem pole gate drive makes it suitable to drive high gate charge power FETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5                    | 2                    | V <sub>CC</sub> | IC operating current is supplied to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                    | 1                    | FB              | The feedback pin is connected to the input of the error amplifier to monitor the PFC output voltage for regulation. Also, this pin detects the PFC output transient condition to enable DRE, SOVP and FOVP for overshoot–less and undershoot–less output regulation. A 250 nA sink current is built–in to trigger the UVP protection and disable the part if the feedback pin is accidently open. NCP1623A FB pin further sources a current (I <sub>FB(LL)</sub> of 25 µA typically) to adjust a lower output regulation level in low–line conditions for higher efficiency and downsized boost inductor design. |

|                      | 5                    | DIS             | A high level or open circuit on this pin disables the controller and reduces $I_{CC}$ bias current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | Ŭ                    | 210             | for low standby power.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                      | 7                    | NC              | No Connect (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

1. True no connect. Printed circuit board traces are allowable.

#### **Table 2. MAXIMUM RATINGS**

| Parameter                                                                         | Symbol              | Value                                      | Units |

|-----------------------------------------------------------------------------------|---------------------|--------------------------------------------|-------|

| Power Supply Input                                                                | V <sub>CC</sub>     | –0.3 to 30                                 | V     |

| CS/ZCD Pin with 5 mA of Clamp Current                                             | CS/ZCD              | –0.3 to 11.5                               | V     |

| Feedback Pin                                                                      | FB                  | –0.3 to 9                                  | V     |

| V <sub>CTRL</sub> Pin                                                             | V <sub>CTRL</sub>   | –0.3 to 9                                  | V     |

| Disable Pin, SOIC-8 Version                                                       | DIS                 | –0.3 to 9                                  | V     |

| Driver Voltage                                                                    | DRV                 | –0.3 to V <sub>DRV(HIGH)</sub><br>(Note 2) | V     |

| Maximum Junction Temperature                                                      | T <sub>J(MAX)</sub> | 150                                        | °C    |

| Storage Temperature Range                                                         | T <sub>STG</sub>    | -60 to 150                                 | °C    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>    | 260                                        | °C    |

| ESD Capability, Human Body Model (Note 4)                                         | ESD <sub>HBM</sub>  | 2                                          | kV    |

| ESD Capability, Charge Device Model (Note 4)                                      | ESD <sub>CDM</sub>  | 1                                          | kV    |

| Moisture Sensitivity Level                                                        | MSL                 | 1                                          | -     |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

V<sub>DRV(HIGH)</sub> is the DRV high clamp voltage if V<sub>CC</sub> is higher than V<sub>DRV(HIGH)</sub> V<sub>DRV</sub> is V<sub>CC</sub> otherwise.

For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

#### THERMAL CHARACTERISTICS (Note 5)

| Parameter                                                              | Symbol        | Value | Unit |

|------------------------------------------------------------------------|---------------|-------|------|

| Thermal Characteristics, TSOP-6<br>Thermal Resistance, Junction-to-Air | $R_{	hetaJA}$ | 230   | °C/W |

| Thermal Characteristics, SOIC-8<br>Thermal Resistance, Junction-to-Air | $R_{	hetaJA}$ | 153   | °C/W |

5. Mounted on a JEDEC standard 51-3 (1s0p) test board, 100 mm<sup>2</sup> copper area, 1 oz copper thickness.

#### **RECOMMENDED OPERATING RANGES**

| Parameter                            | Symbol | Min | Max | Unit |

|--------------------------------------|--------|-----|-----|------|

| Operating Junction Temperature Range |        | -40 | 125 | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### Table 3. ELECTRICAL CHARACTERISTICS

(V\_{CC} = 18.5 V and  $T_{J}$  =  $-40^{\circ}C$  to 125 $^{\circ}C,$  unless otherwise noted)

| Parameter                                                               | Symbol                       | Test Condition                             | Min          | Тур          | Max          | Unit |

|-------------------------------------------------------------------------|------------------------------|--------------------------------------------|--------------|--------------|--------------|------|

| SUPPLY CIRCUIT                                                          |                              |                                            |              |              |              |      |

| V <sub>CC</sub> Turn-On Voltage                                         | V <sub>CC(ON)</sub>          | V <sub>CC</sub> rising                     | 9.75         | 10.50        | 11.25        | V    |

| V <sub>CC</sub> Turn-Off Voltage                                        | V <sub>CC(OFF)</sub>         | V <sub>CC</sub> falling                    | 8.5          | 9.0          | 9.5          | V    |

| V <sub>CC</sub> Turn–On/Off Hysteresis                                  | V <sub>CC(HYS)</sub>         | V <sub>CC(ON) -</sub> V <sub>CC(OFF)</sub> | 1.0          | 1.5          | 2.0          | V    |

| $V_{CC}$ Reset Voltage, I <sub>CC</sub> Drops to I <sub>CC(START)</sub> | V <sub>CC(RST)</sub>         | V <sub>CC</sub> falling                    | 6            | 7            | 8            | V    |

| IC Start-Up Current                                                     | I <sub>CC(START)</sub>       | $V_{CC} = 7 V$                             | -            | 20           | 50           | μA   |

| IC Operating Current without Switching                                  | I <sub>CC1</sub>             | No switching                               | 1            | 0.5          | 1.0          | mA   |

| IC Operating Current when Switching                                     | I <sub>CC2</sub>             | $f_{SW}$ = 50 kHz, No C <sub>L</sub> load  | 1            | 2            | 3            | mA   |

| IC Sleep Mode Current, SOIC-8                                           | I <sub>CC(DIS)</sub>         | DIS pin high                               | 1            | -            | 100          | μA   |

| GATE DRIVE                                                              |                              |                                            |              |              |              |      |

| DRV Rising Time                                                         | t <sub>R</sub>               | C <sub>L</sub> = 1 nF                      | 15           | 30           | 90           | ns   |

| DRV Falling Time                                                        | t <sub>F</sub>               | C <sub>L</sub> = 1 nF                      | 10           | 20           | 50           | ns   |

| DRV Source Resistance                                                   | R <sub>OH</sub>              |                                            | -            | 10           | 20           | Ω    |

| DRV Sink Resistance                                                     | R <sub>OL</sub>              |                                            | -            | 7            | 15           | Ω    |

| DRV High Clamp Voltage                                                  | V <sub>DRV(HIGH)</sub>       | $V_{CC}$ = 30 V, $R_L$ = 33 k $\Omega$     | 10           | 12           | 14           | V    |

| ON-TIME CONTROL                                                         | -                            | -                                          |              | -            | -            | -    |

| Maximum On-Time at Low Line                                             | t <sub>ON(MAX-LL)</sub>      |                                            |              |              |              | μs   |

| Ver. A<br>Ver. C                                                        |                              |                                            | 10.8<br>13.5 | 12.5<br>16.5 | 14.2<br>19.5 |      |

| Maximum On-Time at High Line                                            | t <sub>ON(MAX-HL)</sub>      |                                            |              |              |              | μS   |

| Ver. A                                                                  |                              |                                            | 4.2          | 5.0          | 5.8          | pro  |

| Ver. C                                                                  |                              |                                            | 5.6          | 6.6          | 7.6          |      |

| On–Time Ratio of Low and High Line                                      | K <sub>TON(LL-HL)</sub>      | t <sub>ON(LL)</sub> /t <sub>ON(HL)</sub>   | 2.0          | 2.5          | 3.0          | -    |

| Minimum On Time at Low-Line                                             | t <sub>ON(MIN-LL)</sub>      |                                            | 100          | 180          | 250          | ns   |

| Minimum On Time at High-Line                                            | ton(MIN-HL)                  |                                            | 50           | 100          | 150          | ns   |

| FREQUENCY FOLDBACK AND SKIP                                             | - F                          |                                            |              |              |              | 1    |

| Dead-Time 1                                                             | t <sub>DT1</sub>             | V <sub>CTRL</sub> = 0.63 V                 | 13           | 18           | 23           | μs   |

| Dead-Time 2                                                             | t <sub>DT2</sub>             | V <sub>CTRL</sub> = 0.75 V                 | 5.5          | 8.5          | 11.5         | μs   |

| VCTRL Frequency Foldback Enter Voltage                                  | V <sub>CTRL(FF-EN)</sub>     | V <sub>CTRL</sub> falling                  | 1.87         | 2.08         | 2.29         | V    |

| VCTRL Frequency Foldback Exit Voltage                                   | V <sub>CTRL(FF-EX)</sub>     | V <sub>CTRL</sub> rising                   | 1.96         | 2.18         | 2.40         | V    |

| VCTRL Frequency Foldback Hysteresis                                     | V <sub>CTRL(FF-HYS)</sub>    |                                            | 75           | 100          | 120          | mV   |

| Minimum Frequency                                                       | f <sub>MIN</sub>             |                                            | 24           | 28           | 32           | kHz  |

| VCTRL Skip Enter Voltage                                                | V <sub>CTRL(SKIP-EN)</sub>   | V <sub>CTRL</sub> falling                  | 0.50         | 0.56         | 0.62         | V    |

| VCTRL Skip Exit Voltage                                                 | V <sub>CTRL</sub> (SKIP-EX)  | V <sub>CTRL</sub> rising                   | 0.55         | 0.62         | 0.68         | V    |

| VCTRL Skip Hysteresis                                                   | V <sub>CTRL</sub> (SKIP-HYS) |                                            | 40           | 70           | 100          | mV   |

| FEEDBACK REGULATION                                                     |                              | 1                                          |              | r            | 1            | 1    |

| FB Regulation Reference Voltage                                         | V <sub>REF</sub>             |                                            | 2.44         | 2.50         | 2.56         | V    |

| FB Source Current at Low Line, Ver. A                                   | I <sub>FB(LL)</sub>          |                                            | 23.75        | 25.00        | 26.25        | μA   |

| Error Amplifier Source Current                                          | I <sub>EA(SOURCE)</sub>      | V <sub>FB</sub> = 2.4 V                    | 15           | 20           | 25           | μA   |

| Error Amplifier Sink Current                                            | I <sub>EA(SINK)</sub>        | V <sub>FB</sub> = 2.6 V                    | -25          | -20          | -15          | μA   |

| Error Amplifier Gain                                                    | G <sub>EA</sub>              |                                            | 110          | 200          | 290          | μS   |

| VCTRL Maximum Clamping Voltage                                          | V <sub>CTRL(MAX)</sub>       | V <sub>FB</sub> = 2 V                      | 4.0          | 4.5          | 5.0          | V    |

| VCTRL Minimum Clamping Voltage                                          | V <sub>CTRL(MIN)</sub>       | V <sub>FB</sub> = 3 V                      | 0.3          | 0.5          | 0.8          | V    |

| VCTRL Startup Source Current                                            | IVCTRL(START)                |                                            | 90           | 120          | 150          | μA   |

|                                                                         |                              |                                            |              |              |              |      |

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

(V\_{CC} = 18.5 V and  $T_{J}$  =  $-40^{\circ}C$  to 125°C, unless otherwise noted)

| Parameter                                                     | Symbol                       | Test Condition                                 | Min        | Тур        | Max        | Unit |

|---------------------------------------------------------------|------------------------------|------------------------------------------------|------------|------------|------------|------|

| FEEDBACK DYNAMIC RESPONSE ENHANCER (                          | DRE)                         |                                                |            |            | 1          |      |

| FB DRE Enter Voltage Ratio                                    | K <sub>FB(DRE-EN)</sub>      | V <sub>FB(DRE-EN)</sub> / V <sub>REF</sub>     | 94.5       | 95.5       | 96.5       | %    |

| FB DRE Exit Voltage Ratio                                     | K <sub>FB(DRE-EX)</sub>      | V <sub>FB(DRE-EX)</sub> / V <sub>REF</sub>     | 96.5       | 97.5       | 98.5       | %    |

| FB DRE Hysteresis Ratio                                       | K <sub>FB(DRE-HYS)</sub>     |                                                | 1          | 2          | 3          | %    |

| VCTRL DRE Source Current                                      | IVCTRL(DRE)                  |                                                | 180        | 215        | 250        | μA   |

| FEEDBACK SOFT AND FAST OVER VOLTAGE P                         |                              | AND FOVP)                                      |            |            |            |      |

| FB SOVP Enter Voltage Ratio                                   | K <sub>FB(SOVP-EN)</sub>     | V <sub>FB(SOVP-EN)</sub> / V <sub>REF</sub>    | 103.5      | 105.0      | 106.5      | %    |

| FB SOVP Exit Voltage Ratio                                    | K <sub>FB(SOVP-EX)</sub>     | V <sub>FB(SOVP-EX)</sub> / V <sub>REF</sub>    | 101.5      | 103.0      | 104.5      | %    |

| FB SOVP Hysteresis Ratio                                      | K <sub>FB(SOVP-HYS)</sub>    |                                                | 1          | 2          | 3          | %    |

| FB SOVP Enter Voltage Ratio at Low Line, Ver. A               | K <sub>FB(SOVP-EN-LL)</sub>  | V <sub>FB(SOVP-EN-LL)</sub> / V <sub>REF</sub> | 108.5      | 110.0      | 111.5      | %    |

| FB SOVP Exit Voltage Ratio at Low Line, Ver. A                | K <sub>FB(SOVP-EX-LL)</sub>  | V <sub>FB(SOVP-EX-LL)</sub> / V <sub>REF</sub> | 106.5      | 108.0      | 109.5      | %    |

| FB SOVP Hysteresis Ratio at Low Line, Ver. A                  | K <sub>FB(SOVP-HYS-LL)</sub> |                                                | 1          | 2          | 3          | %    |

| FB FOVP Enter Voltage Ratio                                   | K <sub>FB(FOVP-EN)</sub>     | V <sub>FB(FOVP-EN)</sub> / V <sub>REF</sub>    | 105.5      | 107.0      | 108.5      | %    |

| FB FOVP Exit Voltage Ratio                                    | K <sub>FB(FOVP-EX)</sub>     | V <sub>FB(FOVP-EX)</sub> / V <sub>REF</sub>    | 103.5      | 105.0      | 106.5      | %    |

| FB FOVP Hysteresis Ratio                                      | K <sub>FB(FOVP-HYS)</sub>    |                                                | 1          | 2          | 3          | %    |

| FB FOVP Enter Voltage Ratio at Low Line, Ver. A               | K <sub>FB(FOVP-EN-LL)</sub>  | V <sub>FB(FOVP-EN-LL)</sub> / V <sub>REF</sub> | 112.5      | 114.0      | 115.5      | %    |

| FB FOVP Exit Voltage Ratio at Low Line, Ver. A                | K <sub>FB(FOVP-EX-LL)</sub>  | V <sub>FB(SOVP-EX-LL)</sub> / V <sub>REF</sub> | 110.5      | 112.0      | 113.5      | %    |

| FB FOVP Hysteresis Ratio at Low Line, Ver. A                  | K <sub>FB(FOVP-HYS-LL)</sub> |                                                | 1          | 2          | 3          | %    |

| FEEDBACK UNDER VOLTAGE PROTECTION (U)                         |                              |                                                |            |            |            |      |

| FB UVP Enter Voltage                                          | V <sub>FB(UVP-EN)</sub>      | V <sub>FB</sub> falling                        | 240        | 300        | 360        | mV   |

| FB UVP Exit Voltage                                           | V <sub>FB(UVP-EX)</sub>      | V <sub>FB</sub> rising                         | 470        | 530        | 590        | mV   |

| FB UVP Enter Voltage at Low Line, Ver. A                      | V <sub>FB(UVP-EN-LL)</sub>   | V <sub>FB</sub> falling                        | 1.1        | 1.2        | 1.3        | V    |

| FB UVP Exit Voltage at Low Line, Ver. A                       | V <sub>FB(UVP-EX-LL)</sub>   | V <sub>FB</sub> rising                         | 1.2        | 1.3        | 1.4        | V    |

| FB UVP Sink Current                                           | I <sub>FB(UVP)</sub>         |                                                | 50         | 250        | 450        | nA   |

| CURRENT SENSE AND ZERO CURRENT DETEC                          |                              | •                                              |            |            |            |      |

| CS Over-Current Protection (OCP) Voltage                      | V <sub>CS(OCP)</sub>         |                                                | 450        | 500        | 550        | mV   |

| CS OCP Leading Edge Blanking Time                             | t <sub>OCP(LEB)</sub>        |                                                | 320        | 400        | 460        | ns   |

| CS OCP to DRV Off Delay Time                                  | t <sub>OCP(DLY)</sub>        | $dV_{CS/ZCD}$ / $dt = 10 V/\mu s$              | -          | 40         | 200        | ns   |

| CS Over-Stress Protection (OVS) Voltage                       | V <sub>CS(OVS)</sub>         |                                                | 675        | 750        | 825        | mV   |

| CS OVS Leading Edge Blanking Time                             | t <sub>OVS(LEB)</sub>        |                                                | 50         | 200        | 350        | ns   |

| CS OVS Watch Dog Timer                                        | tovs(WDG)                    |                                                | 700        | 800        | 900        | μs   |

| ZCD High Threshold Voltage                                    | V <sub>ZCD(TH-H)</sub>       | V <sub>CS/ZCD</sub> rising                     | 5          | 40         | 75         | mV   |

| ZCD Low Threshold Voltage                                     | V <sub>ZCD(TH-L)</sub>       | V <sub>CS/ZCD</sub> falling                    | -75        | -40        | -5         | mV   |

| ZCD Low Threshold Hysteresis                                  | V <sub>ZCD(TH-HYS)</sub>     |                                                | 50         | 80         | 110        | mV   |

| ZCD Blanking Time                                             | t <sub>ZCD(BLANK)</sub>      |                                                | 500        | 600        | 700        | ns   |

| ZCD to DRV On Delay Time<br>Ver. A<br>Ver. C                  | <sup>t</sup> ZCD(DLY)        |                                                | 170<br>250 | 220<br>310 | 270<br>370 | ns   |

| ZCD Watch Dog Timer                                           | t <sub>ZCD(WDG)</sub>        |                                                | 80         | 200        | 320        | μs   |

| CS/ZCD Source Current<br>for Short-to-Ground Pin Detection    | IZCD(GND)                    |                                                | 40         | 50         | 60         | μΑ   |

| CS/ZCD Threshold Voltage<br>for Short-to-Ground Pin Detection | V <sub>ZCD(GND)</sub>        |                                                | 200        | 240        | 280        | mV   |

| CS/ZCD Clamp Voltage                                          | V <sub>CS/ZCD(CL)</sub>      | I <sub>CS/ZCD</sub> = 5 mA                     | 8.0        | 9.5        | 11.5       | V    |

#### Table 3. ELECTRICAL CHARACTERISTICS (continued)

(V<sub>CC</sub> = 18.5 V and T<sub>J</sub> =  $-40^{\circ}$ C to 125°C, unless otherwise noted)

| Parameter                                                  | Symbol                      | Test Condition              | Min      | Тур      | Max      | Unit     |

|------------------------------------------------------------|-----------------------------|-----------------------------|----------|----------|----------|----------|

| LINE RANGE DETECTION                                       | · · · · ·                   |                             | •        | •        | •        |          |

| CS/ZCD High Line Detection Voltage                         | V <sub>CS/ZCD(HL)</sub>     | $V_{CS/ZCD}$ rising         | 1.65     | 1.80     | 1.95     | V        |

| ZCD Low Line Detection Voltage                             | V <sub>CS/ZCD(LL)</sub>     | V <sub>CS/ZCD</sub> falling | 1.45     | 1.55     | 1.65     | V        |

| ZCD Line Detection Hysteresis                              | V <sub>CS/ZCD(LD-HYS)</sub> |                             | 200      | 300      | 400      | mV       |

| CS/ZCD Line Detection Blanking Time                        | t <sub>LD(BLANK)</sub>      | V <sub>CS/ZCD</sub> falling | 20       | 25       | 30       | ms       |

| CS/ZCD Line Detection Watch Dog Timer, Ver. A              | t <sub>LD(WDG)</sub>        |                             | 430      | 500      | 560      | ms       |

| BROWN-OUT (BO) - DISABLED IN A AND C VEI                   | RSION                       |                             |          |          |          |          |

| CS/ZCD BO Enter Voltage                                    | V <sub>CS/ZCD(BO-EN)</sub>  | V <sub>CS/ZCD</sub> falling | 730      | 790      | 850      | mV       |

| CS/ZCD BO Exit Voltage                                     | V <sub>CS/ZCD(BO-EX)</sub>  | $V_{CS/ZCD}$ rising         | 860      | 940      | 1020     | mV       |

| CS/ZCD BO Hysteresis                                       | V <sub>CS/ZCD(BO-HYS)</sub> |                             | 130      | 145      | 160      | mV       |

| CS/ZCD BO Blanking Time                                    | t <sub>BO(BLANK)</sub>      |                             | 35       | 50       | 65       | ms       |

| VCTRL BO Sink Current                                      | I <sub>VCTRL(BO)</sub>      |                             | 20       | 30       | 40       | μA       |

| SECOND OVER VOLTAGE PROTECTION (OVP2)                      | - C VERSION ONLY            |                             |          |          |          |          |

| ZCD OVP2 Enter Voltage                                     | V <sub>ZCD(OVP2-EN)</sub>   | $V_{CS/ZCD}$ rising         | 3.61     | 3.77     | 3.93     | V        |

| ZCD OVP2 Blanking Time                                     | t <sub>OVP2(BLANK)</sub>    |                             | 0.8      | 1.0      | 1.2      | μs       |

| ZCD OVP2 Reset Time to Disable DRV                         | t <sub>OVP2(RST)</sub>      |                             | 55       | 75       | 95       | ms       |

| THERMAL SHUTDOWN                                           |                             |                             |          |          |          |          |

| Thermal Shutdown Threshold (Note 6)                        | T <sub>LIMT</sub>           |                             | 150      | -        | -        | °C       |

| Thermal Shutdown Hysteresis (Note 6)                       | H <sub>TEMP</sub>           |                             | -        | 50       | -        | °C       |

| DISABLE MODE - SOIC8 ONLY                                  |                             |                             |          |          |          |          |

| DIS Sleep Mode Enter Voltage                               | V <sub>DIS(EN)</sub>        | V <sub>DIS</sub> rising     | 1.5      | 1.8      | 2.1      | V        |

| DIS Sleep Mode Exit Voltage                                | V <sub>DIS(EX)</sub>        | V <sub>DIS</sub> falling    | 0.8      | 1.1      | 1.4      | V        |

| DIS Sleep Mode Hysteresis                                  | V <sub>DIS(HYS)</sub>       |                             | 0.5      | 0.7      | 0.9      | V        |

| DIS Sleep Mode Detection Blanking Time<br>Ver. A<br>Ver. C | t <sub>DIS(BLANK)</sub>     |                             | 16<br>16 | 25<br>25 | 34<br>34 | ms<br>μs |

| DIS Pull – Up Resistance                                   | R <sub>DIS</sub>            |                             | 370      | 530      | 690      | kΩ       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 6. Values based on design and/or characterization.

# DEFINITIONS

#### General

Extremely compact, the NCP1623 is designed to optimize the efficiency of your PFC stage throughout the load range. It also incorporates protection features for a rugged operation. More generally, NCP1623 is ideal in systems where cost–effectiveness, reliability, high power factor and efficiency ratios are key requirements:

# Low Start–Up Current and Large V<sub>CC</sub> Range

The A and C versions ( $V_{CC(ON)}$  of 10.5 V typically) are preferred in applications where the controller is fed by an external power source (from an auxiliary power supply or from a downstream converter). Its maximum start-up level (11.25 V,  $V_{CC(ON)}$ ) eases circuit powering from traditional 12–V rails. After start-up, the high  $V_{CC}$  maximum rating allows a large  $V_{CC}$  operation range from 9.5 V up to 30 V, thus easing the circuit feeding.

# **Output Stage Totem Pole**

NCP1623 incorporates a -0.5 A / +0.8 A gate driver to efficiently drive most power FETs typically used in 70 to 300 W power supplies. As V<sub>CC</sub> can be as high as 30 V, an internal clamp limits the DRV pin to 14 V max to be compatible with typical gate–source max ratings of industry MOSFETs.

# Valley Synchronized Frequency Fold-Back

NCP1623 classically operates in critical conduction mode (CrM) until the power drops below a threshold level where the PFC stage enters the discontinuous conduction mode (DCM) with a dead time prolonged as the load further decays (frequency foldback). This novel technique also provides stable valley turn-on in both CrM and DCM for a maximized efficiency. In addition, the minimum frequency clamp (33 kHz typically) prevents audible frequencies and the on-time is modulated to ensure near-unity power factor in both CrM and DCM operations.

#### Compactness

The NCP1623 features the CS/ZCD multifunctional pin based on a novel technique for an enhanced control and a large bunch of protections in a small TSOP6 (or SOIC8) package with few external components. In addition, the NCP1623A forces a lower output regulation level in low-line condition to raise the PFC stage efficiency and reduce its size. This 2-level Follower Boost technique best fits for applications where the downstream converter (like a flyback power supply) can withstand input voltage variations in a cost-effective and efficient manner.

# Feedback Transient Control (SOVP, FOVP and DRE)

Since PFC stages exhibit low loop bandwidth, abrupt changes in the load or input voltage (e.g. at start-up) may cause excessive over or under voltages. Firstly, the soft and fast over voltage protections (SOVP and FOVP) interrupt the power delivery when the output voltage is excessive. At output voltage undershoot, the circuit dramatically speeds up the regulation loop when the output voltage goes below the low detect threshold (dynamic response enhancer – DRE).

# Over Current and Over Stress Protection (OCP, OVS)

The circuit senses the FET current and turns it off if the sensed current exceeds the OCP limit. In addition, the circuit pauses FET switching for 800  $\mu$ s when the current reaches OVS threshold as result of an inductor saturation or a short of the bypass diode.

#### Brown–Out Protection (BO, Disabled in A and C Version)

The circuit detects too low ac line conditions and stops operation thus protecting the PFC stage from excessive stress.

# Second Over–Voltage Protection (OVP2, C Version Only)

CS/ZCD multi-functional pin is used to detect excessive output voltage levels and prevent a destructive output voltage runaway if the feedback network happens to be wrong. (incorrect resistors value, aging effects...)

#### **Under-Voltage Protection (UVP)**

This circuit turns off FET switching when the FB pin voltage drops close to 0 V at low ac line or a failure in the feedback network (e.g., accidental short to ground / open failure of the FB pin).

# Thermal Shutdown (TSD)

An internal thermal circuitry disables the gate drive when the junction temperature exceeds  $150^{\circ}$ C. The circuit resumes operation once the temperature drops below approximately  $100^{\circ}$ C ( $50^{\circ}$ C hysteresis).

# Disable Function (SOIC8 Package Only)

In case of SOIC8 package option, DIS pin is provided to disable most of the internal blocks in NCP1623 to minimize  $V_{CC}$  supply current.

#### APPLICATIONS INFORMATION

#### FREQUENCY CONTROL

#### Valley Synchronized Frequency Foldback (VSFF)

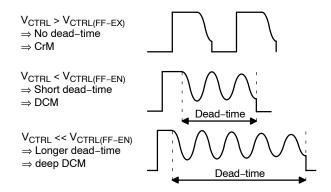

The NCP1623 implements the Valley Synchronized Frequency Fold–back (VSFF) which consists of operating the PFC stage in critical conduction mode (CrM) until the power drops below a threshold level. As the power is further reduced under the threshold, the PFC stage enters the discontinuous conduction mode (DCM) with a dead time which gets longer.

Practically, the output of the regulation error amplifier ( $V_{CTRL}$ ) is used to select the operation mode and to adjust the dead-time duration. More specifically, the circuit enters the DCM mode when  $V_{CTRL}$  drops below a frequency foldback enter voltage,  $V_{CTRL(FF-EN)}$  and remains in this mode until  $V_{CTRL}$  exceeds a frequency foldback exit voltage,  $V_{CTRL(FF-EX)}$  with 100 mV hysteresis,  $V_{CTRL(FF-HYS)}$ . Figure 3 summarizes this functioning.

Figure 3. Drain Voltage in VSFF

$V_{CTRL}$  determines the turn-on time (t<sub>ON</sub>) in the voltage mode where  $V_{CTRL} - V_{CTRL(MIN)}$  (0.5 V) sets t<sub>ON</sub> proportionally and  $V_{CTRL}$  control range is up to  $V_{CTRL(MAX)}$  (4.5 V). Therefore, the input power is determined by:

$$P_{IN} = \frac{V_{IN.RMS}^{2}}{2L} \cdot \frac{t_{ON(MAX)} \cdot \left(V_{CTRL} - V_{CTRL(MIN)}\right)}{V_{CTRL(MAX)} - V_{CTRL(MIN)}}$$

(eq. 1)

V<sub>CTRL(FF-EN)</sub> is typically 2.08 V for the A and C version so that the input power level entering frequency foldback is:

$$\mathsf{P}_{\mathsf{IN}} = \frac{\mathsf{V}^2_{\mathsf{IN.RMS}}}{2\mathsf{L}} \cdot \mathsf{t}_{\mathsf{ON}(\mathsf{MAX})} \cdot 0.395 \tag{eq. 2}$$

To further improve efficiency, the MOSFET turn on is delayed until its drain-source voltage is at its valley. Practically, the circuit forces the dead-time dictated by the  $V_{CTRL}$  level. However, the NCP1623 does not immediately generate a DRV pulse if it detects that the FET drain-source

voltage is not minimum. In other words, the dead-time is extended until the next valley is detected.

Whether the frequency is reduced by VSFF, an on-time modulation in NCP1623 adjusts the DRV turn-on time to compensate the dead-times in DCM for unity power factor. Also, the minimum frequency clamp prevents the system from operating at audible frequencies.

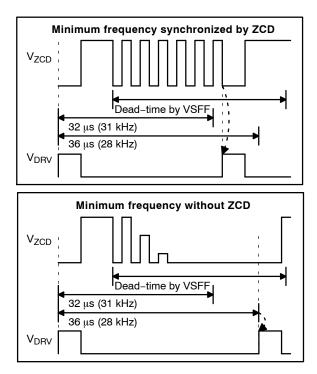

#### Minimum Switching Frequency

The DCM dead-time is an increasing function of  $V_{CTRL(FF-EN)} - V_{CTRL}$ . This frequency foldback function reduces the light-load switching frequency to optimize the efficiency. However, an internal minimum frequency logic limits the switching frequency above the audible frequency.

Figure 4. Minimum Switching Frequency

As shown by Figure 4, 32  $\mu$ s switching period is counted and the DRV output will then turn on when the circuit detects the next valley. However, if no valley can be detected, DRV is forced high in 36  $\mu$ s switching period whatever the drain–source voltage is. As a result, the minimum frequency is typically between 31 kHz (32  $\mu$ s switching period) if a valley is immediately detected and 28 kHz (36  $\mu$ s switching period) if no valley can be detected.

Note that if the circuit cannot detect ZCD signal at all during DRV turn-off time, the circuit does not generate any DRV pulses until the 200  $\mu$ s ZCD watchdog time has elapsed.

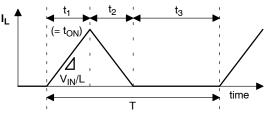

#### **ON-TIME MODULATION**

When the FET is on, the inductor current of a CrM/DCM PFC boost stage starts from zero and ramps up with the slope of  $V_{IN}/L$  where L is the inductor value as shown in Figure 5. At the end of the on time (t<sub>1</sub> or t<sub>ON</sub>), the inductor starts to demagnetize. The inductor current ramps down until it reaches zero. The duration of this phase is t<sub>2</sub>. At that moment, a new switching cycle starts if the circuit operates in CrM. When in DCM, there is a dead time t<sub>3</sub> that lasts until the next clock is generated.

Figure 5. Inductor Current in DCM

One can show that in both CrM and DCM, the input current is given by:

$$I_{IN} = V_{IN} \frac{t_1 \cdot (t_1 + t_2)}{2 \cdot L \cdot T} = V_{IN} \frac{t_{ON} \cdot (t_1 + t_2)}{2 \cdot L \cdot T}$$

(eq. 3)

where  $T = t_1 + t_2 + t_3$ , switching period (t<sub>3</sub> being 0 in CrM).

In the light of the eq. 3, we note that  $I_{IN}$  is proportional to  $V_{IN}$  if  $t_1 \cdot (t_1 + t_2)/T$  is a constant. In the voltage mode without On–time Modulation, DRV turn–on time ( $t_{ON}$  or  $t_1$  in eq. 3) is set by:

$$t_{ON} = t_{ON(MAX)} \cdot \frac{V_{CTRL} - V_{CTRL(MIN)}}{V_{CTRL(MAX)} - V_{CTRL(MIN)}}$$

(eq. 4)

where  $t_{ON(MAX)}$  is maximum turn-on time and  $t_{ON(MAX)}$  at low-line is 2.5 times longer than high-line condition by 2-level line feedforward.

In order to keep  $t_1 \cdot (t_1 + t_2)/T$  constant, NCP1623 further modulate  $t_{ON}$  by the factor of T/( $t_1 + t_2$ ) information detected from previous switching:

$$t_{ON} = t_{ON(MAX)} \cdot \frac{V_{CTRL} - V_{CTRL(MIN)}}{V_{CTRL(MAX)} - V_{CTRL(MIN)}} \cdot \frac{T}{t_1 + t_2}$$

(eq. 5)

$(t_1 + t_2)/T$  in eq. 3 is removed by  $T/(t_1 + t_2)$  in the modulated  $t_{ON}$  eq. 5 so that the input current is finally given by:

$$I_{IN} = V_{IN} \frac{t_{ON(MAX)}}{2 \cdot L} \cdot \frac{V_{CTRL} - V_{CTRL(MIN)}}{V_{CTRL(MAX)} - V_{CTRL(MIN)}}$$

(eq. 6)

Therefore, NCP1623 controls both CrM and DCM with no degradation in power factor and no discontinuity in the power delivery.

#### FEEDBACK REGULATION

#### OTA and VCTRL Function

A trans-conductance error amplifier (OTA) with access to the inverting input and output is provided as shown in Figure 6. It features a FB reference voltage for output voltage regulation of 2.5 V, a typical trans-conductance gain of 200  $\mu$ S and a maximum capability of about  $\pm 20 \,\mu$ A OTA output current. The VCTRL pin is the output of the error amplifier for external loop compensation. Typically, a type-2 network is applied between the VCTRL pin and ground to set the regulation bandwidth below about 20 Hz. VCTRL basically controls turn-on time, dead time in VSFF, skip mode and STATICOVP:

- Turn-on time is proportional to V<sub>CTRL</sub> V<sub>CTRL(MIN)</sub> as in eq. 5.

- Dead time (ZCD to DRV turn-on delay time) is lengthened as V<sub>CTRL</sub> is lowered from V<sub>CTRL(FF-EN)</sub>.

- V<sub>CTRL</sub> is pulled down by 30 μA I<sub>VCTRL(BO)</sub> when brown-out or DIS sleep mode entering process starts. If V<sub>CTRL</sub> is lower than 0.5 V V<sub>CTRL(MIN)</sub> in the 30 μA current enable condition, STATICOVP is triggered and NCP1623 enters OFF mode.

#### Follower Boost – A version only

At low-line, a Follower Boost reduces the output voltage to optimize the PFC stage efficiency and significantly shrink its size and cost. In particular, the boost inductance and the MOSFET losses can be dramatically reduced. Since, the output voltage must remain higher than the line voltage, the output voltage is lowered in low line only while it remains regulated to the default nominal level generally set to 400 V in high-line conditions. Practically, the NCP1623A controls this 2-level follower boost operation through the feedback pin which sources the current  $I_{FB(LL)}$  (25 µA typically) in low line detection condition.  $I_{FB(LL)}$  offsets the feedback voltage as follows:

$$V_{FB} = \frac{R_{FB2}}{R_{FB1} + R_{FB2}} \cdot V_{OUT} + R_{FB1} \parallel R_{FB2} \cdot I_{FB(LL)}$$

(eq. 7)

where  $R_{FB1}$  and  $R_{FB2}$  are the upper and the lower resistors of the feedback bridge as shown in Figure 1.

Finally, the output regulation voltage level is:

$$V_{OUT} = \frac{R_{FB1} + R_{FB2}}{R_{FB2}} \cdot V_{REF} - R_{FB1} \cdot I_{FB(LL)}$$

(eq. 8)

Thus, the low-line regulation level depends on the feedback upper resistance,  $R_{FB1}$ . As an example, if  $_{RFB1}$  is 6 M $\Omega$  and  $R_{FB2}$  is 37.7 k $\Omega$ :

$$\begin{split} V_{\text{OUT(HL)}} &= \frac{6\ \text{M}\,+\,37.7\ \text{k}}{37.7\ \text{k}} \cdot 2.5 \,=\,400\ \text{V} \\ V_{\text{OUT(LL)}} &=\,400\ \text{V}\,-\,6\ \text{M}\,\cdot\,25\ \mu \,=\,250\ \text{V} \end{split}$$

Figure 6. Feedback Regulation and Transient Control

### FEEDBACK TRANSIENT CONTROL

#### Soft Start

At startup,  $I_{VCTRL(START)}$  sources an external compensation capacitor properly for soft start. When FB voltage reaches close to  $V_{REF}$ , the sourcing current of the OTA is reduced to 0 A where PFCOK signal is set to high level and  $I_{VCTRL(START)}$  is turned off.

#### Dynamic Response Enhancer (DRE)

The NCP1623 embeds a "Dynamic Response Enhancer" (DRE) that deals with the under–shoots of the output voltage at abrupt increases of the load current. An internal comparator monitors the FB pin and when this voltage is lower than 95.5%  $V_{REF}$ , a 200  $\mu$ A I<sub>VCTRL(DRE)</sub> is sourced to speed up the charge of the compensation network as shown in Figure 6. Effectively this appears as a 10x increase in the loop gain. DRE is disabled during the start–up sequence until the PFC stage has stabilized and PFCOK is high. DRE is also disabled when the OVP2 (Second Over Voltage Protection) is triggered.

#### Soft / Fast Over Voltage Protection (SOVP, FOVP)

In case of output over–shoots, soft OVP is firstly triggered by comparing FB voltage and a soft OVP threshold,  $V_{FB(SOVP)}$  as in Figure 6. Once the soft OVP is triggered, the turn–on time is gradually decreased in 4 to 5 switching periods to smoothly reduce powering. If FB voltage is even higher than a fast OVP threshold,  $V_{FB(FOVP)}$ , switching is immediately disabled. At low–line condition with A version enabling follower boost, soft and fast OVP thresholds,  $V_{FB(SOVP-LL)}$  and  $V_{FB(FOVP-LL)}$ , are increased.

Based on these control methods at output voltage transient condition, NCP1623 triggers DRE, soft OVP and fast OVP at below levels:

- DRE:

- $V_{FB(DRE)} = 95.5\%/97.5\% \text{ x } V_{REF}$

- Soft OVP:

- $V_{FB(SOVP)} = 105\%/103\% \text{ x } V_{REF}$

- $V_{FB(SOVP-LL)} = 110\%/108\% \text{ x } V_{REF}$

- Fast OVP:

- $V_{FB(FOVP)} = 107\%/105\% \text{ x } V_{REF}$

- $V_{FB(FOVP-LL)} = 114\%/112\% \text{ x } V_{REF}$

where  $V_{FB(SOVP-LL)}$  and  $V_{FB(FOVP-LL)}$  are set at low-line with Follower Boost enabled in A version.

#### Under Voltage Protection (UVP)

If the FB pin is open,  $V_{FB}$  is pulled down lower than an UVP threshold voltage ( $V_{FB(UVP)}$ ) and DRV switching stops. The output voltage of the PFC stage is scaled down by a resistor divider and monitored by the OTA inverting input (FB pin voltage). FB sink current,  $I_{FB(UVP)}$  for UVP, is minimized less than 450 nA to allow the use of a high impedance feedback resistor network.

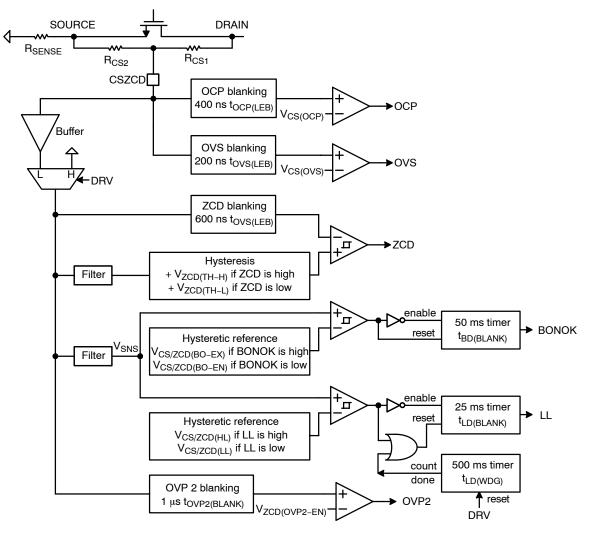

#### CURRENT SENSE AND ZERO CROSS DETECTION

The NCP1623 uses CS/ZCD pin to detect a switching FET conduction current and drain voltage. The FET current is detected by a current sense resistor ( $R_{SENSE}$ ) inserted between the FET source and ground. The drain voltage is monitored by directly sensing  $V_{DS}$  using a resistive bridge or by monitoring a reflected  $V_{DS}$ , typically obtained from an

auxiliary winding as shown in Figure 1. The direct  $V_{DS}$  sensing is a simple solution with no auxiliary winding and the auxiliary winding based ZCD sensing is generally preferred to improve CS/ZCD noise immunity with lower standby power.

As illustrated in Figure 7, the CS/ZCD pin provides the input signal for the following functions:

Figure 7. CS/ZCD Internal Circuit Block

#### Excessive Current Protection (OCP and OVS)

The NCP1623 turns off the FET when  $V_{CS/ZCD}$  reaches the over-current threshold (500 mV  $V_{CS(OCP)}$ ) after OCP blanking time (400 ns  $t_{OCP(LEB)}$ ) from DRV on. In addition, if  $V_{CS/ZCD}$  further exceeds the overstress level (750 mV  $V_{CS(OVS)}$ ) after OVS blanking time (200 ns  $t_{OVS(LEB)}$ ) from DRV on, FET is turned off for OVS watch dog time (800 µs  $t_{OVS(WDG)}$ ).

#### Zero Current Detection (ZCD)

The NCP1623 turns on DRV at the valley of the drain-source voltage to minimize switching loss and noise. After ZCD blanking time (600 ns  $t_{ZCD(BLANK)}$ ),  $V_{CS/ZCD}$  is

compared with the sum of the filtered  $V_{CS/ZCD}$  and  $V_{ZCD(TH-H/L)}$  hysteresis to generate ZCD signal.

When no signal is received that triggers the ZCD comparator during the off-time, an internal 200  $\mu$ s (t<sub>ZCD(WDG)</sub>) watchdog timer initiates the next drive pulse. At the end of this delay, CS/ZCD pin sources 50  $\mu$ A I<sub>ZCD(GND)</sub> and compare V<sub>CS/ZCD</sub> with 240 mV V<sub>ZCD(GND)</sub> to detect a possible grounding of this pin and prevent a subsequent fault operation.

#### Line Sensing

A low pass filtered CS/ZCD voltage,  $V_{SNS}$ , is an image of the input voltage. The blanking time (25 ms,  $t_{LD(BLANK)}$ ) for

low-line (LL) detection is set longer than a half-line cycle but not that long to quickly detects an abrupt line transient from high to low. When the line changes from low to high and  $V_{SNS}$  is over  $V_{CS/ZCD(HL)}$ , high line mode is immediately entered. When high-line is detected (that is, when signal "LL" of Figure 7 is low), the loop gain,  $t_{ON} / (V_{CTRL} - V_{CTRL(MIN)}) \mu s/V$ , is divided by about 2.5 to ensure a 2-level feedforward.

The FB pin of the A version sources the current  $I_{FB(LL)}$  when low-line is detected. This is used to reduce the regulation level at low-line and hence provide the follower boost capability. Also, when follower boost is enabled, the line sensing result is forced to high-line if DRV switching is disabled for a line detection watch dog time (500 ms  $t_{LD(WDG)}$ ).

#### Brown Out

The NCP1623 uses  $V_{SNS}$  (filtered  $V_{CS/ZCD}$ ) for the input voltage detection same as the line sensing. By default, when powered, the circuit is in a fault state ("BONOK" high) and BONOK is set to low when  $V_{SNS}$  exceeds  $V_{CS/ZCD(BO-EX)}$ .

As shown in Figure 7, when  $V_{SNS}$  is lower than the brown-out enter voltage ( $V_{CS/ZCD(BO-EN)}$ ) for BO blanking time (50 ms t<sub>BO(BLANK)</sub>), BONOK signal is high and the drive is not immediately disabled. Instead, a 30 µA current source ( $I_{VCTRL(BO)}$ ) gradually reduces  $V_{CTRL}$ . As a result, the circuit keeps generating DRV pulses until the STATICOVP trips (that is when  $V_{CTRL}$  reaches the minimum clamp level, 0.5 V  $V_{CTRL(MIN)}$  as shown in Figure 6). This method relieves the risk of input voltage bouncing the fault line detection caused by EMI filter oscillation from an abrupt DRV stop.

#### Second Over Voltage Protection (OVP2)

During the FET turn-off time, the CS/ZCD pin signal is proportional to the output voltage and can hence unveil overshoots. This provides an additional protection to protect the PFC stage in case of a failure of the resistive network at FB pin. When an OVP2 fault is detected after OVP2 blanking time ( $t_{OVP2(BLANK)}$ ) from DRV off, the circuit stops generating DRV pulses for 75 ms  $t_{OVP2(RST)}$  typically. OVP2 is disabled for 60 ms at startup and for 10 ms at the end of 75 ms  $t_{OVP2(RST)}$  time to prevent an abnormal OVP2 detection at the transient condition, but the output voltage could be over the OVP2 level if the bulk voltage is abruptly charged during these OVP2 disabling times.

#### THERMAL SHUT-DOWN

An internal thermal sensing circuitry disables the circuit gate drive and keeps the power switch off when the junction temperature exceeds 150°C. The NCP1623 remains off until the junction temperature drops below about 100°C (50°C hysteresis). The temperature shutdown remains active as long as  $V_{CC}$  is higher than  $V_{CC(RST)}$ . The reset action forces the TSD threshold to 150°C so that any cold start–up will be done with the proper TSD level.

#### OFF MODE

The NCP1623 turns off DRV switching and enters the OFF mode when one of the following faults is detected:

- UVLO when V<sub>CC</sub> < V<sub>CC(OFF)</sub>.

- TSD when  $T_J > 150^{\circ}C$ .

- UVP when  $V_{FB} < V_{FB(UVP)}$ .

- STATICOVP triggered by BO or DIS sleep mode.

In OFF mode,  $V_{CTRL}$  is grounded and PFCOK signal is reset to low. Also, the major part of the circuit sleeps except for UVLO, TSD, UVP, BO and DIS blocks.

In case of OFF mode triggered by DIS function, the circuit consumption is further minimized to  $I_{CC(DIS)}$  (100  $\mu$ A max).

#### **DISABLE FUNCTION**

The NCP1623 operation is disabled when the DIS pin voltage exceeds the DIS sleep mode enter voltage ( $V_{DIS(EN)}$ , 2.1 V maximum) for DIS blanking time ( $t_{DIS(BLANK)}$ ). Practically, this occurs if the DIS pin is let floating since an internal 530 k $\Omega$  resistor pulls up the pin. In this case, the V<sub>CC</sub> current consumption is reduced to I<sub>CC(DIS)</sub> (100  $\mu$ A maximum) and the PFC stage stops operating.

Similar to power reducing sequence in brown-out, the drive is not immediately disabled and 30  $\mu$ A current source gradually reduces V<sub>CTRL</sub> until the STATICOVP function trips in Figure 6. The DIS sleep mode is maintained until the DIS pin is externally pulled down below the DIS sleep mode exit voltage (V<sub>DIS(EX)</sub>, 0.8 V minimum).

If the NCP1623 enters the OFF mode by other fault detections (not by STATICOVP in DIS process), the DIS pin is grounded through a 530 k $\Omega$  resistor.

#### **OUTPUT DRIVE**

The output stage in DRV pin contains a totem pole optimized to minimize cross-conduction currents, making the NCP1623 compatible with high-frequency operation. Its high current capability (-500 mA / +800 mA) allows it to effectively drive high gate charge power FET. In the large  $V_{CC}$  range (up to 30 V), the DRV pin turn-on voltage is clamped up to 14 V.

#### FAILURE DETECTION

When manufacturing a power supply, components can be accidently shorted or improperly soldered. Such failures can also happen to occur later on because of the components fatigue or excessive stress. The false open/short circuits are generally required not to cause fire, smoke nor big noise. The NCP1623 integrates functions which help meet this requirement.

#### FB Pin Open Protection

A 250 nA sink current ( $I_{FB(UVP)}$ ) pulls down the FB pin voltage if it is floating so that the UVP protection trips. This current source is small (450 nA maximum) so that its impact

on the bulk voltage regulation level remains negligible with typical feedback resistor dividers.

#### GND Pin Open Protection

If the GND pin is not connected, GND pin voltage is floating and could be higher than PFC stage power ground level. If NCP1623 detects a reversed voltage between GND and CS/ZCD pin for 800  $\mu$ s, IC is reset with no switching operation.

#### CZ/ZCD Pin Short Protection

If ZCD signal is not detected at all at CS/ZCD pin short condition, ZCD watchdog timer doesn't allow DRV turn–on for 200  $\mu$ s t<sub>ZCD(WDG)</sub>. After the watchdog time, the

NCP1623 checks the CS/ZCD pin short condition where the operation stops if  $V_{CS/ZCD}$  is lower than 275 mV ( $V_{ZCD(GND)}$  maximum) when shortly sourcing 40  $\mu$ A ( $I_{ZCD(GND)}$  minimum). Therefore, CS/ZCD pin external impedance should be higher than 7 k $\Omega$ .

### Bypass Diode Short Protection

A bypass diode is generally placed between the input and output high–voltage rails to divert this inrush current. When the bypass diode is short–circuited, the inductor current enters deep CCM as the discharging inductor current slope is very gentle. In such case, the overstress protection (OVS) can trip and stop the drive switching for 800 µs t<sub>OVS(WDG)</sub>.

#### Table 4. ORDERING INFORMATION

| Device        | Marking | Package          | Shipping <sup>†</sup> |

|---------------|---------|------------------|-----------------------|

| NCP1623ASNT1G | UPD     | TSOP-6 (Pb-Free) | 3000 / Tape & Reel    |

| NCP1623ADR2G  | 1623A   | SOIC-8 (Pb-Free) | 2500 / Tape & Reel    |

| NCP1623CDR2G  | 1623C   |                  |                       |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### Table 5. CIRCUITS SPECIFIC OPTIONS

|                                               | NCP1623 Versions |                  |  |

|-----------------------------------------------|------------------|------------------|--|

| Options                                       | А                | С                |  |

| Package                                       | TSOP6 / SOIC8    | SOIC8            |  |

| Follower Boost                                | Yes              | No               |  |

| Maximum On-time at LL/HL                      | 12.5 μs / 5.0 μs | 16.6 μs / 6.6 μs |  |

| DIS Mode Detection Blanking Time (SOIC8 Only) | 25 ms            | 25 μs            |  |

| OVP2 Protection                               | No               | Yes              |  |

| Brown–Out Protection                          | No               | No               |  |

#### TSOP-6 3.00x1.50x0.90, 0.95P **CASE 318G ISSUE W** DATE 26 FEB 2024 NDTES D DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2018. 1. CONTROLLING DIMENSION: MILLIMETERS. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH. MINIMUM 2. З. 6 5 4 LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. MATERIAL. DIMENSIONS D AND E1 DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15 PER SIDE. DIMENSIONS D AND E1 ARE DETERMINED AT DATUM H. PIN 1 INDICATOR MUST BE LOCATED IN THE INDICATED ZONE Ē1 NOTE 5 1 3 MILLIMETERS H DIM MIN NΠΜ MAX e -2 GAUGE PLANE 0.90 1.00 1.10 А TOP VIEW A1 0.01 0.06 0.10 0.80 0.90 1.00 Α2 -A2 0.25 0.38 0.50 b SEATING PLANE Μ Ċ 0.10 0.18 0.26 С 0.05 C 3.00 DETAIL Z D 2.90 3.10 SCALE 3:1 F 2.50 A1-2.75 3.00 SIDE VIEW PLANE Ε1 1.30 1.50 1.70 0.85 0.95 1.05 е 0.20 0.40 DETAIL Z L 0.60 L2 0.25 BSC М 0° 10° 6X --0.60 END VIEW 6X -0.95 3.20 1 -0.95 PITCH RECOMMENDED MOUNTING FOOTPRINT

\*For additional information on our Pb-Free strategy and soldering details, please download th e EN Semiconductor Soldering and Mounting Techniques Reference manual, SELDERRM/D.

DURSEM

| DOCUMENT NUMBER:                                                                     | 98ASB14888C                                                                                                | Electronic versions are uncontrolled except when accessed directly from the Document Repo<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                                   |                           |  |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| DESCRIPTION:                                                                         | TSOP-6 3.00x1.50x0.90, 0.95P                                                                               |                                                                                                                                                                                                                                                                                                                | PAGE 1 OF 2               |  |  |

| the right to make changes without furth<br>purpose, nor does <b>onsemi</b> assume ar | er notice to any products herein. <b>onsemi</b> make<br>ny liability arising out of the application or use | LLC dba <b>onsemi</b> or its subsidiaries in the United States and/or other cour<br>es no warranty, representation or guarantee regarding the suitability of its pr<br>of any product or circuit, and specifically disclaims any and all liability, inc<br>e under its patent rights nor the rights of others. | oducts for any particular |  |  |

# onsemí.

#### TSOP-6 3.00x1.50x0.90, 0.95P CASE 318G ISSUE W

DATE 26 FEB 2024

#### GENERIC MARKING DIAGRAM\*

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:<br>PIN 1. DRAIN<br>2. DRAIN<br>3. GATE<br>4. SOURCE<br>5. DRAIN<br>6. DRAIN              | STYLE 2:<br>PIN 1. EMITTER 2<br>2. BASE 1<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 2<br>6. COLLECTOR 2    | STYLE 3:<br>PIN 1. ENABLE<br>2. N/C<br>3. R BOOST<br>4. Vz<br>5. V in<br>6. V out                            | STYLE 4:<br>PIN 1. N/C<br>2. V in<br>3. NOT USED<br>4. GROUND<br>5. ENABLE<br>6. LOAD           | STYLE 5:<br>PIN 1. EMITTER 2<br>2. BASE 2<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 1<br>6. COLLECTOR 2 | STYLE 6:<br>PIN 1. COLLECTOR<br>2. COLLECTOR<br>3. BASE<br>4. EMITTER<br>5. COLLECTOR<br>6. COLLECTOR |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| STYLE 7:<br>PIN 1. COLLECTOR<br>2. COLLECTOR<br>3. BASE<br>4. N/C<br>5. COLLECTOR<br>6. EMITTER   | STYLE 8:<br>PIN 1. Vbus<br>2. D(in)<br>3. D(in)+<br>4. D(out)+<br>5. D(out)<br>6. GND                         | STYLE 9:<br>PIN 1. LOW VOLTAGE GATE<br>2. DRAIN<br>3. SOURCE<br>4. DRAIN<br>5. DRAIN<br>6. HIGH VOLTAGE GATE | 2. GND<br>3. D(OUT)–<br>4. D(IN)–<br>5. VBUS                                                    | STYLE 11:<br>PIN 1. SOURCE 1<br>2. DRAIN 2<br>3. DRAIN 2<br>4. SOURCE 2<br>5. GATE 1<br>6. DRAIN 1/GATE 2  | STYLE 12:<br>PIN 1. I/O<br>2. GROUND<br>3. I/O<br>4. I/O<br>5. VCC<br>6. I/O                          |

| STYLE 13:<br>PIN 1. GATE 1<br>2. SOURCE 2<br>3. GATE 2<br>4. DRAIN 2<br>5. SOURCE 1<br>6. DRAIN 1 | STYLE 14:<br>PIN 1. ANODE<br>2. SOURCE<br>3. GATE<br>4. CATHODE/DRAIN<br>5. CATHODE/DRAIN<br>6. CATHODE/DRAIN |                                                                                                              | LE 16:<br>N 1. ANODE/CATHODE<br>2. BASE<br>3. EMITTER<br>4. COLLECTOR<br>5. ANODE<br>6. CATHODE | STYLE 17:<br>PIN 1. EMITTER<br>2. BASE<br>3. ANODE/CATHODE<br>4. ANODE<br>5. CATHODE<br>6. COLLECTOR       |                                                                                                       |

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB14888C                               | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DESCRIPTION: TSOP-6 3.00x1.50x0.90, 0.95P |                                                                                                                                                                               | PAGE 2 OF 2 |  |  |

| onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                                           |                                                                                                                                                                               |             |  |  |

# onsemí

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# STYLES ON PAGE 2

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 1 OF 2 |  |

| onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |             |                                                                                                                                                                                     |             |  |

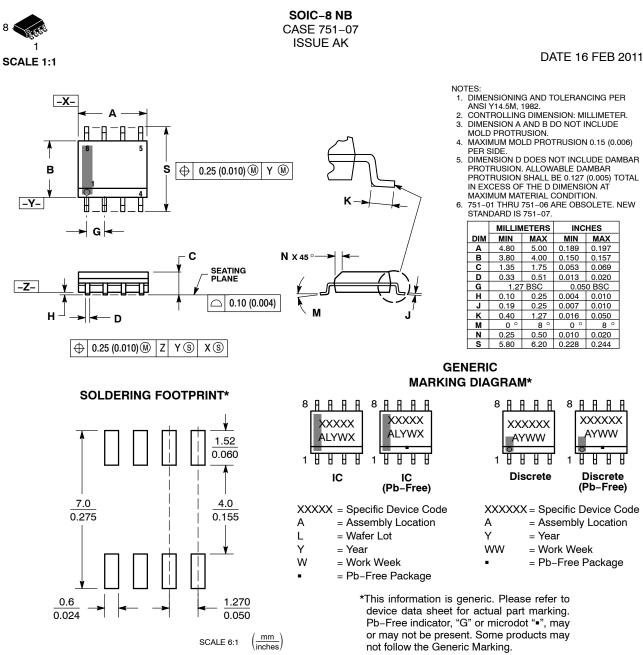

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

STYLE 1: PIN 1. EMITTER COLLECTOR 2. 3. COLLECTOR 4. EMITTER 5. EMITTER BASE 6. 7 BASE EMITTER 8. STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN DRAIN 4. GATE 5. 6. GATE SOURCE 7. 8. SOURCE STYLE 9: PIN 1. EMITTER, COMMON COLLECTOR, DIE #1 COLLECTOR, DIE #2 2. З. EMITTER, COMMON 4. 5. EMITTER, COMMON 6 BASE. DIE #2 BASE, DIE #1 7. 8. EMITTER, COMMON STYLE 13: PIN 1. N.C. 2. SOURCE 3 GATE 4. 5. DRAIN 6. DRAIN DRAIN 7. DRAIN 8. STYLE 17: PIN 1. VCC 2. V2OUT V10UT З. TXE 4. 5. RXE 6. VFF 7. GND 8. ACC STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3 CATHODE 3 CATHODE 4 4. 5. CATHODE 5 6. COMMON ANODE COMMON ANODE 7. 8. CATHODE 6 STYLE 25: PIN 1. VIN 2 N/C REXT З. 4. GND 5. IOUT IOUT 6. IOUT 7. 8. IOUT STYLE 29: BASE, DIE #1 PIN 1. 2 EMITTER, #1 BASE, #2 З. EMITTER, #2 4. 5 COLLECTOR, #2 COLLECTOR, #2 6.

STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 COLLECTOR, #2 3. 4 COLLECTOR, #2 BASE, #2 5. EMITTER, #2 6. 7 BASE #1 EMITTER, #1 8. STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN SOURCE 4. SOURCE 5. 6. GATE GATE 7. 8. SOURCE STYLE 10: GROUND PIN 1. BIAS 1 OUTPUT 2. З. GROUND 4. 5. GROUND 6 BIAS 2 INPUT 7. 8. GROUND STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3 P-SOURCE P-GATE 4. P-DRAIN 5 6. P-DRAIN N-DRAIN 7. N-DRAIN 8. STYLE 18: PIN 1. ANODE ANODE 2. SOURCE 3. GATE 4. 5. DRAIN 6 DRAIN CATHODE 7. CATHODE 8. STYLE 22 PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3 COMMON CATHODE/VCC 4. I/O LINE 3 COMMON ANODE/GND 5. 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND STYLE 26: PIN 1. GND 2 dv/dt З. ENABLE 4. ILIMIT 5. SOURCE SOURCE 6. SOURCE 7. 8. VCC STYLE 30: DRAIN 1 PIN 1. DRAIN 1 2 GATE 2 З. SOURCE 2 4 SOURCE 1/DRAIN 2 SOURCE 1/DRAIN 2 5.

6.

7.

8 GATE 1

SOURCE 1/DRAIN 2

STYLE 3: PIN 1. DRAIN, DIE #1 DRAIN, #1 2. DRAIN, #2 З. DRAIN, #2 4. GATE, #2 5. SOURCE, #2 6. 7 GATE #1 8. SOURCE, #1 STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS THIRD STAGE SOURCE GROUND З. 4. 5. DRAIN 6. GATE 3 SECOND STAGE Vd 7. FIRST STAGE Vd 8. STYLE 11: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. З. GATE 2 4. 5. DRAIN 2 6. DRAIN 2 DRAIN 1 7. 8. DRAIN 1 STYLE 15: PIN 1. ANODE 1 2. ANODE 1 ANODE 1 3 ANODE 1 4. 5. CATHODE, COMMON CATHODE, COMMON CATHODE, COMMON 6. 7. CATHODE, COMMON 8. STYLE 19: PIN 1. SOURCE 1 GATE 1 SOURCE 2 2. 3. GATE 2 4. 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 MIRROR 1 8. STYLE 23: PIN 1. LINE 1 IN COMMON ANODE/GND COMMON ANODE/GND 2. 3 LINE 2 IN 4. LINE 2 OUT 5. COMMON ANODE/GND COMMON ANODE/GND 6. 7. 8. LINE 1 OUT STYLE 27: PIN 1. ILIMIT OVI O 2 UVLO З. 4. INPUT+ 5. 6. SOURCE SOURCE SOURCE 7. 8 DRAIN

#### DATE 16 FEB 2011

STYLE 4: PIN 1. 2. ANODE ANODE ANODE З. 4. ANODE ANODE 5. 6. ANODE 7 ANODE COMMON CATHODE 8. STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 З. BASE #2 COLLECTOR, #2 4. COLLECTOR, #2 5. 6. EMITTER, #2 EMITTER, #1 7. 8. COLLECTOR, #1 STYLE 12: PIN 1. SOURCE SOURCE 2. 3. GATE 4. 5. DRAIN 6 DRAIN DRAIN 7. 8. DRAIN STYLE 16 EMITTER, DIE #1 PIN 1. 2. BASE, DIE #1 EMITTER, DIE #2 3 BASE, DIE #2 4. 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 COLLECTOR, DIE #1 7. COLLECTOR, DIE #1 8. STYLE 20: PIN 1. SOURCE (N) GATE (N) SOURCE (P) 2. 3. 4. GATE (P) 5. DRAIN 6. DRAIN DRAIN 7. 8. DRAIN STYLE 24: PIN 1. BASE EMITTER 2. 3 COLLECTOR/ANODE COLLECTOR/ANODE 4. 5. CATHODE 6. CATHODE COLLECTOR/ANODE 7. 8. COLLECTOR/ANODE STYLE 28: PIN 1. SW\_TO\_GND 2. DASIC OFF DASIC\_SW\_DET З. 4. GND 5. 6. V MON VBULK 7. VBULK 8 VIN