Is Now Part of

**ON Semiconductor®**

To learn more about ON Semiconductor, please visit our website at

[www.onsemi.com](http://www.onsemi.com)

---

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# AN-4176

## 1 kV SenseFET 統合型パワースイッチ

### 1. 概要

産業用ドライバやエネルギーメーターなど、3相 AC 電源から給電される産業機器では、アナログおよびデジタル回路用に低電力の DC 安定化電源を提供できる補助電源段を必要とする場合がよくあります。

この電源段には以下のような特別の仕様が要求されます。

- 広範な AC 入力電圧範囲 : 45 V<sub>AC</sub> ~ 460 V<sub>AC</sub>

- 高いラインサージへの耐性を備えた堅牢なシステム

- 電磁接触試験からの保護

- 電源オフ後の長いホールドアップ時間を確保する大出力容量

このような電源の設計には、高電圧 MOSFET が総コストを押し上げてしまうため、困難を伴います。

FSL4110LR は、産業機器における最適化された補助電源段を設計できるようにするために、アバランシェ耐量の高い 1 kV SenseFET と PWM コントローラーで構成されています。

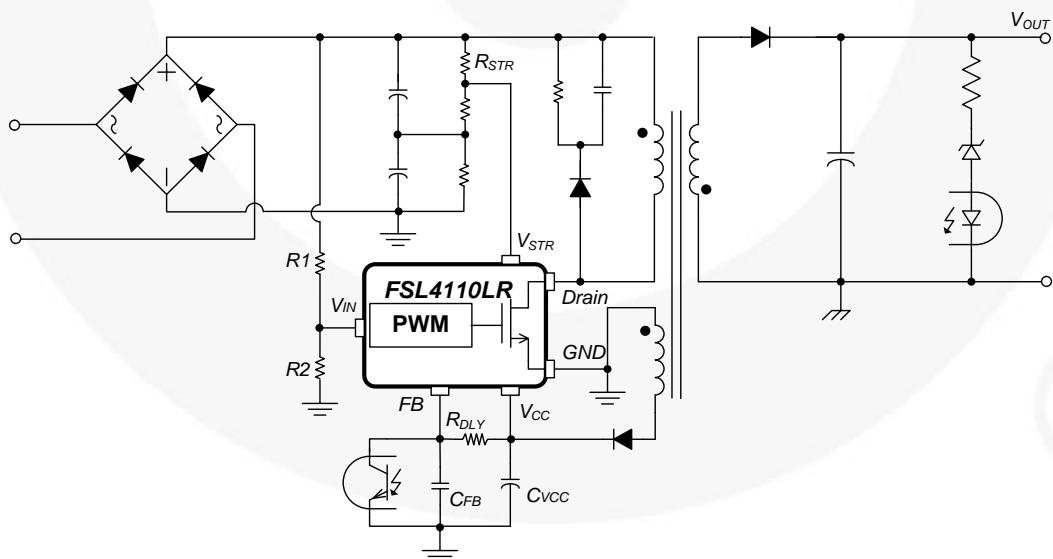

### 2. 概要

FSL4110LR は、統合型パルス幅変調 (PWM) コントローラーと、アバランシェ耐量の高い 1000 V SenseFET で構成され、高入力電圧のオフラインスイッチングモード電源 (SMPS) を最小限の外部部品点数で実現できるよう特別に設計されています。V<sub>CC</sub> は、補助バイアス巻線無しで、内蔵の高電圧電源レギュレーターを通して供給可能です。

PWM コントローラー部は固定周波数発振器、低電圧誤動作防止回路 (UVLO)、リーディングエッジブランкиング (LEB)、最適化されたゲートドライバー、内部ソフトスタート、ループ補償用の温度補償精密電流源、および豊富な保護回路が含まれています。

ディスクリート MOSFET と PWM コントローラによるソリューションに比べ、FSL4110LR は、総コスト、部品点数、PCB サイズ、重量を減らせると同時に、効率性、生産性、システム信頼性を向上させます。このデバイスは、費用効果の高いフライバックコンバーター設計の基本プラットフォームを提供します。

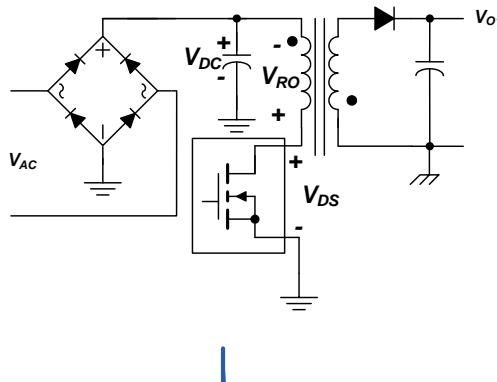

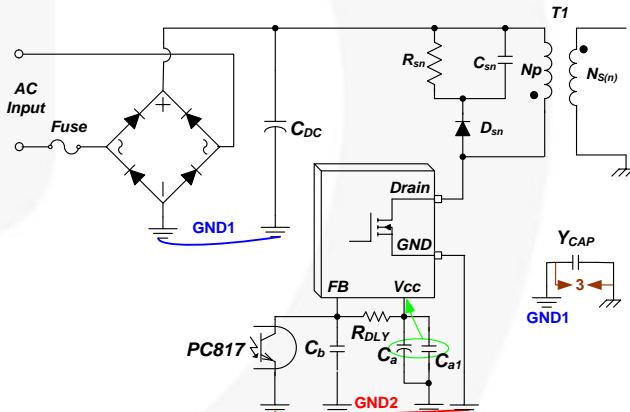

図 1. 代表的用途

### 3. 機能概要

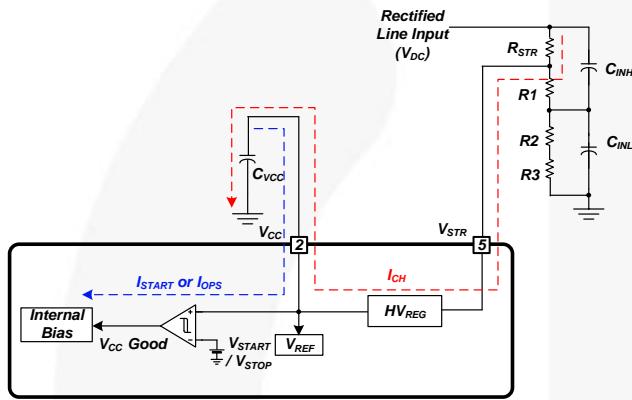

#### 3.1. スタートアップと高電圧レギュレータ

スタートアップ時に、高電圧レギュレーター ( $HV_{REG}$ ) の内部高電圧電流源 ( $I_{CH}$ ) は、図 2 に示すように内部バイアス電流 ( $I_{START}$ ) を供給し、 $V_{CC}$  ピンに接続された外部コンデンサ ( $C_{VCC}$ ) を充電します。この内部高電圧電流源は、 $V_{CC}$  が  $V_{START}$  (12 V) に達するまで動作します。定常動作中、内部高電圧レギュレーター ( $HV_{REG}$ ) は  $V_{CC}$  を 10 V に維持し、すべての内部回路に動作スイッチング電流 ( $I_{OPS}$ ) を供給します。従って、FSL4110LR には外部バイアス回路は不要です。外部バイアスから供給される  $V_{CC}$  が 10 V を超えると、高電圧レギュレーターは停止します。しかし、セルフバイアスの場合は電力消費が増加します。

図 2. スタートアップと  $HV_{REG}$  ブロック

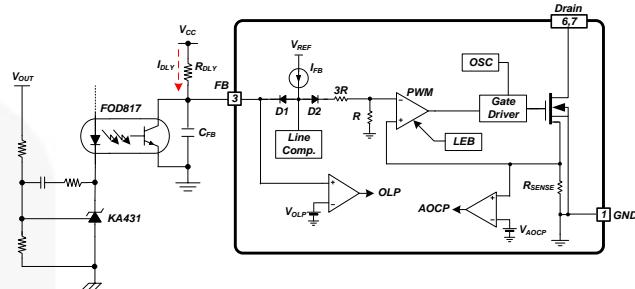

#### 3.2. フィードバック制御

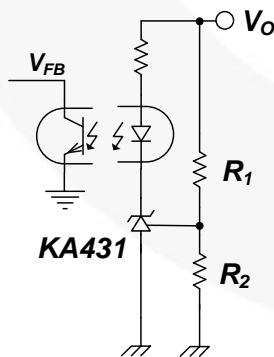

FSL4110LR は、電流モード制御スキームを採用しています。オプトカプラ（例えば FOD817 など）と 2 次側シャントレギュレータ（例えば KA431 など）は、一般的にフィードバック回路構成のために使用されます。フィードバック電圧を  $R_{SENSE}$  抵抗にかかる電圧と比較することで、スイッチングデューティサイクルの制御が可能になります。入力電圧が増加、あるいは出力負荷が減少すると、シャントレギュレーターの基準入力電圧は上がります。この電圧がシャントレギュレーターの内部基準電圧を超えると、オプトカプラーのオプトダイオードの電流が増加し、フィードバック電圧を引き下げ、ドレン電流を減少させます。

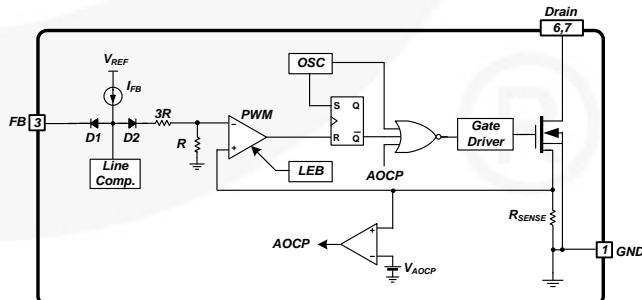

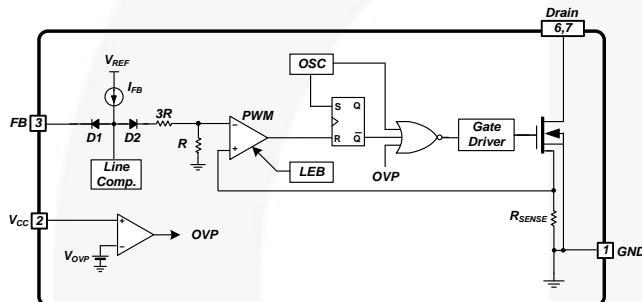

##### 3.2.1. パルス毎の電流制限

電流モード制御が採用されているため、図 3 にあるように SenseFET を流れるピーク電流は PWM コンパレータの反転入力によって制限されます。100  $\mu$ A の電流源 ( $I_{FB}$ ) が内部抵抗 ( $3R + R = 24 \text{ k}\Omega$ ) のみを通って流れていると仮定すると、ダイオード D2 のカソード電圧は約 2.4 V です。フィードバック電圧 ( $V_{FB}$ ) が 2.4 V を超えると D1 はブロックされるため、D2 のカソード最大電

圧はこの電圧にクランプされます。したがって、SenseFET のピーク電流値は次のように制限されます。

$$\frac{2.4V}{R_{SENSE}} \times \text{Sense Ratio} \quad (1)$$

図 3. パルス幅変調 (PWM) 回路

##### 3.2.2. リーディングエッジブランкиング (LEB)

内部 SenseFET が起動すると同時に、通常一次側容量と二次側整流器の逆回復によって、SenseFET を通して高電流スパイクが発生します。 $R_{SENSE}$  抵抗にかかる過電圧は、電流モードの PWM 制御においてフィードバック動作の誤作動を引き起こします。この影響に対応するため、FSL4110LR はリーディングエッジブランкиング (LEB) 回路を採用しています。この回路は、SenseFET がオンすると、 $t_{LEB}$  (250 ns) の間、PWM コンパレータを抑制します。

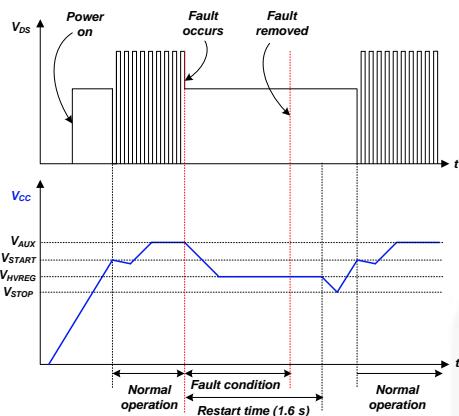

#### 3.3. 保護回路

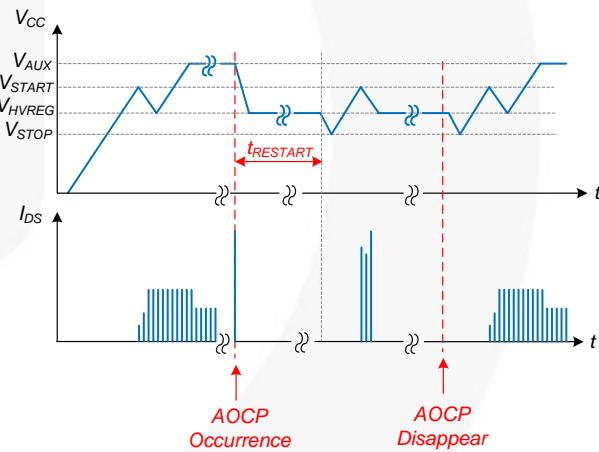

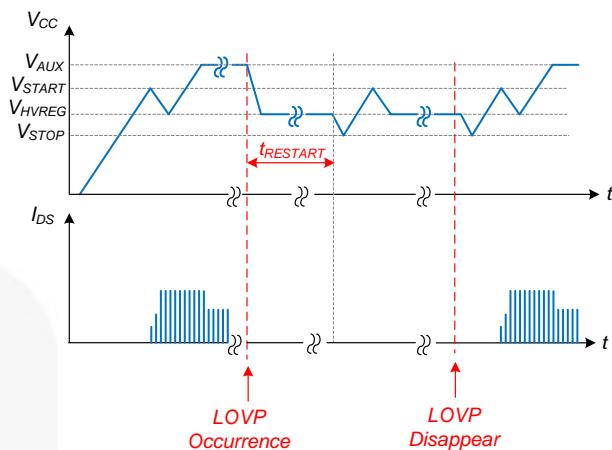

保護機能には、過負荷保護 (OLP)、過電圧保護 (OVP)、低電圧ロックアウト (UVLO)、異常過電流保護 (AOCP)、サーマルシャットダウンが含まれます。図 4 に示すように、すべての保護機能はオートリストアモードで動作します。これらの保護回路は、外部装置を使用せず IC 内に完全統合されているため、費用と PCB のスペースを増加させることなく信頼性が向上します。故障が発生した場合、スイッチングは停止し、SenseFET はオフのままになります。同時に、オートリストアの間、電力消費と能動および受動部品へのストレスを削減するため、内部保護タイミング制御が作動します。内部保護タイミング制御が作動すると、内部高電圧レギュレーターにより  $V_{CC}$  が 10 V に制限される一方、スイッチングは停止します。この内部保護タイミング制御は、オートリストア遅延時間 (1.6 s) が終了するまで継続されます。1.6 s に達すると、内部の高電圧レギュレーターは停止し、 $V_{CC}$  が下がります。 $V_{CC}$  が UVLO 停止電圧の  $V_{STOP}$  (8 V) に達すると、保護はリセットされ、内部高電圧電流源は再度  $V_{CC}$  コンデンサーを高電圧スタートアップピン ( $V_{STR}$ ) 経由で充電します。 $V_{CC}$  が UVLO 開始電圧の  $V_{START}$  (12 V) に達すると、FSL4110LR は通常動作を再開します。このように、オートリストア機能は、故障が解消するまで、電源 SenseFET のスイッチングの作動・停止を交互に繰り返すことができます。

図 4. オートリスタート保護波形

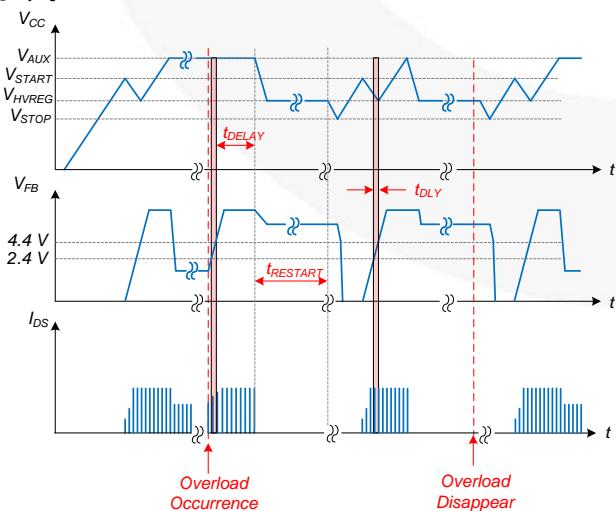

### 3.3.1. 過負荷保護 (OLP)

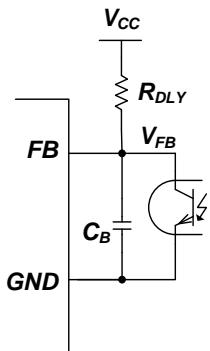

過負荷は、予期しない異常事態のために負荷電流が通常レベルを超過した状態として定義されます。この状況では、保護回路は SMPS を保護する為に働く必要があります。しかしながら、SMPS が通常動作の場合でも、負荷変化中に過負荷保護回路が誘発される場合があります。こういった不要な動作を防止するため、過負荷保護回路は一定時間経過した後にのみ作動するよう設計されており、一時的な状況か本当の過負荷状況かを判断します。パルス・バイ・パルスの電流制限機能によって、SenseFET に流れる最大ピーク電流は制限されます。出力がこの最大電力を超えて消費した場合、出力電圧はセット電圧以下に減少します。これによりオプトダイオードを通る電流が減少し、オプトカプラーのトランジスターの電流も減ることで、フィードバック電圧 ( $V_{FB}$ ) が上昇します。 $V_{FB}$  が 2.4 V を超えると、内部ダイオード  $D1$  がブロックされ、 $R_{DLY}$  による電流 ( $I_{DLY}$ ) が  $C_{FB}$  の充電を開始します。フィードバック電圧が 4.4 V に達すると、内部の固定遅延時間 ( $t_{DELAY}$ ) のカウントが開始されます。フィードバック電圧が  $t_{DELAY}$  (100 ms) 後も 4.4 V を超えている場合、スイッチング動作が停止します（図 5 を参照）。内部 OLP 回路を図 6 に示します。

セルフバイアスでは、5 MΩ 以下の  $R_{DLY}$  値が推奨されます。

図 5. OLP 波形

図 6. OLP 回路

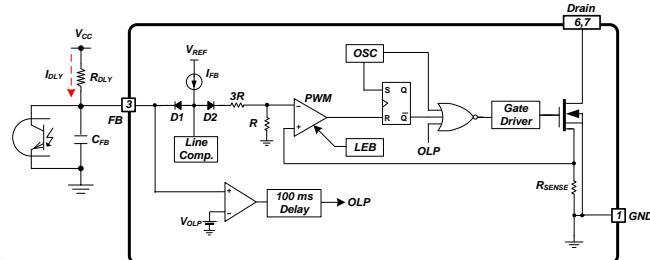

### 3.3.2. 異常過電流保護 (AOCP)

二次整流ダイオードまたは変圧器ピンがショートした際、最小、ターン・オン時間中、極度に高い  $di/dt$  と共に大電流が SenseFET に流れることもあります。OLP がトリガされるまで SenseFET に激しい電流ストレスがかかるため、そのような異常状態で FSL4110LR を保護するには、過負荷保護機能では不十分です（図 7を参照）。内部 AOCP 回路を図 8 に示します。ゲートのターン・オン信号がパワー SenseFET に印加された時、AOCP ブロックが起動しセンス抵抗を通じて電流をモニターします。抵抗にかかる電圧は、設定された AOCP レベルと比較されます。センス抵抗の電圧が AOCP レベルを超えると、NOR ゲート入力にハイ信号が適用され、SMPS が停止します。

図 7. AOCP 波形

図 8. AOCP 回路

### 3.3.3. 過電圧保護 (OVP)

二次側のフィードバック回路が誤動作、またはフィードバック経路の開放を引き起こすはんだ不良があった場合、オプトカプラトランジスタ経由の電流はほぼゼロになります。すると、 $V_{FB}$  が過負荷状態と同様に上昇することで、過負荷保護機能がトリガされるまで設定された最大ドレイン電流が流れます。出力に要求以上のエネルギーが供給されるため、過負荷保護が作動する前に出力電圧が定格電圧を超過する可能性があり、結果として二次側デバイスの破壊につながります。このような状況を避けるため、OVP 回路が採用されています。一般に、バイアス巻線を使用する場合、 $V_{CC}$  は出力電圧に比例するため、FSL4110LR では出力電圧を直接モニターする代わりに、 $V_{CC}$  を利用します。 $V_{CC}$  が 24.5 V を超えると、OVP 回路がトリガされてスイッチング動作が停止します。通常動作時に OVP が不必要に作動しないように、通常時は  $V_{CC}$  が 24.5 V より低くなるように設計する必要があります。内部 OVP 回路を図 9 に示します。

図 9. OVP 回路

### 3.3.4. サーマルシャットダウン (TSD)

同じパッケージに SenseFET と制御 IC を統合することで、SenseFET の温度の検出が容易になります。ジャンクション温度が 140°C を超えたとき、サーマルシャットダウンが作動します。FSL4110LR は、温度が  $t_{RESTART}$  (1.6 s) 以内に 60°C 下がると、再起動します。

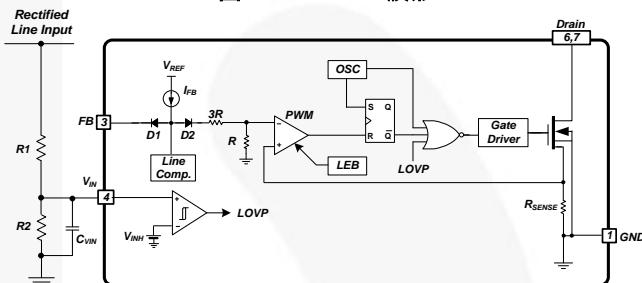

### 3.3.5. ライン過電圧保護 (LOVP)

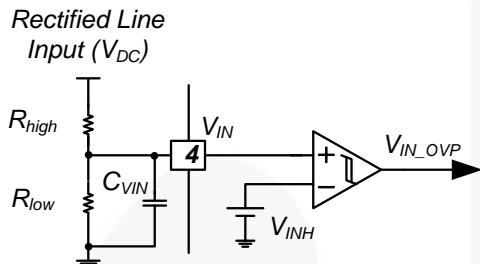

ライン入力電圧が望ましくないレベルまで増加した場合、高ライン入力電圧はシステム全体に高電圧ストレスを発生させます。このような異常状態から SMPS を保護するため、LOVP が組み込まれています。この機能は、抵抗分圧を使用して  $V_{IN}$  電圧を検出することで実現されます。 $V_{IN}$  電圧が 2.0 V より高い場合は異常状態と見なされ、 $V_{IN}$  電圧が  $t_{RESTART}$  以内に 1.9 V 程度にまで下がるまで、PWM スイッチングが停止します（図 10 を参照）。図 11 は LOVP 回路を示します

図 10. LOVP 波形

図 11. LOVP 回路

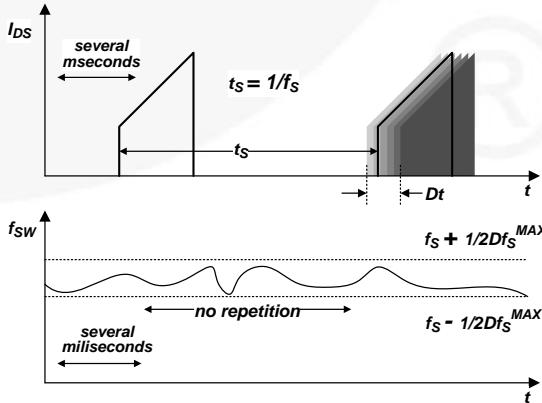

### 3.4. オシレータブロック

オシレータの周波数は内部で設定され、FSL4110LR は、図 12 に示すようにランダムな周波数変動機能を備えています。スイッチング周波数の変動によって、EMI のテスト装置で測定された帯域幅よりも広い周波数の範囲にエネルギーを拡散させることで EMI を削減できます。周波数の変動範囲は内部で固定されています。しかし、その選択は、外部フィードバック電圧と内部フリーランニングオシレータの組み合わせによってランダムに選択されます。ランダムに選択されたスイッチング周波数は、国際的な EMI 要件を満たすため、スイッチング周波数周辺で EMI ノイズを効率的に拡散し、AC 入力ラインフィルタの代わりに費用対効果の良いインダクタの使用を可能にします。

図 12. 周波数変動波形

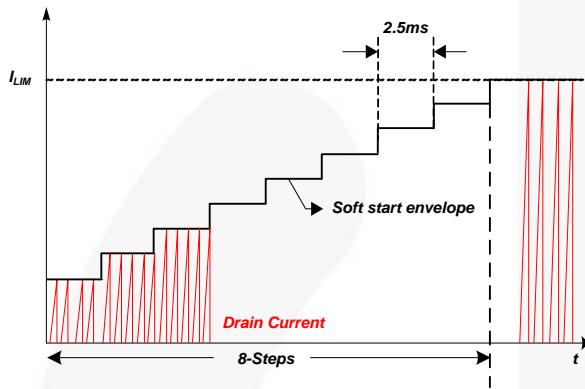

### 3.5. ソフトスタート

内部のソフトスタート回路は、起動後に SenseFET 電流を徐々に増加させます。標準的なソフトスタート時間は 20 ms で、スタートアップの間、SenseFET の電流は、図 13 に示すように段階的に増加します。このパワースイッチングデバイスのパルス幅は、トランジスト、インダクタ、コンデンサのための適した動作状況を確立するため継続的に増加します。出力コンデンサの電圧は、必要な出力電圧をスムーズに確立するため徐々に増加します。ソフトスタートはまた、トランジスト飽和の防止と二次ダイオードへのストレス削減に役立ちます。

図 13. 内部ソフトスタート

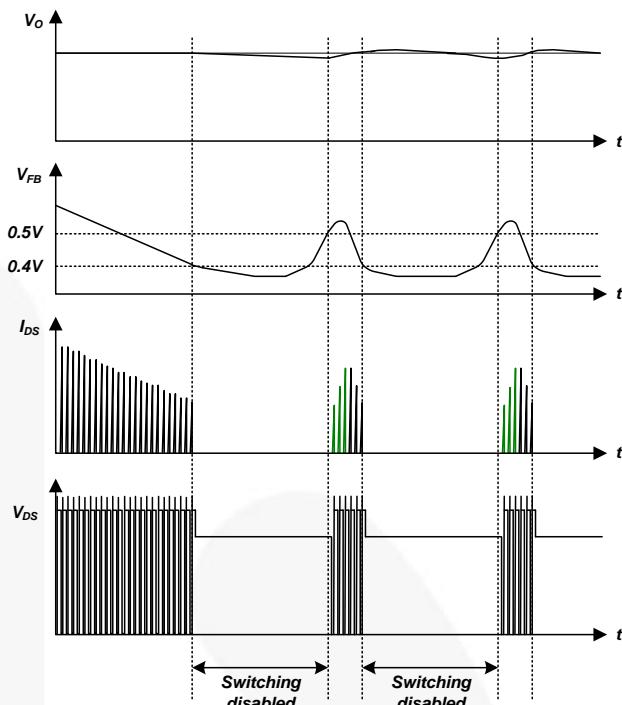

### 3.6. バーストモード動作

待機モードでの電力消費を最小化するため、FSL4110LR はバースト・モードに突入します。負荷が減少するにつれて、フィードバック電圧も減少します。フィードバック電圧が  $V_{BURL}$  (400 mV) を下回ると、図 14 に示すようにデバイスは自動的にバーストモードに移行します。この時点では、スイッチングは停止し出力電圧は待機電流の負荷によって決まる比率まで下落し始めます。これによって、フィードバック電圧は上昇します。 $V_{BURH}$  (500 mV) を超えると、スイッチングが再開されます。その後、帰還電圧は下落しプロセスが繰り返されます。バースト・モードは、SenseFET のスイッチングを交互に有効、無効化し、待機モードでのスイッチング損を削減します。加えて、可聴騒音を削減するため、ソフトスタートが動作します。

図 14. バーストモード動作

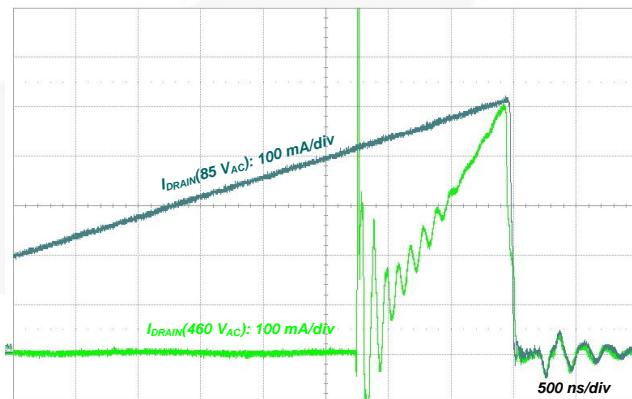

### 3.7. ライン補償

全てのスイッチング装置には、それに固有の伝搬遅延があります。この伝搬遅延は、 $t_{CLD}$  に定義される電流制限遅延の原因になります。電流制限遅延  $t_{CLD}$  があるために、低入力電圧と高入力電圧では電流ピークに差が生じます。電流ピークの分散は入力電圧間の差に関連しており、入力電圧の差が大きいほど電流ピークは分散します。

入力電圧に関わらず、一定の電流ピークを維持するために、ライン補正が必要となります。FSL4110LR はライン補正機能を備えており、高入力電圧の実際のピーク値は低入力電圧のピーク値と同様になります。 $t_{CLD}$  の影響は、図 15 に示すように無視できる程度です

図 15.  $I_{LIMIT}$  波形 (85 V<sub>AC</sub> 対 460 V<sub>AC</sub>)

## 4. 設計例

ここでは、e メータリングシステム用、入力電圧 85 V<sub>AC</sub>~460 V<sub>AC</sub> の 6 W フライバックコンバーターの設計例を取り上げます。

### 4.1. システムスペックを決定する

| 1. Define the system specifications       |            |            |            |            |

|-------------------------------------------|------------|------------|------------|------------|

| Minimum Line voltage ( $V_{line}^{min}$ ) | 85 V.rms   |            |            |            |

| Maximum Line voltage ( $V_{line}^{max}$ ) | 460 V.rms  |            |            |            |

| Line frequency ( $f_L$ )                  | 60 Hz      |            |            |            |

| 1st output for feedback                   | $V_{o(n)}$ | $I_{o(n)}$ | $P_{o(n)}$ | $K_{L(n)}$ |

| Full load output power ( $P_o$ )          | 20 V       | 0.30 A     | 6 W        | 100 %      |

| Estimated efficiency ( $\eta$ )           | 6.0 W      |            | 80 %       |            |

| Full load input power ( $P_{in}$ )        | 7.5 W      |            |            |            |

図 16. システムスペック

- 出力電力 ( $P_O$ ) = 6.0 W (20 V / 0.3 A)

- $V_{AC}$  入力電圧範囲 = 85~460 V<sub>AC</sub>

- ライン周波数 ( $f_L$ ) = 60 Hz

- 推定効率 ( $\eta$ ) > 80%

電力変換効率を推定して最大入力電力を算出するためには、推定効率が必要です。参照するデータがない場合、低電圧出力アプリケーションでは  $\eta = 0.7 \sim 0.75$ 、高電圧出力アプリケーションでは  $\eta = 0.8 \sim 0.85$  に設定します。

複数出力の SMPS の場合、各出力の負荷占有係数は、次のように定義されます。

$$K_{L(n)} = \frac{P_{O(n)}}{P_O} \quad (2)$$

ここで  $P_{O(n)}$  は、n 番目の出力の最大出力電力です。単出力の SMPS の場合は  $K_{L(1)}=1$  です。

このアプリケーションは単出力であるため、 $K_{L(n)}$  の値は 1 です。

### 4.2. DC リンクコンデンサー ( $C_{DC}$ )、DC リンク電圧範囲、スタートアップ抵抗 ( $R_{STR}$ ) を決定します

| 2. Determine DC link capacitor, DC link voltage range & startup resistor ( $R_{STR}$ ) |                |

|----------------------------------------------------------------------------------------|----------------|

| DC link capacitor ( $C_{DC}$ )                                                         | 22 $\mu$ F     |

| Bulk capacitor charging duty ratio ( $D_{ch}$ )                                        | 0.2            |

| Minimum DC link voltage ( $V_{DC}^{min}$ )                                             | 100 V          |

| Maximum DC link voltage ( $V_{DC}^{max}$ )                                             | 651 V          |

| Startup charging current ( $I_{CH}$ )                                                  | 1 mA           |

| Recommended startup resistor ( $R_{STR}$ )                                             | 88 K $\Omega$  |

| Determine startup resistor ( $R_{STR}$ )                                               | 100 k $\Omega$ |

| Power loss in startup resistor ( $P_{RSTR}$ )                                          | 400.0 mW       |

図 17.  $C_{DC}$  と  $R_{STR}$  の決定

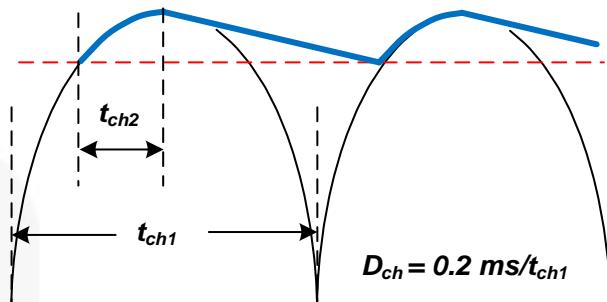

DC リンクコンデンサーの値には、ユニバーサル入力電圧範囲 (85~460 V<sub>AC</sub>) では入力電力 1 ワット当たり 2 ~3  $\mu$ F、ヨーロッパ入力電圧範囲 (195~460 V<sub>AC</sub>) では入力電力 1 ワット当たり 1  $\mu$ F が標準的に使用されます。図 18 は、修正された入力電圧波形を示します。

青線は DC リンクコンデンサーのリップル電圧を示します。DC リンクコンデンサーの最小および最大電圧は式とで表されます (3)(4)。

図 18. ブリッジダイオードとバルクコンデンサーの電圧波形

$$V_{DC}^{min} = \sqrt{2 \times (V_{line}^{min})^2 - \frac{(P_o)/\eta \times (1-D_{ch})}{C_{DC} \times f_L}} \quad (3)$$

$$= \sqrt{2 \times (85V_{AC})^2 - \frac{6W/0.8 \times (1-0.2)}{22\mu F \times 60Hz}} \\ = 100V$$

$$V_{DC}^{max} = \sqrt{2} \times V_{line}^{max} = \sqrt{2} \times 460V = 651V \quad (4)$$

ここで、 $D_{ch}$  は、図 18 に示す DC リンクコンデンサーに対する充電期間のデューティ比で、標準的には 0.2 度程です。

出力電力は 6 W であるため、コンデンサー  $C_{DC}$  は 12  $\mu$ F~18  $\mu$ F です。 $C_{DC}$  に対し標準の近似値 22  $\mu$ F を選択し、上式に代入します。よって、式 (3) と (4) から、 $V_{DC}^{min}$  は 100 V、 $V_{DC}^{max}$  は 651 V になります。

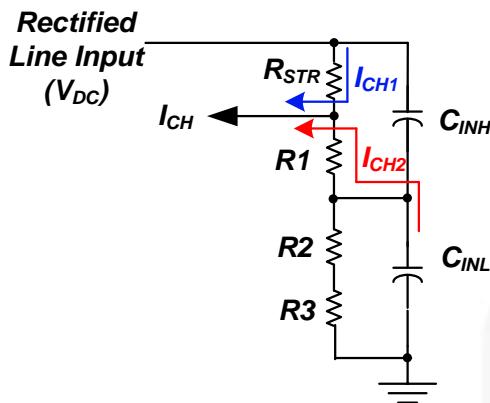

高入力電圧アプリケーションには高電圧定格のバルクコンデンサーが必要ですが、サイズが大型化し価格も上がります。この解決策として、相対的に低電圧定格の直列接続バルクコンデンサーが考えられます。直列接続のコンデンサーの場合、良好な電圧均等化を実現するためにバランス抵抗が必要です。低抵抗は、軽負荷状態で比較的大きな待機電力の消費につながります。この状況を避けるためには、数 M $\Omega$  の抵抗を使用することをお勧めします。HV<sub>REG</sub> は、バランス抵抗を通るライン電圧から供給されます。直列接続したバルクコンデンサーの中間点から HV<sub>REG</sub> を供給すると、バルクコンデンサーの電圧不均衡が生じ、ライン電圧が低いときにスタートアップ時間が長くなりすぎる可能性があります。そのため、HV<sub>REG</sub> は、図 19 に示すように、 $R_{STR}$  と R1 との間から供給することをお勧めします。スタートアップ充電電流 ( $I_{CH}$ ) は、 $R_{STR}$  と R1 から供給されます。しかし、R1 から供給される  $I_{CH2}$  は  $R_{STR}$  から供給される  $I_{CH1}$  よりかなり低いため、 $I_{CH1}$  は  $I_{CH}$  と同様であると見なせます。FSL4110LR を起動するには、1 mA 以上の  $I_{CH}$  が必要です。

図 19. バランス抵抗

スタートアップ抵抗 ( $R_{STR}$ ) は式 (5) により算出できます。

$$R_{STR} \leq \frac{V_{DC}^{\min} - V_{START}}{I_{CH}} = \frac{100V - 12V}{1mA} = 88k\Omega \quad (5)$$

ここで、 $R_{STR} + R1 = R2 + R3$ 、 $I_{CH} = 1 \text{ mA}$

このアプリケーションノートでは、 $R_{STR}$  の値として 100 kΩ を使用します。

### 4.3. 反射出力電圧 ( $V_{RO}$ )、最大デューティ比 ( $D_{MAX}$ )、巻数比を決定する

| 3. Determine Maximum duty ratio (Dmax)           |

|--------------------------------------------------|

| Output voltage reflected to primary ( $V_{RO}$ ) |

| 80 V                                             |

| Maximum duty ratio at full loading ( $D_{max}$ ) |

| 0.33 --->DCM operation                           |

| Max nominal MOSFET voltage ( $V_{ds}^{nom}$ ) =  |

| 731 V                                            |

図 20. 最大デューティ比の決定

フライバックコンバーターには、連続導通モード (CCM) と不連続導通モード (DCM) の 2 種類の動作モードがあります。CCM と DCM には、それぞれの長所、短所があります。一般的に、DCM の方が整流ダイオードに対して優れたスイッチング条件を提供します。なぜなら、ダイオードは電流がゼロになる時点で逆バイアスされるように動作するためです。DCM の場合、CCM に比べ蓄えられる平均エネルギーが小さいため、トランジスタのサイズも小さくできます。しかし、DCM では本質的に RMS 電流が高くなるため、MOSFET の導通損失と出力コンデンサーの電流ストレスは増加します。したがって、DCM は、スマートメータリングなどの高電圧・低電流出力のアプリケーションに適していると言えます。DCM 動作であるため、 $D_{max}$  には 0.33 を使用します。

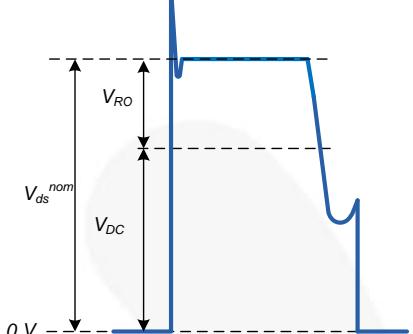

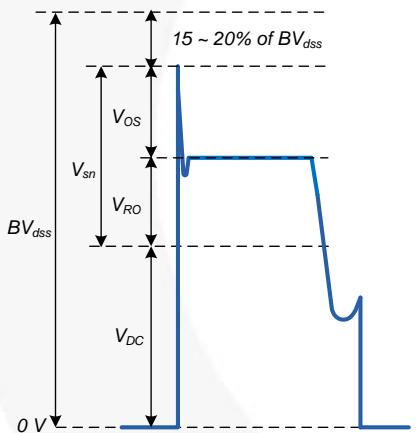

FSL4110LR 内の SenseFET がオフすると、入力電圧 ( $V_{DC}$ ) と、出力から一次側への反射電圧 ( $V_{RO}$ ) が、図 21 に示すように MOSFET に印加されます。 $D_{max}$  を決定した後、 $V_{RO}$  と、MOSFET にかかる最大公称電圧 ( $V_{ds}^{nom}$ ) は、次のように求めます。

$$V_{ds}^{nom} = V_{DC}^{\max} + V_{RO} = 651V + 80V = 731V \quad (6)$$

図 21. 出力から一次側への反射電圧

$V_{ds}^{nom}$  は、漏れインダクタンスによる電圧スパイクを考慮すると、MOSFET の定格電圧の 65~75% になります。

### 4.4. トランス一次側インダクタンス ( $L_m$ ) を求め、電流制限値を選択する

| 4. Determine transformer primary inductance (Lm) |

|--------------------------------------------------|

| Switching frequency of FPS ( $f_s$ )             |

| 50 kHz                                           |

| Ripple factor ( $K_{RF}$ )                       |

| 1 --->OK                                         |

| Primary side inductance ( $L_m$ ) =              |

| 1438 uH                                          |

| Maximum peak drain current ( $I_{ds}^{peak}$ ) = |

| 0.46 A                                           |

| RMS drain current ( $I_{ds}^{rms}$ ) =           |

| 0.15 A                                           |

| 5. Choose the proper FPS considering the input power and current limit |

|------------------------------------------------------------------------|

| Typical current limit of FPS ( $I_{LM}$ )                              |

| 0.52 A                                                                 |

| Minimum $I_{LM}$ considering tolerance of 12%                          |

| 0.46 A > 0.46 A --->OK                                                 |

図 22. トランス一次側インダクタンスと電流制限値の決定

負荷条件と入力電圧の変動に応じて、CCM と DCM の間で動作が切り替わります。どちらの動作モードでも、トランジスタの一次側インダクタンスの設計におけるワーストケースは、全負荷、最小入力電圧時です。この条件下の  $L_m$  は、次のように求めます。

$$L_m = \frac{(V_{DC}^{\min} \times D_{max})^2}{2 \times P_{in} \times f_s \times K_{RF}} = \frac{(100V \times 0.33)^2}{2 \times 7.5W \times 50kHz \times 1} \approx 1.4mH \quad (7)$$

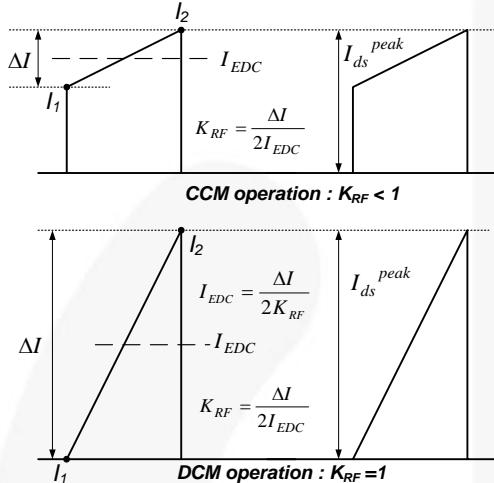

ここで、 $f_s$  はスイッチング周波数、 $K_{RF}$  は全負荷、最小入力電圧時のリップルファクタです。 $K_{RF} = 1$ 。

$K_{RF}$  は図 23 のように定義されます。DCM モードでは  $K_{RF} = 1$ 、CCM モードでは  $K_{RF} < 1$  になります。リッ

フルファクタは、トランスのサイズ、MOSFET の電流の RMS 値と密接に関連しています。リップルファクタを小さくすることで MOSFET で発生する導通損失を抑えられますが、リップルファクタを小さくし過ぎると、トランスのサイズが大きくなります。CCM モードで動作するフライバックコンバーターを設計する場合、ユニバーサル入力電圧範囲の場合は  $K_{RF} = 0.25 \sim 0.5$ 、ヨーロッパ入力電圧範囲の場合は  $K_{RF} = 0.4 \sim 0.8$  に設定するのが一般的です。

図 23. MOSFET のドレイン電流と KRF

$L_m$  を求めたら、通常動作時の MOSFET の最大ピーケ電流と RMS 電流は、次のように求めます。

$$I_{ds}^{peak} = \sqrt{\frac{2 \times P_{IN}}{L_m \times f_s}} = \sqrt{\frac{2 \times 7.5W}{1.4mH \times 50kHz}} \quad (8)$$

$$\approx 0.46A$$

SenseFET の最大ピーケドレイン電流 ( $I_{ds}^{peak}$ ) が式 (8) から求められます。パルス毎の電流制限レベル ( $I_{LIM}$ ) が  $I_{ds}^{peak}$  よりも高くなるようにします。FSL4110LR における  $I_{LIM}$  の許容範囲は ± 12% です。したがって、 $I_{ds}^{peak}$  は、 $I_{LIM}$  の 88% 未満となるように、0.46 A とします。

ドレインの rms 電流は次式により求められます。

$$I_{ds}^{rms} = \sqrt{3 \times (I_{EDC})^2 + \left(\frac{\Delta I}{2}\right)^2} \times \frac{D_{MAX}}{3} \quad (9)$$

$$\approx \sqrt{3 \times (0.228)^2 + \left(\frac{0.457}{2}\right)^2} \times \frac{0.33}{3} \approx 0.15A$$

$$\text{where, } I_{EDC} = \frac{\Delta I}{2 \times K_{RF}} \approx 0.228$$

$$\Delta I = \frac{V_{DC}^{min} \times D_{max}}{L_m \times f_s} \approx 0.457$$

#### 4.5. トランスのコアサイズ ( $A_e$ ) と一次側最小巻線数 ( $N_p^{min}$ ) を決定する

| 6. Determine the proper core and the minimum primary turns |                      |         |

|------------------------------------------------------------|----------------------|---------|

| Saturation flux density ( $B_{sat}$ )                      | 0.35 T               |         |

| Cross sectional area of core ( $A_e$ )                     | 22.8 mm <sup>2</sup> |         |

| Minimum primary turns ( $N_p^{min}$ )                      | =                    | 105.0 T |

図 24. トランスのコアサイズと一次側最小巻線数の決定

このアプリケーションノートでは、EPC17 コアを選択します。選択したコアをもとに、次式により、コアが飽和しない範囲でトランストラス一次側の最小巻線数を求めます。

$$N_p^{min} = \frac{L_m \times I_{LIM} \times 1.12}{B_{sat} \times A_e} \times 10^6 \quad (10)$$

$$\approx \frac{1.438mH \times 0.52A \times 1.12}{0.35T \times 22.8mm^2} \times 10^6 \approx 105 Turns$$

ここで、 $B_{max}$  は飽和磁束密度、 $A_e$  はコアの断面積です。

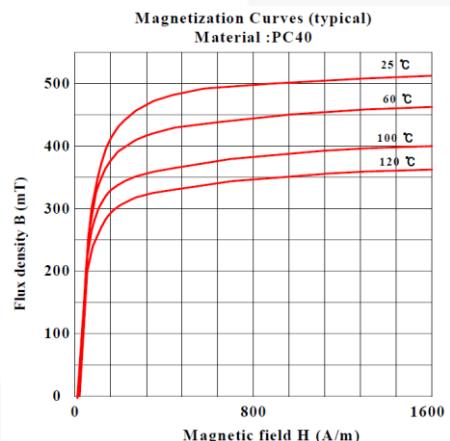

図 25 は TDK のフェライトコア (PC40) の代表的な特性を示します。飽和磁束密度 ( $B_{sat}$ ) は温度上昇とともに減少するので、高温時の特性を考慮する必要があります。参考するデータがない場合、 $B_{sat} = 0.3 \sim 0.35$  T にします。過渡時または障害時には MOSFET のドレイン電流が  $I_{ds}^{peak}$  を超えて  $I_{LIM}$  に到達するので、遷移時のコアの飽和を避けるために、 $I_{LIM}$  を式 (8) に適用し、 $I_{ds}^{peak}$  は使用しません。

図 25. フェライトコア標準 B-H 特性 (TDK/PC40)

#### 4.6. 二次側巻線数 ( $N_s$ )、 $V_{CC}$ 巻線数 ( $N_A$ ) を決定する

| 7. Determine the number of turns for each output |            |            |                       |      |

|--------------------------------------------------|------------|------------|-----------------------|------|

| $V_{cc}$ (Use $V_{cc}$ start voltage)            | $V_{o(n)}$ | $V_{f(n)}$ | $\# \text{ of turns}$ |      |

| 1st output for feedback                          | 14 V       | 1.2 V      | 20.0                  | 20 T |

| VF : Forward voltage drop of rectifier diode     | 20 V       | 0.5 V      | 27                    | 27 T |

Primary turns ( $N_p$ ) = 105 T

→ enough turns

図 26. 各出力の巻線数の決定

まず、基準値として、一次側とフィードバック制御される二次側の巻線数との比 ( $n$ ) を求めます。

$$n = \frac{N_p}{N_{S1}} = \frac{V_{RO}}{V_{O1} + V_{F1}} \quad (11)$$

ここで  $N_p$ 、 $N_{S1}$  はそれぞれ、一次側、基準出力の巻線数、 $V_{O1}$  は出力電圧、 $V_{F1}$  はダイオードの基準出力の順方向電圧です。

次に、最終的な  $N_p$  が式 (10) で求めた  $N_p^{\min}$  よりも大きくなるように、適切な  $N_{S1}$  の整数値を決定します。

出力側と  $V_{CC}$  の巻線数は次式で求められます。

$$N_{S1} = \frac{N_p \times (V_{O1} + V_{F1})}{V_{RO}} = \frac{105 \times (20V + 0.5V)}{80V} \approx 27 \text{ Turns} \quad (12)$$

$$N_A = \frac{N_{S1} \times (V_{CC} + V_{Fa})}{V_{O1} + V_{F1}} = \frac{27 \times (14V + 1.2V)}{20V + 0.5V} \approx 20 \text{ Turns} \quad (13)$$

ここで、 $V_{Fa}$  は  $V_{CC}$  ダイオードの順方向電圧、 $V_{F1}$  は二次側ダイオードの順方向電圧です。

$V_{CC}$  は FSL4110LR の供給電圧公称値です。出力負荷の増加に伴い  $V_{CC}$  も増加しますので、通常動作時に過電圧保護が作動しないよう、 $V_{CC}$  は 14 V に設定するのが妥当です。

## 4.7. 二次側の整流ダイオードを選択する

### 9. Choose the rectifier diode in the secondary side

|                  | $V_{D(n)}$ | $I_{D(n)}^{\text{rms}}$ |

|------------------|------------|-------------------------|

| Vcc diode        | 138 V      | 0.10 A                  |

| 1st output diode | 187 V      | 0.84 A                  |

図 27. 二次側の整流ダイオードの選択

出力側整流ダイオードの最大逆方向電圧と、rms 電流は次のように求めます。

$$V_D = V_{O1} + \frac{V_{DC}^{\max} \times (V_{O1} + V_{F1})}{V_{RO}} \quad (14)$$

$$= 20V + \frac{651V \times (20V + 0.5V)}{80V} \approx 187V$$

$$I_D^{\text{rms}} = I_{ds}^{\text{rms}} \times \sqrt{\frac{1 - D_{\max}}{D_{\max}}} \times \frac{V_{RO} \times K_{L(1)}}{V_{O1} + V_{F1}} \quad (15)$$

$$= 0.15A \times \sqrt{\frac{1 - 0.33}{0.33}} \times \frac{80V \times 1}{20V + 0.5V} \approx 0.84A$$

標準的には、ダイオードの最大逆方向電圧 ( $V_{RRM}$ ) は  $V_D$  の 1.3 倍、ダイオードの平均順方向電流は  $I_D^{\text{rms}}$  の 1.5 倍です。しかし、出力容量と出力電圧が大きい場合、ソフトスタート時には出力コンデンサーを充電するだけの出力電圧が得られないため、ダイオードの  $V_{RRM}$  は  $V_D$  の 3 倍必要です。したがって整流ダイオードとして EGP30J を選択します。（EGP30J のスペック：最大逆方向電圧  $V_{RRM}$  は 600 V、平均順方向電流  $I_F$  は 3 A）

## 4.8. 一次側 RCD スナバを決定する

### 11. Design RCD snubber for SenseFET (at peak load)

|                                                   |          |

|---------------------------------------------------|----------|

| Primary side leakage inductance ( $L_{lk}$ )      | 16 uH    |

| Maximum Voltage of snubber capacitor ( $V_{sn}$ ) | 155 V    |

| Maximum snubber capacitor voltage ripple          | 6 %      |

| Power loss in snubber resistor ( $P_{sn}$ )       | 0.2 W    |

| Snubber resistor ( $R_{sn}$ )                     | 139.3 kΩ |

| Snubber capacitor ( $C_{sn}$ )                    | 2.4 nF   |

図 28. 一次側 RCD スナバの決定

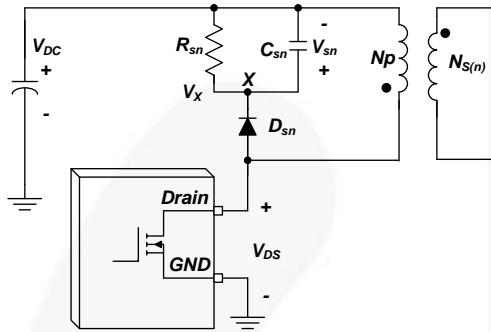

パワー MOSFET がオフすると、トランジスタの漏れインダクタンスにより高いスパイク電圧がドレインに発生します。大きな電圧により MOSFET がアバランシェ降伏を引き起こし、さらには FSL4110LR の損傷に至る可能性があります。したがって、電圧をクランプする回路を附加する必要があります。

RCD スナバ回路と MOSFET のドレイン電圧波形を図 29 と図 30 にそれぞれ示します。RCD スナバ回路は、MOSFET ドレイン電圧がダイオードのノード X の電圧を超えると、スナバダイオード ( $D_{sn}$ ) がオンすることで、図 29 に示すように、漏れインダクタンスによる電流を吸収します。スナバ回路の解析において、スナバコンデンサーの電圧値が 1 回のスイッチングサイクルでは著しく変化しない程度に十分に大きいと仮定しています。

スナバ回路設計の最初のステップは、最小入力電圧、全負荷時のスナバコンデンサーの電圧 ( $V_{sn}$ ) を決定することです。 $V_{sn}$  を決定したら、最小入力電圧、全負荷時にスナバ回路で消費される電力を次式により求めます。

$$P_{sn} = \frac{V_{sn}^2}{R_{sn}} = \frac{1}{2} L_{lk} \times (I_{ds}^{\text{peak}})^2 \times f_s \times \frac{V_{sn}}{V_{sn} - V_{RO}} \quad (16)$$

$$= 0.5 \times 20\mu H \times (0.46A)^2 \times 50kHz \times \frac{160V}{160V - 80V}$$

$$\approx 0.2W$$

$V_{sn}$  は  $V_{RO}$  よりも大きくする必要があるため、 $V_{sn}$  は  $V_{RO}$  の 2~2.5 倍に設定するのが一般的です。 $V_{sn}$  の値が小さすぎると、式 (16) からわかるように、スナバ回路に著しい損失が発生します。漏れインダクタンスは他のすべての巻線を短絡した状態で、一次巻線に対しスイッチング周波数を用いて測定します。

次に、この電力損失をもとに適切な定格ワット数のスナバ抵抗を選択します。標準的には、スナバコンデンサー電圧のリップル電圧は 5~10% です。スナバ抵抗 ( $R_{sn}$ ) と容量 ( $C_{sn}$ ) は次式により求めます。

$$R_{sn} = \frac{V_{sn}^2}{P_{sn}} = \frac{[155V]^2}{0.2W} \approx 139.3k\Omega \quad (17)$$

$$C_{sn} = \frac{V_{sn}}{\Delta V_{sn} \times R_{sn} \times f_s} \quad (18)$$

$$= \frac{155V}{6\% \times 155V \times 139.3k\Omega \times 50kHz} \approx 2.4nF$$

$R_{sn}$  からのパワー損失を低減するために、 $R_{sn}$  には、式(17)で得られた  $139.3\text{ k}\Omega$  よりも大きい値を選択する必要があります。 $R_{sn}$  の値が大きくなると、 $V_{sn}$  も上昇します。 $R_{sn}$  の推奨値は  $200\text{ k}\Omega \sim 47\text{ k}\Omega$  です。 $V_{ds}^{max}$  が、図 30 に示すように  $800\text{ V}$  (SenseFET の定格電圧の 80%) より低いかどうか確認してください。このアプリケーションノートでは、 $C_{sn}$  と  $R_{sn}$  の値として、 $2.2\text{ nF}$  と  $150\text{ k}\Omega$  をそれぞれ使用します。

スナバダイオードの電圧定格は  $BV_{dss}$  よりも高くなればなりません。スナバ回路には、通常、電流定格  $1\text{ A}$  の超高速ダイオードを用います。

図 29. 一次側 RCD スナバ回路

図 30. MOSFET のドレイン電圧波形

#### 4.9. 二次側 RCD スナバを決定する

| 12. Design snubber for Output Diode (at startup)    |          |

|-----------------------------------------------------|----------|

| Rigging frequency for 2'nd diode ( $f_{RING}$ )     | 25 MHz   |

| Capacitance of 2'nd diode ( $C_D$ )                 | 75 pF    |

| Peak Voltage of 2'nd diode                          | 328 V    |

| Snubber capacitor ( $C_{sns}$ ) for 2'nd diode =    | 225.0 pF |

| Inductance ( $L_{sec}$ ) at 2'nd side =             | 0.54 uH  |

| Snubber resistor ( $R_{sns}$ ) for 2'nd diode =     | 84.9 Ω   |

| Power loss in 2'nd snubber resistor ( $P_{sns}$ ) = | 0.6 W    |

図 31. 二次側 RCD スナバの決定

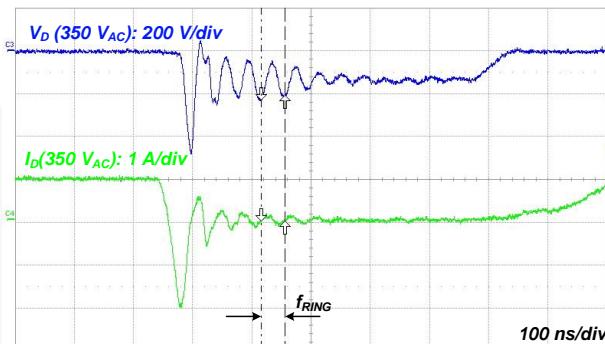

スタートアップ時は出力電圧が非常に低く、フライバックコンバーターは CCM モードで動作します。出力電圧が高く、出力容量が大きいと、図 32 に示すように非常に高いスパイク電圧が二次側ダイオードに発生

します。電圧スパイクを減らすために、二次側ダイオードにスナバを使用する必要があります。

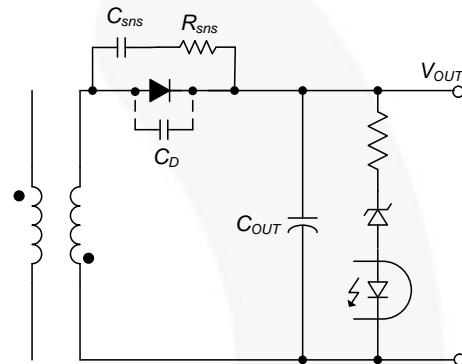

$C_D$  は二次側ダイオードの容量です。 $C_{sns}$  と  $R_{sns}$  は、図 33 に示すように外部スナバ回路です。

図 32. スナバがない場合の二次側電圧スパイク

図 33. 二次側スナバ回路

スナバの設計では、図 32 に示すような二次側の振動のリング周波数を測定して、二次側ダイオードの容量を確認する必要があります。

$$f_{RING} = 25\text{ MHz} \quad (19)$$

$$C_D = 75\text{ pF}$$

$f_{RING}$  の半分となる  $C_{sns}$  は、次式により求められます。

$$C_{sns} = 3 \times C_D = 3 \times 75\text{ pF} = 225\text{ pF} \quad (20)$$

$C_{sns}$  を求めたら、二次側インダクタンス ( $L_{sec}$ ) は次式により得られます。

$$L_{sec} = \frac{\left(\frac{2}{f_{RING} \times 2\pi}\right)^2}{C_D + C_{sns}} = \frac{\left(\frac{2}{25\text{ MHz} \times 2\pi}\right)^2}{75\text{ pF} + 225\text{ pF}} \approx 0.54\text{ uH} \quad (21)$$

さらに  $R_{sns}$  は  $L_{sec}$  と  $C_D$  によって求められます。

$$R_{sns} = \sqrt{\frac{L_{sec}}{C_D}} = \sqrt{\frac{0.54\text{ uH}}{75\text{ pF}}} \approx 84.9\Omega \quad (22)$$

パワー損失の  $P_{sns}$  は次式により求められます。

$$P_{sns} = \frac{C_{sns} \times V^2 \times f_S}{2} = \frac{225\text{ pF} \times (328\text{ V})^2 \times 50\text{ kHz}}{2} \approx 0.6\text{ W} \quad (23)$$

このアプリケーションノートでは、 $C_{sns}$  に  $330\text{ pF}$ 、 $R_{sns}$  に  $150\text{ }\Omega$  を使用します。

## 4.10. ライン過電圧保護 (LOVP) のための DC リンク電圧を決定する

### 13. Line Over Voltage Protection

|                                                              |         |

|--------------------------------------------------------------|---------|

| Target line over AC voltage                                  | 472 Vac |

| Maximum DC voltage at target line over AC voltage =          | 667.5 V |

| Line over voltage threshold voltage ( $V_{INH}$ )            | 2.00 V  |

| Selected upper side resistor ( $R_{high}$ )                  | 9.0 MΩ  |

| Recommended $V_{IN}$ pin lower side resistor ( $R_{low}$ ) = | 27.0 kΩ |

| Recommended minimum $V_{IN}$ pin filter capacitor =          | 1.2 nF  |

| Maximum power loss on $V_{IN}$ sense resistors =             | 46.9 mW |

図 34. ライン過電圧の決定

図 35. LOVP 回路

式 (24) によりローサイド抵抗を算出します。

$$R_{low} = \frac{V_{INH} \times R_{high}}{V_{DC} - V_{INH}} = \frac{2V \times 9M\Omega}{667.5V - 2V} \cong 27k\Omega \quad (24)$$

分圧抵抗の値は、必要に応じて調整可能です。低抵抗は、軽負荷状態で比較的大きな待機電力の消費につながります。このような状況を避けるため、数 MΩ の抵抗が推奨されます。安定動作のために、数 MΩ の抵抗には、数百 pF の容量のコンデンサー ( $C_{VIN}$ ) が  $V_{IN}$  端子と GND の間に必要となります。

## 4.11. フィードバック抵抗の決定

### 14. Design Feedback control loop & Determine OLP delay time

|                                      |         |

|--------------------------------------|---------|

| Voltage divider resistor ( $R_1$ )   | 33.0 kΩ |

| Voltage divider resistor ( $R_2$ ) = | 4.7 kΩ  |

図 36. フィードバック抵抗

図 37. 単出力のフィードバック回路

式 (25) によりローサイドフィードバック抵抗を算出します。

$$R_2 = \frac{R_1 \times 2.5V}{V_{O1} - 2.5V} = \frac{33k\Omega \times 2.5V}{20V - 2.5V} = 4.7k\Omega \quad (25)$$

ここで、KA431 の基準電圧は 2.5 V です。

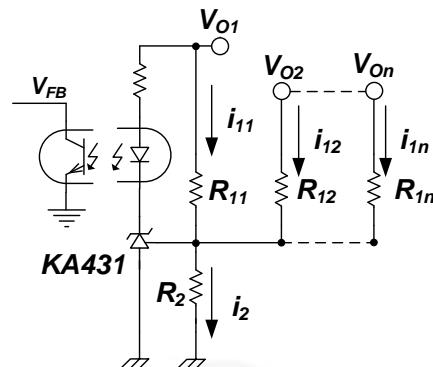

フィードバック回路に対する重み付け係数は、図 38 のように複数出力に適用できます。

図 38. 複数出力のフィードバック回路への重み付け

式 (26) により、フィードバック回路に重み付けするフィードバック抵抗を算出します。

$$\begin{aligned} i_2 &= i_{11} + i_{12} + \dots + i_{1n} \\ &= (W_{11} \times i_2) + (W_{12} \times i_2) + \dots + (W_{1n} \times i_2) \\ W_{11} + W_{12} + \dots + W_{1n} &= 1 \\ R_{1k} &= \frac{V_{on} - V_{ref}}{W_{1k} \times i_2}, \quad k = 1 \dots n. \end{aligned} \quad (26)$$

ここで、 $W_{1k}$  は出力の有効重み値です。

次の出力条件の場合

- $V_{O1} = 20$  V,  $W_1 = 0.1$

- $V_{O2} = 5$  V,  $W_2 = 0.9$

- $i_2 = 1$  mA

- $V_{ref} = 2.5$  V.

フィードバック抵抗は次式により求められます。

$$\begin{aligned} R_2 &= \frac{V_{ref}}{i_2} = \frac{2.5V}{1mA} = 2.5k\Omega \\ R_{11} &= \frac{V_{o1} - V_{ref}}{W_1 \times i_2} = \frac{20V - 2.5V}{0.1 \times 1mA} = 175k\Omega \\ R_{12} &= \frac{V_{o2} - V_{ref}}{W_2 \times i_2} = \frac{5V - 2.5V}{0.9 \times 1mA} = 2.8k\Omega \end{aligned} \quad (27)$$

## 4.12. 過負荷保護 (OLP) の遅延時間 ( $t_{OLP}$ ) を決定する

### 14. Design Feedback control loop & Determine OLP delay time

|                                         |          |

|-----------------------------------------|----------|

| Feedback pin capacitor ( $C_B$ ) =      | 68 nF    |

| Internal OLP delay time ( $t_{DELAY}$ ) | 100 ms   |

| OLP delay resistor ( $R_{DLY}$ )        | 4.7 MΩ   |

| Total OLP delay time =                  | 160.5 ms |

図 39. OLP の遅延時間

図 40. FB 用外部回路

過負荷保護 (OLP) の合計遅延時間は次式により算出できます。

$$\begin{aligned} t_{OLP} &= t_{DELAY} + t_{DLY} \\ &= 100ms - R_{DLY} \times C_{FB} \times \ln\left(1 - \frac{2}{V_{CC} - 2.4}\right) \\ &= 100ms - 4.7M\Omega \times 68nF \times \ln\left(1 - \frac{2V}{14V - 2.4V}\right) \\ &\approx 160.5ms \end{aligned} \quad (28)$$

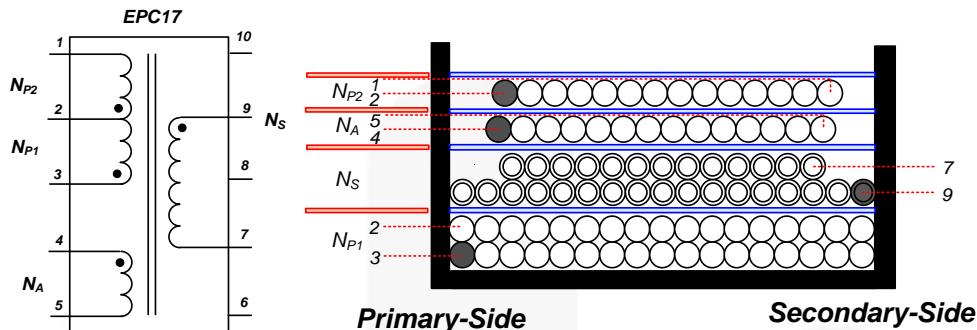

## 5. プリント基板レイアウト

高い周波数のスイッチング電流または電圧を扱う場合、プリント基板レイアウトの設計が非常に重要な問題となります。優れた PCB レイアウトは EMI を抑え、サージや ESD 試験から電源回路を保護します。

### 5.1. ガイドライン

優れた EMI 特性を確保し、ライン周波数のリップル成分を抑制するため、ブリッジ整流回路の出力は、最初にコンデンサー  $C_{DC}$  に接続し、次にスイッチング回路に接続します。図 41 を参照してください。

高周波の電流ループは、 $C_{DC}$  - トランス - ドレイン端子 - GND 端子 -  $C_{DC}$  で形成されます。この電流ループで囲まれる面積はできるだけ小さくしてください。パターンは短く（特に  $GND2 \rightarrow GND1$ ）、直線的に太くします。MOSFET のドレイン、RCD スナバに関連した高電圧がかかるパターンは、無用な干渉を防ぐためにコントロール回路から離してレイアウトします。

- $GND2$  で示されるコントロール回路のグランドを最初に接続し、次に他の回路に接続します。

- デカップリング効果を高めるため、 $C_a$  と  $C_{a1}$  はコントローラーの直近に配置してください。特にセラミックコンデンサー ( $C_{a1}$ ) は、 $V_{CC}$  端子と端子 1 (GND) の間に可能な限り近づけて配置する必要があります。推奨間隔は 3 mm 以下です。

以下に、それぞれ長所と短所を持つ推奨される 2 つのグランド接続を示します。

- $GND2 \rightarrow GND1$  : センス信号が共通インピーダンスによる影響を受けにくいという長所があります。

- ESD 放電経路は、トランス二次側から浮遊容量を介して最初に  $GND1$  に到達し、その後メイン電源に戻ると考えられます。コントロール回路が放電経路に入らないようにしてください。コモンモードチョークに先端放電パターンを設けることで、高周波インピーダンスを下げ、ESD 耐性を高める効果があります。

- 3 の位置に先端放電経路を設けて静電気エネルギーを迂回させます。図 41 に示すような放電経路が推奨されます。

- 一次側と二次側の間に Y コンデンサーを必要とする場合は、Y コンデンサーを  $C_{DC}$  の正極端子に接続してください。Y コンデンサーを一次側の GND に接続する場合は、 $C_{DC}$  の負極端子 ( $GND1$ ) に直接接続してください。Y コンデンサーに先端放電パターンを施すのも ESD 対策として有効です。ただし、2 つの先端部間の沿面距離は、安全上の理由から少なくとも 5 mm は離す必要があります。

図 41. レイアウトの検討

## 6. 典型的なアプリケーション回路

| アプリケーション | 出力電力  | 入力電圧範囲                 | 出力電圧／最大電流    |

|----------|-------|------------------------|--------------|

| E メータリング | 6.0 W | 85~460 V <sub>AC</sub> | 20 V / 0.3 A |

### 6.1. 特長

- 1 kV アバランシェ耐量を持つ SenseFET 内蔵

- 高精度固定動作周波数 : 50 kHz

- V<sub>CC</sub> は、バイアス巻線またはセルフバイアス回路のいずれかから供給可能です。

- 可聴雑音を最小化するソフトバーストモード動作

- 低 EMI のためのランダム周波数変動

- パルスバイパルス電流制限

- さまざまな保護機能 : 過負荷保護 (OLP)、過電圧保護 (OVP)、異常過電流保護 (AOCP)、ヒステリシスのある内部サーマルシャットダウン (TSD)。低電圧誤動作防止回路 (UVLO) とヒステリシスのあるライン過電圧保護 (LOVP)。

- 内蔵型内部スタートアップとソフトスタート回路

- すべての保護に対する安全なオートリストートモードのための固定 1.6 s の再起動時間

## 6.2. 回路図

図 42. 回路図

表 1. 6 W 評価ボードの部品表

| 項目 | 記号                                 | 製品名                  | 数量 | 概要                                   |

|----|------------------------------------|----------------------|----|--------------------------------------|

| 1  | IC101                              | FSL4110LRN           | 1  | 7DIP、フェアチャイルド                        |

| 2  | IC201                              | FOD817A              | 1  | 4DIP、フェアチャイルド                        |

| 3  | IC202                              | KA431LZ              | 1  | TO-92、フェアチャイルド                       |

| 4  | D1, D2, D3, D4, D101, D102         | S1M                  | 6  | 1000 V / 1 A 汎用ダイオード、SMA、フェアチャイルド    |

| 5  | D202                               | EGP30J               | 1  | 1000 V / 3 A ダイオード、DO-201AD、フェアチャイルド |

| 6  | F1                                 | SS-5-1 A             | 1  | 1 A ヒューズ                             |

| 7  | MOV                                | 510 V <sub>RMS</sub> | 1  | 510 V <sub>RMS</sub>                 |

| 8  | L101                               | 1 mH                 | 1  | フィルターインダクター、10 Φ                     |

| 9  | L102                               | 保留                   |    | 保留                                   |

| 10 | L202                               | 3.3 μH               | 1  | フィルターインダクター、8 Φ                      |

| 11 | T1                                 | Lm = 1.4 mH          | 1  | EPC17 コア                             |

| 12 | R101, R102, R103, R104, R106, R107 | 2 MΩ                 | 4  | SMD 抵抗 3216                          |

| 13 | RSTR                               | 100 kΩ               | 2  | SMD 抵抗 3216                          |

| 14 | R105                               | 3.9 MΩ               | 2  | SMD 抵抗 3216                          |

| 16 | R108, R109, R110                   | 3 MΩ                 | 3  | SMD 抵抗 3216                          |

| 17 | RVIN                               | 27 kΩ                | 1  | SMD 抵抗 3216 / 1%                     |

| 18 | R111                               | 150 kΩ               | 1  | 抵抗 1 W                               |

| 19 | R112, R114                         | 0 Ω                  | 2  | SMD 抵抗 3216                          |

| 20 | R113                               | 保留                   |    | 保留                                   |

| 21 | RDLY                               | 4.7 MΩ               | 1  | SMD 抵抗 2012 / 1%                     |

| 22 | R201                               | 150 Ω                | 1  | 抵抗 1 W                               |

| 23 | R202                               | 510 Ω                | 1  | SMD 抵抗 2012                          |

| 24 | R203                               | 3.3 kΩ               | 1  | SMD 抵抗 2012                          |

| 25 | R204                               | 20 kΩ                | 1  | SMD 抵抗 2012                          |

| 26 | R205                               | 33 kΩ                | 1  | SMD 抵抗 2012 / 1%                     |

| 27 | R206                               | 4.7 kΩ               | 1  | SMD 抵抗 2012 / 1%                     |

| 28 | C101, C102, C103, C104             | 22 μF / 400 V        | 4  | 電解コンデンサー、105°C                       |

| 29 | C105                               | 10 nF / 50 V         | 1  | SMD コンデンサー 2012                      |

| 30 | C106                               | 68 nF / 50 V         | 1  | SMD コンデンサー 2012                      |

| 31 | C107                               | 2.2 nF / 1 kV        | 1  | セラミックコンデンサー                          |

| 32 | C108                               | 100 nF / 50 V        | 1  | SMD コンデンサー 2012                      |

| 33 | C109                               | 22 μF / 50 V         | 1  | 電解コンデンサー、105°C                       |

| 34 | C201                               | 330 pF / 1 kV        | 1  | セラミックコンデンサー                          |

| 35 | C202, C203                         | 1000 μF / 35 V       | 2  | 電解コンデンサー、105°C                       |

| 36 | C204                               | 100 nF / 50 V        | 1  | SMD コンデンサー 2012                      |

| 37 | C205                               | 47 nF / 50 V         | 1  | SMD コンデンサー 2012                      |

| 38 | CY201                              | 2.2 nF               | 1  | Y コンデンサー                             |

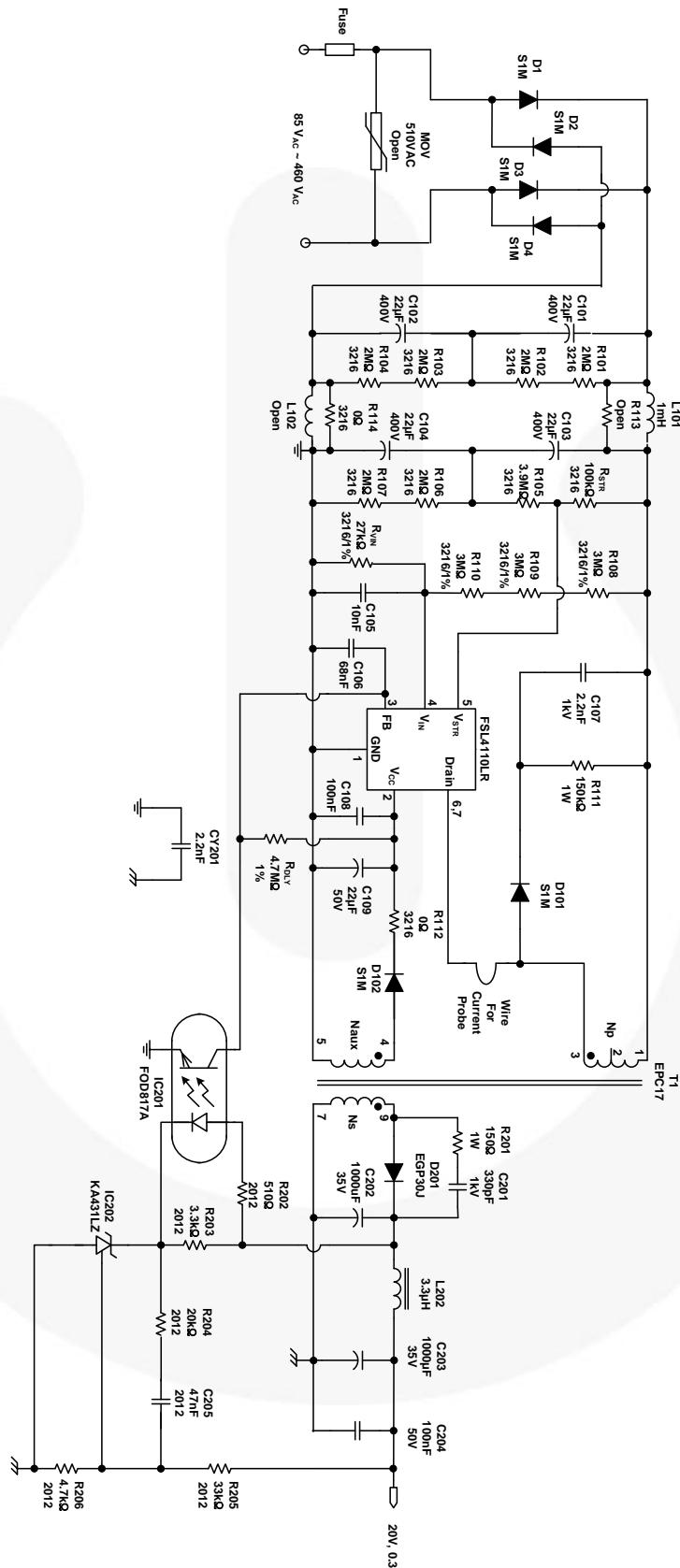

### 6.3. トランスの仕様

- コア : EPC17 (PC-40,  $A_e=22.8 \text{ mm}^2$ )

- Bobbin : 10 ピン

図 43. トランスの仕様

表 2. 卷線の仕様

|                                  | 端子 (S → F) | ワイヤー          | 巻数    | 巻線方法  |

|----------------------------------|------------|---------------|-------|-------|

| N <sub>P1</sub>                  | 3 → 2      | 0.2 φ×1       | 72 Ts | ソレノイド |

| 絶縁 : ポリエステルテープ 厚み = 0.025 mm、3 層 |            |               |       |       |

| N <sub>S</sub>                   | 9 → 7      | 0.2 φ×1 (TEX) | 27 Ts | ソレノイド |

| 絶縁 : ポリエステルテープ 厚み = 0.025 mm、3 層 |            |               |       |       |

| N <sub>A</sub>                   | 4 → 5      | 0.15 φ×1      | 20 Ts | ソレノイド |

| 絶縁 : ポリエステルテープ 厚み = 0.025 mm、3 層 |            |               |       |       |

| N <sub>P2</sub>                  | 2 → 1      | 0.2 φ×1       | 33 Ts | ソレノイド |

| 絶縁 : ポリエステルテープ 厚み = 0.025 mm、3 層 |            |               |       |       |

表 3. 電気特性

|         | ピン  | 仕様         | 備考          |

|---------|-----|------------|-------------|

| インダクタンス | 1-3 | 1.4 mH ±6% | 50 kHz, 1 V |

| リーケージ   | 1-3 | 20 μH 最大   | 他のすべての端子を短絡 |

## 6.4. 実験結果

表 4. 効率

|        | 85 V <sub>AC</sub> | 110 V <sub>AC</sub> | 230 V <sub>AC</sub> | 265 V <sub>AC</sub> | 350 V <sub>AC</sub> | 400 V <sub>AC</sub> | 460 V <sub>AC</sub> |

|--------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| 全負荷    | 83.97%             | 84.85%              | 83.71%              | 82.78%              | 80.29%              | 78.69%              | 76.60%              |

| 負荷 75% | 84.13%             | 84.82%              | 83.07%              | 82.20%              | 79.53%              | 77.61%              | 75.01%              |

| 負荷 50% | 84.20%             | 84.18%              | 80.34%              | 78.87%              | 74.59%              | 71.72%              | 68.13%              |

| 負荷 25% | 81.05%             | 80.71%              | 72.76%              | 70.25%              | 63.58%              | 59.52%              | 55.08%              |

表 5. 動作温度

|                 | 85 V <sub>AC</sub> | 460 V <sub>AC</sub> | 備考                |

|-----------------|--------------------|---------------------|-------------------|

| FSL4110LRN      | 42.0°C             | 48.4°C              | ボックス 2 (Box 2)    |

| トランス            | 47.0°C             | 51.5°C              | サークル 1 (Circle 1) |

| スナバ回路付き二次側ダイオード | 41.8°C             | 49.0°C              | ボックス 3 (Box 3)    |

## 6.5. 実験波形

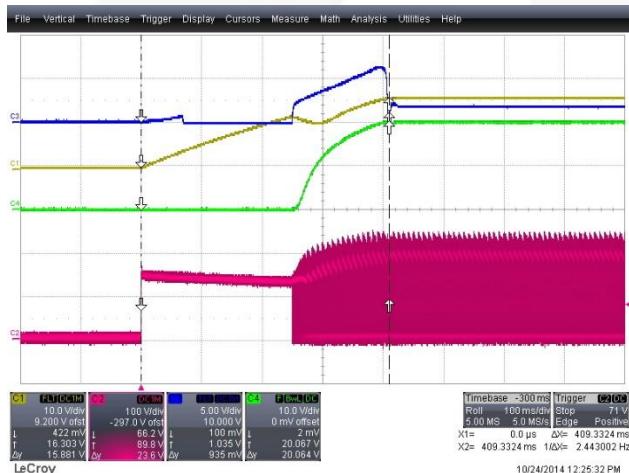

図 44. スタートアップ時間 = 409 ms、85 V<sub>AC</sub>、全負荷時、(CH1 : V<sub>CC</sub> (10 V/div)、CH2 : V<sub>DS</sub> (100 V/div)、CH3 : V<sub>FB</sub> (5V/div)、CH4 : V<sub>OUT</sub> (10 V/div)、時間 : 100 ms/div)

図 45. V<sub>DS</sub>=786 V、V<sub>DIODE</sub>=249 V、定常状態、全負荷時、460 V<sub>AC</sub> (CH1 : V<sub>DIODE</sub> (200 V/div)、CH2 : V<sub>DS</sub> (200 V/div)、時間 : 5 μs/div)

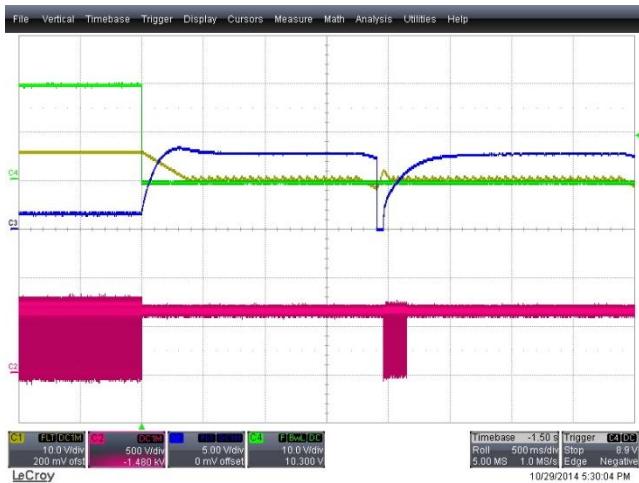

図 46. OLP トリガ、出力短絡 460 V<sub>AC</sub>、全負荷時、

(CH1 : V<sub>CC</sub> (10 V/div)、CH2 : V<sub>DS</sub> (500 V/div)、CH3 : V<sub>FB</sub>

(5 V/div)、CH4 : V<sub>OUT</sub> (10 V/div)、時間 : 500 ms/div)

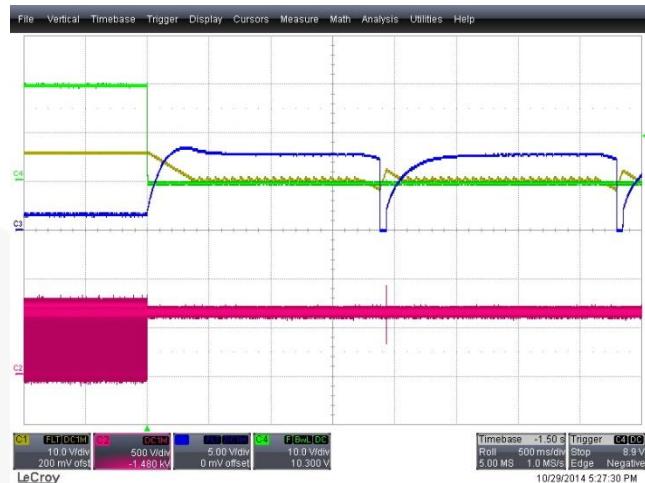

図 47. AOCP トリガ、出力短絡 460 V<sub>AC</sub>、全負荷時、

(CH1 : V<sub>CC</sub> (10 V/div)、CH2 : V<sub>DS</sub> (500 V/div)、CH3 : V<sub>FB</sub>

(5 V/div)、CH4 : V<sub>OUT</sub> (10 V/div)、時間 : 500 ms/div)

## 7. 参考文献

### FSL4110LR 製品情報

[AN-4137 —Design Guidelines for Offline Flyback Converters Using the FPS™](#)

[AN-4147 —Design Guideline for RCD Snubber of Flyback Converters](#)

#### 免責事項

フェアチャイルドセミコンダクターは、信頼性、機能、設計を向上させるために、更なる通告なしに、ここに記載したあらゆる製品に変更を加える権利を留保します。フェアチャイルドは、ここに記載した製品または回路の適用や使用から生じるいかなる責任も負わず、特許権に基づくライセンスや他者の権利を譲渡することもありません。

#### 生命維持の方針

フェアチャイルドの製品は、フェアチャイルドセミコンダクターコーポレーション社長の書面による明示的な承諾がない限り、生命維持装置または生命維持システム内の重要な部品に使用することは認められていません。

本規約内の定義：

1. 生命維持装置または生命維持システムとは、(a) 外科的に体内に埋め込まれて使用されることを意図したもの、(b) 生命を維持あるいは支持するもの、(c) ラベルに表示された使用法に従って適切に使用された場合にその不具合が使用者に重大な傷害をもたらすことが合理的に予想されるもの、を言います。

2. 重要な部品とは、生命維持装置または生命維持システム内のあらゆる部品を指し、これらの不具合が生命維持装置または生命維持システムの不具合の原因に、またはその安全性および効果に影響を及ぼす原因になるものと合理的に予想されるものを言います。

ON Semiconductor and  are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA

**Phone:** 303-675-2175 or 800-344-3860 Toll Free USA/Canada

**Fax:** 303-675-2176 or 800-344-3867 Toll Free USA/Canada

**Email:** [orderlit@onsemi.com](mailto:orderlit@onsemi.com)

**N. American Technical Support:** 800-282-9855 Toll Free

USA/Canada

**Europe, Middle East and Africa Technical Support:**

Phone: 421 33 790 2910

**Japan Customer Focus Center**

Phone: 81-3-5817-1050

**ON Semiconductor Website:** [www.onsemi.com](http://www.onsemi.com)

**Order Literature:** <http://www.onsemi.com/orderlit>

For additional information, please contact your local

Sales Representative