**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

# AN-5077 Design Considerations for High Power Module (HPM)

## Abstract

Fairchild's High Power Module (HPM) solution offers higher reliability, efficiency, and power density to improve performance and reduces size and weight compared to a discrete solution. It also provides simpler repair and maintenance and design. The market trend in industrial power systems; such as photo-voltaic inverters, welding machines, and uninterruptible power supplies; is rapidly moving toward the module approach. Fairchild's leading power semiconductor products in the market include 600 V / 650 V field-stop IGBTs, 650 V / 1200 V field-stop trench IGBTs, 600 V / 650 V super-junction MOSFETs and fast / soft recovery diodes. Fairchild has now launched the High Power Module (HPM) solution with leading power devices. This application note introduces HPM products and shows the differences between module vs. discrete solutions, describes considerations and guidance for PCB layout design, and explains how to design and use HPMs properly and efficiently.

### Introduction of HPM

The HPM "F-series" offers custom modules as well as standard modules, covering a full scope in the power, ranging up to hundreds of amperes with 600 V / 650 V / 1200 V devices. F-1 and F-2 cover under tens of kilowatts and will be extended to the larger package size for the higher power. Figure 1 shows the package dimensions.

#### Figure 1. Package Dimension of F1 & F2

#### **F-Series Key Features**

- High Integration and Compact Design

- Low Switching Loss

- Low Stray Inductances

- Optimized Thermal Performance

- Long Isolation Distances and Creepage

- Press-Fit Contact Technology

The HPM features provides superb reliability and high efficiency to systems and benefits system design through design-friendly layout, mounting with PressFIT terminal, fast solderless assembly, and the optimized system cost for the diverse topologies such as converters, inverters, and customized circuitry.

#### **Design Considerations**

- Parasitic Inductances

- Voltage / Current Spikes / Oscillations through Parasitic Inductance

- Route of PCB Patterns

- Kelvin Source / Emitter Gate Drive

- Location of Components

# **PCB Layout Guidance**

This section demonstrates the general guideline for Printed Circuit Board (PCB) layout by discussing considerations that affect the performance of HPM. The following sections detail how to optimize the design of PCB with HPM.

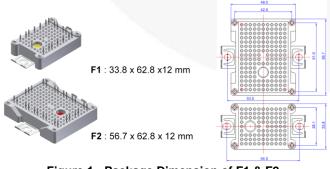

Figure 2. Double-Pulse Inductive Switching Circuit with Parasitic Inductance and Switching Behavior

#### **Influence of Parasitic Inductance**

Parasitic inductance in fast-switching applications is a major problem, causing over-voltage spikes and increasing switching turn-off losses. Figure 2 shows the double-pulse inductive switching circuit with parasitic inductances: L<sub>DS</sub>, L<sub>SS</sub>, and L<sub>G</sub> and the switching behavior. The switching characteristics can be measured using the circuit under any voltage and current stresses without self-heating as long as the double-pulse gate signals are given. The influence of each inductance through the circuit is visible, which also represents almost inductive switching circuits. The influence is well documented from prior research<sup>[1]-[2]</sup> and reaffirmed through simulated results from PSpice models.<sup>[3]</sup> The di<sub>D</sub>/dt drain-current slope is generated during switching transients and limited by L<sub>SS</sub> as a negative voltage source. There are voltage spikes and drops in parasitic inductances by the di/dt, such as:  $\Delta V_{DS1} = (L_{DS}+L_{SS}) * di_D/dt_1$ ,  $\Delta V_{GS1} = L_{SS} *$  $di_D/dt_1$ ,  $\Delta V_{GS2} = L_{SS} * di_D/dt_2$ ,  $\Delta V_{GS3} = L_{SS} * di_D/dt_3$ , and  $\Delta V_{DS3} = (L_{DS} + LSS) * di_D/dt_3.$

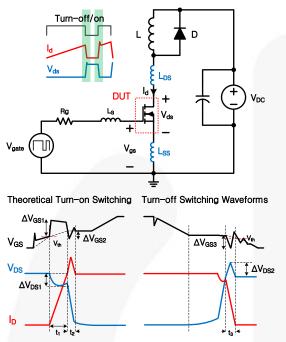

The simulation result in Figure 3 shows the effect of the drain inductance,  $L_{DS}$ , also called loop inductance. The inductance intrinsically resonates with the output capacitance of MOSFET / IGBT and diode junction capacitance when turning on and off. That oscillation inevitably affects the gate loop through Miller capacitance. Therefore, as  $L_{DS}$  increases, ringing in all  $V_{GS}$ ,  $V_{DS}$ , and  $I_D$  waveforms is introduced during the switching transients.

The overshoot in  $V_{DS}$  at turn-off is much more significant than in the gate drive loop, which can cause worse oscillation and stresses on the device over breakdown voltage. Though the DC-link voltage is only 400 V, the peak voltage at turn-off can reach up to 480 V with 60 nH loop inductance in the simulated conditions, while only 420 V with 1 nH even with the same di<sub>D</sub>/dt. The drain inductance comes from the long and narrow PCB route from DC-link capacitor's positive pin-to-pin of MOSFET / IGBT's drain / collector and even from the internal parasitic of package, such as long lead or substrate.

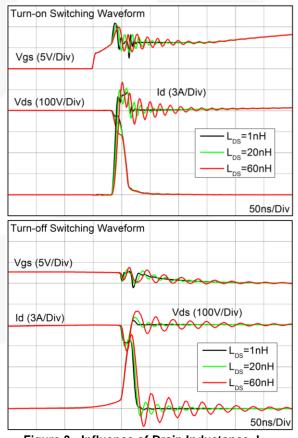

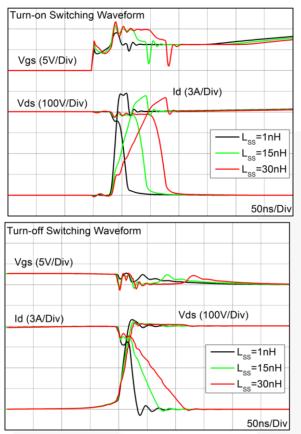

The simulated turn-on and turn-off switching waveforms in Figure 4 clearly show the influence of the common source inductance, L<sub>SS</sub>. L<sub>SS</sub> serves as a negative feedback from the switching loop into the gate loop. During the rise and fall periods of I<sub>D</sub>, the voltage across the inductance,  $V_{LSS}=L_{SS}*di_D/dt1$ , reduces the gate voltage. This decreases the charging current for gate charge, slowing down the drain current. The increase of L<sub>SS</sub> decreases the di<sub>D</sub>/dt due to the lower negative V<sub>LSS</sub>. Although that increase can suppress the current ringing into the device and reduce the voltage across the parasitic inductances due to the lower di<sub>D</sub>/dt, it significantly increases the switching energy loss at turn-on and turn-off. The inductance results from the parasitic on the route from the source / emitter pin of MOSFET / IGBT to the DC-link capacitor's negative pin and its package lead and internal bonding wires to connect the chip's active source / emitter area to the package lead pin.

Figure 3. Influence of Drain Inductance, L<sub>DS</sub>

Figure 4. Influence of Common Source Inductance, Lss

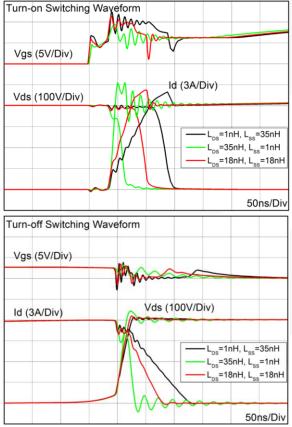

Figure 5. Influence L<sub>DS</sub> and L<sub>SS</sub>

The ringing is caused by  $L_{DS}$ , which can be suppressed by  $L_{SS}$  because of its negative feedback effect to limit di<sub>D</sub>/dt slope. The simulation result in Figure 5 demonstrates that voltage overshoot is determined by both the total parasitic inductance and the magnitude of common-source inductance. For example, the voltage overshoot at turn-off is reduced with an increase of common-source inductance by decreasing di<sub>D</sub>/dt slope while keeping a constant total inductance. However, the price is much higher switching loss. Electromagnetic Interference (EMI) problems caused by overshoot and oscillation in parasitic inductances can be removed by increasing the turn-off gate resistor that limits the charging and discharging gate current, having the same effect as an increase in  $L_{SS}$ .

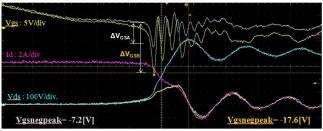

Since the common-source inductance works as dependent source on di<sub>D</sub>/dt during the switching transient state; in this period of di<sub>D</sub>/dt, the equivalent circuit in the gate drive path can be expressed as R-L-C series resonance circuit with the dependent source of  $V_{LSS}$ .<sup>[4]</sup> Two different values of gate inductance are compared in clamped inductive load switching circuit in Figure 6. A circuit with low value for  $L_G$ (white lines) has lower peak gate negative voltage than the circuit with higher L<sub>G</sub> (color lines). To achieve optimized gate waveform, it is necessary to reduce gate inductance, L<sub>G</sub>, as well as common-source inductance, L<sub>SS</sub>. The gate inductance can come from long and narrow PCB route from driver to gate pin, parasitic components of drive IC, gate resistor, internal bonding wires, and long lead length. The PCB designer should place the gate driver as close electrically as possible to minimize the potential resonance from the gate loop inductance and avoid parallel PCB pattern that create parasitic capacitance between the positive and negative rails.

The influence of inductances  $L_{DS}$ ,  $L_{SS}$ , and  $L_G$  can come from components' parasitic and PCB routes. Before design and layout with HPM, the difference between discrete and module must be understood. The components' parasitic inductance; such as bonding wire, copper substrate, lead pin, resistors, and capacitor stray inductance must be managed by considering the difference and stray, then reducing the parasitic inductance of the PCB pattern caused by the long and narrow paths and the types of route (discussed in the next section).

Figure 6. Influence of Gate Stray Inductance

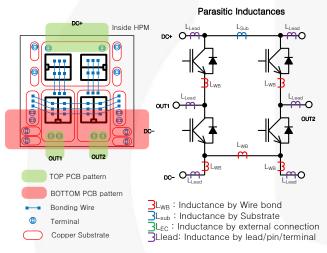

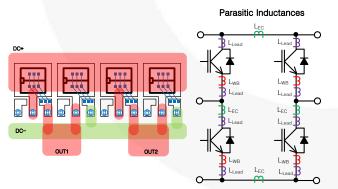

#### HPM vs. Discrete — Reducing Inductance

Figure 7 and Figure 8 show parasitic inductances in fullbridge configuration with discrete devices and HPM. L<sub>WB</sub> is parasitic inductance by wire bonding, L<sub>EC</sub> is by external connection like PCB pattern,  $L_{\text{LEAD}}$  is by leads / pins / terminals, and L<sub>SUB</sub> is substrate's parasitic inductance. Other components, like contact resistors and stray capacitances, are eliminated to focus on the inductance. The discrete solution has more parasitic inductances than HPM because the inevitable external connection from pin to pin through the PCB pattern and additional terminals to connect each device. Therefore, with the same gate resistance and devices, HPM solution can provide the higher di/dt, dv/dt by lower common source / emitter inductance and less oscillation due to lower drain / collector inductance than discrete solution. HPM offers optimized switching performance over discrete solutions regarding the components' parasitic inductance. The next effort should be to reduce PCB pattern strays of route to HPM.

Figure 7. HPM Full-Bridge, Parasitic Inductance

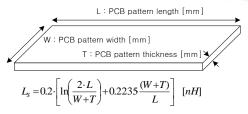

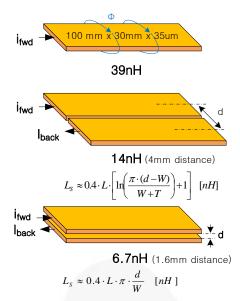

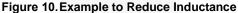

The PCB pattern's parasitic self inductance can be defined as Figure  $9^{[5]}$ , which increases with the longer path, narrower width, and thinner thickness. It also depends on the type of the route, as shown in Figure  $10^{[6]}$ . From the equation, a flat conductor of the first example has a self inductance of 39 nH by PCB pattern of 100 mm length, 30 mm width, in case of 1 ounce (0.0035 mm). The two flat side-by-side patterns with 4 mm distance of the second example, considering isolation distance over 400 V on a single layer, show a return inductance of 14 nH to cancel the magnetic field; partly by bringing the return current close to the forward current. The third example of two flat patterns in parallel on a double-layer layout, can be reduced to 6.7 nH with 1.6 mm distance.

To reduce loop inductance from DC-link capacitors to HPM's power pins, the third example would be the best layout with multilayer and second example is also suitable for single-layer because the parasitic capacitance is not a large problem in a drain-source loop path. Regarding the gate inductance, these examples might increase the capacitances, causing more oscillations. It is therefore important that gate driver be placed as close electrically as possible to remove inductance, then avoid the route like these examples for the lower capacitance. The vertical route of gate line against drain / collector and source / emitter also can reduce the capacitances.<sup>[7]</sup>

#### AN-5077

#### **Effectiveness of Kelvin Source/Emitter**

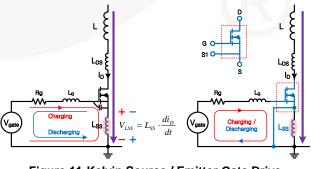

HPM provides an additional pin for a Kelvin source / emitter to drive the gate. In this section, the effectiveness of the Kelvin, improving switching performance by removing oscillation by high di/dt, is discussed.

Figure 11 indicates the effectiveness of Kelvin source / emitter drive on the gate-source drive path compared with a conventional three-pin gate drive. When turning on and off, the stray inductance counteracts as a dependent source by  $di_D/dt$  and the voltage across  $L_{SS}$ ,  $V_{LSS}=L_{SS}*di_D/dt$ , becomes negative feedback to disturb charging and discharging current into gate-source, decreasing  $di_D/dt$ . The Kelvin source drive can remove this disturbance by separating the gate-drive current from the high-drain current. It can increase the di/dt slope with the same resistor and with less gate oscillation compared to the three-pin drive.

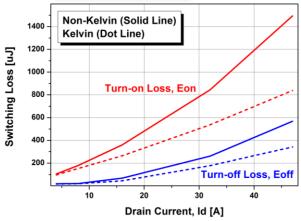

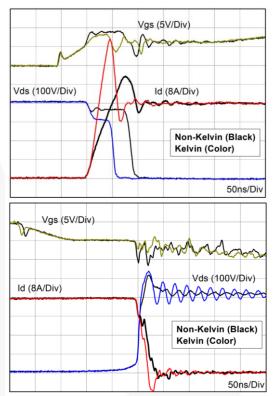

Figure 12 shows the switching loss improvement of 77 m $\Omega$ SuperFET® 2 FRFET® inside HPM at V<sub>CE</sub>=400 V, T<sub>C</sub>=25°C, and R<sub>g</sub>=10  $\Omega$  with Kelvin source drive compared with non-Kelvin. The solid line is non-Kelvin and the dotted line is Kelvin drive. With the advantage, it can reduce the switching performance by up to 44% E<sub>ON</sub> as well as 40% E<sub>OFF</sub> at the rated current. In the measured switching waveforms of Figure 13, it is clear that it increases di<sub>D</sub>/dt with Kelvin drive, so can reduce switching energy losses. Compared with non-Kelvin, 3 A-to-30 A di/dt slope is increased from 627 A/µs to 1430 A/µs for E<sub>ON</sub>, 25 A-to-5 A slope from 804 A/µs to 1170 A/µs, while slightly increasing 100 V-to-300 V dv/dt slope from 54.4 V/ns to 57.9 V/ns at turn-off. It shows that the faster di/dt is the more effective.

The most important benefit of Kelvin drive is the ability to increase di/dt with less gate oscillation compared with threepin. Increasing switching speed can normally be achieved by reducing the gate resistor, but that can result in higher gate oscillation due to increased gate current. This means that Kelvin drive should be mandatory for the faster switching devices, especially for a module with lower parasitic inductance than discrete devices. In low-frequency switching with low di/dt line-frequency, it is optional.

Figure 12. Switching Loss Improvement by Kelvin

Figure 13. Switching Waveform Comparison for Kevin

In this section, the advantage of Kelvin drive is discussed. The additional pin provides better switching performance with the less gate oscillation than three-pin driving. As shown in switching waveforms, di/dt and dv/dt are increased, which means the PCB designer must consider EMI and reduce parasitic elements, such as loop / drain inductance and capacitance of gate-to-drain / source.

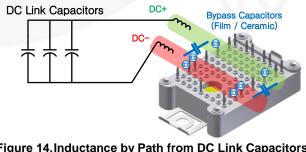

#### **Location of Bypass Capacitor**

The location of the DC-link capacitors is important because a long path from DC-link capacitors to the DC+ and DCterminals of the HPM results in the high parasitic inductance, as shown in Figure 14, even with the welldesigned PCB layout. The bypass capacitor is required to reduce the disadvantage of the long path, which can't be avoided. Figure 15 shows the influence by the location of bypass capacitors. The color waveforms with the bypass capacitor closest to module's DC input pin has less oscillation in turn-on/off currents, turn-off voltage, and gate waveforms. Voltage drop during turned-on is also reduced compared to the black lines with the long path.

Figure 14.Inductance by Path from DC Link Capacitors to Terminals

Figure 15. Effectiveness of Bypass Capacitor

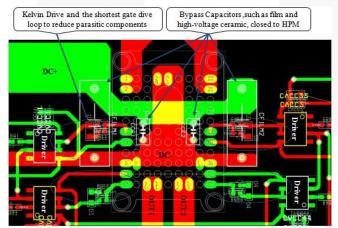

Figure 16. Example of PCB Design

Figure 16 shows an example of PCB design with HPM. Bypass capacitors of film and high-voltage ceramic capacitors are placed close to the module to remove the drawback of the long path from the DC-link capacitor. The gate drive loop is separated from the main drain current path using Kelvin source pins for improved switching. It is also considered the shortest path for lower inductance to place the driver IC as close as possible and routed into a both-side pattern to reduce capacitances.

# **Summary and Conclusion**

Considerations for PCB design, investigation of the influences of parasitic inductances and methods to reduce it, and the benefits of Kelvin drive have been discussed.

#### Summary of HPM Design Considerations

- Drain (loop) inductance: larger L<sub>DS</sub> causes oscillations in switching voltage and current, which can be minimized with the proposed examples.

- Common source inductance, which is related to di<sub>D</sub>/dt: smaller inductance increases speed, but can cause oscillation. HPM provides an optimized pattern compared to discrete configuration.

- Gate loop inductance, which resonates with gate junction capacitance and stray capacitance, resulting in gate oscillation: the placement of the drive IC close to HPM, the shortest path, and the route to avoid parasitic capacitance are recommended.

- Kelvin drive: can improve switching performance, providing higher di<sub>D</sub>/dt even with the less gate oscillation, which removes the drawback of commonsource inductance.

- Bypass capacitor: close to the module can remove the drawback of long path from DC-link capacitors to power terminals of module.

## References

- [1] Zheng Chen, Dushan Boroyevich and Rolando Burgos, "Experimental Parametric Study of the Parasitic Inductance Influence on MOSFET Switching Characteristics," The 2010 International Power Electronics Conference.

- [2] Y. Xia, H. Shah, T. P. Chow and R. J. Gutmann, "Analytical Modeling and Experimental Evaluation of Interconnect Parasitic Inductance on MOSFET Switching Characteristics," in Proc. IEEE APEC 2004, vol. 1, pp. 516-521.

- [3] PSpice Models of Super Junction MOSFETs on Fairchild semiconductor website, http://www.fairchildsemi.com/models/modelDetails?modelType=PSPICE#resultDiv

- [4] Dongkook Son, Wonsuk Choi, "New generation Super-Junction MOSFET in PQFN88 for High Efficiency and Low Profile Power Systems," The 2012 PCIM-Aisa.

- [5] "PCB Design Guidance for SPM," AN-9760, Fairchild Semiconductor.

- [6] "Parasitic effects in Power Electronics", PEMC Power Electronics and EMC

- [7] "New Generation Super-Junction MOSFETs, SuperFET II and SuperFET II Easy Driver MOSFETs for high Efficiency and Lower Switching Noise," AN-5232, Fairchild Semiconductor.

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC