Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

# AN-6602 Low Noise JFET – The Noise Problem Solver

## Introduction

The most versatile low noise active device available to the designer today is the Junction Field-Effect Transistor (JFET). JFETs are virtually free of the problems which have plagued bipolar transistors—limited bandwidth, popcorn noise, a complex design procedure to optimize noise performance. In addition, JFETs offer low distortion and very high dynamic range.

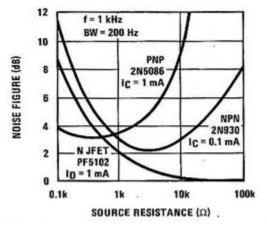

Most designers think of JFETs for very high source impedances. However, modern devices offer the designer performance improvements over bipolar transistors in Noise Figure (NF) for all but lowest impedance ( $<5000\Omega$ ) sources and even then may provide improved performance If popcorn noise, bandwidth or circuit component noise is a consideration (see Figure 1).

Therefore, the purpose of this article is to review low noise design procedures and indicate the simplicity of designing high performance low noise amplifiers with low cost JFETs.

Figure 1. Bipolar and JFET Transistor Noise Comparison

### **Review of Basics**

Before guidelines are established for designing low noise JFET amplifiers, a method of noise characterization must be chosen. Designers are confronted with a multitude of different noise parameters such as Noise Figure (NF), noise voltage and current densities, noise temperature, noise resistance, etc. Designers are primarily concerned with signal to noise (S/N) ratios preferring noise voltage, ( $e_n$ ) and current ( $i_n$ ) density.

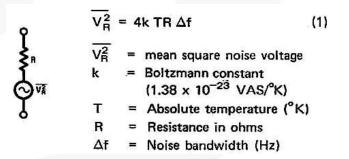

Noise generally manifests itself in three forms: thermal noise, shot noise and flicker or "1/f" noise. Thermal noise arises from thermal agitation of electrons in a conductor and is given by Nyquist's relation:

The noise of a resistor may be represented as a spectral density (V<sup>2</sup>/Hz) or more commonly in uV/ $\sqrt{N}$  Hz or nV/ $\sqrt{V}$  Hz and is given by:

$$e_{nR} = (\overline{V_R^2} / \Delta f)^{1/2}$$

(2)

It is sometimes more convenient to represent thermal noise as noise current instead of a noise voltage. One needs only to consider the Norton equivalent yielding a noise current density.

The second basic form of noise, shot noise, is due to the randomness of current flow (discrete charge particles) in semiconductor P-N junctions.

$$\vec{i}^2 = 2 q I_{DC} \Delta f$$

(4)

$\vec{i}^2 = Mean square noise current$

$q = Charge of an electron (1.6 × 10-19 AC)$

q = Charge of an electron (1.6 x 10<sup>-19</sup> AS)

$I_{DC}$  = dc current flowing through the junction (A)

$\Delta f = Noise bandwidth (Hz)$

As with thermal noise, shot noise may be represented as a current density (A $^2/Hz)$  or pA/ $\!\sqrt{Hz}.$

$$i_n = (\overline{i^2}/\Delta f)^{1/2}$$

(5)

It should be noted that both thermal noise and shot noise are "white" noise sources, i.e. frequency independent.

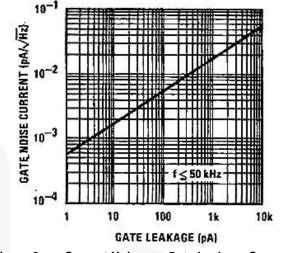

Figure 3. Current Noise vs. Gate Leakage Current

The third basic noise source confronting designers is flicker or "1/f" noise whose density is roughly inversely proportional to frequency starting at about 1 kHz in both JFETs and bipolar transistors and increasing as frequency is decreased. Through careful processing, flicker noise in JFETs has been reduced to levels nearly insignificant to the designer. Flicker noise in JFETs is primarily a noise voltage and is source independent. Flicker noise in bipolar transistors is a function of base and leakage current increasing with increased source impedance or operating currents.

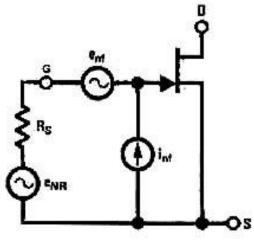

A simple noise model of a JFET or any amplifying device may be constructed using a thermal and shot noise source which would adequately describe its noise performance allowing signal to noise ratios to be calculated directly.

Figure 4. Simple JFET Noise Model

2

The input noise per unit bandwidth at some frequency may be calculated from the mean square sum of the noise sources (assuming the JFET noise sources are uncorrelated or independent of one another).

$$e_{nt}^2 = e_{nR}^2 + e_{nf}^2 + i_{nf}^2 R_s^2$$

(6)

The total noise in the same bandwidth  $\Delta f$ , where the noise sources are independent of frequency, is simply:

$$V_{\text{NOISE}} = (e_{\text{nt}}^2 \ \Delta f)^{1/2}$$

(7)

Practically, noise sources are not frequency independent except resistor noise with no dc bias. The total input noise for the non-ideal case may be calculated by breaking the spectrum up into several small bands and calculating the noise in each band where the noise sources are nearly frequency independent. The total Input noise would then be the RMS sum of the noise in each of the bands N1... Nn.

$$V_{\text{NOISE}} = (V_{\text{N1}}^2 + V_{\text{N2}}^2 + \dots + V_{\text{Nn}}^2)^{1/2}$$

(8)

### THE DESIGN PROCESS

The final circuit configuration and suitable JFET will be determined by the external circuit constraints.

- 1) Minimum signal to noise ratio (maximum amplifier noise)

- 2) Type and magnitude of source impedance (resistive or reactive)

- 3) Amplifier input impedance requirements

- 4) Bandwidth and maximum frequency of interest

- 5) Maximum operating temperature

- 6) Stage gain

- 7) Power supply voltage and current limitations

- 8) Circuit configuration, single or dual device

The design procedure is dependent on the type of source and each case must be considered separately. Resistive sources will be considered first because they are the least restrictive for the preamplifier.

### **Resistive Sources**

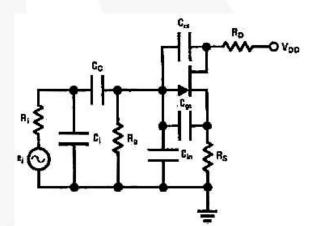

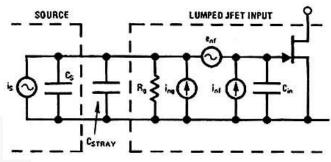

Preamplifiers for resistive sources are typically voltage amplifiers requiring a fixed input resistance and capacitance consistent with the maximum frequency of interest and source resistance. In most cases a resistor of the desired value connected between the gate and ground will satisfy the input resistance requirement leaving the maximum input capacitance as the major concern.

The maximum amplifier input capacitance is a function of the JFET source resistor, input resistance, source capacitance and maximum frequency. The maximum allowable input capacitance will be used In eliminating unsuitable JFET geometrics and optimizing, the circuit configuration. Sometimes the JFET geometry (or type) with the lowest noise may also have an input capacitance that makes it unsuitable. The JFET input capacitance should be considered before noise in high source resistance, wideband amplifier designs.

$$C_{in} \cong C_{rs} \left( 1 + \frac{gm R_D}{1 + gm R_s} \right) + \frac{C_{gs}^*}{1 + gm R_s}$$

(9)

\*C\_{rs} = C\_{is} - C\_{rs}

Figure 5. A Typical Resistive Source JFET Amplifier

If low input capacitance is required, a cascade configuration minimizes input capacitance and still allows high gain within a device type. The cascade configuration can also be used to reduce the voltage across a device, reducing device heating (for high current operation) and gate leakage currents when source impedances are very high.

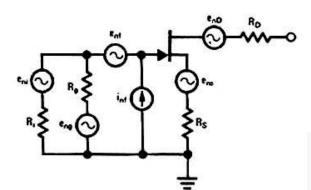

Once the basic circuit configuration has been decided upon or dictated by gain, bandwidth and power supply limitations, the final JFET selection will be on noise. Redrawing the amplifier in Figure 4 with all of the noise sources, the total amplifier noise per unit bandwidth can be found.

Figure 6. A Typical Resistive Source JFET Amplifier with Noise Sources

$$e_{nt} = \left[ e_{nig}^2 + e_{nf}^2 + e_{ns}^2 + \frac{e_{nD}^2}{A_V^2} + i_n^2 (R_i / / R_g)^2 \right]^{1/2} (10)$$

where:

$$e_{nig}^2$$

= The noise of the parallel connection of  $R_i$  and  $R_g$

$\frac{e_{nD}^2}{A_V^2} = \text{The noise at the drain (thermal noise of the load plus the second stage noise)}$  $i_n^2 (R_i //R_g)^2 = \text{The current noise contribution of the}$

When the amplifier is operated at room temperature and moderate drain voltages, the current noise term is usually negligible with source resistances as high as 10 M $\Omega$ . Depending on the voltage gain of the stage, the drain circuit noise may be negligible, simplifying the input noise expression.

JFET

$$e_{nt} = (e_{nig}^2 + e_{nf}^2 + e_{ns}^2)^{1/2}$$

(11)

The final JFET selection will be based on the noise requirements from the maximum allowable noise  $V_{max}$ .

$$V_{MAX} = (e_{nf}^2 + e_{ns}^2)^{1/2}$$

(12)

Depending on  $V_{max}$  and  $e_{nf}^2$ , the source resistor may have to be bypassed to ground to eliminate noise of the bias resistor.

#### **Capacitive Sources**

Preamplifiers for capacitive sources are primarily current amplifiers requiring very high input resistance and controlled input capacitance to match the source capacitance.

Figure 7. JFET Amplifier with an Inductive Source

The source capacitance should equal the sum of the preamplifier input capacitance and the stray capacitance for maximum frequency response and power transfer from the signal source. Assuming the gate resistor,  $R_{g}$ , is so large as to not load the capacitive source, the input noise voltage is:

$$e_{nt} \approx \left[ e_{nf}^{2} + (i_{nf}^{2} + i_{ng}^{2}) \left( \frac{R_{g}^{2}}{(1 + \omega^{2}R_{g}^{2}C^{2})} \right) \right]^{1/2}$$

(13)

where  $C = C_{S} + C_{in}$

with an input signal of

$$e_{s} \cong i_{s} \left( \frac{R_{g}^{2}}{1 + \omega^{2} R_{g}^{2} C^{2}} \right)^{1/2}$$

(14)

When the source and input capacitance are matched, the final JFET geometry will be selected on two criteria: the noise voltage,  $e_n$ , and the current noise from the gate leakage,  $I_{G(ON)}$  to optimize the signal to noise ratio. As in the resistive source case, the circuit configuration and JFET selection is an iterative process using all of the external circuit constraints, device parameters and limitations.

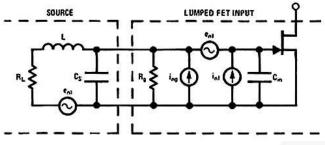

#### **Inductive Sources**

Amplifiers designed for inductive sources (including transformers) require fixed input resistances (as in the resistive source case) and controlled input capacitance (as in the capacitive source case). The input noise per unit bandwidth will rise with increasing frequency to a maximum value at resonance of the inductive source and the input capacitance or when the shunt resistance of the inductor is larger than the input resistance of the amplifier.

Figure 8. JFET Preamplifier with Capacitive Source

The inductive source amplifier is the most difficult to analyze due to the complex input impedance. The input noise per unit bandwidth is given by:

$$e_{nt}^{2} = e_{nf}^{2} + (i_{nf}^{2}) (|Z_{in}|^{2}) + 4 kT (Re (Z_{in}))$$

(15)

where  $Z = X_{CIN} //R_{g}$

and  $Z_{in} = Z //(Z_{L} + R_{L})$

Usually the current noise of the JFET is negligible, simplifying the expression a little, but not much. The optimization process for inductive sources is very complex and it will require the spectrum to be broken up into several small bands to arrive at a final design. Generally, a JFET with a minimum noise voltage will be the proper choice.

Transformers may be used with JFET amplifiers to minimize noise with very low source impedances. Transformers have both drawbacks and advantages and both must be examined before a transformer design is chosen. Poor frequency response, susceptibility to mechanical and magnetic pickup and thermal noise head the list of disadvantages to be weighed against two very important advantages. First, the noise voltage is transformed by the turns ratio N; second, the resistance is transformed by N<sup>2</sup>. These can be used to advantage by matching very low values of source resistance to a relatively noisy amplifier and still maintaining a good signal to noise ratio, i.e., the total noise at the source assuming an ideal transformer is

$$e_{nt}^2 = e_{nRs}^2 + \frac{e_{nAmp}^2}{N^2}$$

(16)

Low noise amplifier design concepts have been introduced for the three basic types of sources. Basic parameters ( $C_{in}$ ,  $e_n$ , gm) were discussed that affect both circuit configuration and JFET type. There is no universal low noise JFET or circuit configuration that solves all problems. Each low

noise amplifier design is different and must be considered within its own frame-work of performance requirements.

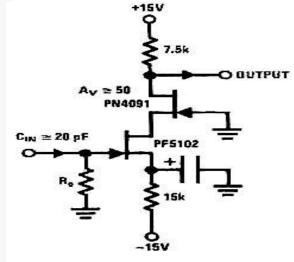

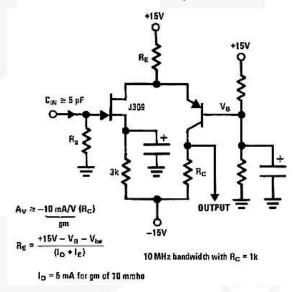

# SOME PRACTICAL LOW NOISE JET INPUT CIRCUITS

Usable Bandwidth 1 MHz

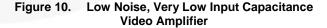

Figure 9. Wide Band, Low Input Capacitance, Very Low Noise Preamplifier

# **APPENDIX A**

## NOISE PARAMETER CONVERSION

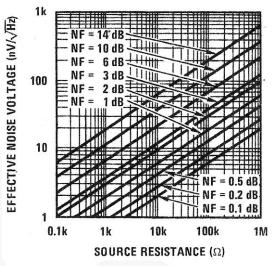

## Noise Figure (NF) to an Effective en

It is more convenient to present noise data for bipolar transistors in the form of contours of constant noise figure at a fixed frequency or plots of noise figure versus frequency at a fixed source resistance due to large values of noise current (in). Noise figure must be converted to an effective noise voltage (enE) for comparisons to be made between a BJT and a JFET or for signal to raise ratio calculations.

By definition:

$$NF = 10 \log \frac{\text{Total Output Noise Power}}{\text{Output Noise Power of the Source}}$$

(A1)

From equations 1 and 2, one finds the source noise power to be

Source Noise Power =

$$\frac{e_{nR}^2 \Delta f}{R_s}$$

(A2)

for some resistance Rs.

Referring to Figure 4, the total output noise power at the input of the amplifier would be:

Total Output Noise Power =

$$\frac{e_{nR}^2 \Delta f}{R_S} + \frac{e_{nf}^2 \Delta f}{R_S} + \frac{e_{nf}^2 \Delta f}{R_S}$$

(A3)

The noise figure (NF) can now be expressed in terms of the noise source generators, enR, enf and inf allowing. an expression to convert noise figure (NF) to an effective noise voltage (enE).

NF = 10 log

$$\left(1 + \frac{e_{nf}^2 + i_{nf}^2 R_S^2}{e_{nR}^2}\right)$$

(A4)

Yielding:

$$e_{nf}^2 + i_{nf}^2 R_s^2 = e_{nE}^2 = (10^{NF/10} - 1) e_{nR}^2$$

(A5)

Figure 11. Effective Noise Voltage (**e**<sub>nE</sub>) vs Noise Figure and Source Resistance (R<sub>s</sub>).

### **Noise Resistance**

The effective noise voltage density (en) and noise current density (in) are found directly by referring to Figure 1, and reading the values for the corresponding resistances.

$$e_{nR} = (4 \text{ KTR})^{1/2}$$

(A6)

$$i_{nR} = \left(\frac{4}{R}\right)$$

(A7)

## APPENDIX B JFET Current Noise

At low frequencies the current noise and voltage noise sources are uncorrelated in JFETs with the current noise being pure shot noise due to gate leakage currents. As frequency is increased, the current noise also increases starting at frequencies as low as 50 kHz in some high capacitance device types.

It has been suggested and experimentally verified that the noise current at high frequencies is due to increased gate input conductance.

$$i_n^2 = 4 \text{ KT} \left[ \text{Re} (Y_{11}) \right]^{-1}$$

(B1)

Re (Y11) is available on high frequency JFET data sheet as the real portion of the common source input admittance parameters. In effect the channel noise is coupling to the gate circuit through the source-gate and drain gate capacitances. Hence low capacitance devices exhibit lower values of noise current at high frequencies than do high capacitance devices.

## REFERENCES

- [1] A. Van der Ziel, "Noise," Prentice-Hall, 1964.

- [2] Richard S.C. Cobbold, "Theory and Applications of Field-Effect Transistors," John Wiley & Sons, 1970.

- [3] C.D. Motchenbacher and F.C. Fitchen, "Low Noise Electronic Design," John Wiley & Sons, 1973.

Author: John Maxwell, January 1976, Note 151

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC