Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

# **AN-9760** PCB Design Guidance for SPM<sup>®</sup>

## Introduction

Inverter system boards are becoming more compact and complex while requiring greater power density. This challenge can be met by adopting a Fairchild Smart Power Module, or SPM<sup>®</sup>. PCB layout design is very crucial in improving reliability, performance, and manufacturability while minimizing noise.

This application note describes several considerations and guidelines for PCB layout design.

# Considerations

- Parasitic Inductance, Resistance, and Capacitance

- Voltage Spikes from di/dt through the Parasitic Inductance

- Route of Power Ground, Signal Ground Layout

- Placement of Passive Components

## **General PCB Guidance**

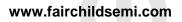

Figure 1 shows the overall guidance for PCB layout design, labeled from number 1 to 12 in order of importance.

Figure 1. Overall PCB Layout

#### Impact of Stray Inductance

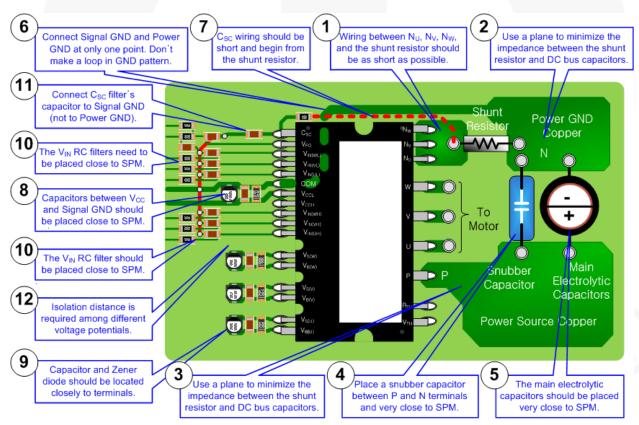

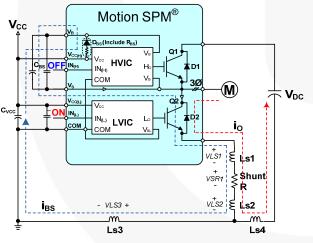

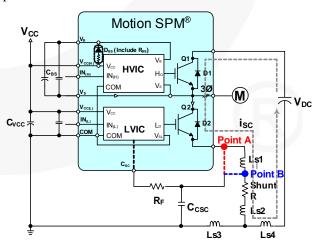

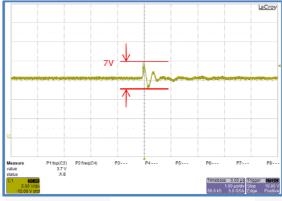

High switching noise may cause a failure in an inverter system. Whenever the IGBT turns on and off, surge voltage is induced due to stray inductance of main current paths on the board. Figure 2 and Figure 3 include Ls1 and Ls2, which is stray inductance in PCB layout. High di/dt occurs at transient periods of the IGBT's turning on and off. This di/dt is induced by the voltage VLS1 and VLS2. It is important to make the traces as short as possible to minimize parasitic inductance.

Figure 3. Bootstrap Capacitor Charging Path

Figure 2 shows low-side gate current ( $i_{GL}$ ) path through the gate to the emitter of IGBT Q2 and LVIC and  $V_{CC}$  to  $L_O$  when the low-side input signal is on. The low-side IGBT gate charging path includes parasitic inductances and a shunt resistor because LVIC  $V_{SL}$  is not connected to the emitter of Q2.

Figure 3 is regarding bootstrap current path  $(i_{BS})$  through the collector to the emitter of IGBT Q2 and  $V_{CC}$ , and  $V_B$  to  $V_S$  when Q2 or D2 is on. This bootstrap capacitor  $(C_{BS})$  charging current path also includes parasitic inductances and the shunt resistor.

Whenever  $i_0$  changes rapidly, voltages induced by Ldi/dt influence the voltage from the IGBT emitter to COM of the IC. Therefore, the IC can be damaged if this voltage spike exceeds the maximum voltage the IC can endure. Typically, breakdown voltage of an IC in SPM is 25V, such as:

$$V_{CC} + V_{LS1} + V_{SR1} + V_{LS2} + V_{LS3} < 25V$$

(1)

If  $V_{CC}$  is 15V,  $V_{LS1} + V_{SR1} + V_{LS2} + V_{LS3}$  should be less than 10V.

The PCB pattern that makes Ls1 and Ls2 should be as short as possible because these are on the high-current paths that supply power to the motor.

It is more difficult to minimize Ls1 and Ls2 in a multi-shunt application for phase-current sensing. Surface-mount type resistors are recommended in that case. Non-inductive resistors need to be used.

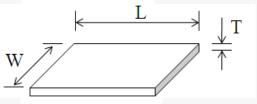

The equation for self inductance is:

Ls =

$$0.2L[ln(\frac{2\times L}{W+T}) + 0.2235(W+T)/L] [nH]$$

(2)

where:

L is PCB pattern length in mm;

W is PCB pattern width in mm; and

T is PCB pattern thickness in mm.

Figure 4. PCB Pattern Definition

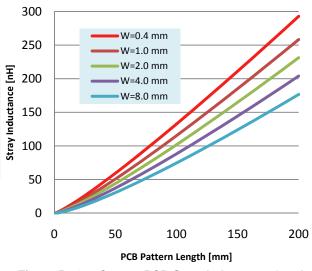

Figure 5 is a graph of PCB pattern length versus stray inductance by PCB pattern width in case of 1 ounce (=0.035mm) copper thickness.

Figure 5. 1oz Copper PCB Stray Inductance Graph

#### AN-9760

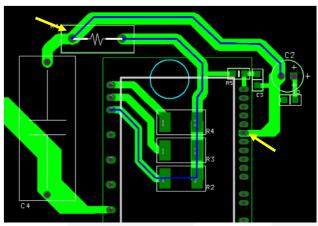

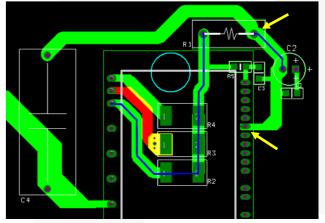

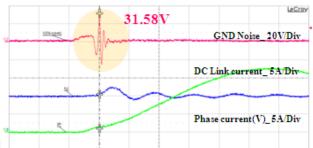

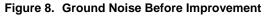

Figure 6 and Figure 7 are PCB layout drawings of a real application. The blue lines on the trace show the signal path. Figure 8 and Figure 9 are the real measured values with an oscilloscope. Measurement points are indicated by yellow arrows in Figure 6 and Figure 7. These demonstrate the importance of stray inductance from PCB pattern.

Figure 6. PCB Layout Before Improvement

Figure 7. PCB Layout After Improvement

The stray inductance before improving PCB layout was about 120nH and it decreased to about 35nH as shown in Equation (2). Induced voltage is calculated as:

$$Vs = L \times \frac{di}{dt} [V]$$

(3)

If the IGBT switching di/dt is 250A/ $\mu$ s, V<sub>s</sub> is calculated as:

$$V_{S\_Before} = 120 \text{nH} \text{ x } 250 \text{A}/\mu\text{s} = 30 \text{V}$$

$$V_{S_After} = 30nH \times 250A/\mu s = 8.75V$$

The actual measured peak voltage is 31.58V before, and 5.94V after, the improved PCB layout.

Even though this type of measurement can't be trusted 100%, 31.58V exceeds the breakdown voltage of the IC inside SPM. Repetitive spikes can gradually damage the IC and may cause failure ultimately. Designers need to minimize the parasitic inductance of the main current path to enhance the reliability and reduce EMI noise.

Figure 9. Ground Noise After Improvement

# Current Sensing for C<sub>sc</sub> Signal

The  $C_{SC}$  input signal is important to detect an over-current situation and prevent damage to the system. Figure 10 shows the different points of  $C_{SC}$  wiring.  $C_{SC}$  wiring can minimize the noise influence from Ls1. When the  $C_{SC}$  wiring is connected at point A, the voltage of  $C_{SC}$  is affected by Ls1 on top of the resistance of the trace. Resistance of this trace results in decrease of trip level because it is similar to adding a resistor in series with the shunt resistor. Ls1 creates the voltage spike at the reverse-recovery current and, therefore, a longer time constant filter is required to avoid nuisance trip. The recommended connection point is B in Figure 10. This can also apply to the current feedback circuit. Ls2 should be minimized to achieve reliable current protection and measurement.

Figure 10. Current-Sensing Point on PCB Layout

AN-9760

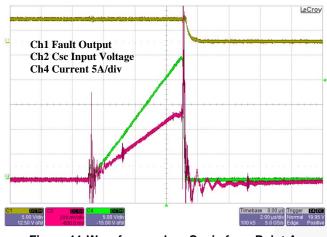

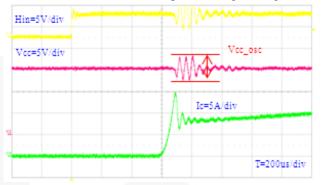

Figure 11. Waveforms when C<sub>SC</sub> is from Point A

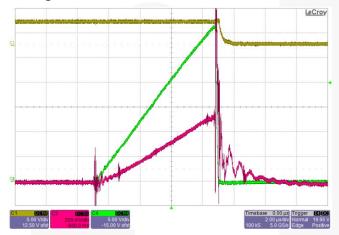

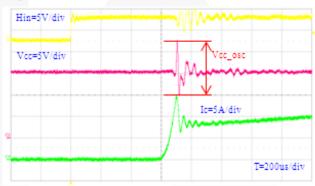

Figure 12. Waveforms when C<sub>SC</sub> is from Point B

Figure 11 and Figure 12 show the difference between two  $C_{sc}$  measuring points. A 20m $\Omega$  shunt resistor is used in this test. The  $C_{sc}$  threshold level is 0.5V; therefore, the overcurrent trip level is 25A DC. Measuring from point A results in lower trip level in terms of actual current, but  $C_{sc}$  voltage is almost the same. Because an RC filter with a 1.8µs time constant is used and there's additional propagation delay from the internal comparator to PWM shutdown and fault output, current keeps rising after it reaches the trip level. Do not be confused by the actual trip level and conclude point A provides better results.

### Location of Capacitor between $V_{\mbox{\scriptsize CC}}$ and COM

Figure 13. Component Placement of V<sub>cc</sub>-COM of SPM<sup>®</sup>

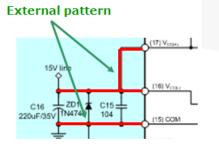

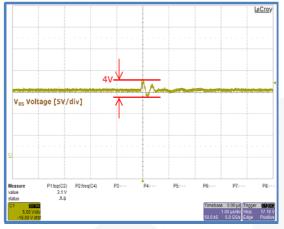

Capacitors between  $V_{CC}$  and COM should be placed close to SPM, as shown in Figure 13. Figure 14 and Figure 15 show the ripple of  $V_{CC}$  when the distance between the capacitor and  $V_{CC}$ -COM varies with 10z copper and 20mil width. A Zener diode is recommended to prevent surge voltage.

Figure 14. 20mm Distance from C16 to V<sub>cc</sub> and COM

Figure 15. 5mm Distance from C16 to V<sub>cc</sub> and COM

### **Location of Bootstrap Capacitor**

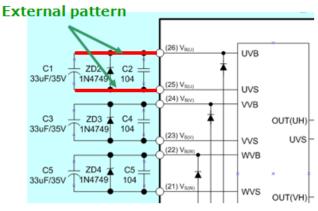

Capacitors between  $V_B$  and  $V_S$  should be placed close to the SPM, as shown in Figure 16. A longer PCB pattern makes higher peak surge voltage. When  $V_S$  becomes negative at switching instances,  $V_{BS}$  can increase more than  $V_{CC}$ . It is recommended to add a Zener diode to prevent surge voltage.

Figure 16. Component Placement in V<sub>BS</sub> of SPM<sup>®</sup>

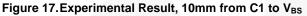

Figure 17 and Figure 18 show ripple voltage of  $V_{BS}$  with different distances from a capacitor to  $V_B$  and  $V_S$ .

Figure 18. Experimental Result, 50mm from C1 to  $V_{BS}$

## **RC Filter for Input Signals**

The  $V_{IN}$  RC filter can be used to prevent erroneous switching of the IGBT. When RC filters are adopted, keep in mind that PWM volt-second can be distorted and PWM performance can deteriorate.

Figure 19. Component Placement in RC Filter of SPM<sup>®</sup>

If PCB layout is done properly, internal pull-down resistors accomplish the job, but additional strong pull-down resistors are often used to make the operation more reliable.

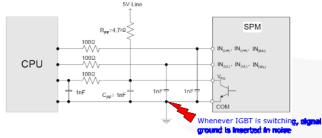

## Location of Snubber Capacitor

Generally, a  $0.1 \sim 2.2 \mu$ F film capacitor is recommended for a snubber capacitor. If the snubber capacitor is installed in the wrong location, shown as A in Figure 16, surge voltage cannot be suppressed effectively. Location B is best in terms of noise suppression, but charging and discharging currents from this snubber capacitor are not reflected on the shunt resistor, which results in error of current feedback measurement or over-current protection. Position C is a reasonable compromise with better suppression than location A without impacting the current-sensing signal accuracy. For this reason, location C is generally used.

Figure 20.DC Link Snubber Capacitor Location

## **Related Resources**

- <u>FNA40560 Smart Power Module Motion SPM®</u>

- FNA40860 Smart Power Module Motion SPM<sup>®</sup>

- FNA41060 Smart Power Module Motion SPM<sup>®</sup>

- FNA41560 Smart Power Module Motion SPM<sup>®</sup>

- FNB40560 Smart Power Module Motion SPM<sup>®</sup>

- <u>FNB41060 Smart Power Module Motion SPM®</u>

- FNB41560 Smart Power Module Motion SPM<sup>®</sup>

- AN-9071 Smart Power Module Motion SPM<sup>®</sup> in µMini DIP SPM<sup>®</sup> Thermal Performance Information

- <u>AN-9072 Smart Power Module Motion SPM<sup>®</sup> in µMini DIP SPM<sup>®</sup> Mounting Guidance</u>

- RD-344 Reference Design for FNA41560 (One Shunt Solution)

- RD-345 Reference Design for FNA41560 (Three Shunt Solution)

- http://www.fairchildsemi.com/models/modelHome

http://www.fairchildsemi.com/products/evaluationboards/

PISCANLERSEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor has against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death ass

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

© Semiconductor Components Industries, LLC