# **ON Semiconductor**

## Is Now

To learn more about onsemi<sup>™</sup>, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# **AND8148/D**

# Using the MC74HC589A as a True SPI-Bus Peripheral

Prepared by: Fred Zlotnick

ON Semiconductor

ON Semiconductor®

http://onsemi.com

## APPLICATION NOTE

#### INTRODUCTION

When it comes to communicating over a serial bus, there are three main methods, SPI (Serial Peripheral Interface), Microwire and I<sup>2</sup>C. The choice is not always easy to make, and often the designer must use whichever hardware is available on his micro-controller or peripherals. Art Eck<sup>1</sup> claims that that of the three common interfaces, SPI is easiest to write code for, and is the fastest protocol.

The SPI-bus was invented in the 1980s as a simple inexpensive way to communicate with peripherals, with a minimum of code and absolute simplicity of the receive function. The SPI-bus is synchronous, with the "master" device responsible for sending out its own clock signal. The bus in its most expansive form consists of 4 wires, SCK (Serial Clock), MISO (Master In Slave Out), MOSI (Master Out Slave In), and SS (Slave Select). The MC74HC589A is a MISO (slave) device only. It will not interfere with the SPI bus use of other master devices in the system, however if there are no other masters, the system reduces to the MISO line, the SCK line and n-number of SS lines. The SS lines can be either a single line controlling a single device or multiple lines for multiple devices. The Latch Clock pin of the NLSF589 is the SS pin for SPI operation. In addition, the MCU needs to provide a logic pin to control the action of the register, either Parallel Load or Serial Shift, this action is not an explicit requirement of SPI, however the part will not function properly, without setting this up. It requires a low to high transition to move the data that has been stored in the shift register, into the output latch. Although the device has an active low Enable pin, it is not necessary to use this pin, and it may be hard wired low.

#### **APPLICATION**

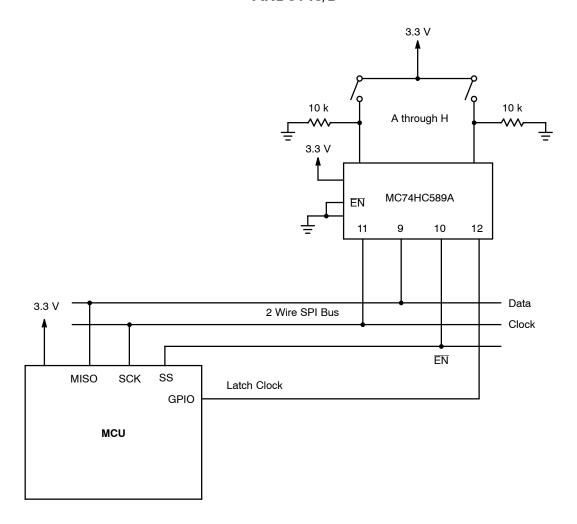

The diagram below shows the use of an MC74HC589 used to detect key closures in a remote location. We only use the MISO port of the MCU. The Key closures are applied to pins A-H. There is no way to determine that a key has either been opened or closed, so the designer must use a "polling" technique. The designer initializes the data, then goes out to the shift register, and reads the data, and looks for a change from the prior state. The designer must return to the SPI port, and update the information on a regular basis e.g. every 30ms. The "HC589" has 8 parallel inputs, along with the various pins for SPI. The diagram shows the switches with pull up resistors on the parallel port (A-H), so the designer just needs to supply a logic level to the port. De-bounce is not explicitly required in hardware. The software engineer might want to return to the port and poll it again, perhaps 10ms later, to see if the closure records the same data. The actual software algorithm will be left to the designer. One further aspect of the design requires the rise and fall times of the clock signals are observed. At a supply voltage of 5 V, the rise time must be = 400 ns to assure the clock are recognized and change state properly. Some designers try to eliminate rf noise by using RC filtering ion the data and clock lines. The recommendation is to use a hysteresis gate(s) on the lines so that the rise and fall time can be met. The circuit is shown operating at 3.3 V, the only requirement is that both the MCU and the shift register function at the same voltage, unless the designer explicitly handles the differences with logic level translators. The diagram shows the EN (Pin 10) asserted with a logic level low, and the latch clock (Pin 12) being asserted with a rising edge applied to this pin. If the designer is trying to save wires, he can use a single gate inverter e.g MC74HC1G14 to create a rising edge from the output enable logic level. Two or more "589s" may be cascaded to get 16, 24 or more bits of data. If this is done, the reader should approach this carefully by reading ON Semiconductor Application Note: AND8144/D and observing the timing issues.

1. Art Eck, Serial Interface for Embedded Design, Circuit Cellar Online- Jan., 2000

### AND8148/D

Figure 1. Application Diagram

ON Semiconductor and was are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative