# **ON Semiconductor**

# Is Now

To learn more about onsemi<sup>™</sup>, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Characterization of ESD Clamping Performance

#### Introduction

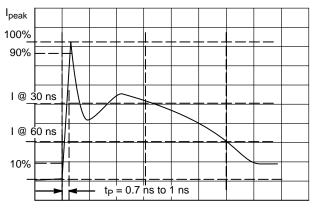

The most commonly used standard for defining a typical electro–static discharge (ESD) event at the system level is IEC61000–4–2, which is distinguished by a waveform with a sub nanosecond rise time and high current levels (see Figure 1). The spec for this waveform calls out 4 levels of ESD magnitudes. Most designers are required to qualify their products to the highest level which is 8 kV contact discharge or 15 kV air discharge.

This test is a survival test designed for a system such as a cell phone or laptop computer. The test procedures for the spec require 10 pulses positive and 10 pulses negative at end user accessible points on the system and then determine if there has been an interruption (soft failure) or damage to the system (hard failure).

Table 1. IEC 61000-4-2 SPEC.

| Level | Test<br>Voltage<br>(kV) | First Peak<br>Current (A) | Current at<br>30 ns (A) | Current<br>at 60 ns<br>(A) |

|-------|-------------------------|---------------------------|-------------------------|----------------------------|

| 1     | 2                       | 7.5                       | 4                       | 2                          |

| 2     | 4                       | 15                        | 8                       | 4                          |

| 3     | 6                       | 22.5                      | 12                      | 6                          |

| 4     | 8                       | 30                        | 16                      | 8                          |

Figure 1. IEC61000-4-2 Spec

#### **Testing ESD Voltage Clamping**

ESD protection devices are an effective solution to protect sensitive circuit elements against these types of ESD surges. Most companies that make protection products, including ON Semiconductor, test their protection devices for survivability to the IEC 61000–4–2 current waveform. The ability of a protection device to survive an ESD stress does not guarantee that it will provide adequate protection

## ON Semiconductor®

www.onsemi.com

## **APPLICATION NOTE**

to sensitive circuit elements, however. To do this the protection component must not only survive the ESD stress, but also maintain very low voltage across it during the ESD event to ensure that the circuit element it is protecting survives. Additional characterization is required to determine a protection device's voltage clamping capability. Examining the voltage waveform across the device during the time domain of an ESD event will give a designer valuable information as to what voltage the IC that is being protected will be exposed to. The following testing procedure outlines the steps ON Semiconductor utilizes to measure the voltage waveform over time of a protection device during an ESD event by obtaining an oscilloscope screenshot of the event.

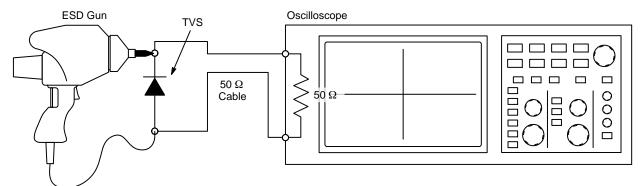

#### Test Procedure to Obtain ESD Voltage Clamping Screenshot

- Mount part on high frequency test board with SMA connector on back side – one terminal of protection part is connected to SMA center pin; other terminal connected to ground.

- 2. 50  $\Omega$  cable connects SMA connection on test board to oscilloscope.

- a. Set oscilloscope to 50  $\Omega$  input impedance to prevent reflections.

- 3. Attenuator used between cable and oscilloscope to protect the oscilloscope.

- a. Set oscilloscope external attenuator setting to match attenuator used to ensure correct voltage measurements.

- Connect ground of ESD gun to ground of ESD test board by clipping it to SMA connection on back side of board. Connect tip of ESD gun to SMA center pin on ESD test board.

- 5. Discharge ESD gun in contact discharge mode at desired voltage.

The ESD diode is isolated between pins that are directly connected to the source of the ESD pulse and ground. The turn on resistance of the protection diode is much lower than the  $50~\Omega$  impedance of the cable so the majority of the current during the ESD event is directed through the protection device. The oscilloscope will then give an

## AND8307/D

accurate reading of the clamping waveform across the device over time during the event.

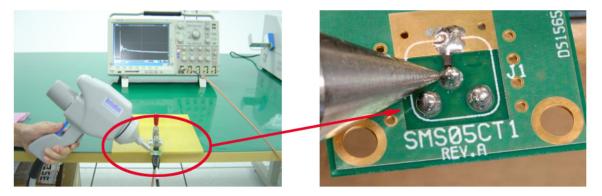

Figures 2 and 3 below illustrate the test setup described in the steps above.

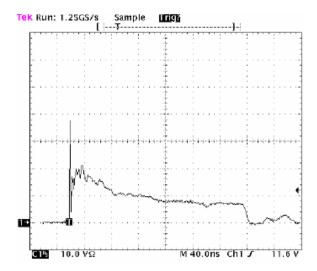

An example of an ESD screenshot is shown in Figure 4. The desired output for an effective ESD protection device is to have a low overall voltage waveform during the entire duration of the ESD event. This screenshot technique

becomes particularly useful when comparing two ESD protection devices for performance. In the past, this information was not readily available on datasheets but since IC's are becoming more sensitive to ESD ON Semiconductor recognizes the need for devices that clamp ESD to low voltages and now includes screenshots of the voltage clamping waveform on the datasheets for all ESD protection devices.

Figure 2. Diagram of ESD Test Setup

Figure 3. Picture of ESD Test Setup

Figure 4. ESD Screenshot Example (ON Semiconductor ESD9X5.0ST5G)

## AND8307/D

ON Semiconductor and iii) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor, "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor data sheets and/or specification by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devic

## **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative