**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# 2 Switch-Forward Current Mode Converter

Prepared by: Thierry Sutto ON Semiconductor

# **ON Semiconductor®**

http://onsemi.com

# **APPLICATION NOTE**

This application note describes the design of 120–W, 125 kHz, two–switch forward current mode converter with the NCP1252 controller. It can viewed the practical implementation of the 2–switch forward converter example described in Ref. [1].

The NCP1252 controller offers everything to build cost-effective and reliable ac-dc switching power supplies implementing the forward converter: NCP1252 detects an output overload without relying on the auxiliary Vcc, a Brown-Out input offers protection against low input voltages and improves the converter safety. Finally a SOIC8 package saves PCB space and represents a solution of choice in cost sensitive projects.

The power supply described here operates from a dc input voltage, as the forward converter is usually connected after a Power Factor Correction (PFC) stage. It generates a 12-V output at 10 A. The efficiency at full load is close to 90% at the nominal output of the PFC.

# **Power Supply Components Calculation**

# Transformer

The following equation extracted from the buck converter running in Continuous Current Mode (CCM), turns ratio will determine the turns ratio of the transformer:

$$V_{out} = \eta \cdot V_{bulk min} \cdot DC_{max} \cdot N$$

(eq. 1)

Where:

- V<sub>out</sub> is the output voltage

- $\eta$  is the targeted efficiency

- V<sub>bulkmin</sub> is the minimum operating input voltage of the forward

- DC<sub>max</sub> is the maximum duty cycle that the NCP1252 can deliver

- N is the turns ratio of the transformer

Extracting the turns ratio from the previous equation, we obtain:

$$N = \frac{V_{out}}{\eta V_{bulk \ min} DC_{max}} = \frac{12}{0.9 \times 350 \times 0.45} = 0.085^{(eq. \ 2)}$$

#### Introduction

A major advantage of the two-switch forward converter is that the power switches only block the supply voltage instead of twice the supply voltage as in the flyback or single-switch forward converter.

Here after, the complete specification, of the two switch-forward converter is described:

| Description                                                         | Value           | Units |

|---------------------------------------------------------------------|-----------------|-------|

| Input voltage Range                                                 | 350-410         | Vdc   |

| Output Voltage                                                      | 12              | Vdc   |

| Output Power                                                        | 96              | W     |

| Output Peak Power during 5 sec<br>per 1 min                         | 120             | W     |

| Minimum Output Load Current(s)                                      | 0               | Adc   |

| Number of Outputs                                                   | 1               |       |

| Nominal Output Voltage                                              | 12<br>±5%       | Vdc   |

| Maximum Output Current                                              | 8               | Adc   |

| Maximum Output Peak Current                                         | 10              | Adc   |

| Output ripple                                                       | 50              | mV    |

| Maximum startup time                                                | < 1             | s     |

| Standby Power                                                       | < 100           | mW    |

| Target Efficiency at full load<br>@ Vin = 390 V dc                  | 90              | %     |

| Load Conditions for Efficiency<br>Measurements (10%, 20%,)          | 20, 50<br>& 100 | %     |

| Min Load Efficiency (Pout = 1.2 W)                                  | > 50            | %     |

| Maximum Transient load step of the maximum output current           | 50              | %     |

| Maximum Output drop voltage from $I_{out} = 5$ to 10 A in 5 $\mu$ s | 250             | mV    |

Using this value in Equation 1, we can estimate the minimum duty cycle at high line by changing the bulk voltage parameter:

$$DC_{min} = \frac{V_{out}}{\eta V_{bulk max} N} = \frac{12}{0.9 \times 410 \times 0.085} = 38.2\%^{(eq. 3)}$$

To ensure enough primary magnetizing current to properly reset the core (drive the stray capacitance and allow the voltage across the winding to reverse), one must usually reduce the primary inductance from the core's ungapped value to one that will cause an adequate magnetizing current. A popular rule of thumb as to make the magnetizing current around 10% of the primary current. Since the primary current is 0.94 A peak (the calculation of this peak current is given on the following paragraph), we will let the magnetizing current rise to 0.1 A. The desired primary inductance, then, with a primary voltage of 350 Vdc and a pulse duration of 3.6  $\mu$ s

$$\begin{pmatrix} \frac{DC_{max}}{F_{sw}} = \frac{0.45}{125 \text{ k}} \end{pmatrix}, \text{ is} \\ L_{mag} = \frac{\frac{V_{bulkmin}}{10\% I_{p\_pk}}}{\frac{DC_{max}}{F_{sw}}} = \frac{\frac{350}{0.1 \times 0.94}}{\frac{0.45}{125 \text{ k}}} = 13.4 \text{ mH}$$

(eq. 4)

Based on this assumption the transformer manufacturer offered the following transformer core: E30/15/7.

#### LC Output Filter:

The crossover frequency  $f_c$  will arbitrarily be selected at 10 kHz. Beyond this value, the converter would pick–up switching noise and would require a more carefull layout. Below, the stringent dropout specification would lead to the selection of a larger output capacitor. Considering a voltage drop mostly dictated by  $f_c$ , the output capacitance and the step load current, we can derive a first capacitor value by using a formula already encountered:

$$C_{out} \geq \frac{\Delta I_{out}}{2\pi f_c \Delta V_{out}} \geq \frac{5}{2\pi \times 10 \text{ k} \times 0.25} \geq 318 \text{ }\mu\text{F} \quad (\text{eq. 5})$$

The above case assumes an ESR much lower than the capacitor impedance at the crossover frequency:

$$R_{ESR} \leq \frac{1}{2\pi f_c C_{out}} \leq \frac{1}{2\pi \times 10 \text{ k} \times 318 \, \mu} \leq 50 \text{ m}\Omega \quad (\text{eq. 6})$$

We must also select a capacitor whose worst case ESR remains below the capacitor impedance at the crossover frequency, in order to limits its contribution to the transient output drop. We are going to parallel two 1000  $\mu$ F FM capacitors from Panasonic.

C = 2000

$$\mu$$

F, FM series @ 16 V

$I_{C,rms} = 5.36 \text{ A} (2*2.38 \text{ A}) @ T_A = +105^{\circ}\text{C}$

$R_{ESR,low} = 8.5 \text{ m}\Omega (19 \text{ m}\Omega/2) @ T_A = +20^{\circ}\text{C}$

$R_{ESR,high} = 28.5 \text{ m}\Omega (57 \text{ m}\Omega/2) @ T_A = -10^{\circ}\text{C}$

Given a  $\Delta I_{out}$  of 5 A, the above room temperature ESR components would, generate an output voltage undershoot/ overshoot of:

$$\Delta V_{out} = \Delta I_{out} R_{ESR,max} = 5 \times 28.5 \text{ m} = 142 \text{ mV} \quad (eq. 7)$$

which is acceptable given a specification of 250 mV.

There is a rule of thumb to select an ESR capacitor equal to the half of the calculated value with Equation 6. This rule will take into account the process variation of the capacitor plus some margin for a startup operation of the power supply at very low ambient temperature.

The final check will include the circulating rms current. However, given the nonpulsating nature of the buck output, we do not expect this current to be that high.

Considering the output power level and the selected capacitor, we can consider the total ripple voltage contributed by the ESR term alone. Thus, if we adopt an ESR of  $22 \text{ m}\Omega$  (approximate value at 0°C), the maximum peak to peak output ripple current must be lower than:

$$\Delta I_{L} \leq \frac{V_{\text{ripple}}}{R_{\text{ESR,max}}} \leq \frac{50 \text{ m}}{22 \text{ m}} \leq 2.27 \text{ A} \qquad (\text{eq. 8})$$

To obtain the output inductor value, we can write the buck ripple expression based on the off-time duration:

$$\Delta I_{L} = \frac{V_{out}}{L} (1 - DC_{min})T_{sw}$$

(eq. 9)

Using Equation 8, we can derive a minimum inductor value for L:

$$L = \frac{V_{out}}{\Delta I_L} (1 - DC_{min}) T_{sw} \ge \frac{12}{2.27} (1 - 0.38) \frac{1}{125 \text{ k}} \ge 26 \text{ } \mu\text{H}$$

If we consider a 10% drop in the inductor value at high temperature and current, let us adopt a 29  $\mu$ H output inductor. But as this value is not standard part we will stick to a 27- $\mu$ H normalized value.

With the selected inductor value, we can calculate the rms current in the output capacitor:

$$I_{C_{out},rms} = I_{out} \frac{1 - DC_{min}}{\sqrt{12\tau_L}} = 10 \times \frac{1 - 0.38}{\sqrt{12 \times 2.813}} = 1.06 \text{ A}$$

Where:

$$\tau_{L} = \frac{L_{out}}{\frac{V_{out}}{I_{out}} \cdot \frac{1}{F_{sw}}} = \frac{27 \,\mu}{\frac{12}{10} \times \frac{1}{125 \,k}} = 2.813 \quad (eq. 12)$$

Given the equivalent capacitor current capability (5.36 A), there is no problem here.

The secondary side peak current will be:

$$I_{s_pk} = I_{out} + \frac{\Delta I_L}{2} = 10 + \frac{2.27}{2} = 11.13 \text{ A}$$

(eq. 13)

On the primary side, this current reflects to:

$$I_{p_pk} = I_{s_pk}N_{ratio} = 11.13 \times 0.085 = 0.946 \text{ A}$$

(eq. 14)

And the valley reaches

And the valley reaches

$$I_{p\_valley} = \left(I_{out} - \frac{\Delta I_L}{2}\right) N_{ratio} = \left(10 - \frac{2.27}{2}\right) \times 0.085 = 0.75 \text{ A} \quad (eq. 15)$$

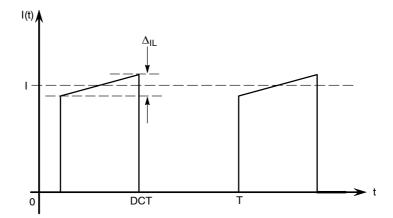

Based on the following Equation 16, we are able to calculate the rms current of a pulsating waveform with linear current (see Figure 1):

$$I_{\text{rms}} = I \sqrt{DC} \sqrt{1 + \frac{1}{3} \left(\frac{\Delta I}{2I}\right)}$$

(eq. 16)

Figure 1. Pulsating Waveform with Linear Ripple Current

This waveform exactly despits the current we have with a forward converter on the primary or secondary side of the tranformer.

When this current is measured on the primary side,  $\Delta I$  represents the reflected secondary–side ripple summed with the magnetizing current. Thus if we would like to accurately

calculate the primary rms current, the magnetizing current should be added to the  $I_{p_pk}$  calculated with Equation 14. The magnetizing inductance has been previously calculated (Equation 4) with 10% of the primary peak current. Therefore the primary rms current can be written has followed:

$$I_{p,rms,10\%} = \sqrt{DC_{max} \left( (1.1 \cdot I_{p_pk})^2 - 1.1 \cdot I_{p_pk} \Delta I_L N + \frac{(\Delta I_L N)^2}{3} \right)}$$

(eq. 17)

$$I_{p,rms,10\%} = \sqrt{0.45 \left( (1.1 \times 0.946)^2 - 1.1 \times 0.946 \times 2.27 \times 0.085 + \frac{(2.27 \times 0.085)^2}{3} \right)} = 0.63 \text{ A}$$

Where:

- DC<sub>max</sub> is the maximum duty cycle that the NCP1252 can deliver

- $I_{p \ pk}$  is the peak current calculated by Equation 14.

- $\Delta I_L$  is the maximum output peak to peak current ripple

- N is the turns ratio of the transformer

#### **Mosfet Selection**

The mosfets are selected based on the maximum input voltage and a derating factor  $k_M$  of 0.85. If we choose 500 V devices (in a two-switch forward converter, the transistor stress is limited to the input voltage), the maximum high-voltage rail must be limited to

$$V_{bulk,max} = BV_{DSS}k_{M} = 500 \times 0.85 = 425 V$$

(eq. 18)

The FDP16N50 has been selected for this application. Its specification are as follows:

- Package TO220

- BV<sub>DSS</sub> = 500 V

- $R_{DS(on)} = 0.434 \Omega$  at  $T_j = 110^{\circ}C (R_{DS(on)} = 0.31 \Omega @$  $T_j = 25^{\circ}C$  multiplied by 1.4:  $R_{DS(on)}$  derating factor for 110°C)

- $Q_G = 45 \text{ nC}$

- $Q_{GD} = 14 \text{ nC}$

Thanks to Equation 17, we can estimate its conduction losses as

$$P_{cond} = I_{p \text{ rms } 10\%}^2 R_{DS(on)} @ T_1 = 110^{\circ}C = 0.632^2 \times 0.434 = 173 \text{ mW}$$

(eq. 19)

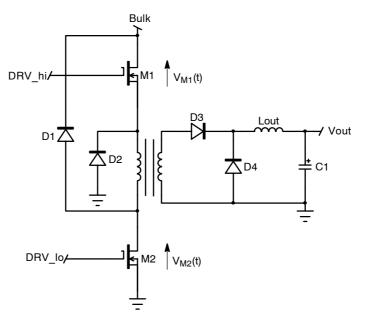

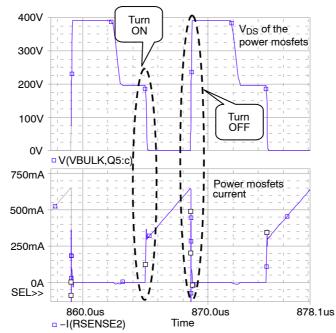

As we are running a 2-switch forward application, the voltage presents on each power switch at the turn-on is equal to the half of the bulk voltage: the two following figures

illustrate the 2-switch forward arrangement and the simulated voltage present on both power switches.

Figure 2. 2-switch Forward Arrangement

Figure 3. Power Mosfet Curves:  $V_{DS}(t)$  and  $I_D(t)$  of the Both Power Mosfets

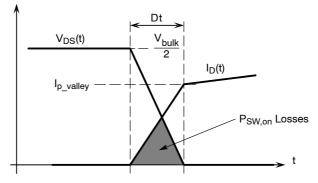

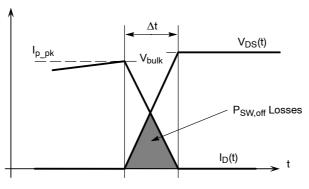

At the turn-on the power losses can be expressed as follow:

Figure 4. Turn-on Losses (PSW,on)

The average power losses at the switch on is a triangle area, the exact calculation can be done via the following integral calculation:

$$\begin{split} \mathsf{P}_{SW,on} &= \mathsf{F}_{sw} \int\limits_{0}^{\Delta t} \mathsf{I}_{\mathsf{D}}(t) \mathsf{V}_{\mathsf{DS}}(t) dt \\ &= \frac{\mathsf{I}_{p\_valley} \frac{\mathsf{V}_{\mathsf{bulk}} \Delta t}{2}}{6} \mathsf{F}_{sw} \end{split} \tag{eq. 20} \\ \mathsf{P}_{SW,on} &= \frac{\mathsf{I}_{p\_valley} \mathsf{V}_{\mathsf{bulk}} \Delta t}{12} \mathsf{F}_{sw} \end{split}$$

Based on the previous equation we are able to estimate the losses at each power mosfet switch on:

$$P_{SW,on} = \frac{I_{p\_valley}V_{bulk,max}\Delta t}{12}F_{sw}$$

(eq. 21)

$$P_{SW,on} = \frac{0.75 \times 410 \times 46.7 \text{ n}}{12} \times 125 \text{ k} = 149 \text{ mW}$$

Where the overlap ( $\Delta t$ ) is estimated via the following equation:

$$\Delta t = \frac{Q_{GD}}{I_{DRV \ pk}} = \frac{14 \text{ n}}{0.300} = 46.7 \text{ ns} \qquad (\text{eq. 22})$$

This overlap estimation does not take into account that the driver of the NCP1252 is a CMOS type, in that case the output driver will not deliver a constant current. Nevertheless the estimation is not so wrong. This overlap is true for a bipolar driver stage that it delivers a constant current.

As we have 2 power mosfets with our application the total switch–on losses will the double of the losses from Equation 21: 358 mW.

Experimental measurement:

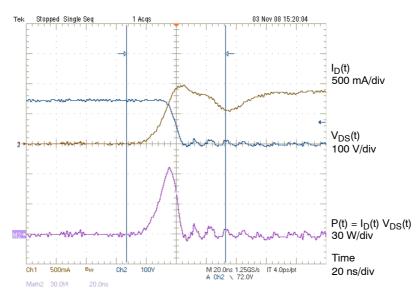

Figure 5. Switching Losses During the Turn On of the LOW Side Mosfet

Figure 6. Switching losses during the turn on of the HIGH side mosfet

Figures 5 and 6 represent the power losses of the power mosfets (high and low side mosfet). From these figures we can note that the drain to source voltage on the low and high side mosfet is not at the half of bulk voltage as expected from the theory and the simulation result.

Drain to source power mosfet voltage is not equal to the half of the bulk voltage due to the parasitic element from the transformer and the power mosfet. The low side power mosfet voltage is equal to 150 V and 240 V for the high side one.

Thus the measured switch-on losses are the following:

- High side switch on losses: 386 mW

- Low side switch on losses: 155 mW

If we compare these experimental results with the theory from Equation 21 where the switch on losses has been estimated to 179 mW per switch, we can conclude that the losses have not been well estimated. This is probably due to the wrong estimation of the driver current capability  $(I_{DRV_pk})$ : we took the hypothesis that the driver is able to deliver a constant current as we have with a bipolar output stage (UC384X like). But as the NCP1252's output driver stage is based on the CMOS technology, the current is varying with the voltage on the power mosfet gate, thus it is really difficult to estimate accurately the overlap.

As the losses of the power MOSFET in a 2–switch forward are very low, the error introduce in these estimations does not impact to much the heat sink calculation.

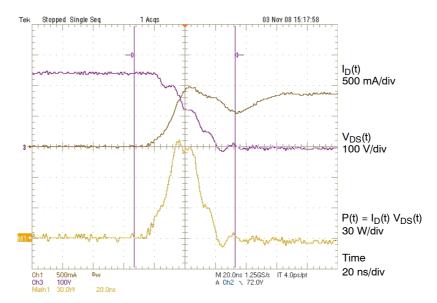

The losses at the turn off can be calculated using the similar method: but now the peak current is at its max value. The drain-to-source voltage of the power switch is close to zero and switches to  $V_{bulk}$ .

Figure 7. Turn-off Losses (P<sub>SW.off</sub>)

Based on the equation used for the switch on losses, we are able to estimate the losses at each power mosfet:

$$P_{SW,off} = \frac{I_{p_pk}V_{bulk,max}\Delta t}{6}F_{sw} = \frac{0.95 \times 410 \times 40 \text{ n}}{6} \times 125 \text{ k} = 324 \text{ mW}$$

(eq. 23)

The overlap ( $\Delta t$ ) is estimated via the following equation:

$$\Delta t = \frac{Q_{GD}}{I_{DRV, pk}} = \frac{14 \text{ n}}{0.350} = 40 \text{ ns}$$

(eq. 24)

We are now able to estimate the overall losses on each power mosfet:

$$\begin{split} \mathsf{P}_{\mathsf{losses}} &= \mathsf{P}_{\mathsf{SW},\mathsf{on}} + \mathsf{P}_{\mathsf{cond}} + \mathsf{P}_{\mathsf{SW},\mathsf{off}} \\ &= 0.149 + 0.173 + 0.324 \end{split} \tag{eq. 25} \\ \mathsf{P}_{\mathsf{losses}} &= 646 \ \mathsf{mW} \end{split}$$

Where:

- Switch-on losses: P<sub>SW,on</sub> = 149 mW

- Conduction losses: P<sub>cond</sub> = 173 mW

- Switch-off losses: P<sub>SW,off</sub> = 324 mW Once we have the total dissipation budget per MOSFET, a heatsink can be calculated.

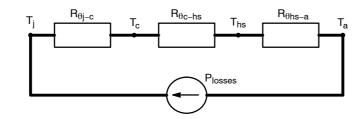

Figure 8. Thermal path between the power mosfet and the heat sink

Where:

- T<sub>i</sub> is the junction temperature of the power mosfet

- $T_c$  is the case temperature of the power mosfet

- T<sub>hs</sub> is the heat sink temperature

- T<sub>a</sub> is the ambient temperature

- $R_{\theta j-c}$  is the thermal resistance between the junction and the case of the power mosfet

- $R_{\theta c-hs}$  is the thermal resistance between the case of the power mosfet and the heat sink

- $R_{\theta hs-a}$  is the thermal resistance between the heat sink and the ambient temperature.

The following condition has to be checked to prevent any over heating of the power mosfet during worst case operation:

$$T_{jmax} - T_{ambmax} > P_{losses} \sum R_{\theta}$$

(eq. 26)

Or it can be written as follow:

$$\begin{split} \mathsf{R}_{\theta h sa} &< \frac{\mathsf{T}_{jmax} - \mathsf{T}_{ambmax}}{\mathsf{P}_{losses}} - \left(\mathsf{R}_{\theta jc} + \mathsf{R}_{\theta chs}\right) \\ &< \frac{110 - 65}{0.646} - (1 + 1.2) \end{split} \tag{eq. 27}$$

$$R_{\theta hsa} < 67.4 \circ C/W$$

Thus the thermal resistance of the heat sink should be lower than  $67.4^{\circ}$ C/W. A KL194/25.4/SW from Seifert (ref.[2]) has been selected (14°C/W).

#### **Diodes Selection**

The choice of the primary freewheeling diodes depends on the transformer magnetizing inductor. The magnetizing peak current can be calculated via the following equation:

$$I_{mag\_pk} = \frac{V_{bulk,min}}{L_{mag}} \frac{DC_{max}}{F_{sw}} = \frac{350}{13.4 \text{ m}} \times \frac{45\%}{125 \text{ k}} = 94 \text{ mA}$$

As the magnetizing and demagnetizing voltage are similar  $(V_{bulk}, \text{ thanks to the } 2\text{-switch forward structure})$ ; both on and reset times are equal.

$$t_{reset} = I_{mag,pk} \frac{L_{mag}}{V_{bulkmin}} = 94 \text{ m} \frac{13.4 \text{ m}}{350} = 3.6 \,\mu\text{s}$$

(eq. 29)

The average current can now be derived in a snapshot:

$$I_{mag\_avg} = \frac{(t_{on} + t_{reset})I_{mag\_pk}}{\frac{2}{F_{sw}}}$$

$$= \frac{\left(\frac{DC_{max}}{F_{sw}} + t_{reset}\right)I_{mag\_pk}}{\frac{2}{F_{sw}}}$$

(eq. 30)

$$= \frac{\left(\frac{0.45}{125 \text{ k}} + 3.6 \text{ }\mu\right) \times 94 \text{ }m}{\frac{2}{125 \text{ }k}}$$

$I_{mag avg} = 42.3 \text{ mA}$

Diode such as the MUR160 accommodates the demagnetization task easily. Usually, in off-line application as the magnetizing current remains low any 1 A high voltage diode (500 or 600 V) can do the job.

Let us now take care of the secondary diodes. In the forward converter, both secondary-side diodes sustain a similar peak inverse voltage (PIV). Given a turns ratio of 0.085 and the diode's derating factor  $k_D$ , the diodes have to sustain the following PIV:

$$PIV = \frac{NV_{bulkmax}}{k_D} = \frac{0.085 \times 410}{0.60} = 58 \text{ V} \quad (eq. 31)$$

Thanks to the low PIV value, we are able to select the following Schottky diode reference: MBRB30H60CT.

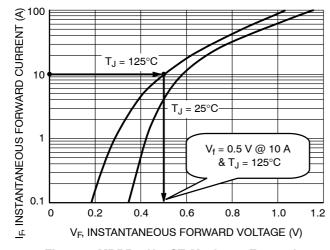

This diode (30 A, 60 V in a TO-220) case features a maximum drop of 0.5 V at 125°C (see Figure 9)

Figure 9. MBRB30H60CT, Maximum Forward Voltage versus Instaneous Current

The series diode would then dissipate the following power in worst case conditions (Low line and maximum duty cycle).

(eq. 32)

$$P_{d on} = V_{f}I_{out}DC_{max} = 0.5 \times 10 \times 0.45 = 2.25 W$$

The freewheeling diode would dissipate slightly more as it conducts during the off time:

$$P_{d_{off}} = V_{f} I_{out} (1 - DC_{min})$$

(eq. 33)

= 0.5 × 10 × (1 - 0.39) = 3.05 W

On average these diodes would dissipate around 5.3 W or 4.4% of the total output power. In order to improve the efficiency it can be interesting to implement a synchronous rectification to replace them.

For these diodes, we can re-use Equation 27 to calculate the required heat sink.

$$\begin{split} \mathsf{R}_{\theta h s-a} &< \frac{\mathsf{T}_{\mathsf{Jmax}} - \mathsf{T}_{\mathsf{AMBmax}}}{\mathsf{P}_{\mathsf{losses}}} - \left(\mathsf{R}_{\theta \mathsf{j-c}} + \mathsf{R}_{\theta \mathsf{c-hs}}\right) \\ &< \frac{125 - 65}{5.33} - (2 + 1.2) \end{split} \tag{eq. 34} \\ \mathsf{R}_{\theta \mathsf{hs-a}} &< 8.06^{\circ}\mathsf{C}/\mathsf{W} \end{split}$$

Thus the thermal resistance of the heat sink should be lower than 8°C/W.

For the demonstration board, the following heat sink has been selected KL195/25.4/SW from Seifert (ref.[2]). It provides a low thermal resistance of 6.2°C/W.

## NCP1252 Component Selection

#### **Switching Frequency Selection**

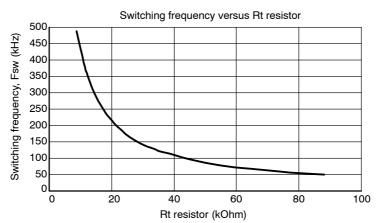

A resistor connected between the  $R_t$  pin and the ground precisely sets the switching frequency between 50 kHz and a maximum of 500 kHz. The following curve helps to select the resistor according the selected switching frequency.

Figure 10. Switching Frequency Selection

The following equation could also be used to calculate the resistor value according to the switching frequency selection:

$$\mathsf{R}_t = \frac{1.95 \times 10^9 \mathsf{V}_{\mathsf{R}_t}}{\mathsf{F}_{\mathsf{sw}}} \tag{eq. 35}$$

Where:

• V<sub>Rt</sub> is the internal voltage reference present on the Rt pin and equal to 2.2 V.

If we assume a switching frequency of 125 kHz,

$$R_{t} = \frac{1.95 \times 10^{9} \times 2.2}{125 \text{ k}} = 34.3 \text{ k}\Omega$$

If we select a 33 k $\Omega$  resistor, this will yield:

$$F_{sw} = \frac{1.95 \times 10^{9} V_{R_{t}}}{R_{t}} = \frac{1.95 \times 10^{9} \times 2.2}{33 \text{ k}} = 130 \text{ kHz}^{(eq. 36)}$$

The measurement on the final board with a resistor equal to 33 k $\Omega$  gives us 130 kHz for the switching frequency.

This oscillator resistor will be laid out as close as possible to the Rt pin (pin #4) of the NCP1252 and its ground (pin #5). As these pins are really close together, it will be not so difficult to take into account this requirement. The robustness of the controller against electrical noise will be improved.

#### Sense Resistor

The NCP1252 featuring a maximum peak current to 1 V, the sense resistor is computed via the following expression, where a 20% margin appears on the primary peak current (10% for the magnetizing current and 10% for general margin):

$$R_{sense} = \frac{F_{CS}}{1.2I_{p \ pk}} = \frac{1}{1.2 \times 0.946} = 884 \text{ m}\Omega \quad (eq. 37)$$

The power dissipation of the sense resistor with a 20% margin on the primary peak current amounts to:

$$P_{R_{sense}} = I_{p,rms,20\%}^{2} R_{sense} = 0.695^{2} \times 0.884 = 427 \text{ mW}$$

Where:

• I<sub>p,rms,20%</sub> is the rms current of the primary peak current with 20% margin on the peak current

As we are using 1206 resistor type sizes with a limited power dissipation of 250 mW, we have to place 2 resistors in parallel in order to fit the authorized power capability. Thus we select 2 resistors of 1.5  $\Omega$ . The new power dissipation will be 362 mW for both resistors and 180 mW for each one.

Despite the presence of a Leading Edge Blanking (LEB = 130 ns), it is recommended to insert between the sense resistor and the CS pin of the controller a small RC filter in order to remove any parasitic noise from the application. This small RC network will "clean" the current sense

measurement and it will improve the robustness of the power supply. Nevertheless this time constant should not be too large compared to the switching period of the controller. It is usually recommended to select a 150–300–ns time constant for the current sense filter network.

The NCP1252 provides an internal ramp compensation appearing on the CS pin. The resistor of the RC filter will play a double function: ramp compensation and time constant for filtering. Thus the ramp compensation will fix the resistor value of the RC filter and then the capacitor will be adjusted to respect the time constant previously defined.

One of the following chapters describes how to calculate the ramp compensation resistor.

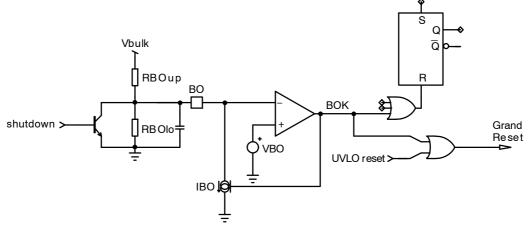

#### Brown-out

By monitoring the level on BO pin, the NCP1252 protects the forward converter against low input voltage conditions. When the BO pin level falls below the  $V_{BO}$  level, the controllers stops pulsing until the input level goes back to normal and resumes the operation via a new soft start sequence.

The brown-out comparator features a fixed voltage reference level ( $V_{BO}$ ). The hysteresis is implemented by using the internal current connected between the BO pin and the ground when the BO pin is below the internal voltage reference ( $V_{BO}$ ).

The following equations show how to calculate the resistors for BO pin.

First of all, select the bulk voltage value at which the controller must start switching  $(V_{bulkon})$  and the bulk voltage for shutdown  $(V_{bulkoff})$  the controller.

- Where:

- $V_{bulkon} = 370 V$

- $V_{bulkoff} = 350 V$

- $V_{BO} = 1 V$  (fixed internal voltage reference)

- $I_{BO} = 10 \ \mu A$  (fixed internal current source)

When BO pin voltage is below  $V_{BO}$  (internal voltage reference), the internal current source (I<sub>BO</sub>) is activated. The following equation can be written:

$$V_{bulkON} = R_{BOup} \left( I_{BO} + \frac{V_{BO}}{R_{BOlo}} \right) + V_{BO}$$

(eq. 39)

When BO pin voltage is higher than  $V_{BO}$ , the internal current source is now disabled. The following equation can be written:

$$V_{BO} = \frac{V_{bulkoff} R_{BOlo}}{R_{BOlo} + R_{BOup}}$$

(eq. 40)

From Equation 40 R<sub>BOup</sub> can be extracted:

$$R_{BOup} = \left(\frac{V_{bulkoff} - V_{BO}}{V_{BO}}\right) R_{BOlo} \qquad (eq. 41)$$

Equation 41 is substituted in Equation 39 and solved for  $R_{BOlo}$ , yields:

$$R_{BOlo} = \frac{V_{BO}}{I_{BO}} \left( \frac{V_{bulkon} - V_{BO}}{V_{bulkoff} - V_{BO}} - 1 \right) \qquad (eq. \, 42)$$

$R_{BOup}$  can be also written independently of  $R_{BOlo}$  by substituting Equation 42 into Equation 41 as follow:

$$\mathsf{R}_{\mathsf{BOup}} = \frac{\mathsf{V}_{\mathsf{bulkon}} - \mathsf{V}_{\mathsf{bulkoff}}}{\mathsf{I}_{\mathsf{BO}}} \qquad (\mathsf{eq.}\ 43)$$

From Equation 42 and Equation 43, the resistor divider value can be calculated:

$$\begin{aligned} \mathsf{R}_{\mathsf{BOlo}} &= \frac{1}{10\,\mu} \Big( \frac{370\,-\,1}{350\,-\,1} - \,1 \Big) = 5731\,\,\Omega \\ \mathsf{R}_{\mathsf{BOup}} &= \frac{370\,-\,350}{10\,\mu} = \,2.0\,\mathsf{M}\Omega \end{aligned}$$

We selected the following values for the brown out resistor divider:

- $R_{BOlo} = 5.1 \text{ K}\Omega + 680 \Omega$

- $R_{BOup} = 1 M\Omega + 1 M\Omega$

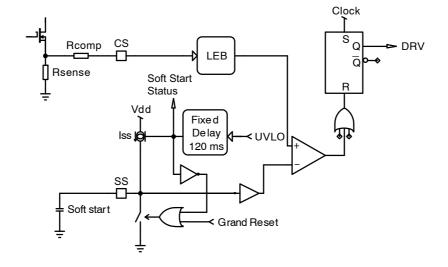

#### Soft Start

The soft start of the NCP1252 controls the peak current of the forward converter during the startup sequence: this prevent any over stress on the power components (primary mosfet, secondary diode and magnetic component like transformer and inductor) during this critical phase and it reduces the output overshoot.

The soft start pin provides a current source connected to an internal voltage reference. Thus a capacitor connected to this current source generates a linear voltage slope that controlling the peak current of the power supply via the current sense resistor. The SS pin voltage is divided by 4 to scale down the SS pin voltage to a compatible CS pin voltage.

#### Figure 12. Soft Start Principle

Based on the following well known equation:

$$I_{SS} = C_{SS} \frac{V_{SS}}{T_{SS}}$$

(eq. 44)

$$C_{SS} = I_{SS} \frac{T_{SS}}{V_{SS}} = 10 \ \mu \frac{15 \ m}{4.0} = 37.5 \ nF \ (eq. 45)$$

By extracting from the previous equation the capacitor value we are able to calculate the soft start duration: if we select  $T_{ss} = 15$  ms,

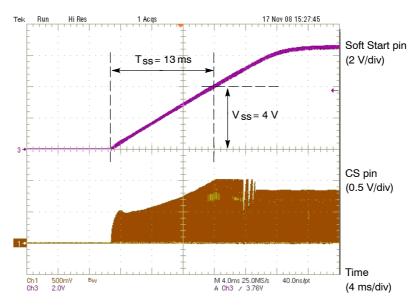

If we select  $C_{ss} = 33$  nF, the soft start duration measured (see Figure 13) on the demoboard is equal to 13 ms.

Figure 13. Soft Start Duration Illustration

Figure 13 illustrates that the max voltage on the soft start pin is equal to 6.6 V, but the peak current of the forward transformer linearly ramps from zero to 4.0 V. Above 4.0 V on the SS pin, the controller will clamp to the max peak current.

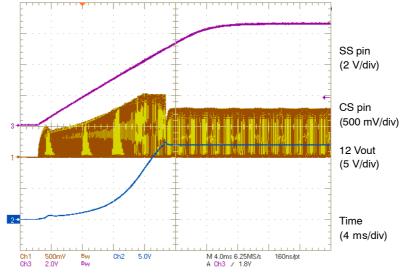

At the beginning of the soft start the peak current variation is not linear due to the Discontinuous Mode Current (DCM) operation of the forward at low peak current and low voltage on the output.

#### **Ramp Compensation Selection**

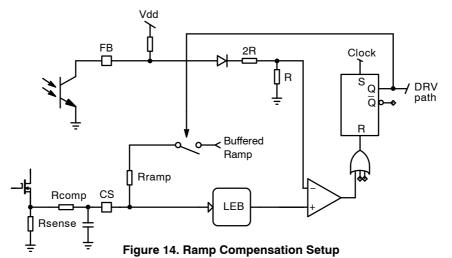

Ramp compensation is a known means to cure subharmonic oscillations. These oscillations take place at

half of the switching frequency and occur only during Continuous Conduction Mode (CCM) with a duty-cycle close or above 50%. To lower the current loop gain, one usually injects between 50 and 100% of the inductor downslope. Figure 14 depicts how internally the ramp is generated:

The ramp compensation applied on CS pin is buffered from the internal oscillator ramp. A switch placed between the buffered internal oscillator ramp and  $R_{ramp}$  disconnects the ramp compensation during the off-time DRV signal.

In the NCP1252, the internal ramp swings with a slope of:

$$S_{int} = \frac{V_{ramp}}{DC_{max}}F_{sw}$$

(eq. 46)

In a forward application the secondary-side downslope viewed on a primary side requires a projection over the sense resistor  $R_{sense}$ . Thus:

$$S_{sense} = \frac{(V_{out} + V_{f})}{L_{out}} \frac{N_{S}}{N_{P}} R_{sense}$$

(eq. 47)

where:

- V<sub>out</sub> is output voltage level

- $V_f$  the freewheel diode forward drop

- Lout, the secondary inductor value

- $N_s/N_p$  the transformer turn ratio

- R<sub>sense</sub>: the sense resistor on the primary side

Assuming the selected amount of ramp compensation to be applied is  $\delta_{comp}$ , then we must calculate the division ratio to scale down  $S_{int}$  accordingly:

$$Ratio = \frac{S_{sense} \delta_{comp}}{S_{int}}$$

(eq. 48)

A few line of algebra determined R<sub>comp</sub>:

$$R_{comp} = R_{ramp} \frac{Ratio}{1 - Ratio}$$

(eq. 49)

The previous ramp compensation calculation does not take into account the natural primary ramp created by the

Then  $R_{comp}$  can be calculated with the same equation used when the natural ramp is neglected.

If we assume that our forward is based on the following information:

2 switch–Forward Power supply specification:

- Regulated output: 12 V

- $L_{out} = 27 \,\mu H$

- $V_f = 0.5 V$  (drop voltage on the regulated output)

- Current sense resistor : 0.75  $\Omega$

- Switching frequency : 125 kHz

transformer magnetizing inductance. In some case illustrate here after the power supply does not need additional ramp compensation due to the high level of the natural primary ramp.

The natural primary ramp is extracted from the following formula:

$$S_{natural} = \frac{V_{bulk}}{L_{mag}} R_{sense}$$

(eq. 50)

Then the natural ramp compensation will be:

$$\delta_{natural\_comp} = \frac{S_{natural}}{S_{sense}}$$

(eq. 51)

If the natural ramp compensation ( $\delta_{natural\_comp}$ ) is higher than the ramp compensation needed ( $\delta_{comp}$ ), the power supply does not need additional ramp compensation. If not, only the difference ( $\delta_{comp}$ - $\delta_{natural\_comp}$ ) should be used to calculate the accurate compensation value.

Thus the new division ratio is:

$$\text{if } \delta_{natural\_comp} < \delta_{comp} \Rightarrow \text{Ratio} = \frac{S_{\text{sense}}(\delta_{comp} - \delta_{natural\_comp})}{S_{\text{int}}} \ \text{(eq. 52)}$$

- V<sub>bulk</sub> = 350 V, minimum input voltage at which the power supply works.

- Duty cycle max :  $DC_{max} = 50\%$

- $V_{ramp} = 3.5 V$ , Internal ramp level.

- $R_{ramp} = 26.5 \text{ k}\Omega$ , Internal pull-up resistance

- Targeted ramp compensation level: 100%

- Transformer specification:

$$-L_{mag} = 13 \text{ m}$$

$$-N_{\rm s}/N_{\rm p} = 0.087$$

Internal ramp compensation level

$$S_{int} = \frac{V_{ramp}}{DC_{max}} F_{sw} \Rightarrow S_{int} = \frac{3.5}{0.50} 125 \text{ kHz} = 875 \text{ mV}/\mu s \qquad (eq. 53)$$

Secondary-side downslope projected over the sense resistor is:

$$S_{sense} = \frac{(V_{out} + V_f)}{L_{out}} \frac{N_S}{N_P} R_{sense} \Rightarrow S_{sense} \frac{(12 + 0.5)}{27 \cdot 10^{-6}} 0.087 \times 0.75 = 30.21 \text{ mV/}\mu s$$

(eq. 54)

Natural primary ramp:

$$S_{natural} = \frac{V_{bulk}}{L_{mag}} R_{sense} \Rightarrow S_{natural} = \frac{350}{13 \cdot 10^{-3}} 0.75 = 20.19 \text{ mV/}\mu s \qquad (eq. 55)$$

Thus the natural ramp compensation is:

$$\delta_{natural\_comp} = \frac{S_{natural}}{S_{sense}} \Rightarrow \delta_{natural\_comp} = \frac{20.19}{30.21} = 66.8\%$$

(eq. 56)

Here the natural ramp compensation is lower than the desired ramp compensation, so an external compensation should be added to prevent sub-harmonics oscillation.

$$\text{Ratio} = \frac{\text{S}_{\text{sense}}(\delta_{\text{comp}} - \delta_{\text{natural\_comp}})}{\text{S}_{\text{int}}} \Rightarrow \text{Ratio} = \frac{30.21(1.00 - 0.67)}{875} = 0.0114 \quad (\text{eq. 57})$$

We can know calculate external resistor (R<sub>comp</sub>) to reach the correct compensation level.

$$\mathsf{R}_{\mathsf{comp}} = \mathsf{R}_{\mathsf{ramp}} \frac{\mathsf{Ratio}}{1 - \mathsf{Ratio}} \Rightarrow \mathsf{R}_{\mathsf{comp}} = 26.5 \cdot 10^3 \frac{0.0114}{1 - 0.0114} = 305 \,\Omega \tag{eq. 58}$$

Thus with  $R_{comp} = 330 \Omega$ , 100% compensation ramp is applied on the CS pin.

As the ramp compensation resistor is now calculated, we are able to calculate the capacitor value of the RC network connected to the CS pin.

If we assume the time constant of the RC network is equal to 220 ns, the capacitor value will be:

$$C_{CS} = \frac{\tau_{RC}}{R_{Comp}} = \frac{220 \text{ n}}{330} = 666 \text{ pF}$$

(eq. 59)

If we select a 680–pF normalized value for  $C_{CS}$  we are really close to the targeted time constant of 220 ns.

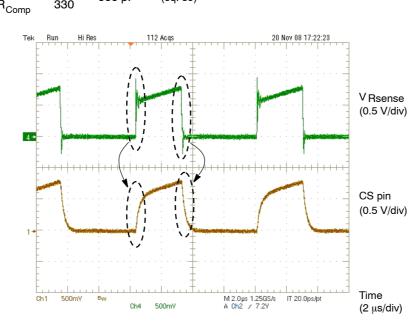

The following figure illustrates the behavior of the RC filtering network.

Figure 15. Comparison of the Voltage on the Current Sense Resistor and After the RC Filter

After filtering the current information of the forward converter provided to the controller is free of noise.

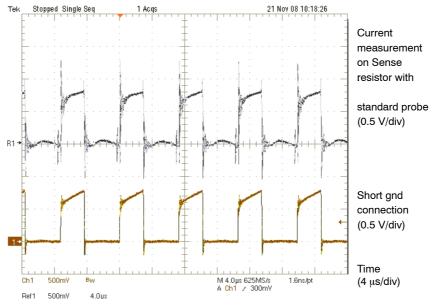

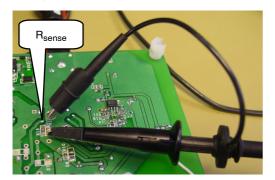

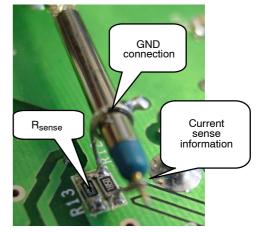

Note: The measurements done in Figure 15 have to be done by respecting a true clean ground probe connection. Usually the scope probe is delivered with a <u>long</u> ground wire: if the original ground wire is used, the current measurement will be worse than in reality. The following figure shows a comparison of the wrong and correct current measurements over the sense resistor.

Both following figures illustrate the different probe connection for measuring the current sense information.

Figure 17 illustrates the standard probe connection: but as the probe's ground wire is quite long, the measurement generates noise (see Figure 16 probe measurement comparison).

Figure 17. Current Sense Measurement on Sense Resistor with Standard Probe Connection

Figure 18 illustrates the correct connection for measuring on a power supply the current sense information. This connection has been done just by removing the plastic tips protection of the standard probe and by soldering two short wires directly to the sense resistor pads.

Figure 18. Current Sense Measurement on Sense Resistor with Short Ground Connection of the Probe

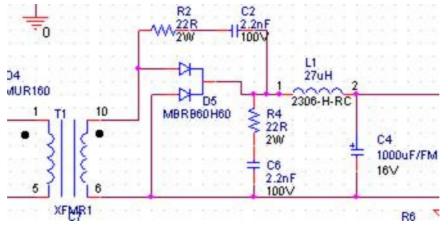

#### Secondary diode snubber calculation:

Without snubbing elements (R2&C2, R4&C6) in parallel with the secondary diodes (D5): some oscillations appear across the secondary diode. These oscillations are the result of the leakage inductance of the secondary side of the transformer with the capacitor behavior of the diode when it blocks. Thus in the worst case condition (max input voltage) it is possible that the maximum reverse voltage of the diode has been reached; with all the consequence.

Figure 19. Secondary Diode Snubbing

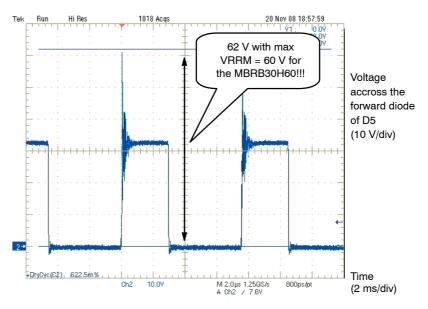

As depicted by the following figure without snubbing element the oscillations at the nominal input voltage reach the maximum reverse voltage of the diode (60 V).

Figure 20. Voltage Applied to the Forward Diode of D5

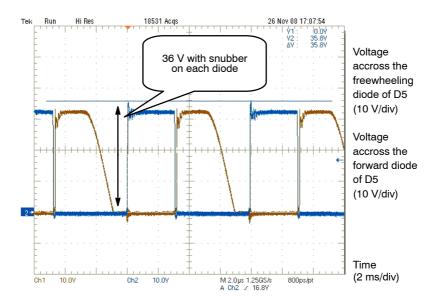

The principle of the snubber placed in parallel of each diode is damp the oscillations. The oscillations take place at the end of the conduction of the diode and they are the consequences of the leakage inductance of the secondary winding and the parasitic diode behavior of the diode.

Knowing the leakage inductance of the secondary winding of the transformer and the oscillation frequency we are able to determine the resistor to be placed in parallel of the diode to damp the oscillations. In that case the resistor will be adjusted to damp completely all the oscillations implying a quality coefficient (Q) of 1:

$$R_{damp} = L_{leak}\omega_r = 118 \text{ n} \times 2\pi \times 22 \text{ M} = 16 \Omega$$

(eq. 60)

After selecting a  $22-\Omega$  resistor for both secondary diodes, the oscillation voltage is now limited to 36 V compared to 62 V without snubber at similar input voltage (373 Vdc). A 2.2-nF capacitor is placed in series with the resistor in order to limit the losses due to the resistor presence.

Figure 21. Voltage Applied to the Secondary Diodes (D5) with Snubber

# **Board Performances**

The following figures illustrate the general performances of this demoboard.

# Startup Delay

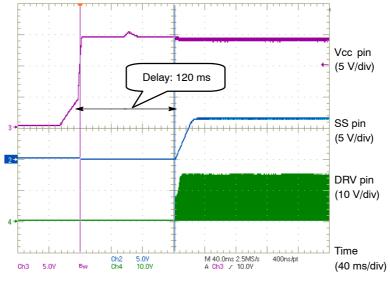

As depicted by Figure 22, when the  $V_{CC}$  voltage is rising from zero and crossing  $V_{CC(ON)}$  level, the NCP1252 sends the first pulses on the DRV pin only when the 120-ms startup delay is elapsed.

Figure 22. Startup Delay

#### Soft Start

Figure 23 depicts a soft start sequence. The CS pin voltage is following the shape of the SS pin voltage. At the beginning of the soft start period, the peak current variation is not linear compare to the middle and the end of the soft start: this non linearity is related due to the DCM (Discontinuous Current Mode) mode of operation of the forward during the first 2 or 3 ms of the soft start when the output voltage is low (< 1 V).

Figure 23. Soft Start at Full Load (10 A)

# **Jittering Frequency**

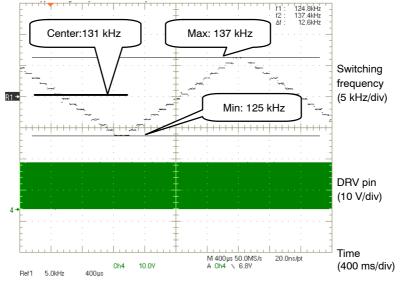

The Jittering frequency featured by the NCP1252 helps to spread out the switching noise and eases the filtering of the power supply. The following figure illustrates the digital jittering frequency of the NCP1252:  $\pm 5\%$  of the centered

switching frequency selected by the resistor connected to  $R_t$  pin with a frequency modulation of 330 Hz. The jittering modulation can be also observed by measuring the  $R_t$  pin voltage.

Figure 24. Jittering Frequency Measurement

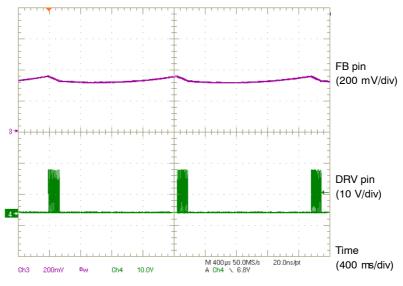

# **No Load Regulation**

Thanks to the skip cycle feature implemented on the NCP1252, it is possible to achieve a real no load regulation without triggering any over voltage protection. The

demonstration board does not have any dummy load and ensure a correct no load regulation. This regulation is achieved by skipping some driving cycles and by forcing the NCP1252 in burst mode of operation.

Figure 25. No Load Regulation (Real No Load to the Output) Vout = 12.096 V

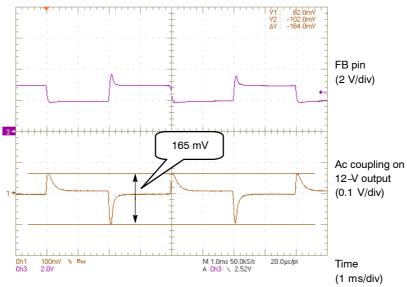

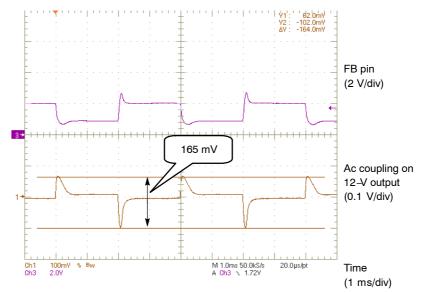

# Step Load Stability

In order to test the close loop stability, a maximum step load of 5 A have been applied on the output. The following figures show the fast transient response without any oscillations and exhibit a low drop voltage 165 mV (1.3% of the nominal output).

Figure 26. Step Load Response from 5 A to 10 A

Figure 27. Step Load Response from 0.5 A to 5.5 A

# Efficiency

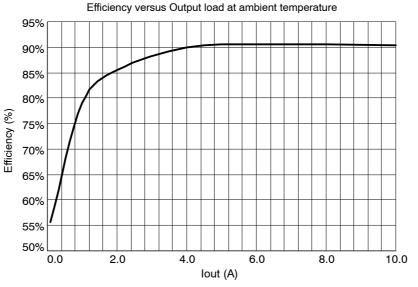

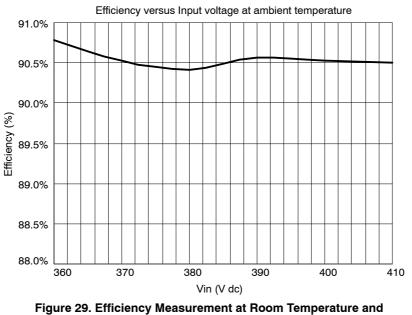

The efficiency measurements have been done at room temp at different load conditions and at the nominal load with different input voltage.

Figure 28. Efficiency Measurement at Room Temperature and Nominal Input Voltage (390 V dc) versus Output Load Variation

Nominal Output Load (10 A dc) versus Intput Voltage

One possible way to improve the efficiency of the demoboard is to implement a synchronous rectification, it will improve by some percent the overall efficiency.

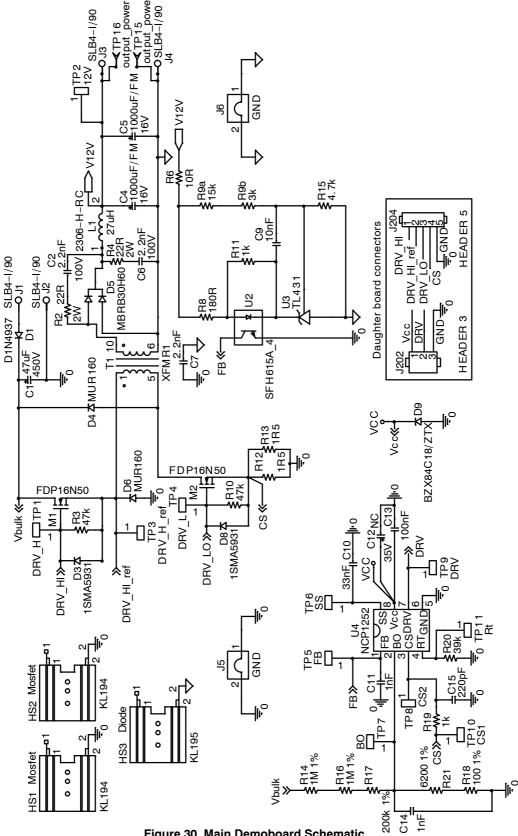

# **Demoboard Schematics**

## Main Board with its Auxiliary Supply

Figure 30. Main Demoboard Schematic

As depicted by Figure 30, the NCP1252 feedback is implemented via a TL431 arranged in a Type 2 corrector. The power supply can be connected directly to a dc source, where the minimum startup voltage is 370 Vdc. There are 2 options for supplying the Vcc to the NCP1252:

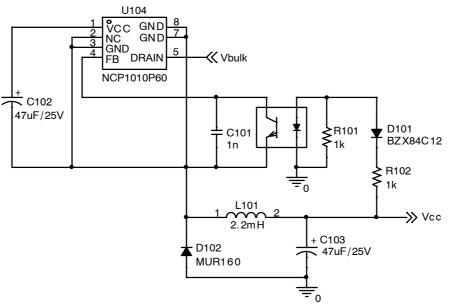

- External  $V_{cc}$  supply: in that case the dedicated connector for the  $V_{cc}$  can be used to supply the 15 Vdc to the demoboard. The NCP1010 controller for the auxiliairy supply must be removed from the board.

- Self  $V_{cc}$  supply: in that case the NCP1010 regulator (see Figure 31) is used to build the 15 V output via a buck converter for stepping down the main bulk voltage to the  $V_{cc}$  level. This auxiliary self supply is implemented on the main board close to the bulk voltage.

Figure 31. Auxiliary Supply Based on the NCP1010 @ 65 kHz

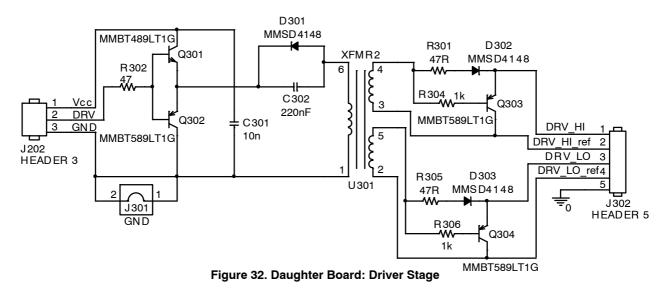

# **Daughter Board: Driver Stage**

The daughter board or the drivers for the high side and low side mosfet is done with a pulse transformer from PREMO.

We selected to drive also the low side power mosfet with the pulse transformer to prevent any difference on the way to drive the low and high side mosfet.

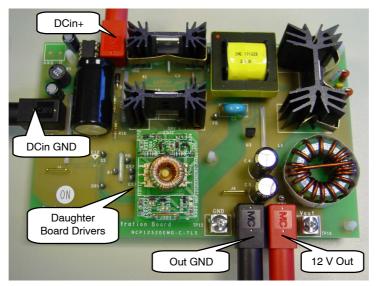

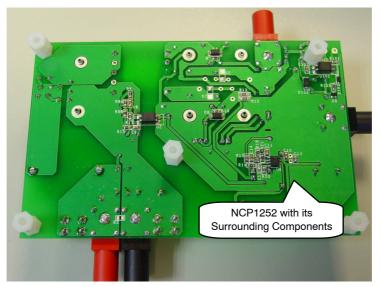

## **Demo Board Picture**

Figure 33. Top View of the Demo Board

Figure 34. Bottom View of the Demo Board

#### References

- 1. C. Basso, "Switch Mode Power Supplies: SPICE Simulations and Practical Designs", McGraw-Hill, 2008.

- 2. Heatsink manufacturer link: <u>http://www.seifert-electronic.de/en/produkt.php?id=50</u> or direct link to the datasheet <u>http://www.digtion-medien.de/seifert/Uploads/seifert\_punkte/pdfs/50%5B0%5D.pdf</u>

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agosciated with such unintended or unauthorized use patent shall claims and so for the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for seale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative