## **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# PoE Auxiliary Supply Applications

#### **Auxiliary Supply Support**

Most of the Ethernet applications can be supplied from a wall wart or via power over Ethernet. A wall wart is adding of an additional power cable and external electronics is therefore not cost effective. Nevertheless it assures operation when the application is connected to a non-PoE switch. Both capabilities can be combined implemented with a minimum cost since the NCP1082 and NCP1083 supports both in a single device. The silicon operates as a full IEEE802.3af and IEEE802.3at respectively compliant device when the PoE capability is available and acts as a DC-DC converter from the wall wart when there is no sourcing device on the cable.

The auxiliary supply support can be implemented in three ways. Dependant where the auxiliary supply is injected the configurations are called front, rear and direct auxiliary supply.

ON Semiconductor®

www.onsemi.com

#### APPLICATION NOTE

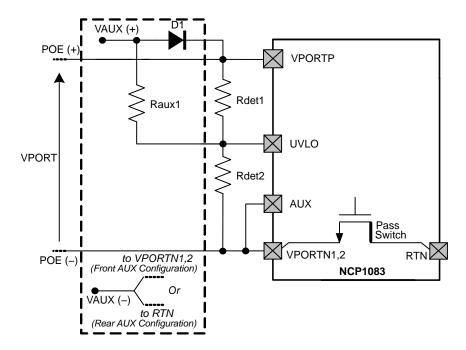

#### **FRONT Auxiliary Supply Connection**

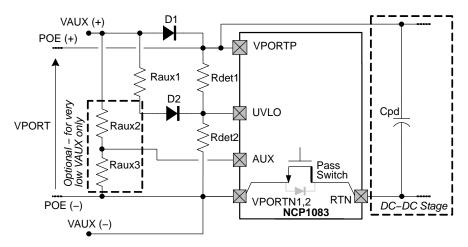

In this case VAUX is inserted between VPORTP & VPORTN<sub>1,2</sub> (see Figure 1). This topology is very similar to a standard POE configuration. The controlled  $C_{pd}$  charging and the current limitation during the PWM operation are still supported by this configuration. This configuration is recommended when the VAUX supply is in the same range as the PoE input voltage but can also be used for low auxiliary supply voltage if the pass switch can handle the input current.

Figure 1. FRONT Auxiliary Supply Configuration

#### **REAR Auxiliary Supply Connection**

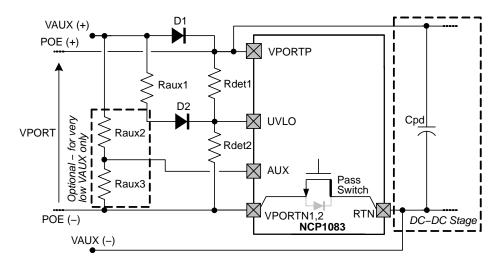

In this case VAUX is inserted between VPORTP & RTN (see Figure 2). When VAUX is connected, the VPORTN $_{1,2}$  pins will be pulled low due to the forward biased bulk-drain diode of the Pass switch. The bulk-drain diode will conduct till the VPORT voltage crosses the external UVLO threshold. Passing the UVLO threshold turns the Pass Switch on and connects VPORTN $_{1,2}$  to RTN pins.

The inrush current in the  $C_{pd}$  capacitor and the operational current are not controlled since the Pass switch is by passed by VAUX. Extra current limitation method might be necessary in order to protect the VAUX supply and/or the  $C_{pd}$  capacitor from large inrush current.

This configuration is suitable for low VAUX supply implementation combined with a current level that can not be supported by the pass switch of the NCP1082 or NCP1082.

Figure 2. REAR Auxiliary Supply Configuration

#### **DIRECT Auxiliary Supply Connection**

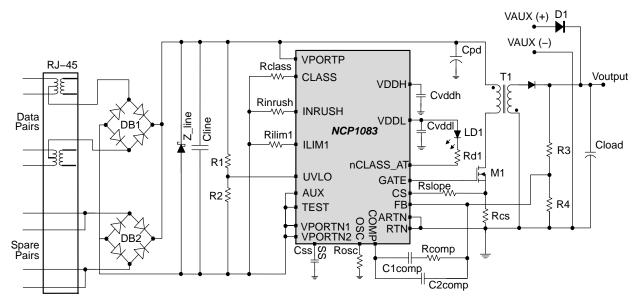

In this case VAUX is inserted on the output of the converter (see Figure 3). Since there is no power distribution over the Ethernet cable the DC-DC converter of the

NCP108x is off. Additional detection circuitry needs to be implemented to switch off the PoE converter in case the auxiliary supply is connected.

Figure 3. Direct Auxiliary Supply Configuration

#### **External Component Configuration**

There are different types of wall warts and auxiliary supplies with a variety of output voltages. To make sure that the input voltage range is supported by DC-DC controller of the NCP1082 and NCP1083 there are two configurations possible dependant on the auxiliary supply voltage ranges.

- VAUX Supply with 9 V < VAUX<sub>(min,max)</sub> Range < 18 V

- VAUX Supply with VAUX<sub>(min,max)</sub> Range > 13.5 V

AUX Configuration with 9 V < VAUX $_{(min,max)}$  < 18 V

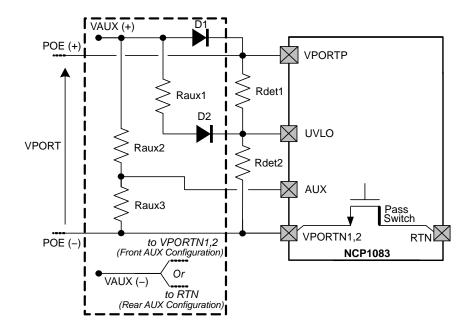

Figure 4 illustrates the necessary additional external components to enable auxiliary supply to support a minimum VAUX voltage down to 9 VDC which guarantee a minimum VPORTP-ARTN voltage of 8.5 VDC (assuming a  $V_{D1max}$  of 0.5 V).

Figure 4. External Components for AUX Usage with Min 9 V < VAUX<sub>(min,max)</sub> < 18 V

The AUX and UVLO pins have to be connected to two resistor ladders:

- The first resistor ladder R<sub>aux2</sub>-R<sub>aux3</sub> has to be defined such that AUX pin is min 1.5 V when VPORT reaches 8.5 V, and max 3.3 V at VAUX<sub>(max)</sub>. The voltage on AUX generates following functions:

- The detection mode is disabled in order to have the internal regulator and biasing cells operating at low VPORT voltage.

- The Dual finger classification state machine and the nCLASS\_AT pin are locked and will not react on fake classification-mark range sequences.

- The second resistor ladder is  $R_{aux1}-R_{det1}-R_{det2}$  on the UVLO pin.  $R_{det1}-R_{det2}$  has a total resistance of 25.5 k $\Omega$ . The  $R_{aux1}$  value has to be defined such that UVLO pin is minimum 1.2 V at when the auxiliary supply is switched on. Having this voltage on UVLO assures that the PWM operation is enabled.

$$\mathsf{R}_{\mathsf{aux3}} = \frac{\mathsf{R}_{\mathsf{aux2}} \cdot \mathsf{V}_{\mathsf{t}}}{\mathsf{V}_{\mathsf{aux}} - \mathsf{V}_{\mathsf{dp}} - \mathsf{V}_{\mathsf{t}}}$$

$$R_{aux1} = \frac{V_{aux} - V_{dp} - V_{d} - V_{t}}{\frac{V_{t}}{845} - \frac{V_{aux} - V_{dp} - V_{d} - V_{t}}{24 \text{ K}}}$$

$$R_{aux1} = 20 \text{ K}\Omega$$

With  $V_d$  is the voltage drop over the rectifiers and masking diodes (typical 0.6 V), and  $V_{dp} = 0.5$  V the forward voltage drop of the NCP1082-3 internal diode, and  $V_t$  is the desired voltage at the AUX pin.

The diode D2 is used to not corrupt the PD detection signature during the PSE detection phase when VAUX is not present.

In case a full range of auxiliary input voltages is required (say 9 V until 57 V), additional zener diodes need to be mounted to protect the AUX and UVLO pins from exceeding the maximum voltage of 3.3 V.

#### AUX Configuration with VAUX, Minimal > 13.5 V

In case VAUX is minimal 13.5 V, VPORTP voltage will be above 13 V during PWM operation. The external components can be reduced as illustrated in Figure 5. The resistor ladder on AUX is not required since the VPORT input supply is always above the detection voltage range. Moreover, the nCLASS\_at pin will not be falsely triggered since the Mark range threshold will not be crossed.

The AUX pin can be strapped to VPORTN<sub>1,2</sub> pins, and D2 is not anymore needed since there will be no current flowing in  $R_{aux1}$  when VAUX is not present.

Figure 5. External Components for AUX Usage with VAUX<sub>(min,max)</sub> > 13.5 V

The  $R_{det1}$ - $R_{det2}$ - $R_{aux1}$  ladders are calculated in the same way as above.

#### Auxiliary Supply & nClass\_AT pin function

As general rule, when VAUX supplies the device and if AUX resistor ladder is used, the nCLASS\_AT state is locked to its current state. We can distinguish two different scenarios:

First one is the case where the device is powered-up and supplied by VAUX only. The nCLASS\_AT state will be locked to the default one which is the disabled state (pulled-up to VDDL).

Second one is the case where VAUX is plugged on a device which is already supplied by a type 2 PSE with dual finger classification capability. The nCLASS\_AT pin will remain active (=low) after the VAUX connection.

Important note: in order to not suffer from unexpected behavior on the nCLASS\_AT pin, it is necessary to use and well configure the resistor ladder on AUX pin if VPORT can go down below 13 V during PWM operation.

#### **Auxiliary Supply & POE Priorities**

#### VAUX Connected before POE

As soon as the device is supplied by VAUX, it can not be detected as PoE-PD by the PSE because the PD detection signature will not be valid (due to internal current consumption in Power Mode). VAUX has to be disconnected in order to allow the detection and power up of the device by a PSE.

#### POE Connected before VAUX Insertion

In case VAUX is inserted on the device which is powered by a PSE, the application will stay supplied by the PSE except for the case where the VAUX voltage is higher than the PSE voltage. In this specific case, due to higher voltage on the VAUX, the current in the cable will drop and cross the DC disconnect range of the PSE (see IEEE802.3af/at standard for more details) which will then remove the power from the cable.

ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative