### **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# LC87F1M16A USB Application Note

2012/09/05 SANYO Semiconductor Co., Ltd. LSI Division

Microcontroller & Flash Development Dept.

## Contents

| Chapter 1. Initialization                       | 1-1  |

|-------------------------------------------------|------|

| 1.1. Control Program Overview                   | 1-2  |

| 1.2. Related Registers                          | 1-3  |

| 1.3. Initializing the LC87F1M16A                | 1-4  |

| 1.4. Initializing the USB Functions             |      |

| Chapter 2. State Transitions and Interrupts     | 2-1  |

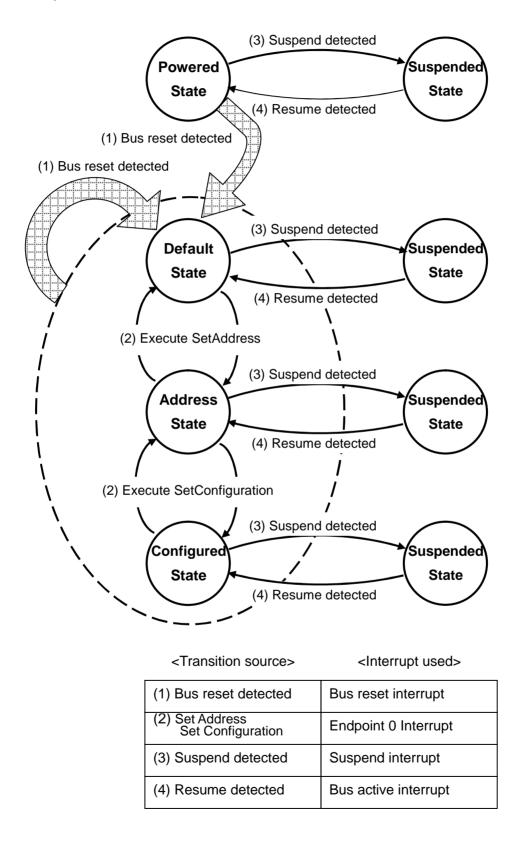

| 2.1. Device State Transition                    | 2-2  |

| 2.1.1 Device Status                             | 2-3  |

| 2.1.2 Transition Ssources                       | 2-5  |

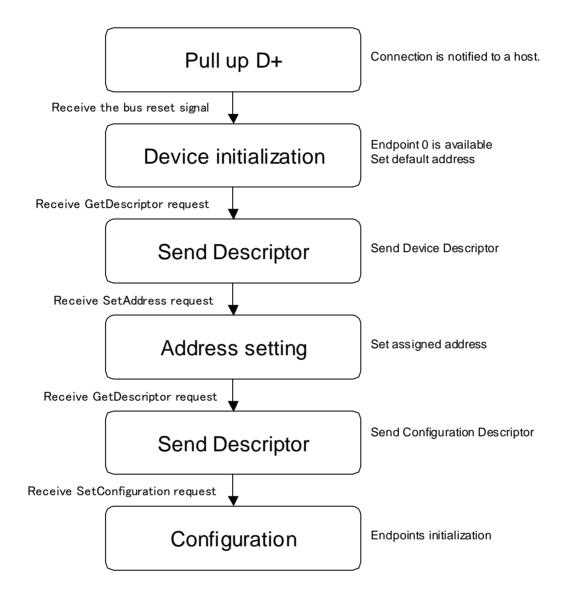

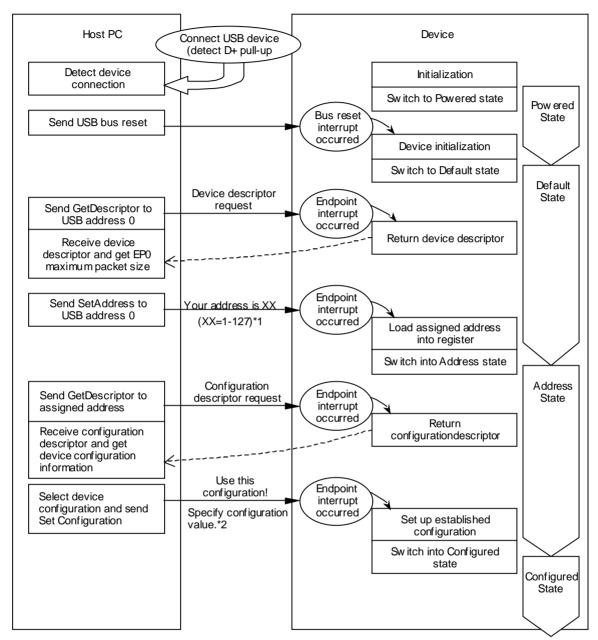

| 2.2. Bus Enumeration                            | 2-6  |

| 2.3. USB Interrupts                             | 2-8  |

| 2.3.1 Overview                                  | 2-8  |

| 2.3.2 Related Registers                         | 2-10 |

| 2.4. USB Bus Reset Interrupt                    | 2-12 |

| 2.5. Endpoint Interrupts                        | 2-14 |

| 2.5.1 Endpoint n ACK interrupts                 |      |

| 2.6. Suspend Interrupts                         |      |

| 2.7. USB Bus Active Interrupt (Resume Detected) |      |

| 2.8. Remote Wakeup                              |      |

| 2.0. Remote Wakeup                              | 2-20 |

| Chapter 3. Control Transfers                    | 3-1  |

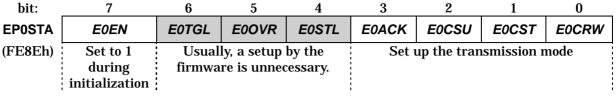

| 3.1. Endpoint 0 Control                         | 3-2  |

| 3.1.1. Related Registers                        | 3-2  |

| 3.1.2. Endpoint 0                               | 3-4  |

| 3.2. Outline of Control Transfer                | 3-5  |

| 3.2.1. Stage Transitions                        | 3-5  |

| 3.2.2. Transaction Configuration                |      |

| 3.2.3. Endpoint 0 Initialization                |      |

| 3.2.4. Control Transfers Processing             |      |

| 3.2.5. Setting Up the Transmission Mode         |      |

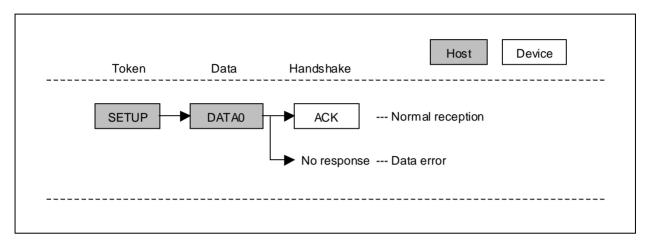

| 3.3. Setup stage                                |      |

| 3.3.1. Outline of Setup stage SETUP transaction |      |

| 3.3.2. SETUP Operation                          |      |

| 3.3.4. Receive Errors                           |      |

| 3.4. Control Write Transfer Data Stage          |      |

| 3.4.1. Outline of Data stage OUT transaction    |      |

| 3.4.2. Data OUT Setup                           |      |

| 3.4.3. Data OUT Operation                       |      |

| 3.4.4. Data OUT Processing                      |      |

| 3.4.5. Receive Errors                                | 3-21 |

|------------------------------------------------------|------|

| 3.5. Control Write and No Data Transfer Status Stage | 3-22 |

| 3.5.1. Outline of Status stage IN transaction        | 3-22 |

| 3.5.2. Status IN Setup                               |      |

| 3.5.3. Status IN Operation                           | 3-23 |

| 3.5.4. Status IN Processing                          | 3-24 |

| 3.5.5. Transmission Errors                           | 3-25 |

| 3.6. Control Read Transfer Data Stage                | 3-26 |

| 3.6.1. Outline of Data stage IN transaction          | 3-26 |

| 3.6.2. Data IN Setup                                 | 3-26 |

| 3.6.3. Data IN Operation                             |      |

| 3.6.4. Data IN Processing                            | 3-28 |

| 3.6.5. Transmission Errors                           | 3-28 |

| 3.7. Control Read Transfer Status Stage              | 3-29 |

| 3.7.1. Outline of Status stage OUT transaction       |      |

| 3.7.2. Status OUT Setup                              | 3-29 |

| 3.7.3. Status OUT Operation                          | 3-30 |

| 3.7.4. Status OUT Processing                         |      |

| 3.7.5. Receive Errors                                | 3-31 |

| Objection A. Bota Transfers                          | 4.4  |

| Chapter 4. Data Transfers                            | 4-1  |

| 4.1. Endpoint Control                                | 4-2  |

| 4.1.1. Related registers                             |      |

| 4.1.2. Endpoints 1-6                                 |      |

| 4.1.3. Setting Up the Transmission Mode              |      |

| 4.2. Outline of Bulk Transfer                        | 4-7  |

| 4.2.1. Outline of Process                            | 4-8  |

| 4.2.2. Endpoint n Initialization (bulk transfer)     |      |

| 4.2.3. Endpoint Descriptor Example                   | 4-10 |

| 4.3. Bulk IN Transfers                               | 4-11 |

| 4.3.1. Bulk IN Setup                                 | 4-11 |

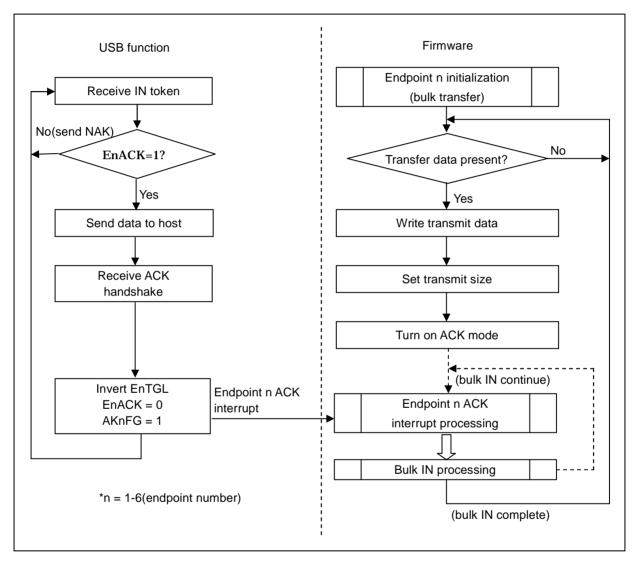

| 4.3.2. Bulk IN Operation                             |      |

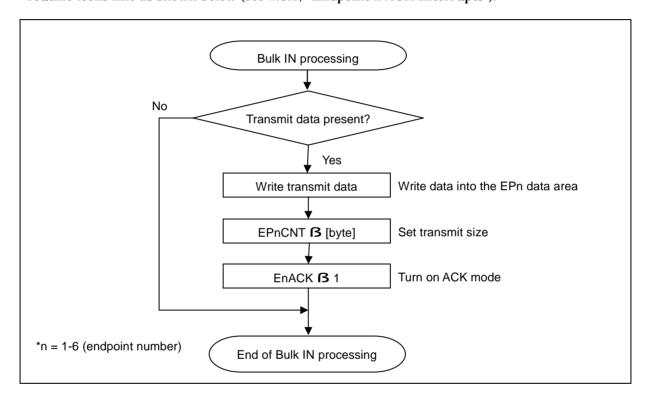

| 4.3.3. Bulk IN Processing                            |      |

| 4.3.4. Transmission Errors                           | 4-13 |

| 4.4. Bulk OUT Transfers                              | 4-14 |

| 4.4.1. Bulk OUT Setup                                | 4-14 |

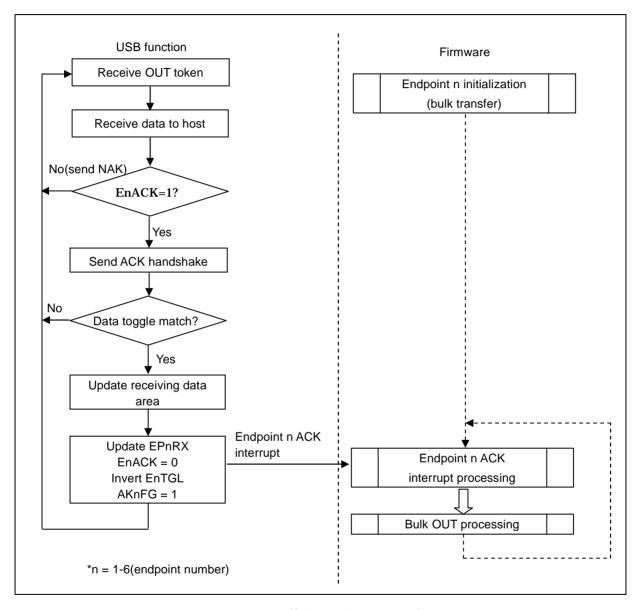

| 4.4.2. Bulk OUT Operation                            | 4-15 |

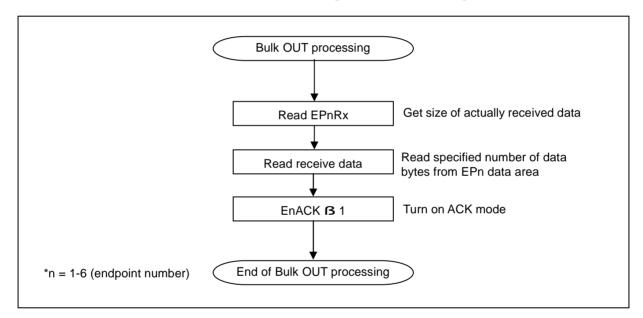

| 4.4.3. Bulk OUT Processing                           | 4-16 |

| 4.4.4. Receive Errors                                | 4-17 |

| 4.5. Outline of Interrupt Transfer                   | 4-18 |

| 4.5.1. Outline of Process                            | 4-19 |

| 4.5.2. Endpoint n Initializaion (interrupt transfer) |      |

| 4.5.3. Endpoint Descriptor Example                   |      |

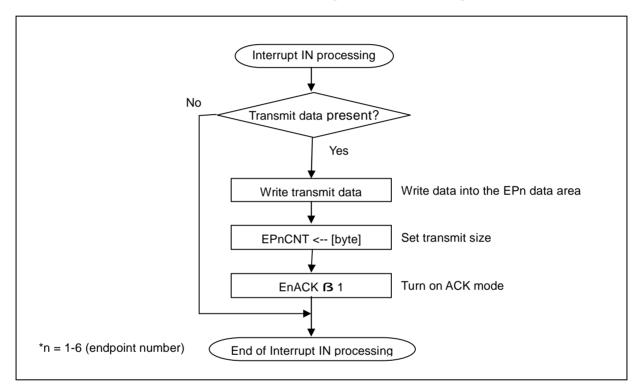

| 4.6. Interrupt IN Transfers                          | 4-22 |

| 4.6.1. Interrupt IN Setup                            | 4-22 |

| 4.6.2. Interrupt IN Operation                        | 4-23 |

| 4.6.3. Interrupt IN Processing                       | 4-24 |

| 4.6.4 Transmission Errors                            | 1-21 |

09/05/12 Contents

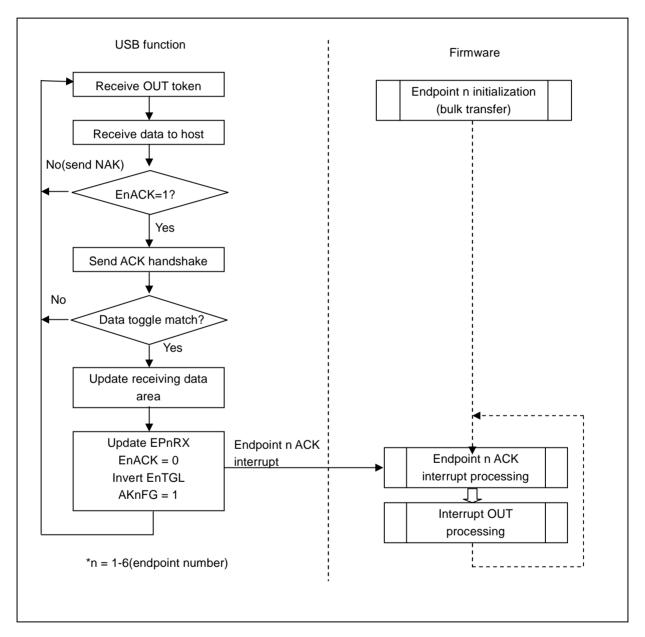

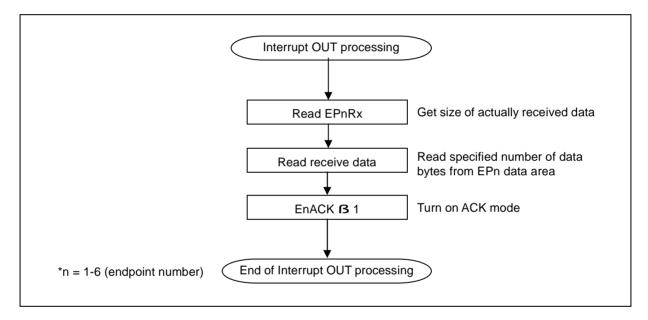

| 4.7. Interrupt OUT Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-25                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 4.7.1. Interrupt OUT Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-25                                                        |

| 4.7.2. Interrupt OUT Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-26                                                        |

| 4.7.3. Interrupt OUT Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-27                                                        |

| 4.7.4. Receive Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-28                                                        |

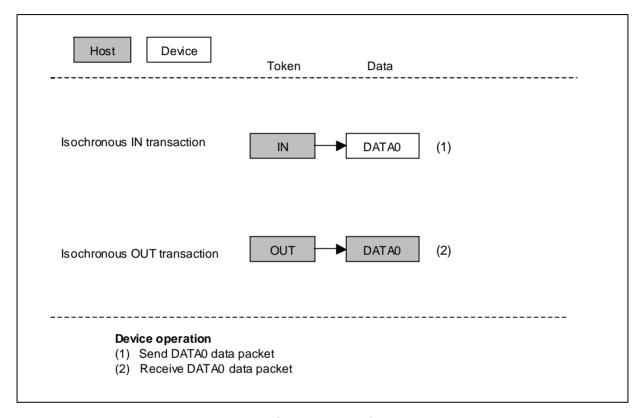

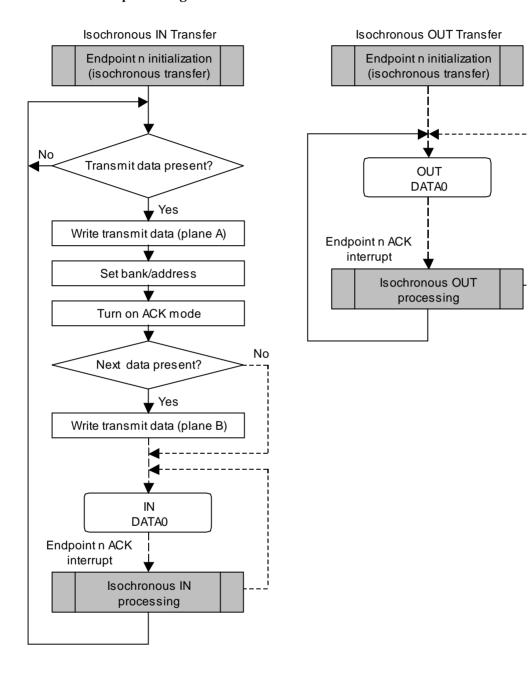

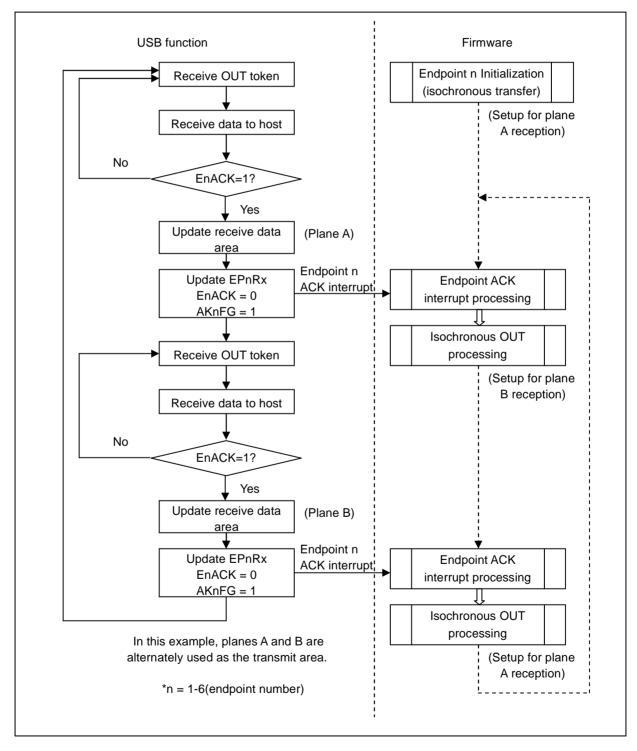

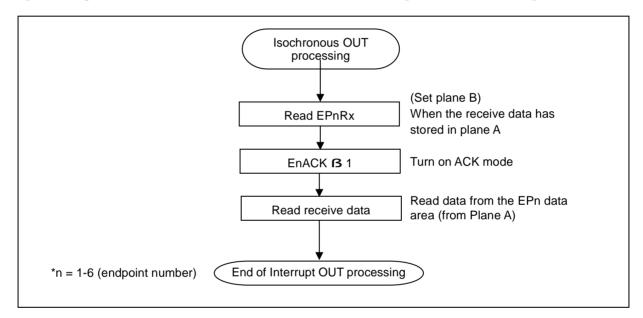

| 4.8. Outline of Isochronous Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4-29                                                        |

| 4.8.1. Outline of Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4-30                                                        |

| 4.8.2. Endpoint n Initializaion (isochronous transfer)                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-31                                                        |

| 4.8.3. Endpoint Descriptor Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-32                                                        |

| 4.8.4. Endpoint Data Areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4-33                                                        |

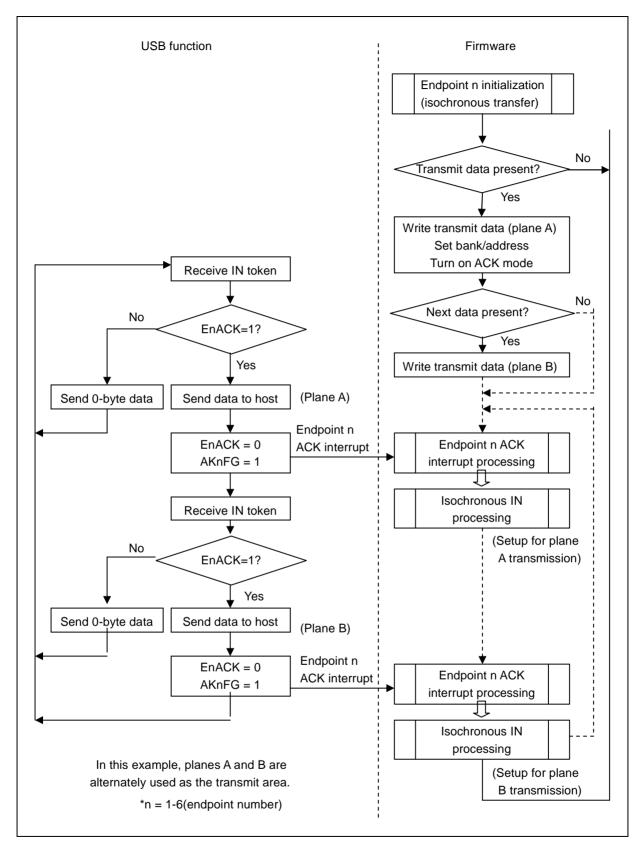

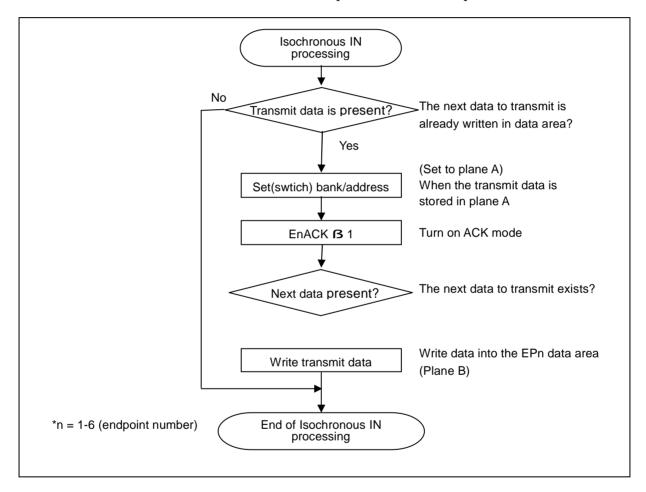

| 4.9. Isochronous IN Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-34                                                        |

| 4.9.1. Isochronous IN Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-34                                                        |

| 4.9.2. Isochronous IN Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-34                                                        |

| 4.9.3. Isochronous IN Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-36                                                        |

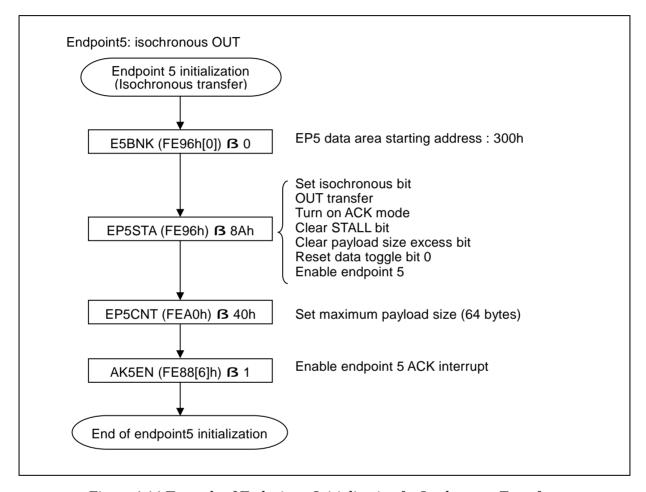

| 4.10. Isochronous OUT Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-37                                                        |

| 4.10.1. Isochronous OUT Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-37                                                        |

| 4.10.2. Isochronous OUT Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |

| 4.10.3. Isochronous OUT Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-39                                                        |

| Chapter 5.Appendix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-1                                                         |

| 5.1. LC87F1M16A RAM Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

| 5.2 Example of Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-3                                                         |

| 5.2. Example of Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-3                                                         |

| 5.2. Example of Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-3                                                         |

| Figures and Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-3                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-3                                                         |

| Figures and Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4                                                  |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4                                                  |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4<br>1-5                                           |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4<br>1-5                                           |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4<br>1-5<br>1-3                                    |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4<br>1-5<br>1-3<br>1-6                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration Figure 1-2 LC87F1M16A Initialization Example Figure 1-3 USB Initialization Example  Table 1-1 Initialization Related Registers Table 1-2 Endpoint Configuration (EPBMOD=0) Table 1-3 Endpoint Configuration (EPBMOD=1) Table 1-4 Endpoint Configuration (EPBMOD=2) Table 1-5 Endpoint Configuration (EPBMOD=3) Table 1-6 Endpoint Configuration (EPBMOD=4) Table 1-7 Endpoint Configuration (EPBMOD=5) | 1-2<br>1-4<br>1-5<br>1-3<br>1-6<br>1-6<br>1-6<br>1-7<br>1-7 |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        | 1-2<br>1-4<br>1-5<br>1-6<br>1-6<br>1-6<br>1-7<br>1-7        |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration Figure 1-2 LC87F1M16A Initialization Example Figure 1-3 USB Initialization Example  Table 1-1 Initialization Related Registers Table 1-2 Endpoint Configuration (EPBMOD=0) Table 1-3 Endpoint Configuration (EPBMOD=1) Table 1-4 Endpoint Configuration (EPBMOD=2) Table 1-5 Endpoint Configuration (EPBMOD=3) Table 1-6 Endpoint Configuration (EPBMOD=4) Table 1-7 Endpoint Configuration (EPBMOD=5) |                                                             |

| Figures and Tables  Chapter 1. Initialization  Figure 1-1 Sample Control Program Configuration                                                                                                                                                                                                                                                                                                                                                                                                        |                                                             |

| Figure 2-3 Example of Bus Enumeration Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-6                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-7                                                                                          |

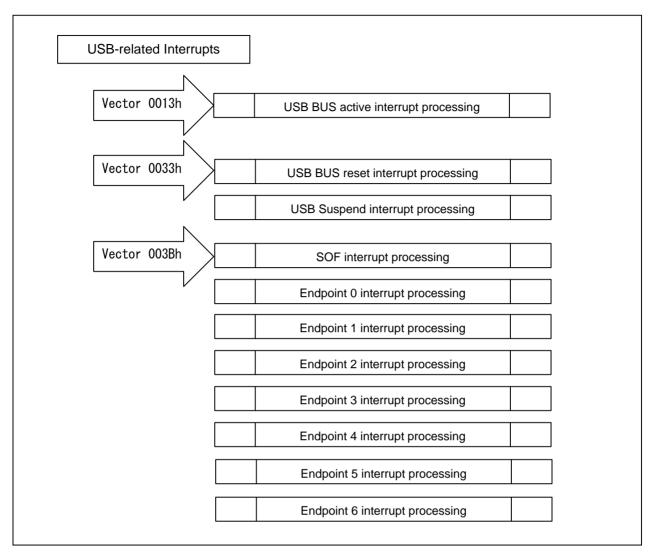

| Figure 2-4 USB-related Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-9                                                                                          |

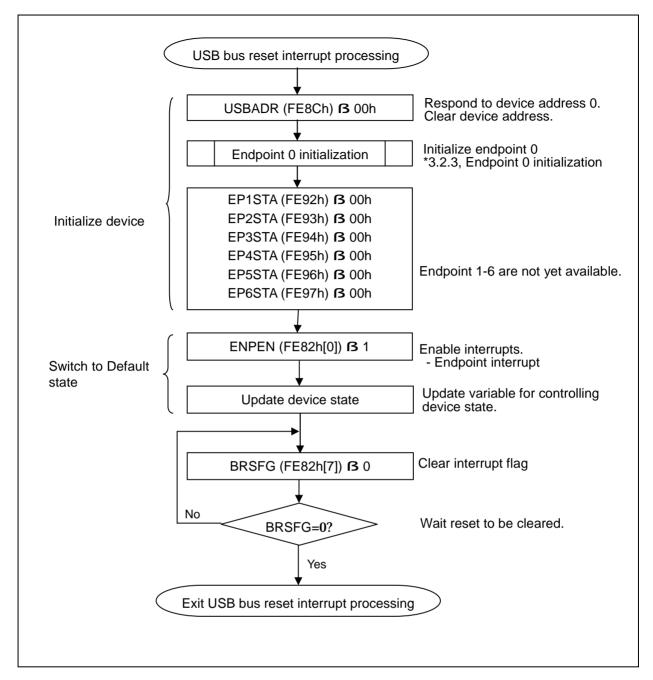

| Figure 2-5 Example of USB Bus Reset Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-13                                                                                         |

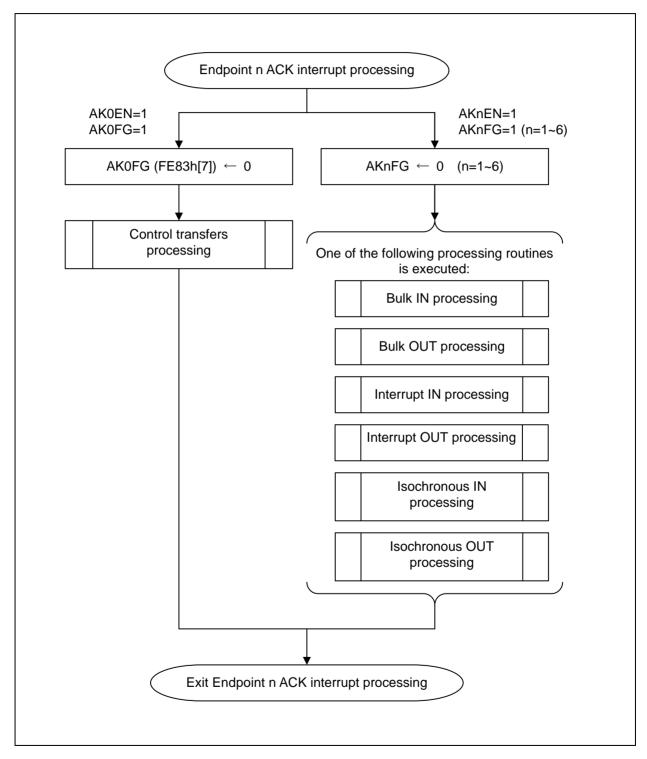

| Figure 2-6 Example of Endpoint n ACK Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-15                                                                                         |

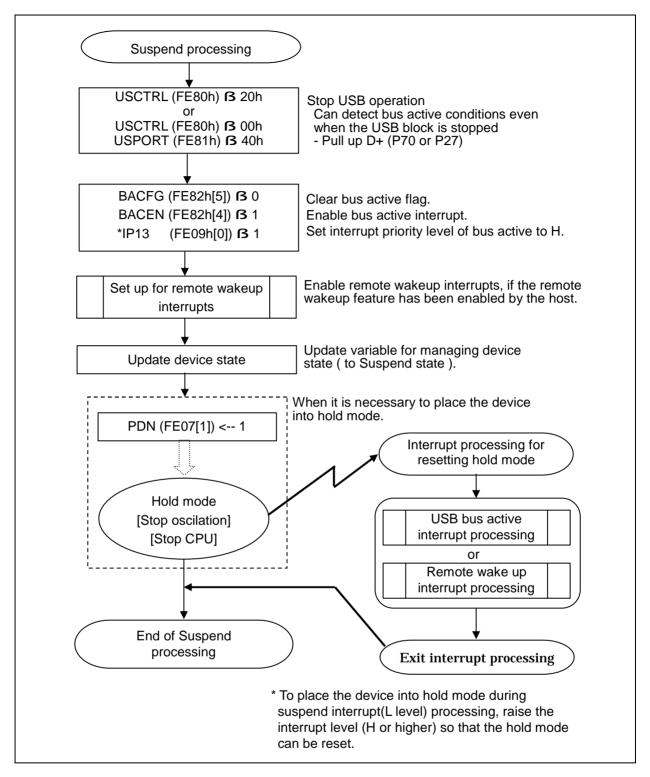

| Figure 2-7 Example of Suspend Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2-17                                                                                         |

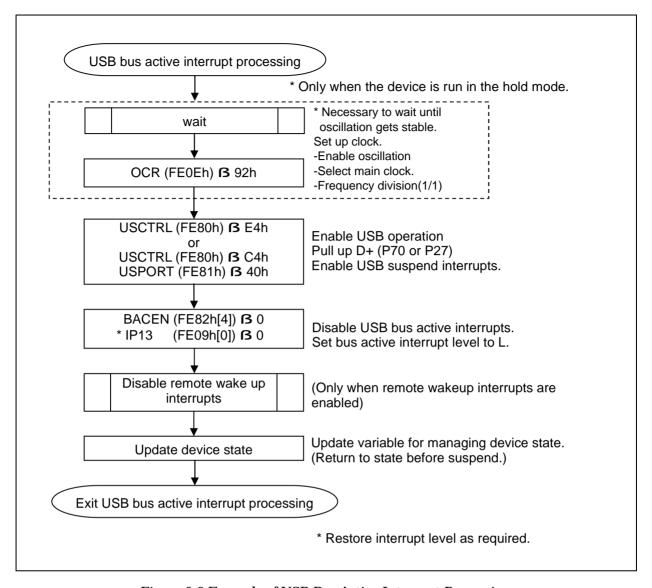

| Figure 2-8 Example of USB Bus Active Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

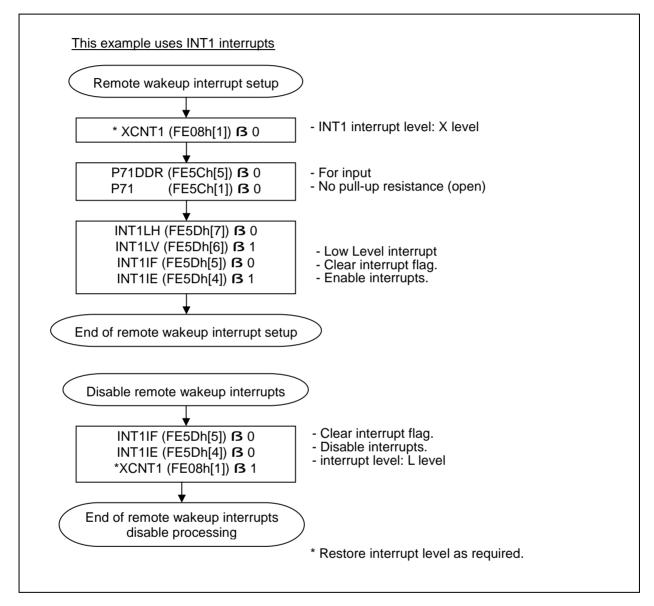

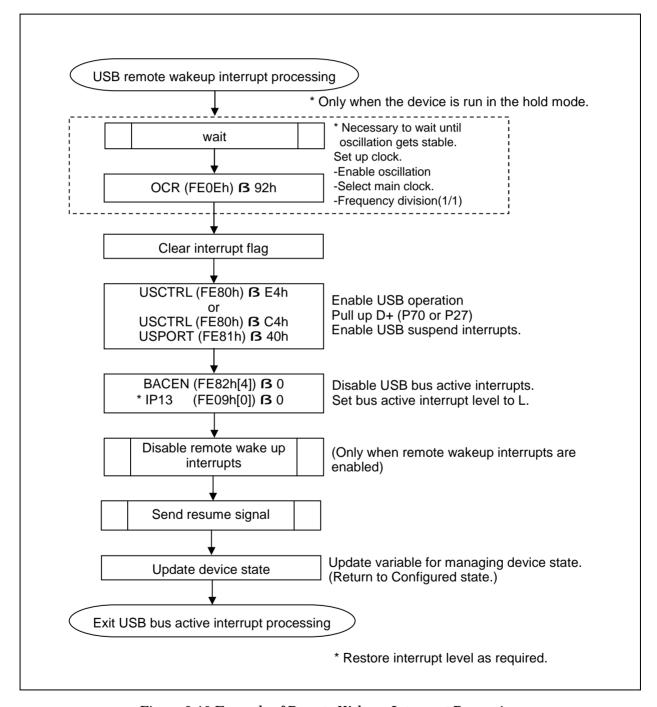

| Figure 2-9 Example of Setting the Device for Remote Wakeup Interrupts (INT0 Interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-21                                                                                         |

| Figure 2-10 Example of Remote Wakeup Interrupt Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

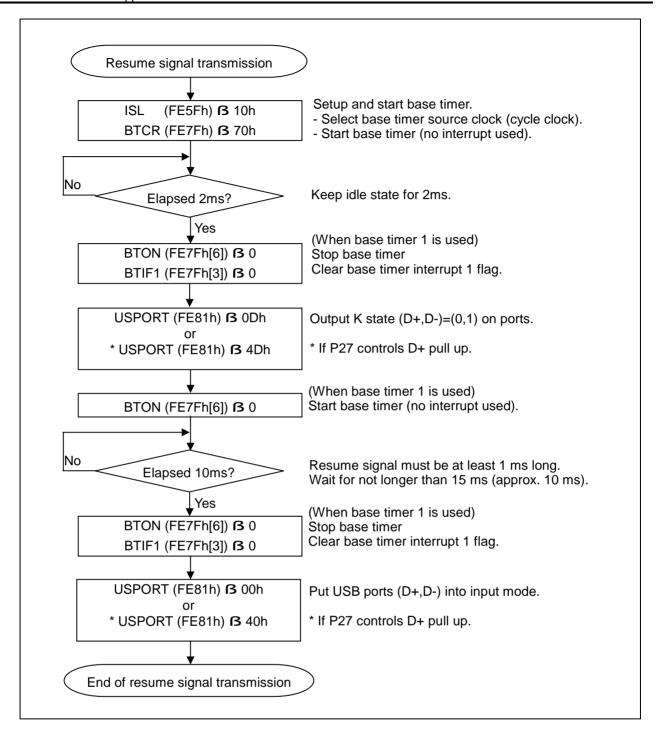

| Figure 2-11 Resume Signal Transmission Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2-24                                                                                         |

| Table 2-1 Device States and Transition Sources (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-3                                                                                          |

| Table 2-2 Device States and Transition Sources (2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

| Table 2-3 USB interrupts list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| Table 2-4 USB interrupts related Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| Table 2-5 USB operation conrtol register Function list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| Table 2-6 USB interrupt register Function list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                              |

| Table 2-7 Endpoint n interrupt register Function list                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| Table 2-8 Interrupts list for Returning from the Hold Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                              |

| Chapter 3. Control Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                              |

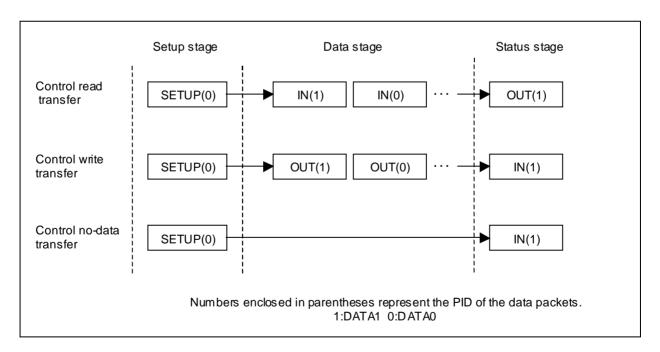

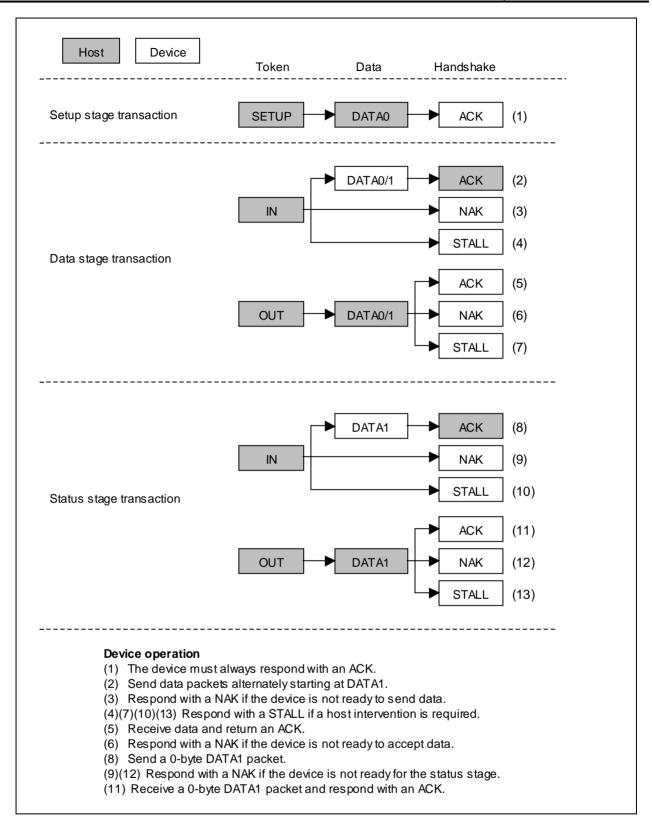

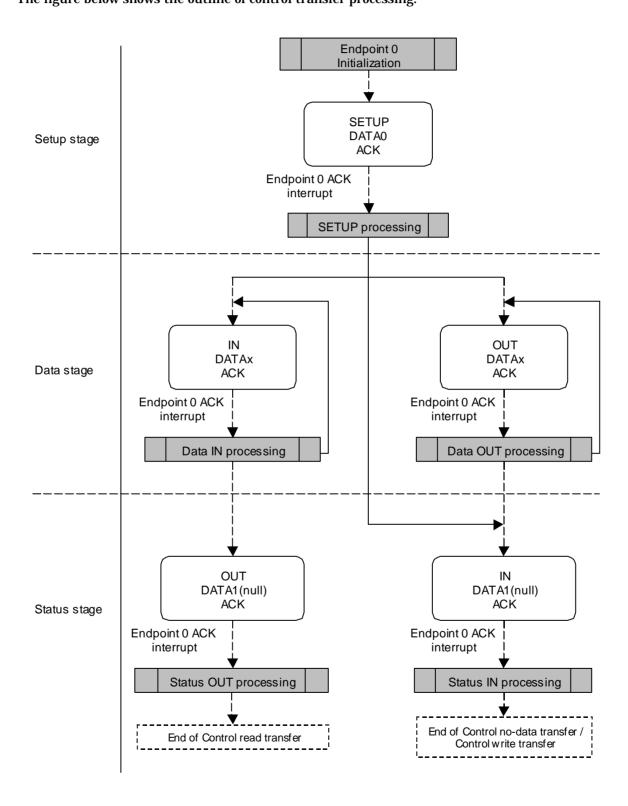

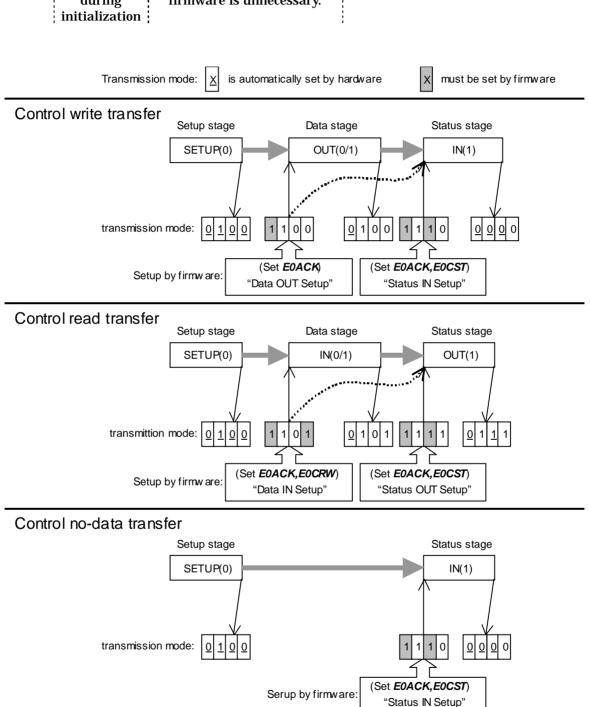

| Figure 3-1 Control Transfer Stage Transitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-5                                                                                          |

| Figure 3-2 Stages of a Control Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-7                                                                                          |

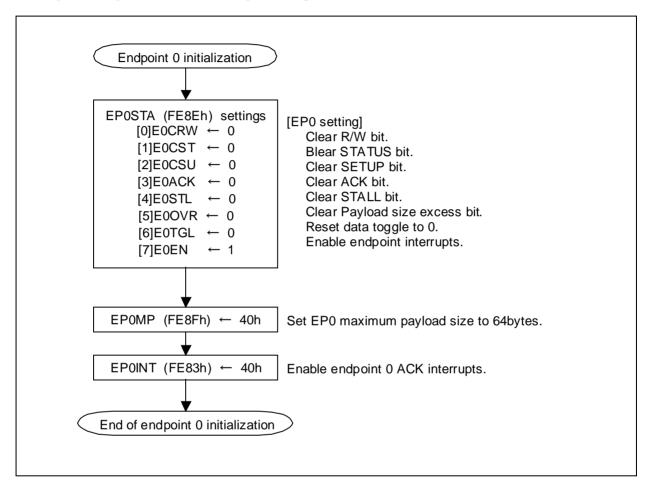

| Figure 3-3 Example of Endpoint 0 Initialization Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-0                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

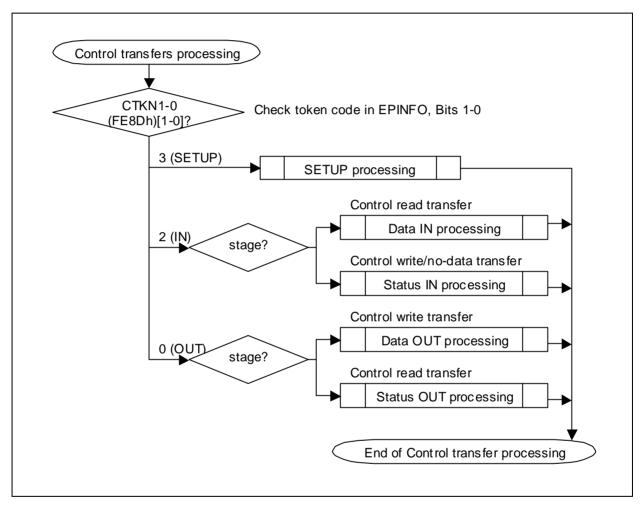

| Figure 3-4 Example of Control Transfers Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                              |

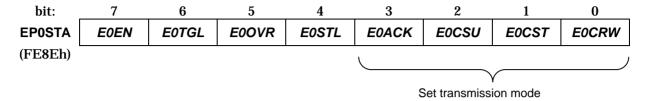

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10<br>3-13                                                                                 |

| Figure 3-4 Example of Control Transfers Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-10<br>3-13                                                                                 |

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-10<br>3-13<br>3-14                                                                         |

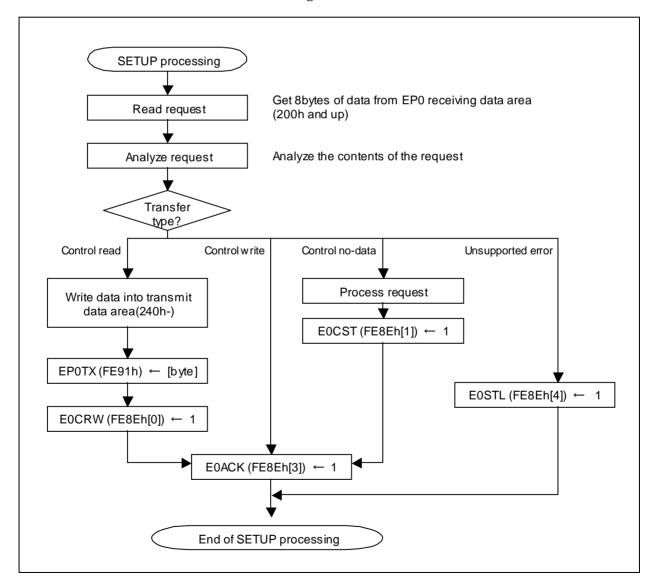

| Figure 3-4 Example of Control Transfers Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-10<br>3-13<br>3-14<br>3-15                                                                 |

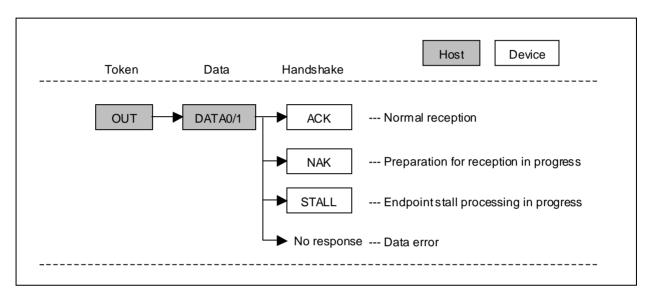

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-10<br>3-13<br>3-14<br>3-15<br>3-16                                                         |

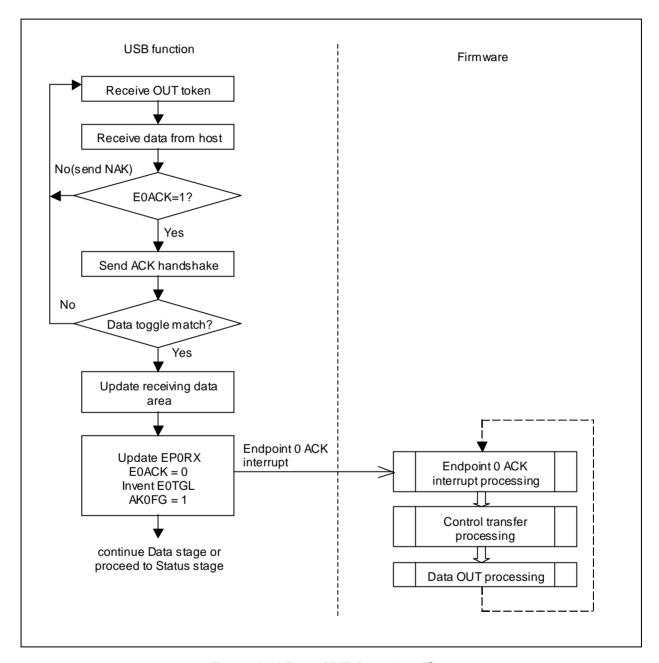

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-18                                                 |

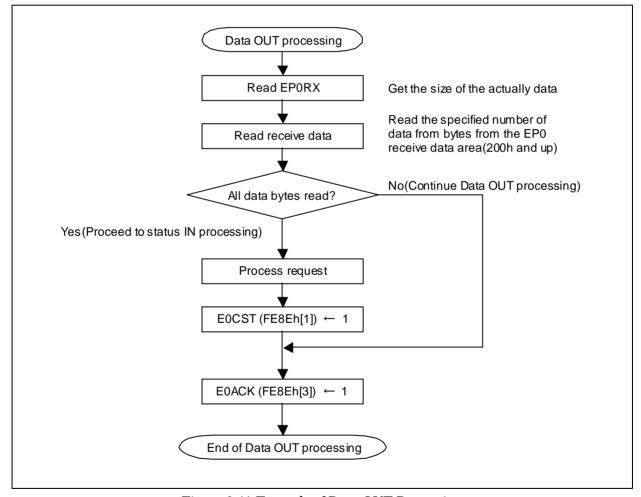

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure_3-11 Example of Data OUT Processing                                                                                                                                                                                                                                                                                                                                                                                                       | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-18<br>3-19<br>3-20                                 |

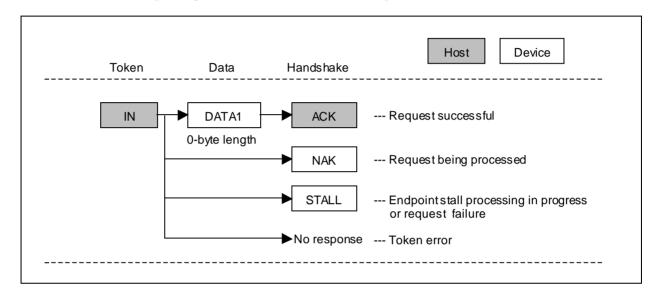

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure_3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction                                                                                                                                                                                                                                                                                                                                                                    | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-18<br>3-19<br>3-20<br>3-22                         |

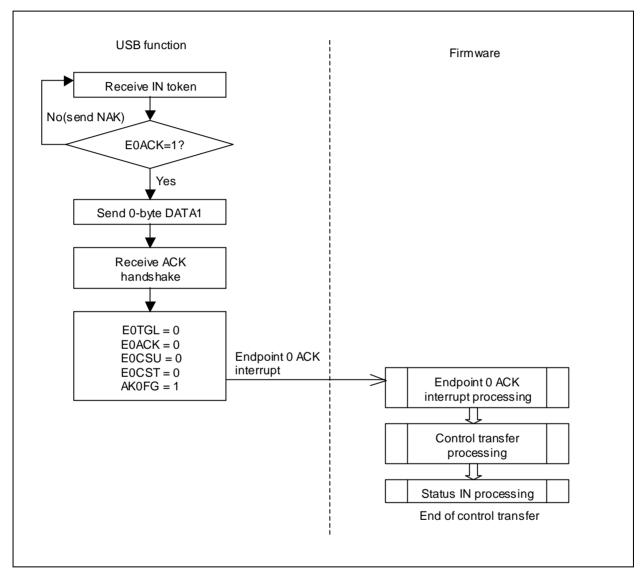

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure 3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction  Figure 3-13 Status IN Operation Flow                                                                                                                                                                                                                                                                                                                              | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-18<br>3-19<br>3-20<br>3-22<br>3-23                 |

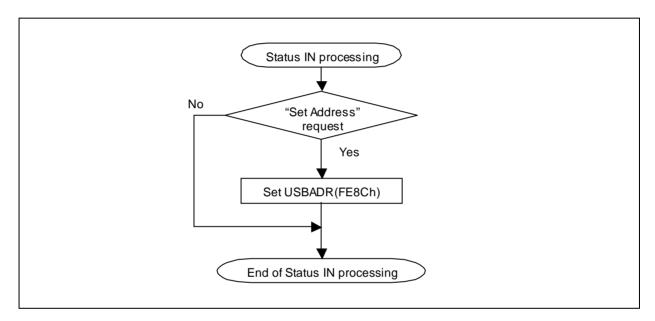

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure 3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction  Figure 3-13 Status IN Operation Flow  Figure 3-14 Example of Status IN Processing                                                                                                                                                                                                                                                                                 | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-19<br>3-20<br>3-22<br>3-23<br>3-24                 |

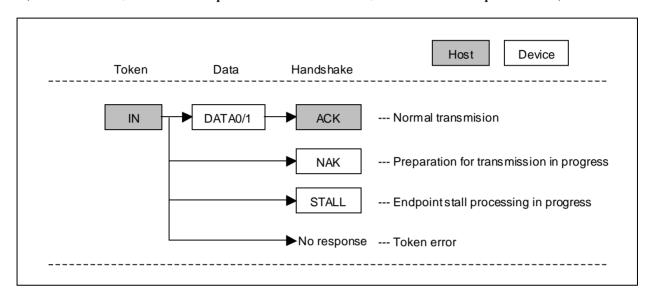

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure 3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction  Figure 3-13 Status IN Operation Flow  Figure 3-14 Example of Status IN Processing  Figure 3-15 Data IN Transaction                                                                                                                                                                                                                                                | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-18<br>3-19<br>3-20<br>3-22<br>3-23<br>3-24         |

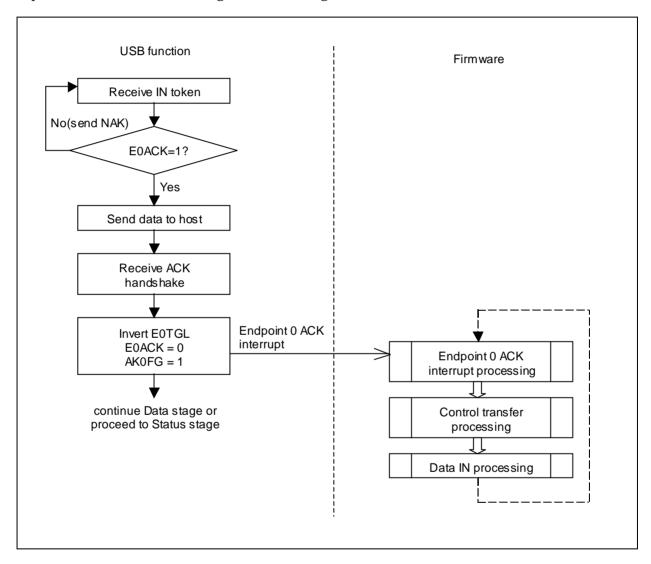

| Figure 3-4 Example of Control Transfers Processing  Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction  Figure 3-7 SETUP Operation Flow  Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction  Figure 3-10 Data OUT Operation Flow  Figure_3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction  Figure 3-13 Status IN Operation Flow  Figure 3-14 Example of Status IN Processing  Figure 3-15 Data IN Transaction  Figure 3-16 Data IN Transaction  Figure 3-16 Data IN Operation Flow                                                                                                                                                                           | 3-10<br>3-13<br>3-14<br>3-15<br>3-16<br>3-19<br>3-20<br>3-22<br>3-23<br>3-24<br>3-26<br>3-27 |

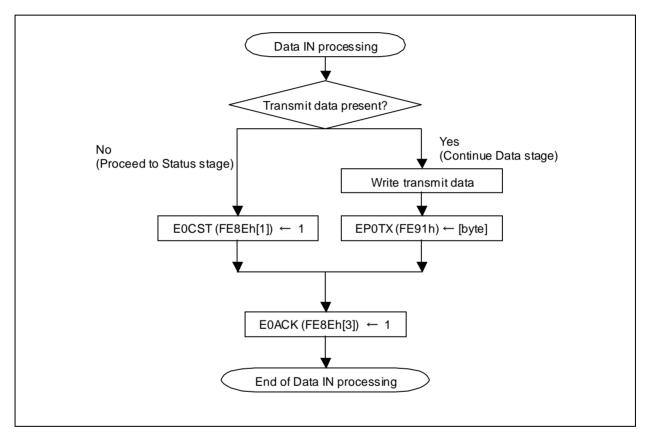

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing Figure 3-15 Data IN Transaction Figure 3-16 Data IN Operation Flow Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing                                                                                                                                           | 3-10 3-13 3-14 3-15 3-16 3-19 3-20 3-22 3-23 3-24 3-26 3-27 3-28                             |

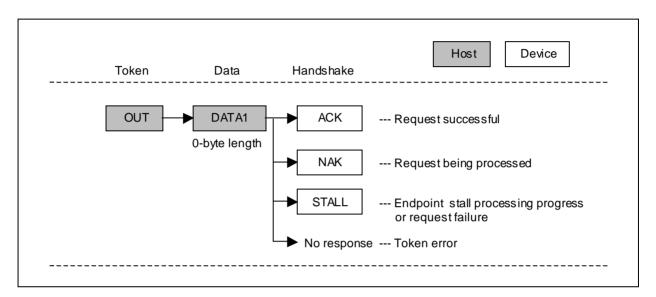

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing Figure 3-15 Data IN Transaction Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing Figure 3-18 Status OUT Transaction                                                                                                                                           | 3-10 3-13 3-14 3-15 3-16 3-18 3-20 3-22 3-23 3-24 3-26 3-27 3-28 3-29                        |

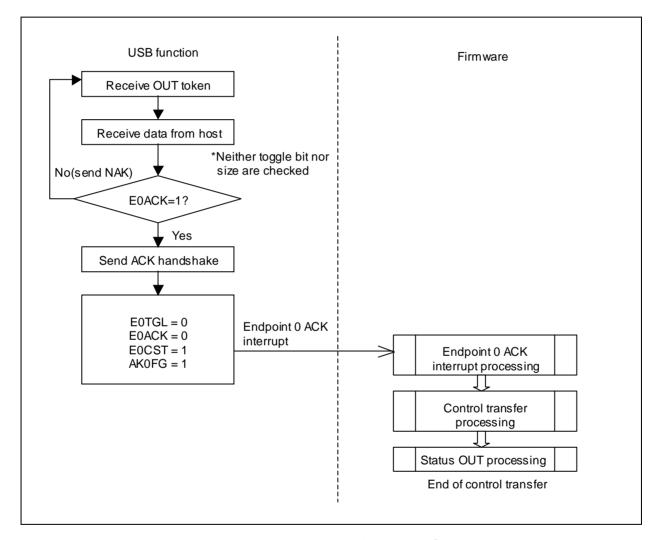

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing Figure 3-15 Data IN Transaction Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing Figure 3-18 Status OUT Transaction Figure 3-19 Status OUT Operation Flow Figure 3-19 Status OUT Operation Flow Figure 3-19 Status OUT Operation Flow                         | 3-10 3-13 3-14 3-15 3-16 3-19 3-20 3-22 3-23 3-24 3-26 3-27 3-28 3-29 3-30                   |

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing Figure 3-15 Data IN Transaction Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing Figure 3-18 Status OUT Transaction                                                                                                                                           | 3-10 3-13 3-14 3-15 3-16 3-19 3-20 3-22 3-23 3-24 3-26 3-27 3-28 3-29 3-30                   |

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing Figure 3-15 Data IN Transaction Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing Figure 3-18 Status OUT Transaction Figure 3-19 Status OUT Operation Flow Figure 3-19 Status OUT Operation Flow Figure 3-19 Status OUT Operation Flow                         | 3-10 3-13 3-14 3-15 3-16 3-19 3-20 3-22 3-23 3-24 3-26 3-27 3-28 3-30 3-31                   |

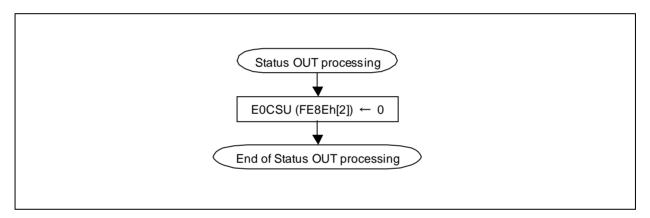

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow  Figure 3-6 SETUP Transaction Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing  Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow  Figure 3-11 Example of Data OUT Processing  Figure 3-12 Status IN Transaction  Figure 3-13 Status IN Operation Flow  Figure 3-14 Example of Status IN Processing  Figure 3-15 Data IN Transaction  Figure 3-16 Data IN Operation Flow  Figure 3-17 Example of Data IN Processing  Figure 3-18 Status OUT Transaction  Figure 3-19 Status OUT Operation Flow  Figure 3-20 Example of Status OUT Processing                                            | 3-103-133-143-153-163-183-203-223-233-243-263-273-283-293-31                                 |

| Figure 3-4 Example of Control Transfers Processing Figure 3-5 Transmission Mode Setting Flow. Figure 3-6 SETUP Transaction. Figure 3-7 SETUP Operation Flow Figure 3-8 Example of SETUP Processing. Figure 3-9 Data OUT Transaction Figure 3-10 Data OUT Operation Flow. Figure 3-11 Example of Data OUT Processing Figure 3-12 Status IN Transaction Figure 3-13 Status IN Operation Flow Figure 3-14 Example of Status IN Processing. Figure 3-15 Data IN Transaction. Figure 3-16 Data IN Operation Flow Figure 3-17 Example of Data IN Processing. Figure 3-18 Status OUT Transaction Figure 3-19 Status OUT Operation Flow Figure 3-20 Example of Status OUT Processing.  Table 3-1 Control Transfer Related Registers. | 3-103-133-143-153-163-193-203-223-233-243-263-273-283-293-303-31                             |

09/05/12 Contents

## **Chapter 4. Data Transfers**

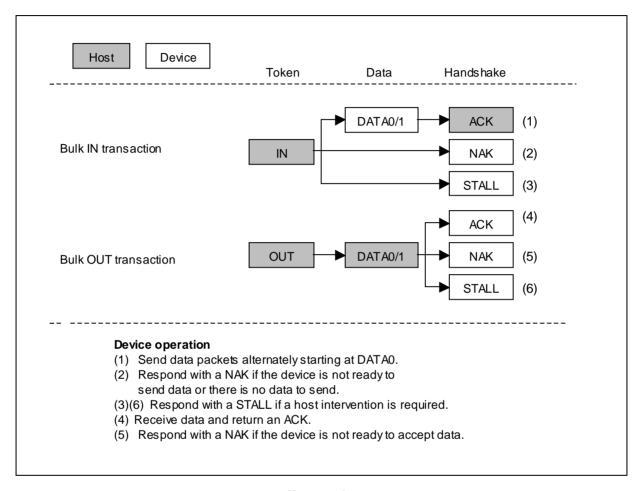

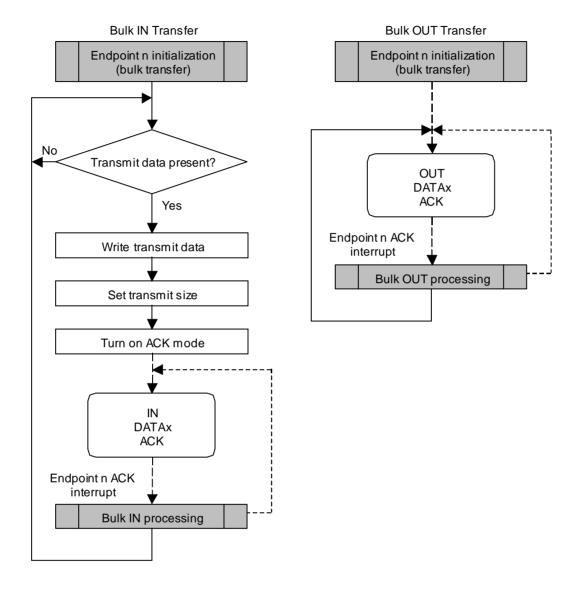

| Figure 4-1 Bulk Transfer Transactions                                      | 4-7  |

|----------------------------------------------------------------------------|------|

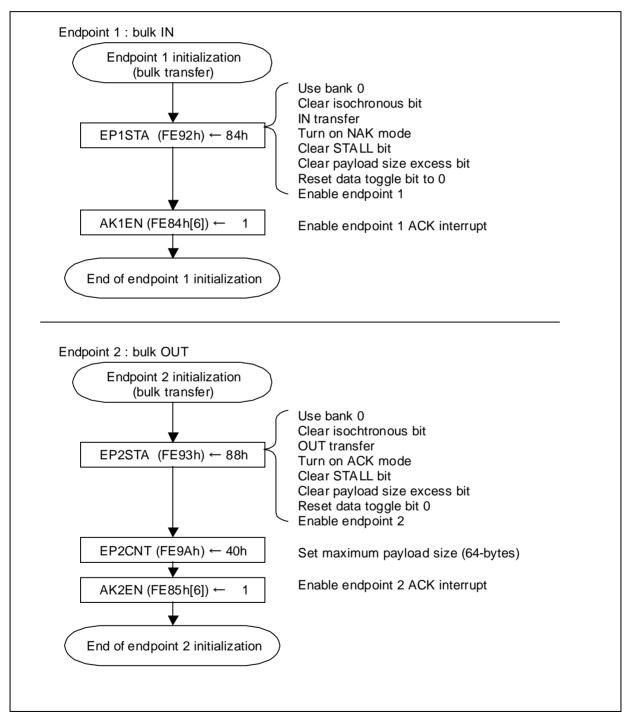

| Figure 4-2 Example of Endpoint n Initialization for Bulk Transfers         | 4-9  |

| Figure 4-3 Bulk IN Operation Flow                                          | 4-12 |

| Figure 4-4 Example of Bulk IN Processing                                   | 4-13 |

| Figure 4-5 Bulk OUT Operation Flow                                         | 4-15 |

| Figure 4-6 Example of Bulk OUT Processing                                  | 4-16 |

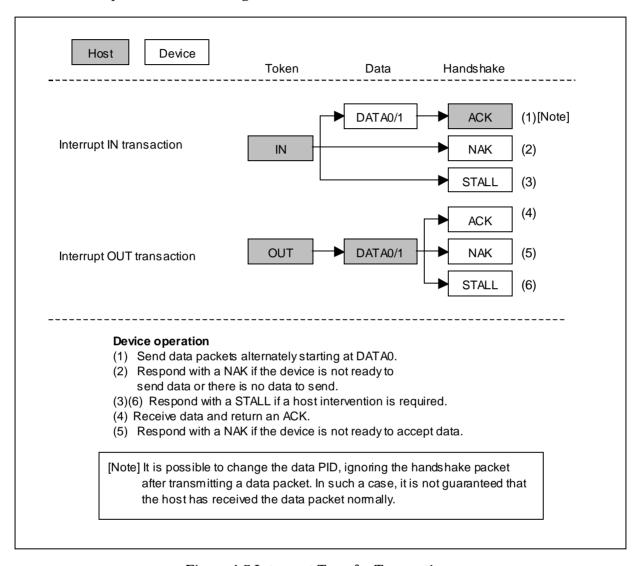

| Figure 4-7 Interrupt Transfer Transactions                                 | 4-18 |

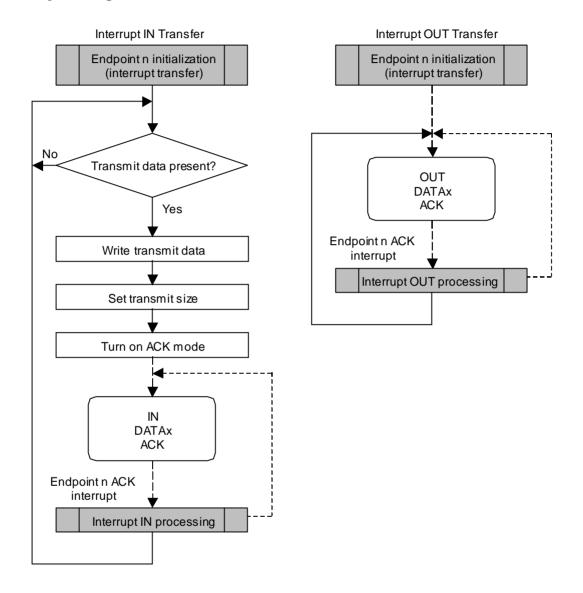

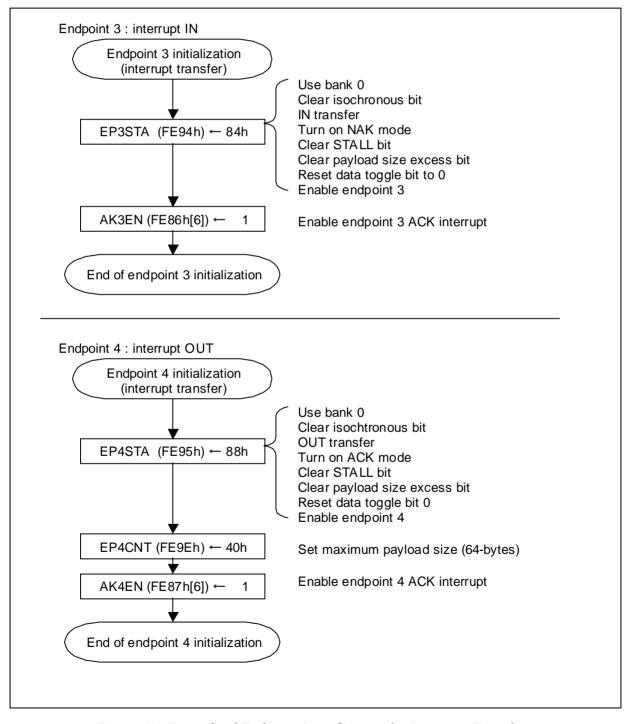

| Figure 4-8 Example of Endpoint Initialization for Interrupt Transfers      | 4-20 |

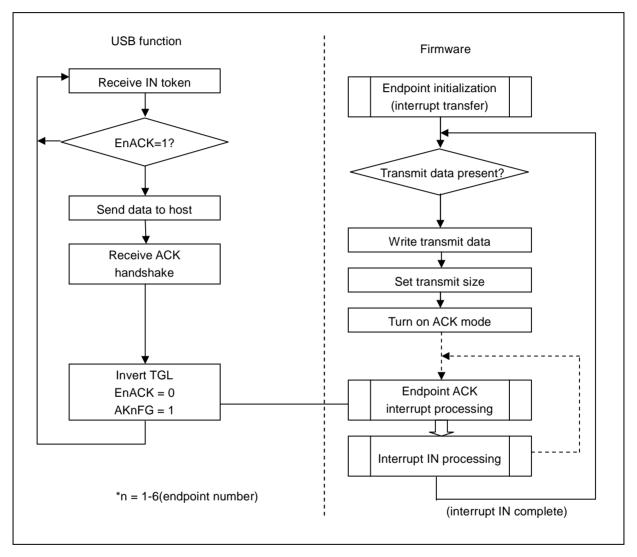

| Figure 4-9 Interrupt IN Operation Flow                                     | 4-23 |

| Figure 4-10 Example of Interrupt IN Processing                             | 4-24 |

| Figure 4-11 Interrupt OUT Operation Flow                                   | 4-26 |

| Figure 4-12 Example of Interrupt OUT Processing                            | 4-27 |

| Figure 4-13 Isochronous Transfer Transactions                              | 4-29 |

| Figure 4-14 Example of Endpoint n Initialization for Isochronous Transfers | 4-31 |

| Figure 4-15 Isochronous IN Operation Flow                                  | 4-35 |

| Figure 4-16 Example of Isochronous IN Processing                           | 4-36 |

| Figure 4-17 Isochronous OUT Operation Flow                                 | 4-38 |

| Figure 4-18 Example of Isochronous OUT Processing                          | 4-39 |

| Table 4-1 Data Transfer Related Registers                                  | 4-2  |

| Table 4-2 Endpoints for Data Transfers                                     | 4-4  |

| Table 4-3 Packet Sizes for Data Transfers                                  |      |

| Table 4-4 Endpoint Descriptor (Bulk Transfer)                              | 4-10 |

| Table 4-5 Endpoint Descriptor (Interrupt Transfer)                         | 4-21 |

| Table 4-6 Endpoint Descriptor (Isochronous Transfer)                       | 4-32 |

# **Chapter 1. Initialization**

| 1.1. Control Program Overview       | 1-2 |

|-------------------------------------|-----|

| 1.2. Related Registers              | 1-3 |

| 1.3. Initializing the LC87F1M16A    | 1-4 |

| 1.4. Initializing the USB Functions | 1-5 |

### 1.1. Control Program Overview

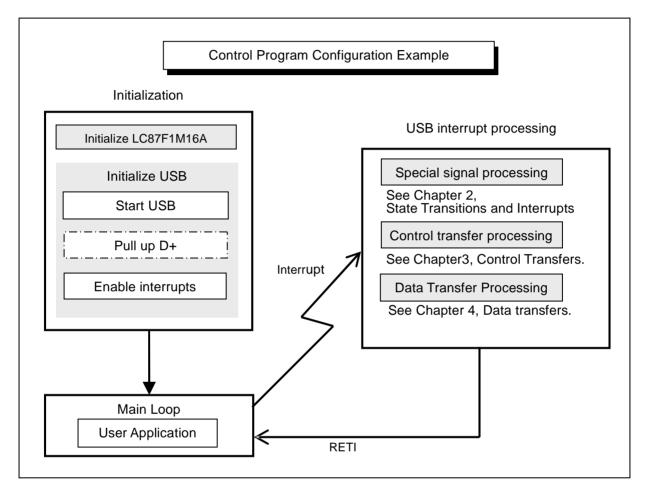

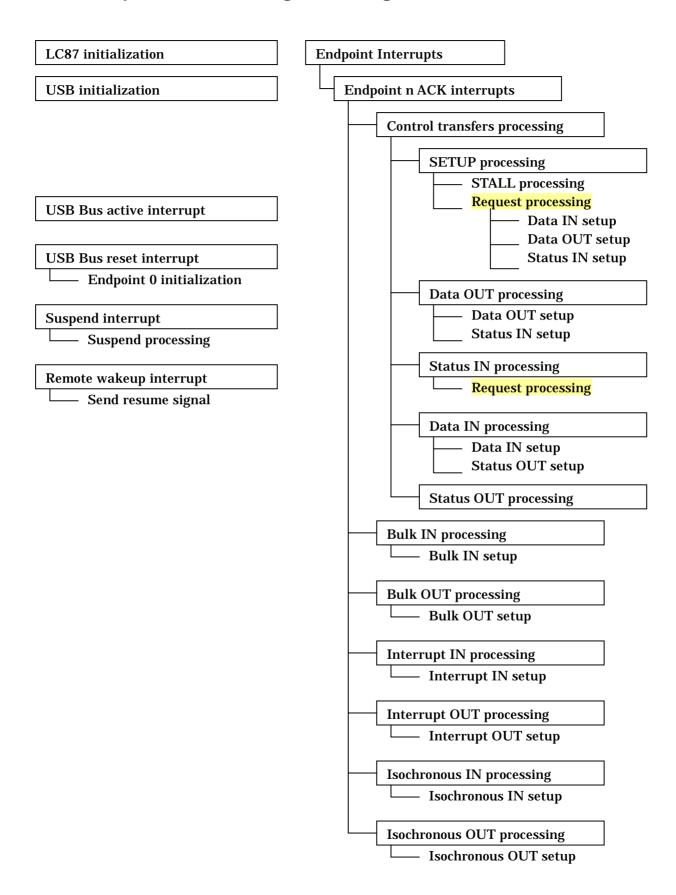

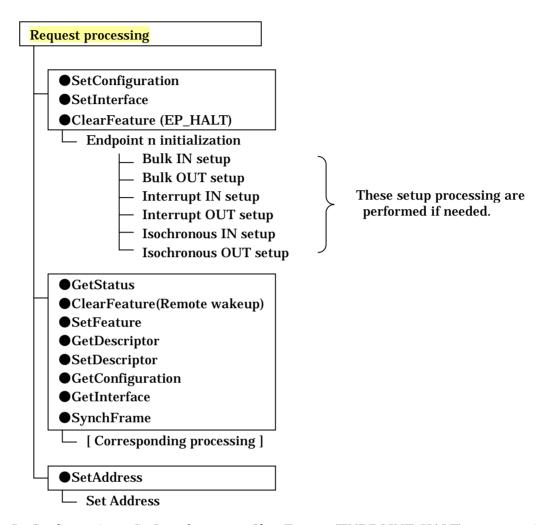

The LC87F1M16A notifies the CPU of USB data transmissions and receptions and special signal processing in the form of interrupts. As such, its control program is composed of an initialization program and a USB interrupt processing program. Assuming that USB sources are to be processed by interrupt processing, the schematic system flow of the LC87F1M16A looks like as shown in below.

The function Main needs to initialize the LC87F1M16A and USB functions. Figure 1-1 shows a sample control program configuration.

Figure 1-1 Sample Control Program Configuration

## 1.2. Related Registers

The table below shows a list of registers that need to be initialized before using the USB functions.

| Register Name                            | Symbol        | Address | R/W | Function              |

|------------------------------------------|---------------|---------|-----|-----------------------|

| USB clock division control register      | USBDIV        | FE04h   | R/W | USB clock devision    |

| Master interrupt enable control register | IE            | FE08h   | R/W | Enables interrupts    |

| System clock division control register   | CLKDIV        | FE0Ch   | R/W | Clock devision        |

| PLL control register                     | PLLCNT        | FE0Dh   | R/W | PLL                   |

| Oscillation control register             | OCR           | FE0Eh   | R/W | Oscillation           |

| USB operation control register           | USCTRL        | FE80h   | R/W | USB operation control |

| USB interrupt control register           | USBINT        | FE82h   | R/W | USB interrupt control |

|                                          |               |         |     | Mapping address in    |

| Endpoint buffer mode register            | <b>EPBMOD</b> | FEABh   | R/W | RAM of the endpoint   |

|                                          |               |         |     | buffer                |

**Table 1-1 Initialization Related Registers**

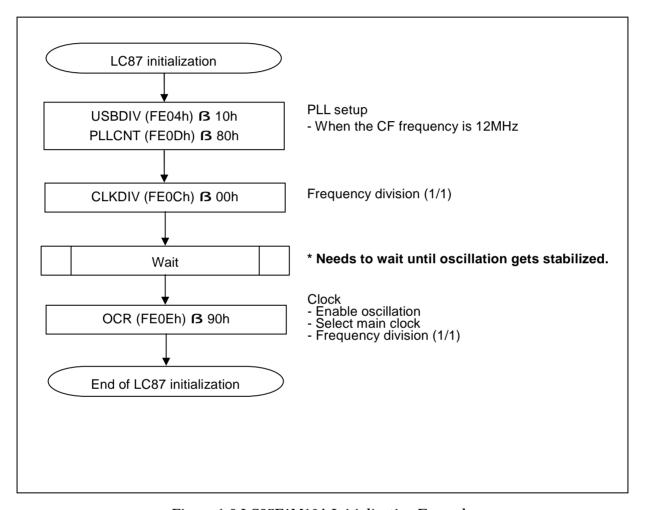

### 1.3. Initializing the LC87F1M16A

When using USB, it is necessary to synchronize the system clock and 48MHz clock for USB. The 48MHz clock for USB is created by PLL circuit using a main clock. The oscillation for the main clock is enabled by connecting a ceramic oscillator and a capacitor across the CF1 and CF2 pins. The system clock selects the divided clock of 48MHz for USB created by the PLL. After the PLL circuit gets stabilized, a wait time need to be provided to avoid unstable operation due to clock related problems. Since the wait time varies depending on the oscillator to be used, an adequate wait time should be provided according to the characteristics of the oscillator.

Figure 1-2 shows a sample procedure for initializing the LC87F1M16A.

Figure 1-2 LC87F1M16A Initialization Example

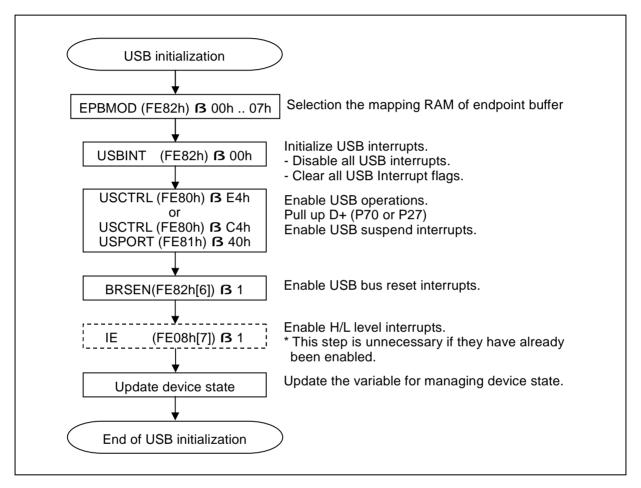

### 1.4. Initializing the USB Functions

It is the Powered state that a USB device initially enters. Accordingly, it is necessary to set up the USB functions so that the device can run in the Powered state. USB initialization should be carried out after completing the initialization of the LC87F1M16A. For details on the device states, see Chapter 2, "State Transitions and Interrupts."

Figure 1-3 shows a sample procedure for initializing the USB.

The endpoint buffer for data transmission and reception (64 bytes maximum) is mapped into RAM. The address mapping RAM of endpoint buffer can be selected by configuring the endpoint buffer mode register (EPBMOD). Table 1-2 – Table 1-10 show the endpoint configuration. In this document EPBMOD=0 (default) is used.

Figure 1-3 USB Initialization Example

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|

| EP0 | Receive  | 64                      | 0200H - 023FH |

|     | Transmit | 04                      | 0240H - 027FH |

| ED1 | Bank 0   | 64                      | 0280H – 02BFH |

| EP1 | Bank 1   | 64                      | 02C0H - 02FFH |

| EDO | Bank 0   | 64                      | 0300H - 033FH |

| EP2 | Bank 1   |                         | 0340H - 037FH |

| EP3 | Bank 0   | 64                      | 0380H - 03BFH |

|     | Bank 1   | 64                      | 03C0H - 03FFH |

| ED4 | Bank 0   | 64                      | 0380H – 03BFH |

| EP4 | Bank 1   | 64                      | 03C0H - 03FFH |

| EP5 | Bank 0   | 64                      | 0300H - 033FH |

|     | Bank 1   | 64                      | 0340H - 037FH |

| EP6 | Bank 0   | 64                      | 0280H – 02BFH |

|     | Bank 1   | 64                      | 02C0H - 02FFH |

Table 1-2 Endpoint Configuration (EPBMOD=0)

|        | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|--------|----------|-------------------------|---------------|

| EP0    | Receive  | 64                      | 0380H – 03BFH |

| EPU    | Transmit | 04                      | 03C0H – 03FFH |

| EP1    | Bank 0   | 64                      | 0300H - 033FH |

| EPI    | Bank 1   | 04                      | 0340H - 037FH |

| EP2    | Bank 0   | C.A                     | 0280H - 02BFH |

| EPZ    | Bank 1   | 64                      | 02C0H - 02FFH |

| EP3    | Bank 0   | 16                      | 0260H – 026FH |

| EFS    | Bank 1   | 10                      | 0270H – 027FH |

| EP4    | Bank 0   | 16                      | 0240H – 024FH |

| EP4    | Bank 1   | 10                      | 0250H - 025FH |

| EP5    | Bank 0   | 16                      | 0220H – 022FH |

| EPO    | Bank 1   | 16                      | 0230H - 023FH |

| EP6    | Bank 0   | 16                      | 0200H - 020FH |

| Bank 1 | 16       | 0210H – 021FH           |               |

Table 1-3 Endpoint Configuration (EPBMOD=1)

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|

| EP0 | Receive  | 64                      | 0380H – 03BFH |

| EPU | Transmit | 04                      | 03C0H - 03FFH |

| EP1 | Bank 0   | 32                      | 0340H - 035FH |

| EFI | Bank 1   | 32                      | 0360H - 037FH |

| EP2 | Bank 0   | 32                      | 0300H - 031FH |

| EP2 | Bank 1   | 32                      | 0320H - 033FH |

| EP3 | Bank 0   | 32                      | 02C0H - 02DFH |

| EFS | Bank 1   | 32                      | 02E0H – 02FFH |

| EP4 | Bank 0   | 32                      | 0280H – 029FH |

| EF4 | Bank 1   | 32                      | 02A0H – 02BFH |

| EP5 | Bank 0   | 32                      | 0240H – 025FH |

| EPO | Bank 1   | 32                      | 0260H - 027FH |

| EDO | Bank 0   | 32                      | 0200H - 021FH |

| EP6 | Bank 1   | J 32                    | 0220H - 023FH |

Table 1-4 Endpoint Configuration (EPBMOD=2)

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|

| EP0 | Receive  | 32                      | 03C0H - 03DFH |

| EFU | Transmit | 32                      | 03E0H - 03FFH |

| ED1 | Bank 0   | 20                      | 0380H - 039FH |

| EP1 | Bank 1   | 32                      | 03A0H - 03BFH |

| ED9 | Bank 0   | 20                      | 0340H - 035FH |

| EP2 | Bank 1   | 32                      | 0360H - 037FH |

| EP3 | Bank 0   | 32                      | 0300H - 031FH |

| EP3 | Bank 1   |                         | 0320H - 033FH |

| EP4 | Bank 0   | 32                      | 02C0H - 02DFH |

| EP4 | Bank 1   |                         | 02E0H - 02FFH |

| EP5 | Bank 0   | 20                      | 0280H - 029FH |

|     | Bank 1   | 32                      | 02A0H - 02BFH |

| EDO | Bank 0   | 32                      | 0240H - 025FH |

| EP6 | Bank 1   |                         | 0260H - 027FH |

Table 1-5 Endpoint Configuration (EPBMOD=3)

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|

| EP0 | Receive  | 32                      | 03C0H - 03DFH |

| EFU | Transmit | 32                      | 03E0H – 03FFH |

| EP1 | Bank 0   | 32                      | 0380H - 039FH |

| EFI | Bank 1   | 32                      | 03A0H - 03BFH |

| EP2 | Bank 0   | 32                      | 0340H – 035FH |

| EF2 | Bank 1   | 32                      | 0360H – 037FH |

| EP3 | Bank 0   | 32                      | 0300H - 031FH |

| EFS | Bank 1   | 32                      | 0320H – 033FH |

| EP4 | Bank 0   | 16                      | 02E0H – 02EFH |

| EF4 | Bank 1   | 10                      | 02F0H – 02FFH |

| EP5 | Bank 0   | 16                      | 02C0H – 02CFH |

| EPO | Bank 1   | 10                      | 02D0H – 02DFH |

| EP6 | Bank 0   | 16                      | 02A0H - 02AFH |

| EP0 | Bank 1   | 16                      | 02B0H – 02BFH |

Table 1-6 Endpoint Configuration (EPBMOD=4)

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|

| EDO | Receive  | 32                      | 03C0H - 03DFH |

| EP0 | Transmit | 32                      | 03E0H - 03FFH |

| ED1 | Bank 0   | 1.0                     | 03A0H - 03AFH |

| EP1 | Bank 1   | 16                      | 03B0H - 03BFH |

| EP2 | Bank 0   | 16                      | 0380H - 038FH |

| EFZ | Bank 1   | 10                      | 0390H - 039FH |

| EP3 | Bank 0   | 16                      | 0360H - 036FH |

| EPS | Bank 1   | 10                      | 0370H - 037FH |

| EP4 | Bank 0   | 16                      | 0340H - 034FH |

| EP4 | Bank 1   | 10                      | 0350H - 035FH |

| EP5 | Bank 0   | 10                      | 0320H - 032FH |

| EPo | Bank 1   | 16                      | 0330H - 033FH |

| EDe | Bank 0   | 10                      | 0300H - 030FH |

| EP6 | Bank 1   | 16                      | 0310H - 031FH |

Table 1-7 Endpoint Configuration (EPBMOD=5)

|     | Setting  | Max. Size<br>(in bytes) | RAM Address   |

|-----|----------|-------------------------|---------------|