## DESCRIPTION

The FAN54120 Evaluation Board is a compact demonstration circuit for the FAN54120 500mA USB Compatible Single Cell Li-Ion Linear Charger with Power Back Capability. This user guide should be used in conjunction with the FAN54120 product datasheet.

The board supports two device packages (WLCSP and DFN). The DFN option is implemented on one board surface, while the CSP package is on the opposite side. Circuit function, features, and connections are replicated on both sides.

## CONNECTIONS

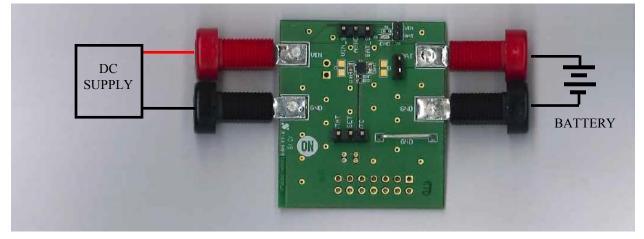

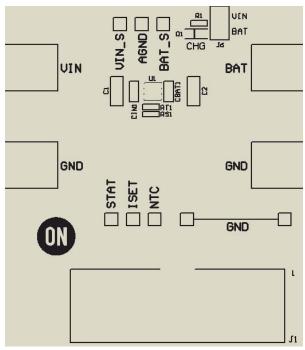

The diagram below illustrates the essential connections for FAN54120 Evaluation Board demonstration.

DC Supply: Connect a 5V, >500mA DC supply to the VIN and GND input terminals.

Battery: Connect a Li-Ion battery to the BAT and GND output terminals.

An electronic battery emulator instrument may be substituted for the battery. A 2 quadrant power source could also be used, although it may have dynamic limitations not suitable for transient testing.

# FEATURES

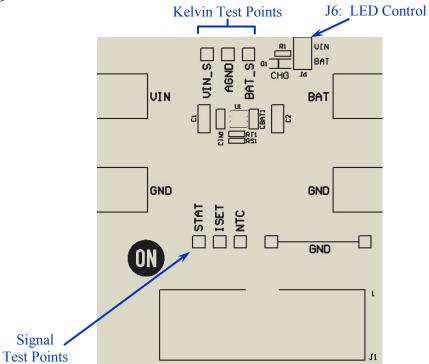

# **Kelvin Test Points**

VIN\_S, BAT\_S, and AGND are Kelvin connected test points for input and output voltage.

# LED Control (J6)

J6 jumper position determines the power source for the LED (VIN or BAT).

If no jumper is installed, the LED will not illuminate, although correct STAT signaling/function is preserved due to it's internal pull-up to BAT.

## **Signal Test Points**

- **STAT:** Test point to indicate charger status. STAT is also used to initiate Power-Back mode operation, by externally forcing STAT low.

- **ISET:** Test point to indicate charger status. STAT is also used to initiate Power-Back mode operation, by externally forcing STAT low.

- NTC: Can be used to connect battery pack NTC, provided RT1/RT2 are un-populated.

Connecting a DC supply to NTC, relative to GND, allows the user to modulate the voltage to demonstrate the JEITA behavior of device. The source must sink >50uA.

Additionally, the NTC=GND functionality can be demonstrated by tying NTC to GND before VIN is applied.

C1 – C4 Empty locations to augment CIN or CBAT - accepts 0603 or 0805 size discretes.

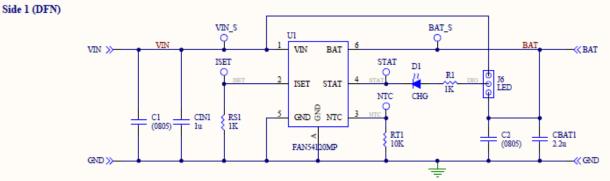

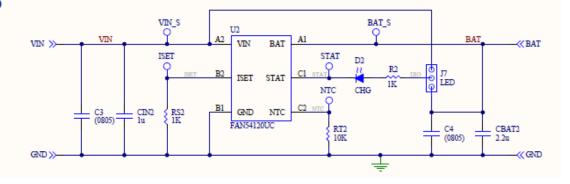

# SCHEMATIC

Side 2 (CSP)

## **COMPONENT LIST**

| REFERENCE DESIGNATOR |                | QTY | DESCRIPTION                  | MANUFACTURER / NUMBER    |

|----------------------|----------------|-----|------------------------------|--------------------------|

| 2x2 DFN6             | CSP6           |     |                              |                          |

| (Top Layer)          | (Bottom Layer) |     |                              |                          |

| U1                   |                | 1   | IC, FAN54120MP420X, 2x2 DFN6 |                          |

|                      | U2             |     |                              | IC, FAN54120UC420X, CSP6 |

| CIN1                 | CIN2           | 1   | 1.0uf, 25V, 10%, X5R, 0603   | TDK CGB3B1X5R1E105K      |

| CBAT1                | CBAT2          | 1   | 2.2uf, 10V, 10%, X5R, 0603   | TDK CGA3E3X5R1A225K      |

| R1, RS1              | R2, RS2        | 2   | 1.00K, 1%, 0402              |                          |

| RT1                  | RT2            | 1   | 10K, 5%, 0402                |                          |

| D1                   | D2             | 1   | LED, Amber, 0603             | Lite-On LTST-C190KFKT    |

| C1, 2                | C3, 4          | 2   | 0805 un-populated            |                          |

# PCB

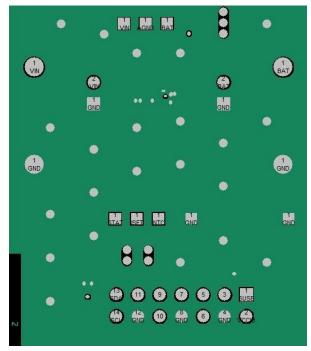

Top Legend

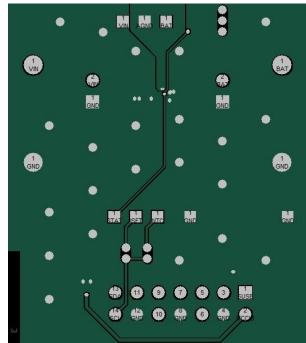

Layer 2

Top Layer

# Layer 3

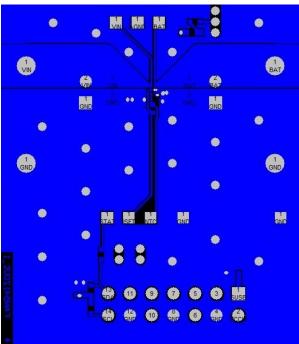

# Bottom Layer

Bottom Legend иIV BAT BUT\_2 DIN<sup>2</sup> ACHD \$11 анэ SL. VIN BAT 8 3 GND GND TAT2 GND ИО [8]] [4] 112 ac ÷L. E B B

#### © 2019 On Semiconductor Corporation

5