# ON Semiconductor®

# Bi-CMOS 集積回路

# CCD 用 垂直クロックドライバ

http://onsemi.jp

### 概要

LV5609LPは、CCD用垂直クロックドライバである。

### 機能

- · 3値出力×2ch

- ·2値出力×2ch

- ·SHT出力×1ch

- · 出力0N抵抗:30Ω typ

# 絶対最大定格/Ta=25℃, V<sub>SS</sub>=VM=0V

| 項目     | 記号                  | 条件      | 定格値             | unit       |

|--------|---------------------|---------|-----------------|------------|

| 最大電源電圧 | V <sub>DD</sub> max |         | 6               | V          |

|        | VH max              |         | 20              | V          |

|        | VL max              |         | -10             | V          |

|        | VH-VL max           |         | 24              | V          |

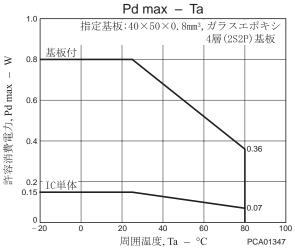

| 許容消費電力 | Pd max              | 指定基板付き※ | 0.8             | W          |

| 動作周囲温度 | Topr                |         | $-20 \sim +80$  | $^{\circ}$ |

| 保存周囲温度 | Tstg                |         | $-40 \sim +125$ | $^{\circ}$ |

<sup>※</sup> 指定基板:40mm×50mm×0.8mm, ガラスエポキシ 4層(2S2P)基板

最大定格を超えるストレスは、デバイスにダメージを与える危険性があります。最大定格は、ストレス印加に対してのみであり、推奨動作条件を超えての機能 的動作に関して意図するものではありません。推奨動作条件を超えてのストレス印加は、デバイスの信頼性に影響を与える危険性があります。

### 許容動作範囲/Ta=25℃, Vss=VM=0V

| 11 1 3 1 1 1 1 0 0 1 1 3 0 1 1 1 1 1 1 1 |                   |    |                    |      |                   |      |  |  |

|------------------------------------------|-------------------|----|--------------------|------|-------------------|------|--|--|

| 項目                                       | 記号                | 条件 | min                | typ  | max               | unit |  |  |

| 電源電圧                                     | $v_{DD}$          |    | 2.0                | 3. 3 | 5. 5              | V    |  |  |

|                                          | VH                |    |                    | 15   | 17                | V    |  |  |

|                                          | VL                |    | -8.5               | -7.5 | -4                | V    |  |  |

|                                          | VH-VL             |    |                    |      | 23. 5             | V    |  |  |

| CMOS入力「H」電圧                              | $v_{IN}H$         |    | 0.8V <sub>DD</sub> |      | $v_{\mathrm{DD}}$ | V    |  |  |

| CMOS入力「L」電圧                              | V <sub>IN</sub> L |    | -0.1               |      | 0.4               | V    |  |  |

**電気的特性**/Ta=25℃, V<sub>DD</sub>=3.3V, V<sub>SS</sub>=0V, VH=15V, VL=−7.5V, VM=0V, ただし特記項目が無い場合

| 項目      | 記号       | 条件                       | min | typ  | max  | unit |

|---------|----------|--------------------------|-----|------|------|------|

| 静的消費電流  | $I_{DD}$ | VDD端子                    |     |      | 1    | μA   |

|         | IH       | VH端子                     |     |      | 10   | μA   |

|         | IL       | VL端子                     | -10 |      |      | μA   |

| 動的消費電流  | $I_{DD}$ | V <sub>DD</sub> 端子 ※1 ※2 |     |      | 1    | mA   |

|         | IH       | VH端子 ※1 ※2               |     | 2. 4 | 4. 5 | mA   |

|         | IL       | VL端子 ※1 ※2               |     | 3    | 5    | mA   |

| 出力オン抵抗  | RL       | $I_0 = +10 \text{mA}$    |     | 20   | 30   | Ω    |

|         | RM       | $I_0 = \pm 10$ mA        |     | 30   | 45   | Ω    |

|         | RH       | I <sub>0</sub> =-10mA    |     | 30   | 40   | Ω    |

|         | RSHT     | I <sub>0</sub> =-10mA    |     | 30   | 40   | Ω    |

| 伝播遅延時間  | TPLM     | 無負荷                      |     |      | 200  | ns   |

|         | TPMH     | 無負荷                      |     |      | 200  | ns   |

|         | TPLH     | 無負荷                      |     |      | 200  | ns   |

|         | TPML     | 無負荷                      |     |      | 200  | ns   |

|         | TPHM     | 無負荷                      |     |      | 200  | ns   |

|         | TPHL     | 無負荷                      |     |      | 200  | ns   |

| 立ち上がり時間 | TTLM     | VL→VM V1, V3 <b>※</b> 1  |     |      | 800  | ns   |

|         |          | VL→VM V2, V4 <b>※</b> 1  |     |      | 800  | ns   |

|         | TTMH     | VM→VH V1, V3 <b>※</b> 1  |     |      | 800  | ns   |

|         | TTLH     | VL→VH SHT ※1             |     |      | 200  | ns   |

| 立ち下がり時間 | TTML     | VM→VL V1, V3 ※1          |     |      | 800  | ns   |

|         |          | VM→VL V2, V4 ※1          |     |      | 800  | ns   |

|         | TTHM     | VH→VM V1, V3 ※1          |     |      | 800  | ns   |

|         | TTHL     | VH→VL SHT ※1             |     |      | 200  | ns   |

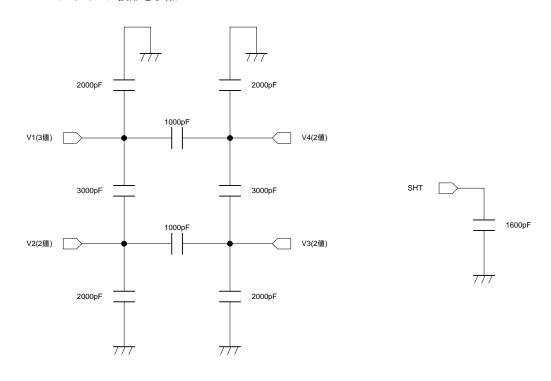

※1 下記 CCD 等価負荷を参照

※27ページのタイミング波形を参照

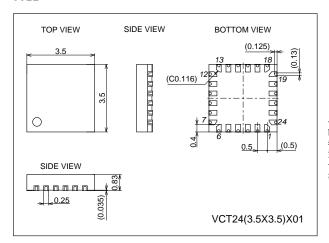

# 外形図

unit:mm (typ)

3322

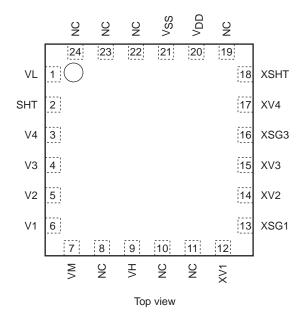

# ピン配置図

端子機能

| <u> </u> |                   |                        |  |  |  |

|----------|-------------------|------------------------|--|--|--|

| 端子No.    | 端子名               | 説明                     |  |  |  |

| 1        | VL                | 出力用Lo電源(-7.5V系)        |  |  |  |

| 2        | SHT               | レベルシフト出力(2値VH, VL)     |  |  |  |

| 3        | V4                | レベルシフト出力(2値VM, VL)     |  |  |  |

| 4        | V3                | レベルシフト出力(3値VH, VM, VL) |  |  |  |

| 5        | V2                | レベルシフト出力(2値VM, VL)     |  |  |  |

| 6        | V1                | レベルシフト出力(3値VH, VM, VL) |  |  |  |

| 7        | VM                | 出力用GND                 |  |  |  |

| 8        | NC                |                        |  |  |  |

| 9        | VH                | 出力用Hi電源(15V系)          |  |  |  |

| 10       | NC                |                        |  |  |  |

| 11       | NC                |                        |  |  |  |

| 12       | XV1               | V1転送パルス入力              |  |  |  |

| 13       | XSG1              | V1読み出しパルス入力            |  |  |  |

| 14       | XV2               | V2転送パルス入力              |  |  |  |

| 15       | XV3               | V3転送パルス入力              |  |  |  |

| 16       | XSG3              | V3読み出しパルス入力            |  |  |  |

| 17       | XV4               | V4転送パルス入力              |  |  |  |

| 18       | XSHT              | SHTパルス入力               |  |  |  |

| 19       | NC                |                        |  |  |  |

| 20       | $v_{\mathrm{DD}}$ | 入力バッファ用電源(3.3V系)       |  |  |  |

| 21       | V <sub>SS</sub>   | 入力バッファ用GND             |  |  |  |

| 22       | NC                |                        |  |  |  |

| 23       | NC                |                        |  |  |  |

| 24       | NC                |                        |  |  |  |

|          |                   |                        |  |  |  |

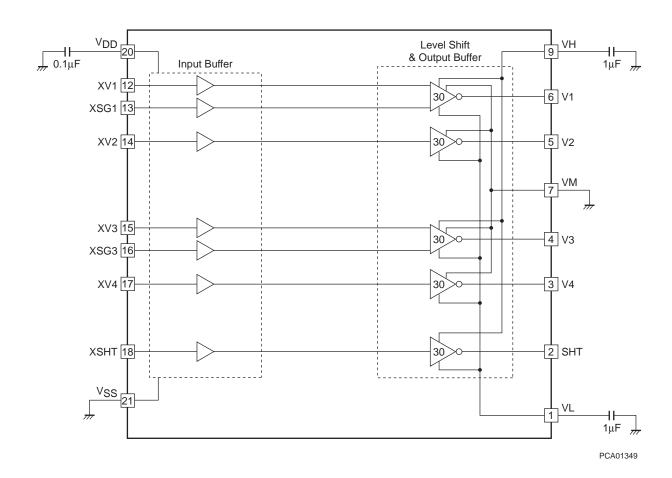

# ブロック図

# 論理機能表

| 入力  |      |     |      | 出力 |    |     |  |

|-----|------|-----|------|----|----|-----|--|

| XV1 | XSG1 | XV2 | XSHT | V1 | V2 | SHT |  |

| XV3 | XSG3 | XV4 |      | V3 | V4 |     |  |

| L   | L    | X   | X    | VH | X  | X   |  |

| L   | Н    | X   | X    | VM | X  | X   |  |

| Н   | L    | X   | X    | VL | X  | X   |  |

| Н   | Н    | X   | X    | VL | X  | X   |  |

| X   | X    | L   | X    | Х  | VM | X   |  |

| X   | X    | Н   | X    | Х  | VL | X   |  |

| X   | X    | X   | L    | X  | X  | VH  |  |

| X   | X    | X   | Н    | Х  | X  | VL  |  |

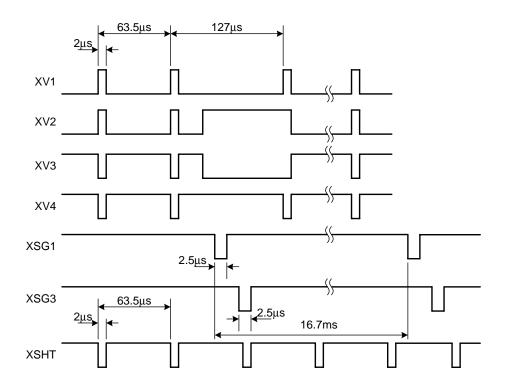

# タイミングチャート

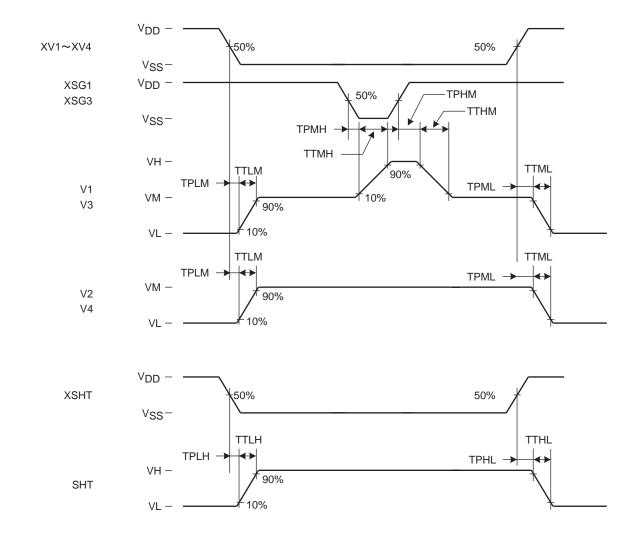

# CCD等価負荷測定タイミング波形

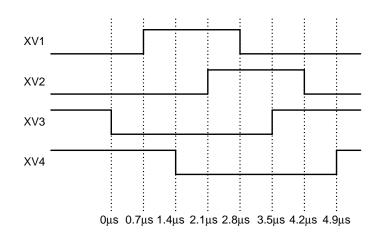

# オーバーラップ部分拡大図

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equ

ON Semi-conductor及びONのロゴはSemi-conductor Components Industries, LLC (SCILLC)の登録商標です。SCILLCは特許、商標、著作権、トレードシークレット(営業秘密)と他の知的所有権に対する権利を保有します。SCILLCの製品/特許の適用対象リストについては、以下のリンクからご覧いただけます。www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLCは通告なしで、本書記載の製品の変更を行うことがあります。SCILLCは、いかなる特定の目的での製品の適合性について保証しておらず、また、お客様の製品において回路の応用や使用から生じた責任、特に、直接的、間接的、偶発的な損害に対して、いかなる責任も負うことはできません。SCILLCデータシートや仕様書に示される可能性のある「標準的」パラメータは、アプリケーションによっては異なることもあり、実際の性能も時間の経過により変化する可能性があります。「標準的」パラメータを含むすべての動作パラメータは、で使用になるアプリケーションに応じて、お客様の専門技術者において十分検証されるようお願い致します。SCILLCは、その特許権やその他の権利の下、いかなるライセンスも許諾しません。SCILLC製品は、人体への外科的移植を目的とするシステムへの使用、生命維持を目的としたアプリケーション、また、SCILLC製品の不具合による死傷等の事故が起こり得るようなアプリケーションなどへの使用を意図した設計はされておらず、また、これらを使用対象としておりません。お客様が、このような意図されたものではない、許可されていないアプリケーション用にSCILLC製品を購入または使用した場合、たとえ、SCILLCがその部品の設計または製造に関して過失があったと主張されたとしても、そのような意図せぬ使用、また未許可の使用に関連した死傷等から、直接、又は間接的に生じるすべてのクレーム、費用、損害、終費、および弁護士料などを、お客様の責任において補償をお願いいたします。また、SCILLCとその役員、従業員、子会社、関連会社、代理店に対して、いかなる損害も与えないものとします。

SCILLCは雇用機会均等/差別撤廃雇用主です。この資料は適用されるあらゆる著作権法の対象となっており、いかなる方法によっても再販することはできません。