# Test Procedure for the NCV7471B5V1GEVB Evaluation Board

# Required Equipment

- Oscilloscope with digital inputs

- Bench Power Supply

- Voltmeter

- Signal Generator (SPI capable)

- NCV7471B Evaluation Board

# Test procedure Step 1 (Power-up sequence, Normal mode, Boost-buck operation):

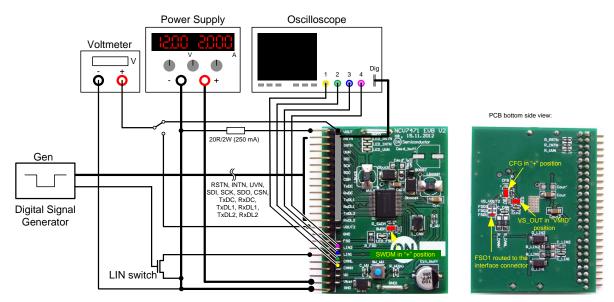

- 1. Connect the setup as shown above, but without VOUT load; SWDM and CFG soldering straps have to be in "+" position

- 2. Set VS\_VOUT2 to "VMID" position

- 3. Apply an input voltage,  $V_{BAT} = 12 \text{ V}$ , current capability min. 1.5 A

- 4. Check VOUT, LIN1, LIN2, CANH, CANL, RxDL1, RxDL2, RxDC, RSTN, INTN and UVN VOUT State

- Check I<sub>BAT</sub>.

## ¬Table 1: Desired Results

| •                               |  |

|---------------------------------|--|

| $I_{BAT} < 20 \text{ mA}$       |  |

| VOUT = ON                       |  |

| LIN1/2 = RECESSIVE              |  |

| CANH, CANL = RECESSIVE          |  |

| RxDL1/2 = HIGH                  |  |

| RxDC = HIGH                     |  |

| RSTN = HIGH (LED_RSTN = off)    |  |

| INTN = HIGH (LED_INTN = off)    |  |

| UVN_VOUT = HIGH (LED_UVN = off) |  |

# Test procedure Step 2 (Boost-buck converter function):

- 1. Connect load to VOUT (250 mA, depending on assembly option)

- 2. Alternate VBAT voltage in full operating range (5 28 V)

- 3. Check VOUT, RSTN, INTN and UVN VOUT State

- Check I<sub>BAT</sub>.

- 5. Set input voltage to initial value, VBAT = 12 V

#### Table 2: Desired Results

| IBAT should decrease with increasing VBAT                      |

|----------------------------------------------------------------|

| VOUT ON                                                        |

| RSTN = HIGH (LED_RSTN = off)                                   |

| INTN = HIGH (LED_INTN = off)                                   |

| UVN_VOUT = HIGH (LED_UVN = off) for VOUT = 5 V                 |

| $UVN_VOUT = LOW (LED_UVN = on) $ for $VOUT < 4.65 $ V $(Typ.)$ |

| VMID > 11 V (check on the test point)                          |

# Test procedure Step 3 (LIN1/2 Transmit in Normal mode):

- 1. Set TxDL1/2 to LOW, wait < 6 ms, set TxDL1/2 HIGH (Generate LIN Dominant state); can be repeated with 50% duty cycle

- Observe LIN1/2 and RxDL1/2. Start observation with TxDL1/2 falling edge.

#### Table 3: Desired Results

| LIN1/2 = Contain one Dominant pattern  |  |

|----------------------------------------|--|

| RxDL1/2 = Contain one Dominant pattern |  |

# Test procedure Step 4 (CAN Transmit in Normal mode):

- Set TxDC to LOW, wait < 300 us, set TxDC HIGH (Generate CAN Dominant state); can be repeated with 50% duty cycle</li>

- 2. Observe CANH, CANL and RxDC. Start observation with TxDC falling edge.

#### Table 4: Desired Results

| CANH, CANL = Contain one Dominant pattern |  |

|-------------------------------------------|--|

| RxDC = Contains one Dominant pattern      |  |

# Test procedure Step 5 (VOUT2 LDO function, SPI function):

- 1. Send SPI command to activate VOUT2 regulator (SPI bit enVOUT2=1 in CONTROL1 register; SPI frame = 0x2400)

- Read SPI data from CONTROL1 register (send SPI frame = 0x3000)

Connect load to VOUT2 (50 mA)

Check VOUT2 State

#### Table 5: Desired Results

| CONTROL1 = 0x3400 |

|-------------------|

| VOUT2 = ON        |

# ON Semiconductor®

### Test procedure Step 6 (Transition to Sleep mode):

- 1. Leave TxDL1, TxDL2 and TxDC floating (to simulate a microcontroller without power supply being connected to digital pins)

- Send SPI Sleep command (SPI frame = 0x0600)

- Disconnect SPI digital pins (to simulate a microcontroller without power supply being connected to digital pins)

Check IBAT, VOUT, VOUT2, RSTN, INTN, UVN\_VOUT State. Caution should be taken with oscilloscope digital probes resistance which could have influence on overall IBAT current.

#### **Table 6: Desired Results**

| I <sub>BAT</sub> = Typ. 300 μA (incl. R_SWDM and R_CFG pull-up current) |  |

|-------------------------------------------------------------------------|--|

| VOUT = OFF                                                              |  |

| RSTN = LOW (LED_RSTN = off, due to VOUT off)                            |  |

| INTN = LOW (LED_INTN = off, due to VOUT off)                            |  |

| UVN_VOUT = LOW (LED_UVN = off, due to VOUT off)                         |  |

# Test procedure Step 7 (LIN1/2 Wakeup):

- 1. In Sleep, generate Remote LIN1 pattern: Set Gen HIGH, wait > 150  $\mu$ s, set Gen LOW

- 2. Check VOUT, RxDL1/2, RSTN, INTN State

#### Table 7: Desired Results

| VOUT = ON                                                             |  |

|-----------------------------------------------------------------------|--|

| RxDL1 = LOW – Signaling Wakeup source                                 |  |

| RxDL2 = HIGH                                                          |  |

| RSTN = HIGH (LED_RSTN = off)                                          |  |

| INTN = 1 ms HIGH / 5 ms LOW pulses - Signaling Wakeup (LED_INTN = on) |  |

| UVN VOUT = HIGH (LED UVN = off)                                       |  |

### Test procedure Step 8 (Fail-safe mode, FSO1 functionality):

- 1. FSO1 soldering strap has to be connected

- 2. Short VOUT, wait > 1.65 s

- 3. Check VOUT, RSTN, FSO1 State

- 4. Remove VOUT short

| VOUT = OFF                 |

|----------------------------|

| RSTN = LOW (LED_RSTN = on) |

| FSO1 = HIGH (LED FSO = on) |

### Test procedure Step 9 (WU function, wakeup from Fail-safe mode):

- 1. Generate Local wakeup: Short WU pin to GND, wait > 50 us (or press the SW WU button)

- 2. Check VOUT, RSTN, FSO1 State

| VOUT = ON                    |

|------------------------------|

| RSTN = HIGH (LED_RSTN = off) |

| FSO1 = HIGH (LED_FSO = on)   |

### **DC** Characteristics

|                                            | MIN                      | TYP   | MAX    |

|--------------------------------------------|--------------------------|-------|--------|

| VOUT ON                                    | 4.9 V                    | 5.0 V | 5.1 V  |

| VOUT2 ON                                   | 4.83 V                   | 5.0 V | 5.17 V |

| RSTN, INTN, UVN_VOUT,<br>RxDL1/2, RxDC LOW |                          |       | 0.4 V  |

| RxDL1/2, RxDC HIGH                         | VOUT-0.4 V               |       |        |

| LIN DOMINANT                               |                          |       | 2 V    |

| LIN RECESSIVE                              | V <sub>BAT</sub> - 1.5 V |       |        |

| CANH DOMINANT                              | 3.0 V                    | 3.6 V | 4.25 V |

| CANL DOMINANT                              | 0.5 V                    | 1.4 V | 1.75 V |

| CANH-CANL RECESSIVE                        | -0.12 V                  |       | 0.05 V |